# Inkjet Printed Microelectronic Devices and Circuits

Ph.D. Thesis Dissertation (Microelectronics and Electronics System Department)

Author: Eloi Ramon i Garcia Supervisor: Jordi Carrabina i Bordoll

UNIVERSITAT AUTÒNOMA DE BARCELONA (UAB) September 2014 Bellaterra, Catalonia

| I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                           |

|                                                                                                                                                                           |

|                                                                                                                                                                           |

Dr. Jordi Carrabina i Bordoll

This work was carried out at Universitat Autònoma de Barcelona, Catalonia, and Technical University of Chemnitz (TUC), Chemnitz, Germany.

#### © 2014 Eloi Ramon i Garcia

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

# **ABSTRACT**

In the last years there has been a growing interest in the realization of low-cost, flexible and large area electronic systems such as item-level RFID tags, flexible displays or smart labels, among others. Printed Electronics has emerged as one of the most promising alternative manufacturing technologies due to its lithography- and vacuum-free processing. Related to this, organic and inorganic solution processed materials advanced rapidly improving the performance of printed devices. However, the fabrication of organic transistors, key element to build circuits for acquisition and processing, suffers from the poor resolution and layer-to-layer registration of current printing techniques such as inkjet and gravure printing. To compensate that, transistors implemented in those technologies have large channel lengths and large gate to source/drain overlaps. These large dimensions limit the performance of the printed transistors, despite the improvements in materials.

This thesis focuses on circumventing the printing resolution challenges using compensation techniques and new layout geometries while keeping an all-inkjet purely printing process. The dissertation deals with the development of microelectronic passive and active devices implemented using low-cost inkjet printing machinery. I focussed my effort in the design, manufacturing & characterization (electrical and morphological) points of view in order to allow the fabrication of organic integrated circuits.

Several thousands of resistors, capacitors and transistors were fabricated, all of them fully inkjet-printed. All devices were morphologically and electrically characterized. A high number of experiments were developed to ensure efficient manufacturing and report on parameter variation, thus obtaining statistically significant data. Process variations present in transistor fabrication lead to a certain variability on the resulting transistor parameters that need to be taken in account. Scalability, variability and yield were analysed by using different strategies.

Fabricated inverters show a clear inversion behaviour demonstrating the state of the inkjet fabrication process to integrate printed devices in circuits. This is a first step in the way to fabricate all-inkjet complex circuits.

The amount of samples manufactured by the fully inkjet printing approach can be considered an outstanding achievement and contributes to a better knowledge of the behaviour and failure origins of organic and printed devices.

# RESUM

En els darrers anys ha anat creixent l'interès per la fabricació de sistemes de baix cost, flexibles i sobre gran àrea com, per exemple, les etiquetes RFID per a identificació de productes, les pantalles flexibles o les etiquetes intel·ligents entre d'altres. La tecnologia d'impressió electrònica (Printed Electronics) s'ha posicionat com una de les tecnologies alternatives de fabricació més prometedores pel fet de no utilitzar tècniques fotolitogràfiques i de buit. Alhora, la millora en materials orgànics i inorgànics ha provocat un increment en les prestacions dels dispositius impresos. Tot i això, la fabricació de transistors orgànics, element clau per a construir circuits electrònics d'adquisició o processament, es veu afectada per la poca resolució i registre entre capes de les tecnologies d'impressió actuals com inkjet o gravat. Per compensar-ho, els transistors implementats utilitzant aquestes tecnologies tenen llargades de canal molt grans i grans solapaments entre porta i font/drenador. Aquestes grans dimensions limiten les prestacions dels transistors impresos, tot i les millores obtingudes en els materials.

Aquesta tesi està enfocada en contrarestar els problemes provocats per la poca resolució en impressió utilitzant tècniques de compensació i noves geometries de dispositius mantenint el procés completament inkjet. Aquest treball s'enfoca en el desenvolupament de dispositius microelectrònics passius i actius implementats amb maquinària inkjet de baix cost. He enfocat el meu esforç en el disseny, la fabricació i la caracterització (elèctrica i morfològica) amb l'objectiu de fer possible la fabricació de circuits integrats orgànics.

En el marc de la tesi, s'han fabricat varis milers de transistors, capacitats i resistències exclusivament amb tecnologia inkjet. Tots els dispositius s'han caracteritzat tant elèctrica com morfològicament. S'ha dut a terme un gran número d'experiments per assegurar una fabricació eficient, estudiar la variabilitat dels paràmetres i obtenir dades estadísticament significatives. La variació en els processos de fabricació de transistors porta a una important variabilitat en els paràmetres dels dispositius impresos fins ara poc estudiada. Escalabilitat, variabilitat i rendiment s'han analitzat utilitzant diferents estratègies.

S'han obtingut circuits digitals amb un comportament adient, demostrant l'estat actual de la tecnologia inkjet per a integrar dispositius impresos en circuits. Aquest és un primer pas en el camí per fabricar circuits més complexes amb tecnologia d'impressió inkjet.

La quantitat de mostres fabricades amb tecnologia inkjet es pot considerar com un assoliment important i contribueix a millorar el coneixement del comportament i els orígens de fallades dels dispositius orgànics i impresos.

$Nothing\ in\ Nature\ is\ random...$

$A\ thing\ appears\ random\ only\ through\ the$   $incompleteness\ of\ our\ knowledge.$

Spinoza (1632 - 1677)

# **ACKNOWLEDGEMENTS**

I would like to show my deepest gratitude to my parents, Albert and Virtuts, for their unflagging care and love throughout my life. They have always been there to support me in all my adventures.

This thesis would not have been possible without the wholehearted support from my wife, Anna, and my daughters Jana and Queralt. With their support, patience and encouragement during these hard years, my dream of pursuing a Ph.D. degree finally comes true.

But at this stage of life it is difficult to remember everybody who had a certain impact on my evolution or the evolution of my thesis work. I will try not to forget anyone, but there are so many, I apologize profusely if I miss someone. It is not intended.

I want to start with my colleagues at CaiaC-UAB: Eduard Fernández, David Castells and Carme Martínez for sharing knowledge, doubts, jokes, breakfast, lunch time, dinners, funny and sad moments... in a good harmony and in a positive way. Thank you. I want specially to thank David for his invaluable support, friendship and ability to create novel ideas. Always interested about everything, he has been an excellent colleague to survive in the toxic waters. At the university I learnt why God drove us out of paradise. Also, I want to give my deepest thanks to Carme for her help during three years: characterizing, analysing, proposing new ideas, and writing papers during holidays... You have been more than a colleague to me. Thank you. I hope to help you in your thesis as you helped me in mine.

I also want to give my thanks to Jordi Mujal, Cristina Casellas and Laia Francesch. We started working together 6 years ago spreading ink everywhere. I also want to thank Nicolas Renaud and Markus Hoffmann, which whom we shared time, conversations, travels and projects. I miss your opinions and contributions.

I want to thank so many people from CAIAC/Cephis group... that it is impossible to mention them all in these lines. I would like to specially thank Ana Alcalde to print part of the devices used in this thesis work. Thanks a lot. Also, I want to thank David Marín to share with me his british working style. I learnt a lot from you. I'm glad that you found your way despite of difficulties. I also want to thank Pilar Orero for her non-british style and to help me know how to deal with my research career.

I want to specially thank my TDK4PE project colleagues: Prof. Henrique Gomes, Prof. Reinhard R. Baumann, Fulvia Villani, Enrico Sowade, Kalyan Yoti Mitra, Adrià Conde, Jofre Pallarès and Francesc Vila for their invaluable cooperation and good harmony during three

hard years of work. It has been an honour to learn from you. We produced outstanding achievements!

I also want to give my thanks to Mariana Medina and Arben Merkoçi whom I learned to do research. It was a pleasure to collaborate with you.

I owe my sincere gratitude to my adviser, Jordi Carrabina, who recruited me in his research group giving me the possibility to learn from him and to trust in me to develop the new research field of printed Electronics. I am grateful that he gives complete freedom for me to pursue my own research interests. I also want to give my thanks to Lluís Terés to offer me a new and amazing opportunity at IMB-CNM. I hope that we will be able to promote new interesting projects together.

I would not have arrived here without excellent teachers. I want to give my sincere gratitude to Pere Pous who push me to start with research in the secondary school. I also want to thank my first and uncompleted thesis supervisor, Antonio Rubio to offer me the first chance to enter in research.

I leave for the end my brothers and friends. I want to thank my brothers and sister for their patience with me. I know that it is not easy to have a brother like me;).

And finally, I want to thank my old friends, Miquel Essomba, Miquel Àngel Alabart, Gal·la Cortadellas, Muntsa Turon, Ildefons Espina and Nuria Oliver for sharing their lives with me during 25 years (Oh, my God, 25!!). I cannot forget my new friends (just 10 years) Eva, Jordi, Silvia, Nyaco, Imma, Joan and Eulàlia. Thanks for the welcome to Centelles.

# CONTENTS

| 1. | INTRO                                                   | DUCTION                                                                                                                                  | 1                 |

|----|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|    | 1.1. Pri                                                | nted Electronics                                                                                                                         |                   |

|    | 1.1.1.                                                  | Technology benefits                                                                                                                      |                   |

|    | 1.1.2.                                                  | Current challenges and trends                                                                                                            |                   |

|    | 1.1.3.                                                  | Summary                                                                                                                                  |                   |

|    | 1.2. App                                                | plications                                                                                                                               |                   |

|    | 1.2.1.                                                  | RFID tags and smart objects                                                                                                              |                   |

|    | 1.2.2.                                                  | Sensors                                                                                                                                  |                   |

|    | 1.2.3.                                                  | Displays                                                                                                                                 | 9                 |

|    | 1.3. Pri                                                | nting techniques                                                                                                                         | 12                |

|    | 1.4. Sta                                                | te of the art on the development of organic inkjet-printed devices and circuit                                                           | s 14              |

|    | 1.5. Obj                                                | jective of this thesis                                                                                                                   | 17                |

|    | 1.6. The                                                | esis organization                                                                                                                        | 18                |

| 2. |                                                         | T DEPOSITION OF FUNCTIONAL MATERIALS                                                                                                     |                   |

|    |                                                         | jet technology                                                                                                                           |                   |

|    | 2.1. IIIK<br>2.1.1.                                     | Drop-on-demand technologies                                                                                                              |                   |

|    | 2.1.2.                                                  | Inkjet printing for electronic applications                                                                                              |                   |

|    | 2.1.3.                                                  | Inkjet printer.                                                                                                                          |                   |

|    |                                                         | nted features characterization and extraction                                                                                            |                   |

|    | 2.2. Fri                                                | Inkjet printing considerations                                                                                                           |                   |

|    | 2.2.2.                                                  | Technology Characterization Methodology                                                                                                  |                   |

|    | 2.2.3.                                                  | Material characterization                                                                                                                |                   |

|    | 2.2.4.                                                  | Experimental for material deposition optimization                                                                                        |                   |

|    | 2.2.5.                                                  | Compensation techniques for improving printed structures                                                                                 |                   |

|    | 2.3 Coc                                                 | ometric design rule extraction                                                                                                           |                   |

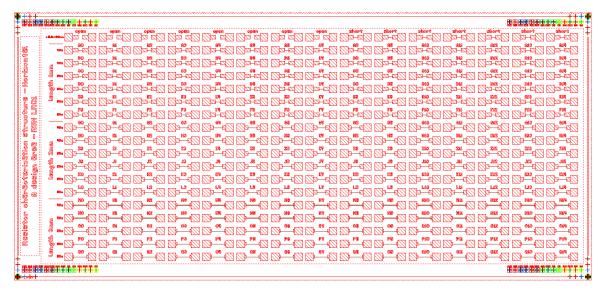

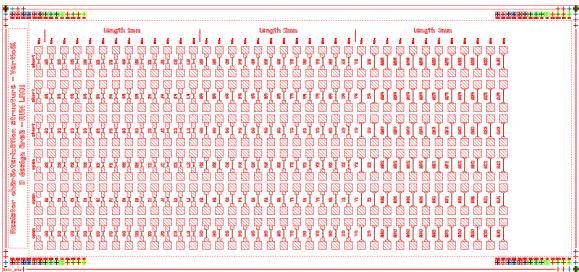

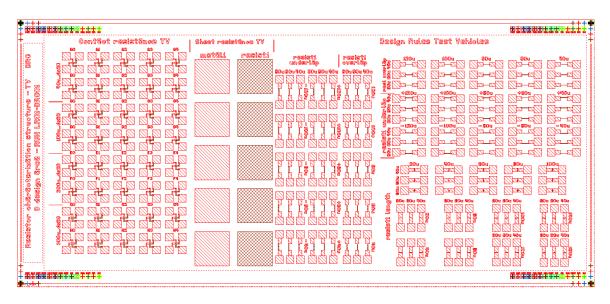

|    | 2.3.1.                                                  | Design Rules Characterization Structure                                                                                                  | 44                |

|    | 2.3.2.                                                  | Automation of Design Rule Extraction                                                                                                     |                   |

|    | 9.4 Tos                                                 | st mask for pattern and overlay parameters in inkjet printing                                                                            |                   |

|    | 2.4.1.                                                  | Alignment marks for inkjet printing                                                                                                      | 50                |

|    | 2.4.2.                                                  | Test mask for pattern and overlay parameters                                                                                             |                   |

|    | 9.5 Sur                                                 | nmary and conclusions                                                                                                                    |                   |

|    |                                                         |                                                                                                                                          |                   |

| 3. |                                                         | OPMENT OF ELEMENTARY DEVICES                                                                                                             |                   |

|    |                                                         | nductive lines                                                                                                                           |                   |

|    | 3.1.1.<br>3.1.2.                                        | Morphological characterization                                                                                                           |                   |

|    |                                                         | •                                                                                                                                        |                   |

|    | 3.2. Res                                                | sistors                                                                                                                                  |                   |

|    | 3.2.1. $3.2.2.$                                         | Inorganic resistors                                                                                                                      |                   |

|    | 3.2.3.                                                  | Inorganic resistor reliability, scalability and variability                                                                              |                   |

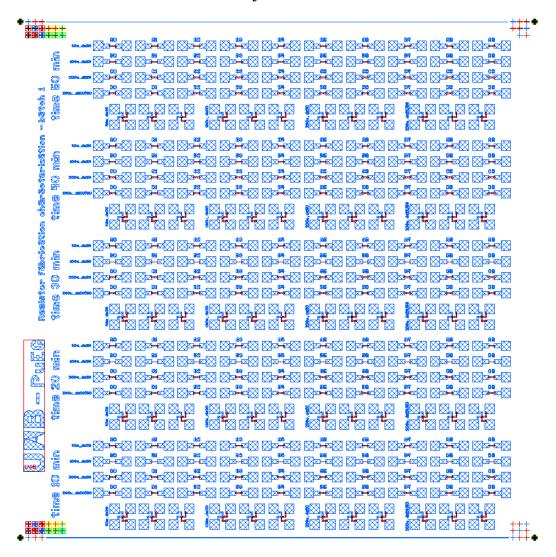

|    | 3.2.3.                                                  | Large-scale fabrication of linear resistors                                                                                              |                   |

|    | 0.4.4.                                                  | Daife scale institution of fillent resistors                                                                                             |                   |

|    | 325                                                     | Largo-scale fabrication of english resistors                                                                                             | 77                |

|    | 3.2.5.<br>3.2.6                                         | Large-scale fabrication of snake resistors  Inorganic resistor-based WORM memories                                                       |                   |

|    | 3.2.6.                                                  | Inorganic resistor-based WORM memories                                                                                                   | 79                |

|    | 3.2.6.<br>3.2.7.                                        | Inorganic resistor-based WORM memories Organic resistors                                                                                 | 79<br>82          |

|    | 3.2.6.<br>3.2.7.<br><b>3.3.</b> Car                     | Inorganic resistor-based WORM memories Organic resistors                                                                                 | 79<br>82          |

|    | 3.2.6.<br>3.2.7.<br><b>3.3.</b> Cap<br>3.3.1.           | Inorganic resistor-based WORM memories Organic resistors  pacitors  Metal-Insulator-Metal (MIM) fabrication                              | 799292            |

|    | 3.2.6.<br>3.2.7.<br><b>3.3. Cap</b><br>3.3.1.<br>3.3.2. | Inorganic resistor-based WORM memories Organic resistors  pacitors  Metal-Insulator-Metal (MIM) fabrication  Electrical characterization | 79 <b>92</b> 9292 |

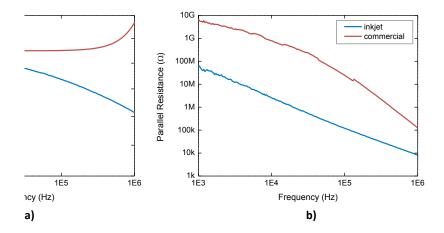

|    | 3.2.6.<br>3.2.7.<br><b>3.3.</b> Cap<br>3.3.1.           | Inorganic resistor-based WORM memories Organic resistors  pacitors  Metal-Insulator-Metal (MIM) fabrication                              | 7992929797        |

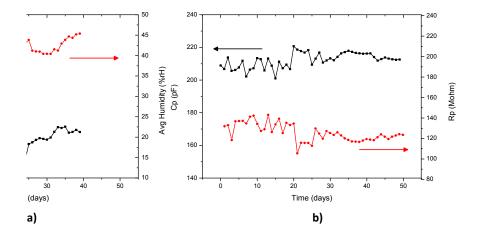

|          | 3.3.6               | . Reliability study of c-PVP MIM capacitors                                     | 105                 |

|----------|---------------------|---------------------------------------------------------------------------------|---------------------|

|          |                     | ircuits using passive devices                                                   |                     |

|          | 3.4.1               |                                                                                 |                     |

|          |                     | ummary and conclusions                                                          |                     |

| 4.       |                     | ICATION OF INKJET-PRINTED ORGANIC THIN FILM TRANSISTORS                         |                     |

|          |                     | ntroduction                                                                     |                     |

|          |                     | TFT Operation and characteristics                                               |                     |

|          | 4.2.1               |                                                                                 |                     |

|          | 4.2.2 $4.2.3$       |                                                                                 |                     |

|          | 4.2.3 $4.2.4$       |                                                                                 |                     |

|          |                     |                                                                                 |                     |

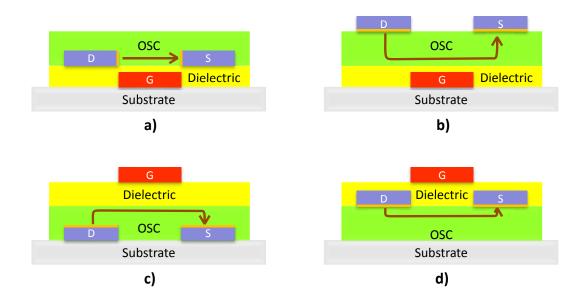

|          | 4.3. F              | abrication of all-Inkjet Printed Organic Thin Film Transistors  OTFT Structures | . <b>125</b><br>125 |

|          | 4.3.2               |                                                                                 |                     |

|          | 4.3.3               |                                                                                 |                     |

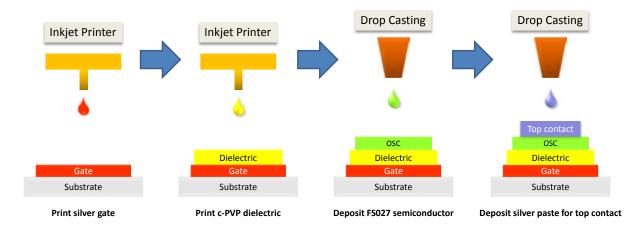

|          | 4.4. M              | anufacturing Process Description of all-inkjet Printed OTFTs                    | . 135               |

|          | 4.4.1               |                                                                                 | 135                 |

|          | 4.4.2               | · · · · · · · · · · · · · · · · · · ·                                           |                     |

|          | 4.4.3               |                                                                                 |                     |

|          | 4.4.4               |                                                                                 |                     |

|          | 4.4.5               |                                                                                 |                     |

|          | 4.4.6               |                                                                                 |                     |

|          |                     | ummary and conclusions                                                          |                     |

| 5.       |                     | RACTERIZATION OF INKJET-PRINTED ORGANIC THIN FILM TRANSISTORS                   |                     |

|          |                     | ntroduction to OTFT electrical characterization                                 |                     |

|          | 5.1.1 $5.1.2$       |                                                                                 |                     |

|          |                     |                                                                                 |                     |

|          | <b>5.2.</b> P 5.2.1 | reliminary Organic Semiconductor Characterization                               | . <b>164</b><br>167 |

|          |                     | lectrical characterization of all-inkjet fabricated OTFTs                       |                     |

|          | 5.3.1               | ·                                                                               |                     |

|          | 5.3.2               |                                                                                 |                     |

|          | 5.3.3               | ·                                                                               |                     |

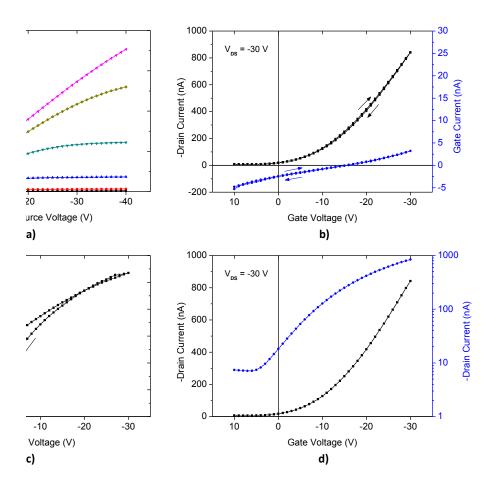

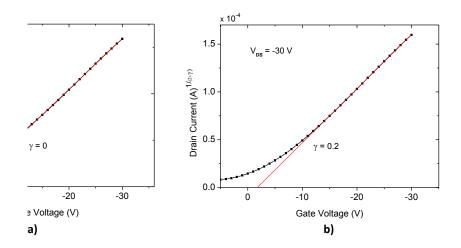

|          | 5.3.4               | . All-inkjet OTFTs preliminary electrical characterization results              | 178                 |

|          | 5.4. S              | tability of OTFTs under bending strain                                          | . 182               |

|          | 5.5. O              | perational Stability and Reliability of all-inkjet OTFTs                        | . 184               |

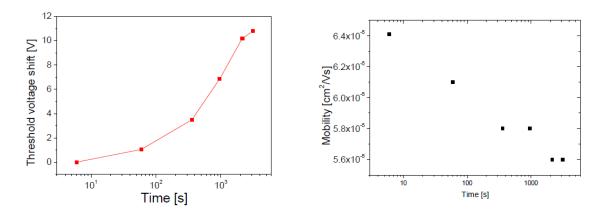

|          | 5.5.1               | OTFT stability over time                                                        | 184                 |

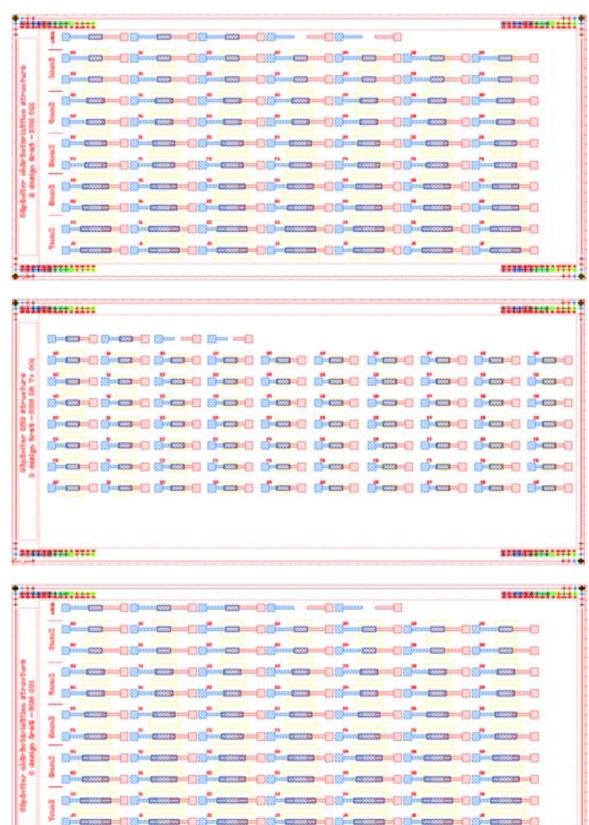

|          | 5.6. L              | arge-scale characterization of inkjet-printed OTFTs                             |                     |

|          | 5.6.1               | J. I                                                                            |                     |

|          | 5.6.2               |                                                                                 |                     |

|          | 5.6.3               | •                                                                               |                     |

|          | 5.7. S              | ummary and conclusions                                                          | . 200               |

| 6.<br>T] |                     | TEGIES FOR THE IMPROVEMENT OF INKJET PRINTED ORGANIC THIN FILM TORS             | 203                 |

|          | 6.1. O              | TFT Encapsulation Strategies                                                    |                     |

|          | 6.1.1               |                                                                                 |                     |

|          | 6.1.2               |                                                                                 |                     |

|          |                     | nprovement of functional layers deposition                                      |                     |

|          | 6.2.1 $6.2.2$       |                                                                                 |                     |

|          |                     |                                                                                 |                     |

|          | <b>6.3.</b> O       | ptimization of OTFTs by design                                                  |                     |

|          | 639                 |                                                                                 | 214<br>218          |

|    | 6.            | 3.3. | Non-overlapped gate OTFTs                                            | 222 |

|----|---------------|------|----------------------------------------------------------------------|-----|

|    | 6.4.          | Sui  | nmary and conclusions                                                | 227 |

| 7. | $\mathbf{AL}$ | L-IN | KJET CIRCUITS AND SYSTEMS                                            | 229 |

|    |               |      | roduction to Logic Circuits                                          |     |

|    |               |      | Basic circuits concepts                                              |     |

|    | 7.2.          | Cir  | cuit characterization                                                | 232 |

|    | 7.3.          | All  | inkjet printed Inverter                                              | 233 |

|    | 7.            | 3.1. | Proposed circuit structure                                           |     |

|    | 7.            | 3.2. | All-inkjet inverter fabrication                                      | 234 |

|    | 7.            | 3.3. | DC analysis                                                          | 234 |

|    | 7.            | 3.4. | Dynamic analysis                                                     | 239 |

|    | 7.            | 3.5. | All-inkjet NAND2 circuit                                             | 241 |

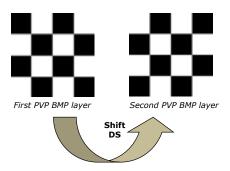

|    | 7.4.          | An   | inkjet adaptive backend strategy for low-yield OTFT digital circuits | 243 |

|    | 7.            | 4.1. | Configurable OTFTs                                                   |     |

|    | 7.            | 4.2. | Standard-cell logic circuits using configurable OTFTs                | 247 |

|    | 7.5.          | Sui  | nmary and conclusions                                                | 252 |

| 8. | CO            | NCI  | USIONS AND FUTURE WORK                                               | 253 |

|    | 8.1.          | Ov   | erview and General Conclusions                                       | 253 |

|    | 8.2.          |      | en Issues and Future Work                                            |     |

| A  | NNEX          | KES. |                                                                      | 259 |

|    | Anne          | ex A | . References                                                         | 260 |

|    | Ann           | ex B | . Author relevant publications                                       | 270 |

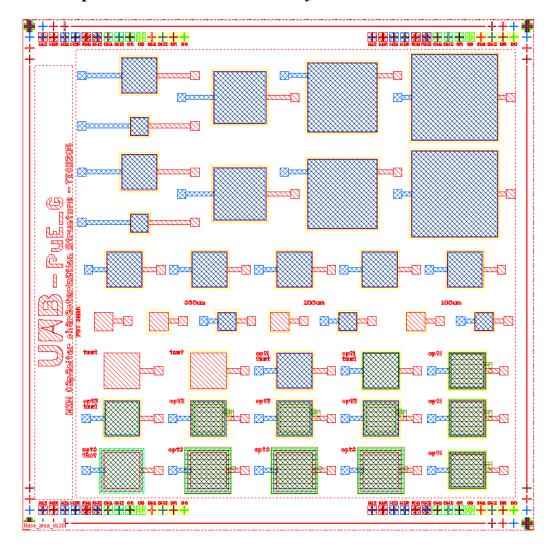

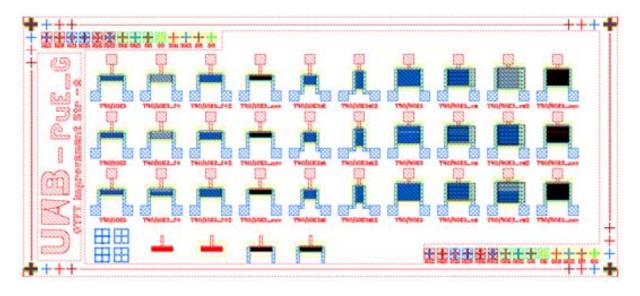

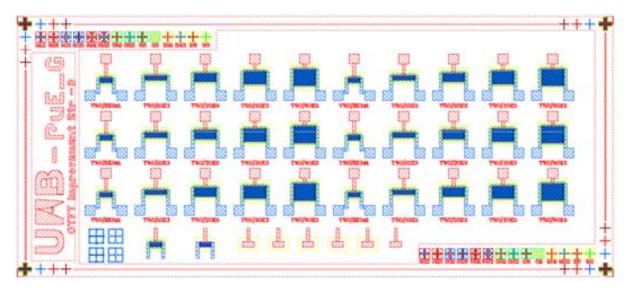

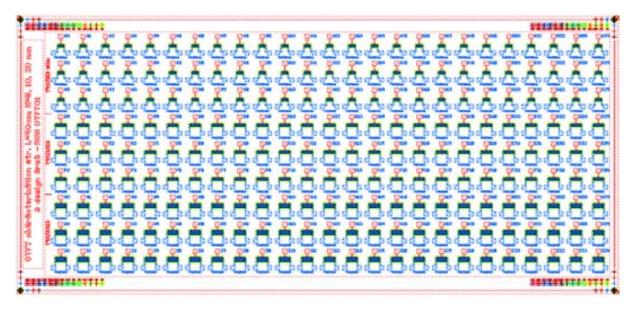

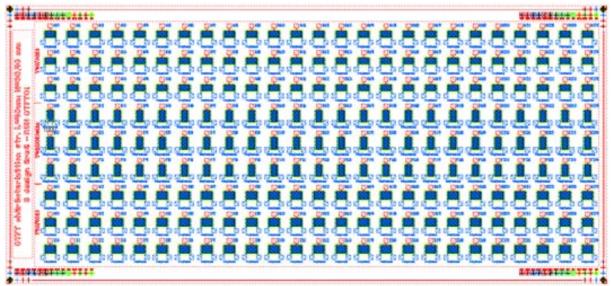

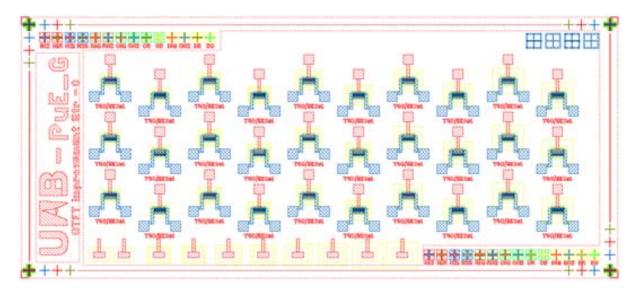

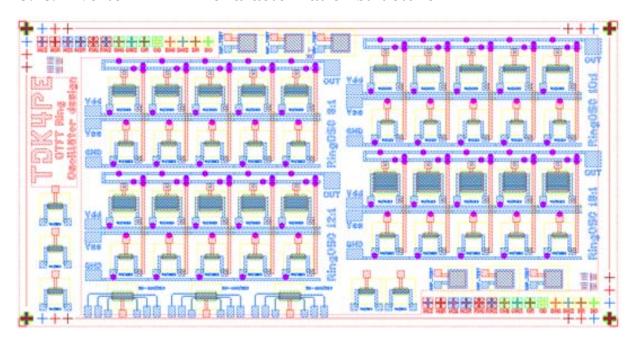

|    |               |      | . Layouts                                                            |     |

|    |               |      | . DuPont Teijin Teonex® Q65FA specifications                         |     |

|    |               |      | OTFT printing recipe                                                 |     |

## LIST OF ACRONYMS

AC Alternating Current

AFM Atomic Force Microscope

AMEPD Active Matrix Electrophoretic Display

AMOLED Active Matrix Organic Light-Emitting Diode

AMTFT Active Matrix Thin Film Transistor

a-Si Amorphous Silicon

BG-BC Bottom Gate – Bottom Contact

BG-TC Bottom Gate - Top Contact

BioFET Bio-Field Effect Transistor

B&W Black&White (monochrome)

CAD Computer Aided Design

CLK Clock

CMOS Complementary Metal-Oxide-Semiconductor

CPD Counter Printing Direction

CSL Current-Source Load

C-PVP Crosslinked Poly(4-vinylphenol)

C-V capacitance-voltage

D Drain electrode

DC Direct Current

DL Diode Load

**DMP** Dimatix Material Printer

DOD Drop-On-DemandDS Drop Spacing

EL Electro Luminescent

EPD Electrophoretic Display

**EU** European Union

FET Field-Effect Transistor

FIB Focus Ion Beam

FlexNet Network of Excellence for the Exploitation of Flexible, Organic and Large Area

Electronics

FOLAE Flexible, Organic and Large Area Electronics

G Gate electrode

HF High Frequency

**HOMO** Highest Occupied Molecular Orbital

IC Integrated Circuit

ITO Indium Tin Oxide

KGO Known Good OTFT

LCD Liquid Crystal Display

LUMO Lowest Unoccupied Molecular Orbital

MEMS Micro-Electromechanical Systems

MIM Metal-Insulator-Metal

MIS Metal-Insulator-Semiconductor

MISFET Metal-Insulator-Semiconductor Field-Effect Transistor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MTR Multiple Trapping and Release

nMOS n-type Metal Oxide Semiconductor

NP Nano Particles

OE Organic Electronics

OE-A Organic Electronics Association

OFET Organic Field Effect Transistor

OLED Organic Light-Emitting Diode

OPC Optical Proximity effect Correction

OPV Organic Photovoltaics

OSC Organic Semiconductor

OTFT Organic Thin Film Transistor

PCB Printed Circuit Board

PD Printing Direction

**PEDOT:PSS** Poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate)

PEN Polyethylene Naphthalate

PET Polyethylene Terephthalate

PFTP Pentafluorothiophenol

PMMA polymethyl-methacrylate

pMOS p-type Metal Oxide Semiconductor

PSC Pattern Shape Correction

PTFE Polytetrafluoroethylene

PVA Polyvinylalcohol

PVP Poly(4-vinylphenol)

PZT Piezoelectric Transducer

P3HT Poly (3-hexyl thiophene)

RC Resistance-Capacitance

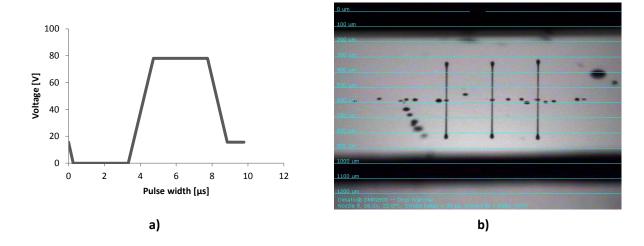

RES Rapid Electrical Sintering

**RET** Resolution Enhancement Techniques

RF Radio Frequency

RFID Radio Frequency Identification

RL Resistor Load

R2R Roll-to-Roll

Source electrode

SAM Self-Assembled Monolayer

SEM Scanning Electron Microscope

SiO<sub>2</sub> Silicon Dioxide S2S Sheet-to-Sheet

TDK4PE Technology & Design Kit for Printed Electronics

**TFT** Thin-Film Transistor

TG-BC Top Gate - Bottom Contact

**TG-TC** Top Gate - Top Contact

TIPS 6,13-Bis(triisopropylsilylethynyl)

**UPC** Universal Product Code

**VOFET** Vertical Organic Field-Effect Transistor

VRH Variable Range Hopping

VTC Voltage Transfer Curve

WID Within- or Intra-die

WORM Write-Once-Read-Many

# LIST OF SYMBOLS

| Symbol                            | Description                                | Units             |

|-----------------------------------|--------------------------------------------|-------------------|

| $\mathbf{C}$                      | Capacitance                                | $\mathbf{F}$      |

| $C_i$                             | Capacitance per unit area of the insulator | F/cm <sup>2</sup> |

| $\mathbf{C}_{\mathbf{insulator}}$ | Insulator Capacitor                        | F                 |

| $C_p$                             | Parallel Capacitance                       | F                 |

| CTE                               | Coefficient of Thermal Expansion           | $\mathbf{K}^{-1}$ |

| d                                 | Thickness                                  | m                 |

| $\mathbf{E}_{\mathbf{G}}$         | Band-gap Energy                            | eV                |

| GND                               | Ground                                     | V                 |

| $I_{DS}$                          | Drain-Source Current                       | A                 |

| $\mathbf{I}_{\mathbf{G}}$         | Gate Current                               | A                 |

| $\mathbf{I}_{	ext{leak}}$         | Leakage Current                            | A                 |

| $\mathbf{I}_{\mathbf{OFF}}$       | Off-current (drain)                        | A                 |

| $I_{ON}$                          | On-current (drain)                         | A                 |

| $I_{\rm ON}/I_{\rm OFF}$          | On/Off Drain Current ratio                 | -                 |

| $IP_s$                            | Semiconductor Ionization Potential         | eV                |

| ${f L}$                           | Channel Length                             | μm                |

| R                                 | Resistance                                 | ohm               |

| R                                 | Bending radius                             | mm                |

| $\mathbf{R}_{\mathbf{B}}$         | Bit resistance                             | ohm               |

| $R_c$                             | Contact Resistance (Resistors)             | $ohm/\mu m^2$     |

| $\mathbf{R_c}$                    | Contact Resistance (OTFTs)                 | ohm/cm            |

| $R_p$                             | Parallel Resistance                        | ohm               |

| RVC                               | Resistor Voltage Coefficient               | ppm/V             |

| $\mathbf{R}_{\square}$            | Sheet Resistance                           | ohm/□             |

| $\mathbf{S}$                      | Spreading (ink fluid)                      | -                 |

| $\mathbf{S}$                      | Strain (bending)                           | %                 |

| $\mathbf{S}$                      | Subthreshold Slope (OTFTs)                 | V/dec             |

| T                                 | Relaxation Time                            | sec               |

| $\mathbf{T_f}$                    | Falling Time                               | sec               |

| $\mathbf{T_r}$                      | Rise Time                                        | sec                  |

|-------------------------------------|--------------------------------------------------|----------------------|

| $T_{\rm pHL}$                       | Falling Propagation Delay                        | sec                  |

| $T_{\mathrm{pLH}}$                  | Rising Propagation Delay                         | sec                  |

| $\mathbf{V}_{\mathbf{D}\mathbf{D}}$ | Supply Voltage                                   | V                    |

| $\mathbf{V_{DS}}$                   | Drain-Source Voltage                             | V                    |

| $\mathbf{V}_{\mathbf{G}}$           | Gate Voltage                                     | V                    |

| $\mathbf{V}_{\mathbf{GS}}$          | Gate-Source Voltage                              | V                    |

| $\mathbf{V}_{\mathbf{IH}}$          | Input High Voltage                               | V                    |

| $\mathbf{V}_{\mathbf{IL}}$          | Input Low Voltage                                | V                    |

| $V_{\rm in}$                        | Input Voltage                                    | V                    |

| $\mathbf{V}_{\mathrm{OH}}$          | Output High Voltage                              | V                    |

| $V_{\mathrm{OL}}$                   | Output Low Voltage                               | V                    |

| $\mathbf{V}_{\mathbf{out}}$         | Output Voltage                                   | V                    |

| VNMH                                | High-state Noise Margin Voltage                  | V                    |

| VNML                                | Low-state Noise Margin Voltage                   | V                    |

| $\mathbf{V}_{\mathbf{SS}}$          | Source Supply Voltage                            | V                    |

| $\mathbf{V}_{\mathbf{T}}$           | Threshold Voltage                                | V                    |

| $\mathbf{W}$                        | Channel Width                                    | μm                   |

| $\Delta V_{T}$                      | Threshold Voltage shift                          | V                    |

| $\epsilon_{ m r}$                   | Relative Permittivity of the material            | F/m                  |

| $\epsilon_{\rm o}$                  | Vacuum Permittivity (8.85·10 <sup>-12</sup> F/m) | F/m                  |

| γ                                   | Gamma Parameter                                  | -                    |

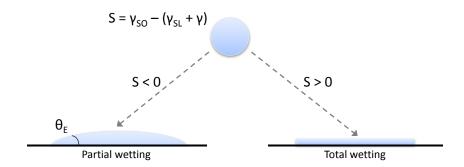

| Yso                                 | Substrate Surface Energy                         | N/m                  |

| Y                                   | Ink Surface Tension                              | N/m                  |

| YSL                                 | Solid-liquid Interaction                         | N/m                  |

| $	heta_{ m E}$                      | Equilibrium Contact Angle                        | degree               |

| μ, μfε                              | Mobility                                         | cm <sup>2</sup> /V•s |

| $\Phi_{\mathrm{M}}$                 | Electrode Work Function                          | $\mathrm{eV}$        |

| $\phi_{\mathrm{B}}$                 | Hole Injection Barrier                           | $\mathrm{eV}$        |

|                                     |                                                  |                      |

# LIST OF FIGURES

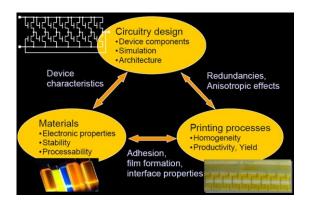

| Figure 1.1. The Printed Electronics equation.                                                                                                                                                                                                                                     | 5         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

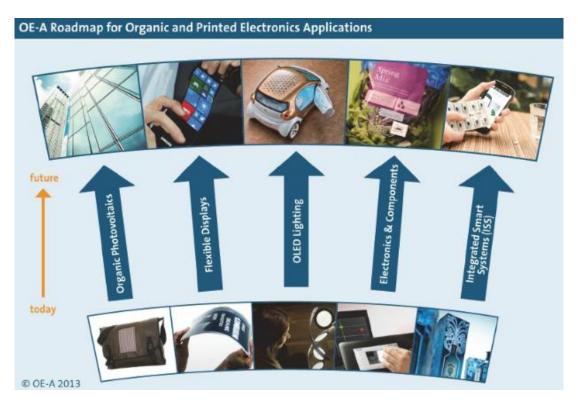

| Figure 1.2. Roadmap for Organic and Printed Electronics Applications [10].                                                                                                                                                                                                        | 6         |

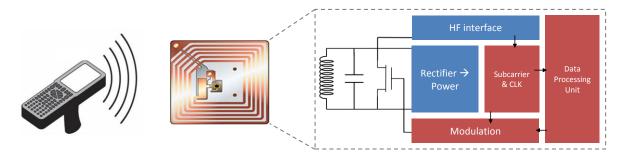

| Figure 1.3. A basic RFID system comprising a reader and a passive tag.                                                                                                                                                                                                            | 7         |

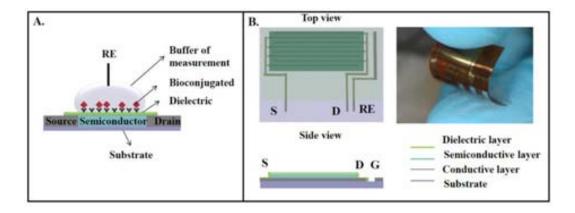

| Figure 1.4. a) Scheme of BioFET components; b) top and side views representing each layer of the BioFET and c) picture of the flexible printed device [17]                                                                                                                        | -         |

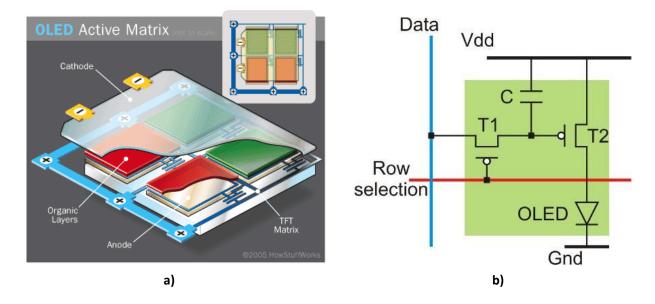

| Figure 1.5. a) In an active-matrix OLED, cathode, organic EL and anode layers are stacked above a low-temperature polysilicon substrate layer that contains a thin-film transistor (TFT circuitry); and b) the schematic layout of a 2T1C pixel driver for AMOLED backplanes [19] | 9         |

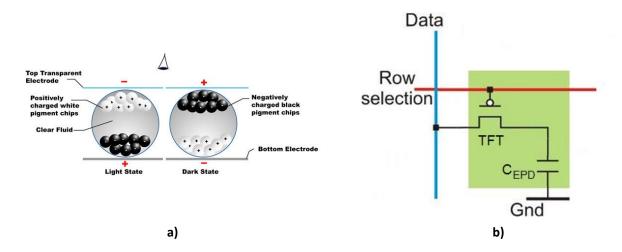

| Figure 1.6. a) Electrophoretic display; and b) Schematic diagram of an AMEPD pixel                                                                                                                                                                                                | . 10      |

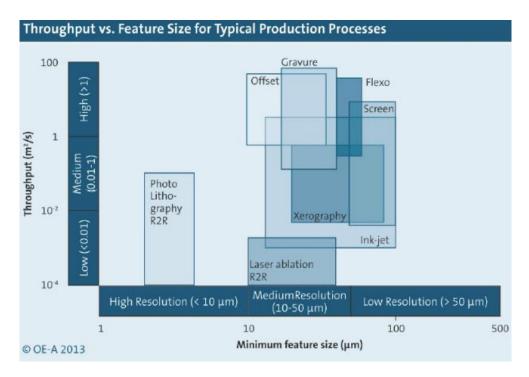

| Figure 1.7. Resolution and throughput for a variety of processes [10]                                                                                                                                                                                                             |           |

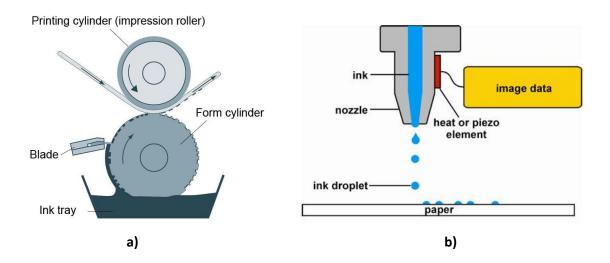

| Figure 1.8. a) Principle of gravure printing; and b) Inkjet printing system.                                                                                                                                                                                                      | . 13      |

| Figure 2.1. Inkjet printing electronics process.                                                                                                                                                                                                                                  | . 20      |

| Figure 2.2. Inkjet versus photolithography process <sup>6</sup>                                                                                                                                                                                                                   | . 20      |

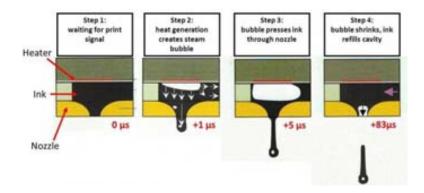

| Figure 2.3. Schematic diagram of a thermal-bubble type inkjet nozzle.                                                                                                                                                                                                             | . 22      |

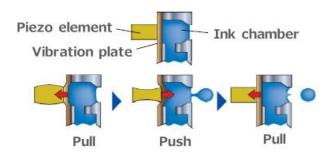

| Figure 2.4. DOD inkjet piezoelectric nozzle ejection process.                                                                                                                                                                                                                     | . 22      |

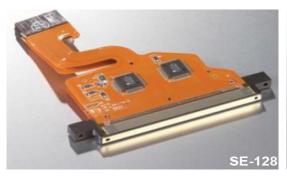

| Figure 2.5. DOD inkjet printheads.                                                                                                                                                                                                                                                | . 23      |

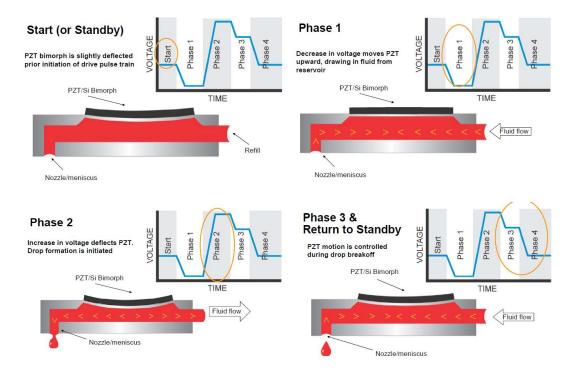

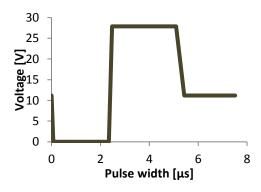

| Figure 2.6. Diagram of a piezoelectric chamber showing the 4 phases of the jetting waveform and the corresponding PZT deflection [82]                                                                                                                                             | . 24      |

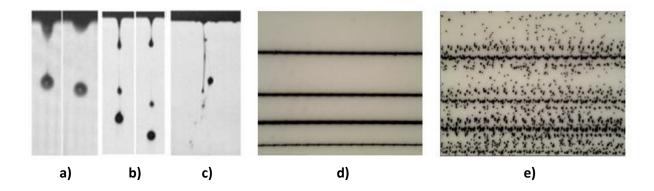

| Figure 2.7. a) Correct jetting drops; b) drops with satellites; c) random spray jetting; d) optimum jetting printed line; and e) satellites effects on a printed line                                                                                                             | . 25      |

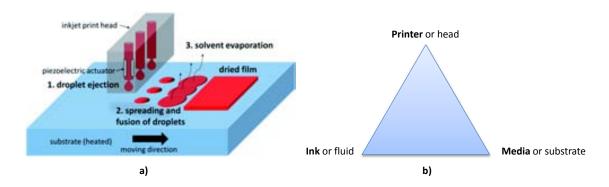

| Figure 2.8. a) Inkjet printing process [84]; and b) the printing "system" [9].                                                                                                                                                                                                    | . 26      |

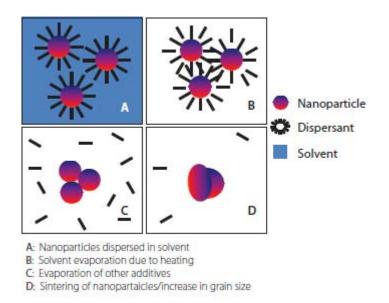

| Figure 2.9. Schematic of a sintering process of nanoparticle inks: A) before heating; B) solvent evaporates and start degradation by heat; C) sintering start; and D) sintering finish [86]                                                                                       |           |

| Figure 2.10. Wetting regimes and equilibrium contact angle                                                                                                                                                                                                                        | . 28      |

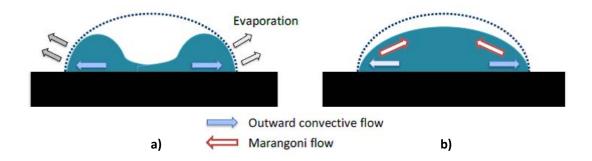

| Figure 2.11. The process of drop drying after deposition with inkjet printing: a) coffee ring formation; b) coffee ring suppressed by Marangoni flow [77]                                                                                                                         | . 29      |

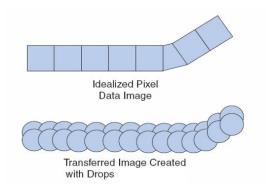

| Figure 2.12. Discrete image formation in digital system.                                                                                                                                                                                                                          | . 30      |

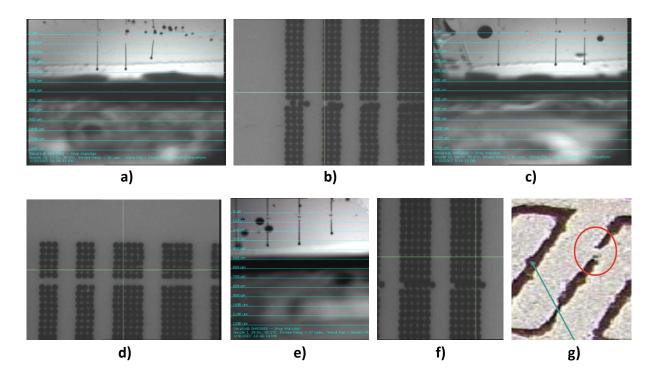

| Figure 2.13. a) Misdirected drops and b) effect on printed pattern; c) non-jetting nozzles and d) effect on printed pattern; e) non-matched velocities; f) and g) effect on printed pattern                                                                                       | . 30      |

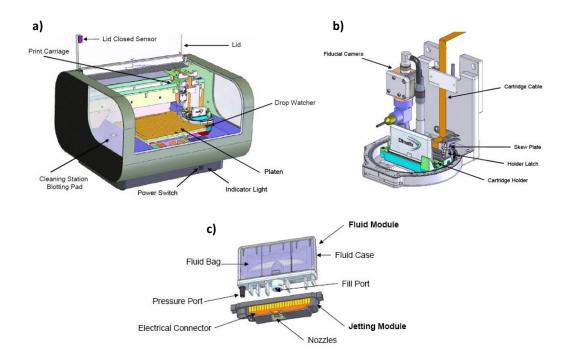

| Figure 2.14. a) Dimatix material printer; b) printer cartridge assembly; and c) printhead and cartridge [82                                                                                                                                                                       | -         |

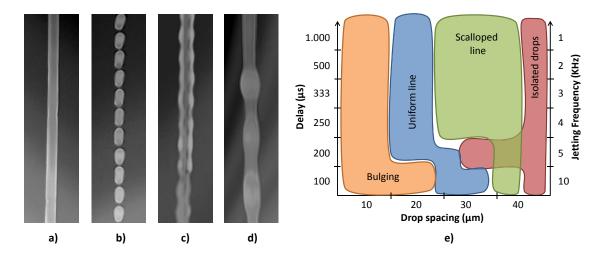

| Figure 2.15. Different printing behaviors.                                                                                                                                                                                                                                        |           |

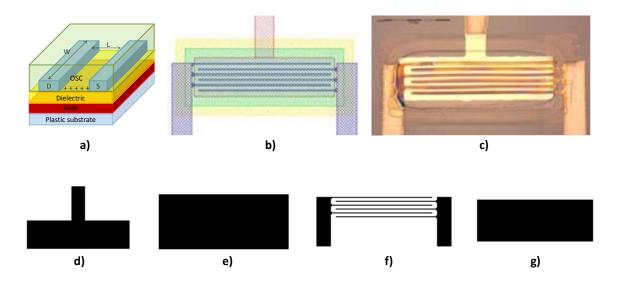

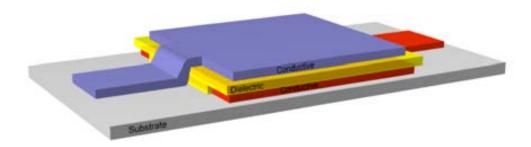

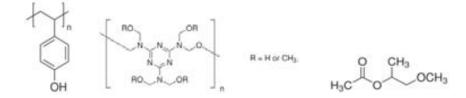

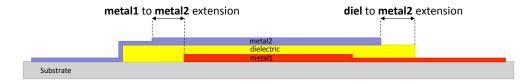

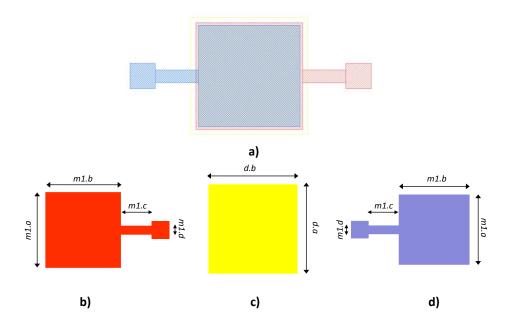

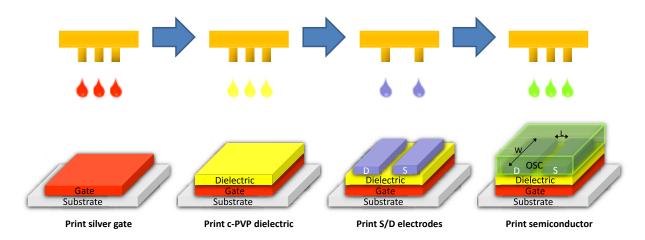

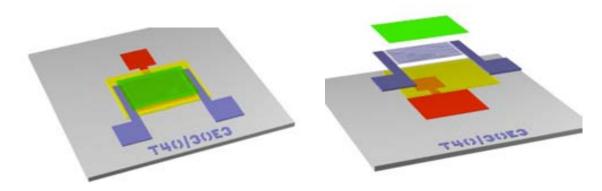

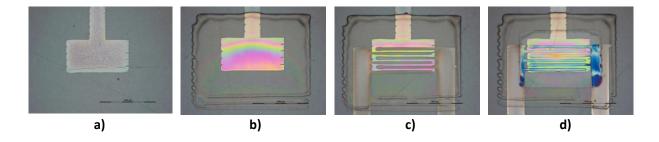

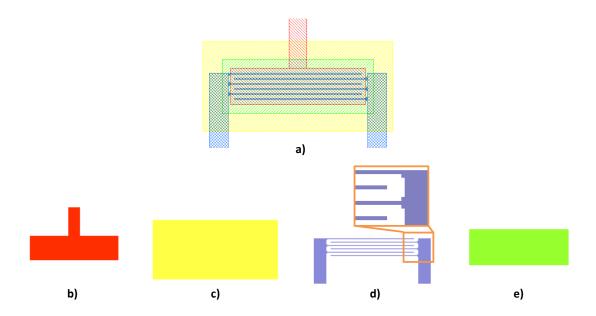

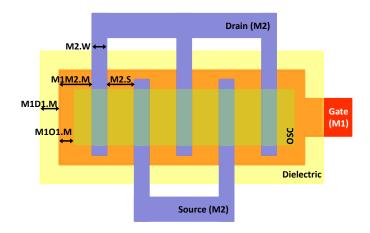

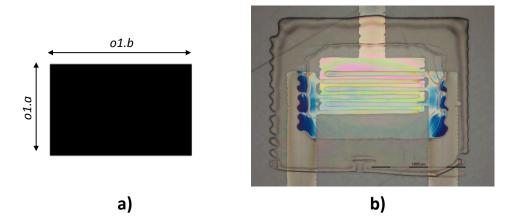

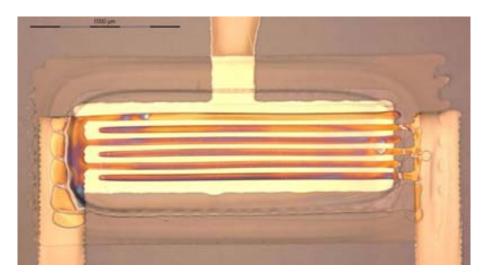

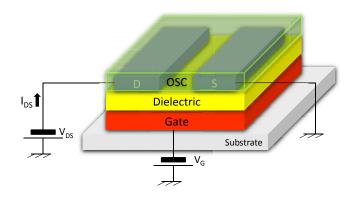

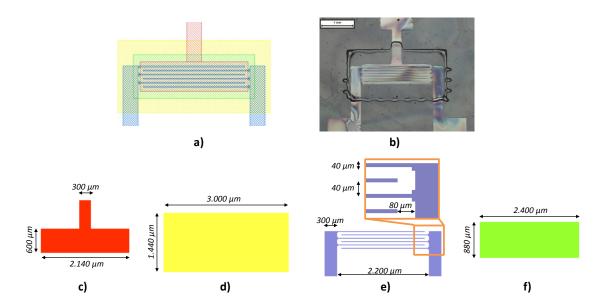

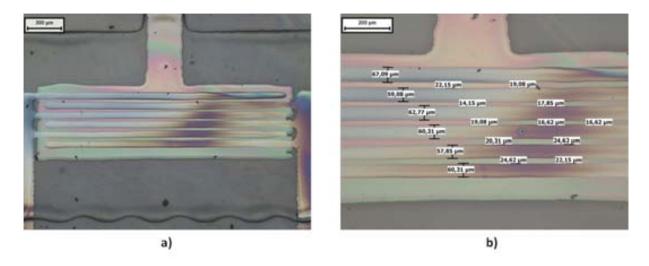

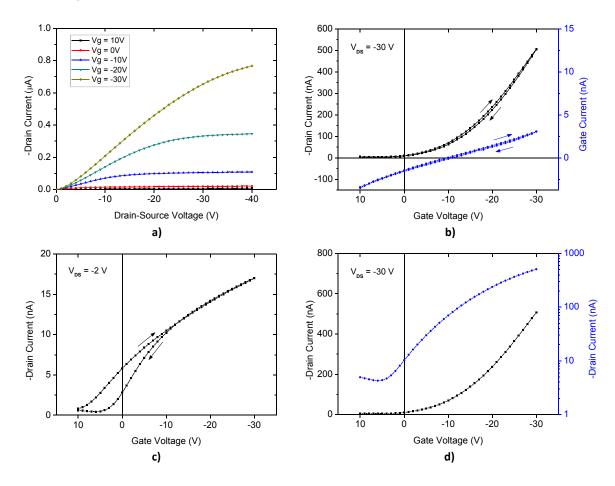

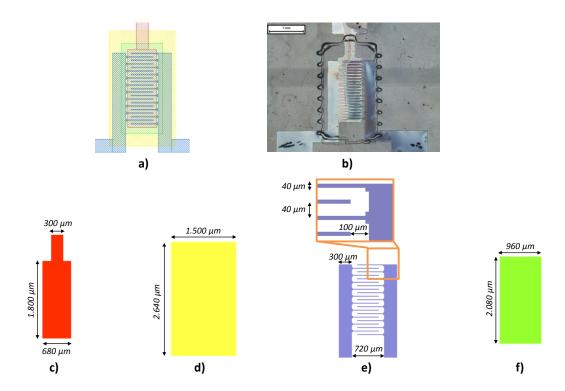

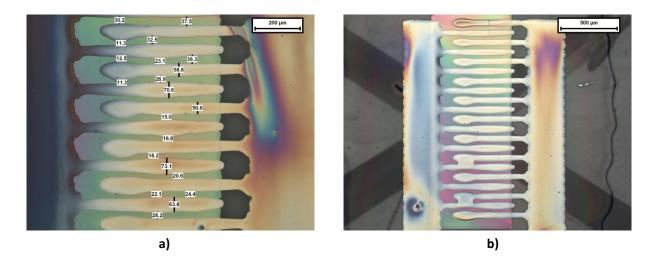

| Figure 2.16. a) OTFT Structure; b) OTFT layout design; c) image of an all-inkjet printed OTFT; d) gate contact layer pattern; e) insulator layer pattern; f) Source/drain layer pattern; and g) semiconductor layer pattern.                                                      |           |

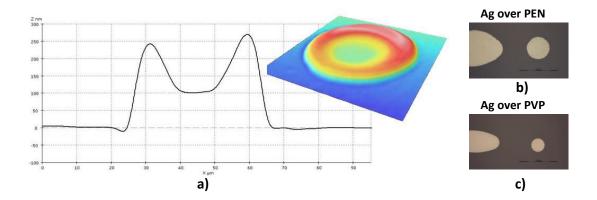

| Figure 2.17. a) 3D and sectional image of a drop with coffee ring; b) silver line and dot over PEN substrate and c) silver line and dot over PVP insulator layer. Images are on the same scale (Note: Measure = 100 μm                                                            | e;<br>n). |

| Figure 2.18. Examples of principal printed line behaviors: a) uniform line; b) isolated drops; c) scalloped; d bulging; and e) typical printed line behavior at intermediate temperature with DS increasing from left to right.                                                   | d)        |

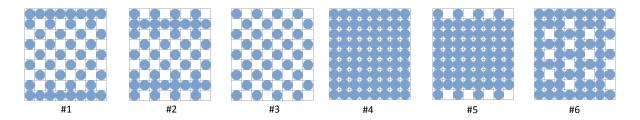

| Figure 2.19. Different drop lattice evaluated. Images represent a portion of a horizontal line                                                                                                                                                                                    |           |

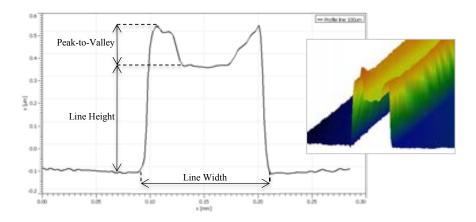

| Figure 2.20. 3D and sectional image of a drop and bead parameters defined.                                                                                                                                                                                                        |           |

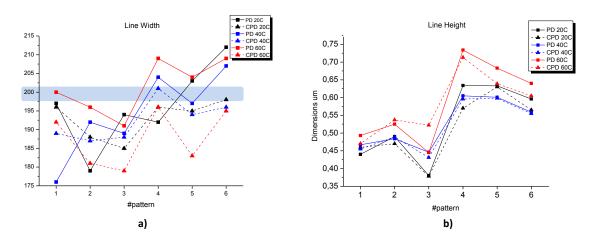

| Figure 2.21. Measured a) line width, and b) line height.                                                                                                                                                                                                                          |           |

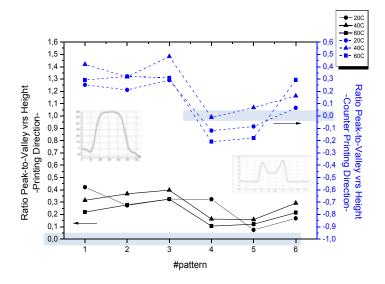

| Figure 2.22. Measured ratio peak-to-valley vs height                                                                                                                                                                                                                              | . 41      |

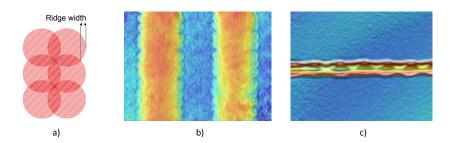

| Figure 2.23. Ridge width effect of scalloped lines.                                                                                                                                                                                                                               | . 41      |

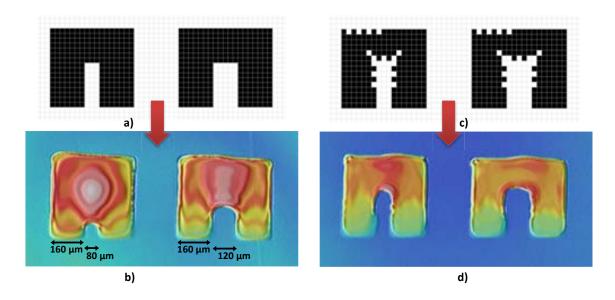

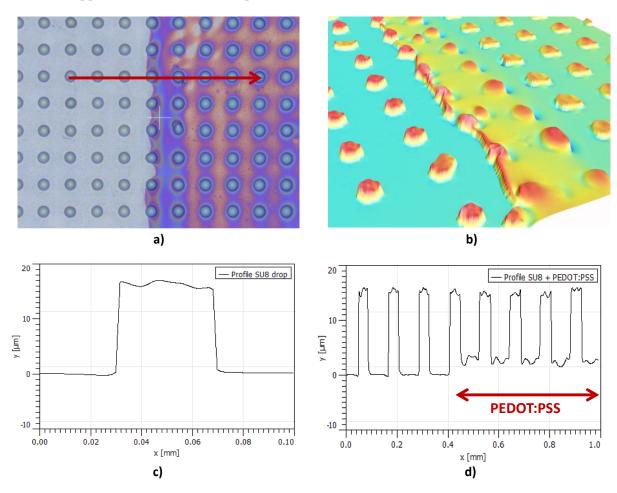

| Figure 2.24. a) Deteriorated printed pattern; and b) Application of a compensation technique                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

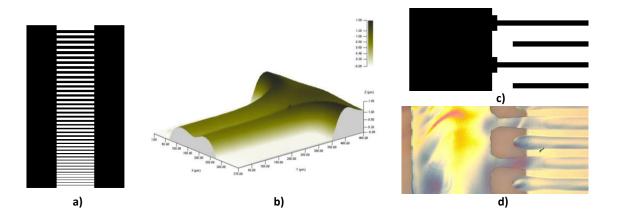

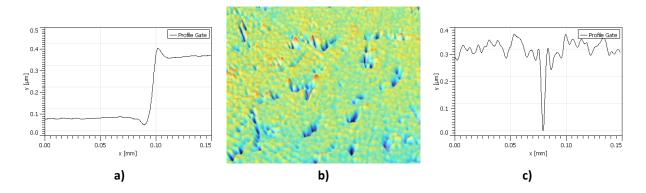

| Figure 2.25. a) Non-compensated notch pattern; b) 3D image of the deposited non-compensated pattern; c) PSC Compensated notch pattern; and d) 3D image for PSC compensated notch rule                                                                                         |

| Figure 2.26. Different compensation strategies evaluated by taking out pixels locally                                                                                                                                                                                         |

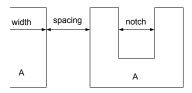

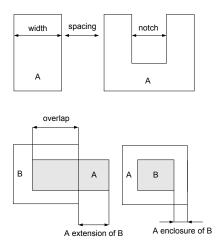

| Figure 2.27. Definition of Basic Geometric Design Rules                                                                                                                                                                                                                       |

| Figure 2.28. Layout of the test structure to characterize the conductive ink on substrate and on insulator.  Note: yellow areas corresponds to insulator layers underneath                                                                                                    |

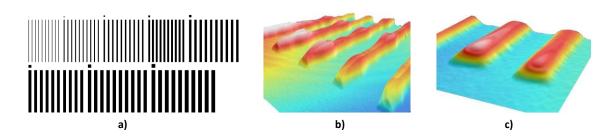

| Figure 2.29. a) Characterization pattern for minimum width rule extraction; b) Non-homogeneous line behavior; and c) homogeneous line behavior                                                                                                                                |

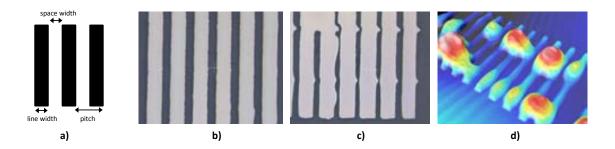

| Figure 2.30. a) Diagram of a line and space pattern; b) Correct spacing; c) printer misalignment; and d) electrical shorts, minimum spacing violated                                                                                                                          |

| Figure 2.31. Left: Test pattern and; right: 3D image for minimum notch rule extraction                                                                                                                                                                                        |

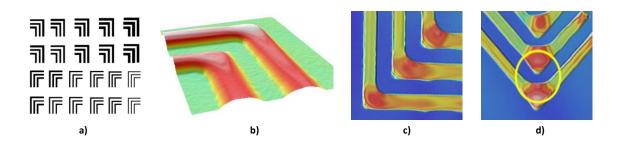

| Figure 2.32. a) Test pattern; b) 3D image of corner patterns; c) corner pattern; and d) corner pattern rotated 45°                                                                                                                                                            |

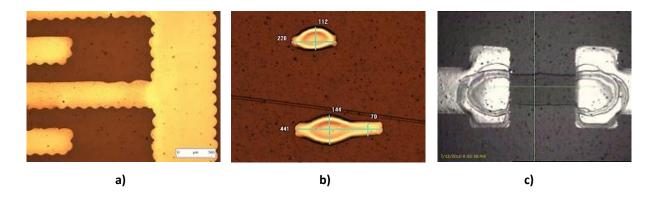

| Figure 2.33. a) Test pattern for junction characterization; b) 3D image of junction; c) layout of Source and Drain electrodes with additive PSC serif-type feature to improve junction; and d) image of printed layout with strangled lines although the compensation applied |

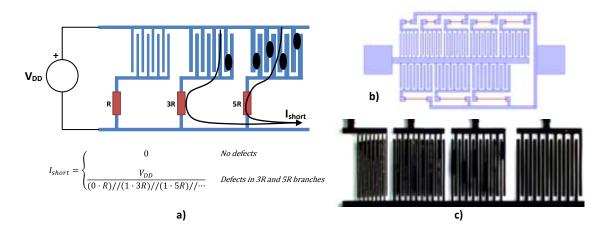

| Figure 2.34. a) Electrical circuit of characterization pattern; b) layout of characterization pattern; and c) printed characterization structure over c-PVP with shorts in smaller spacings                                                                                   |

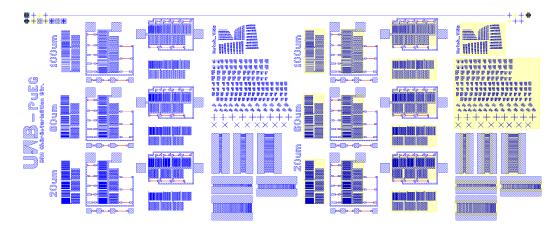

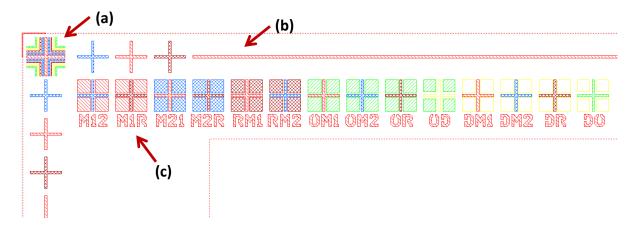

| Figure 2.35. Test and alignment mask designed                                                                                                                                                                                                                                 |

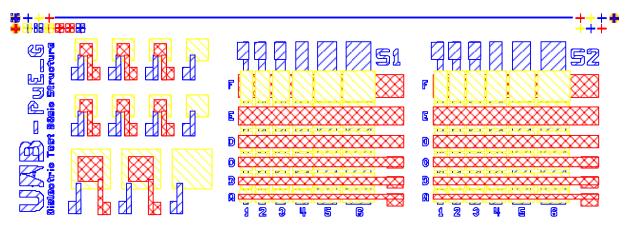

| Figure 2.36. Alignment marks a) between metal1 and dielectric and b) between all the layers: metal1, dielectric, metal 2 and OSC                                                                                                                                              |

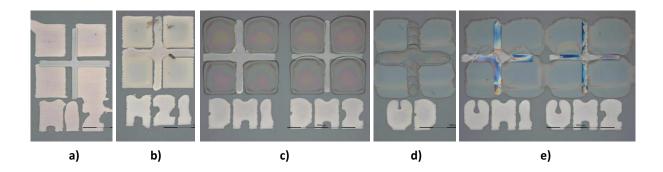

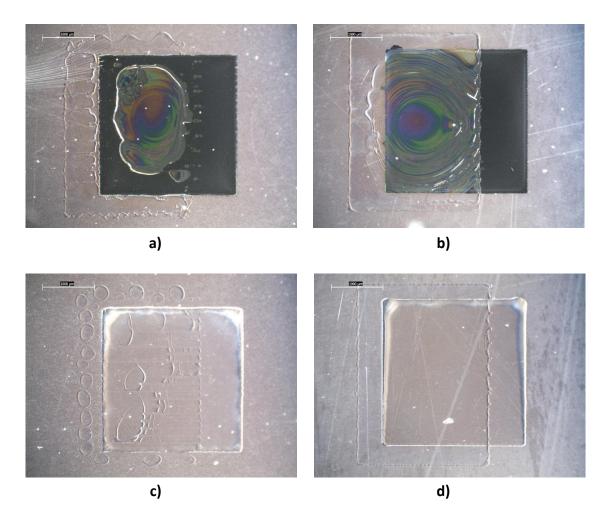

| Figure 2.37. Test masks involving different layers: a) and b) metal1 to metal2; c) dielectric to metal1 and metal2; d) dielectric to OSC and e) OSC to metal1 and metal2 (Note: Bar scale = $1 \text{ mm}$ )                                                                  |

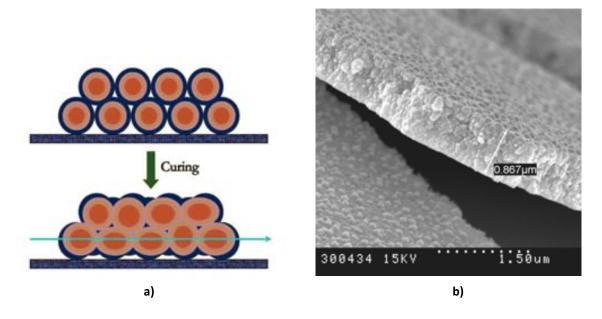

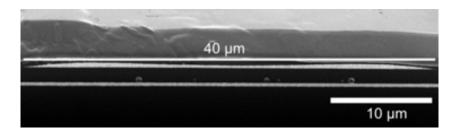

| $Figure \ 3.1. \ a) \ Ink \ curing \ process; \ and \ b) \ SEM \ image \ of \ a \ thin \ film \ using \ silver \ nanoparticle \ ink. \ \ 56$                                                                                                                                  |

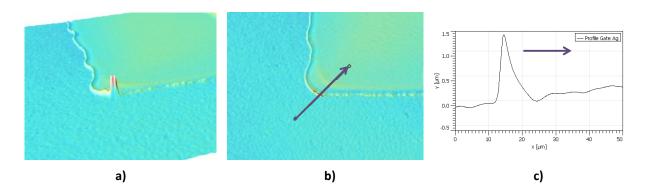

| Figure 3.2. a) Optical image; and b) cross-section of a printed line of Ag nanoparticles on paper obtained by confocal. The average thickness of the silver line was 275 nm                                                                                                   |

| Figure 3.3. a) Optical picture; and b) cross-section of a printed line of Ag nanoparticles on PEN substrate obtained by confocal. The average thickness of the silver line was 450 nm                                                                                         |

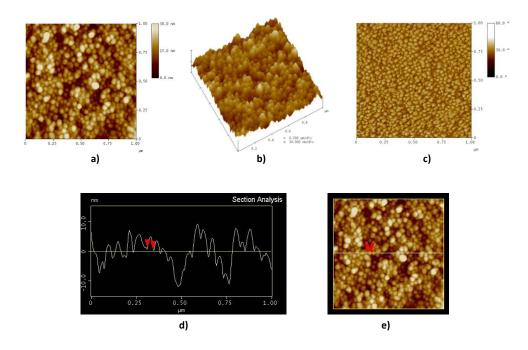

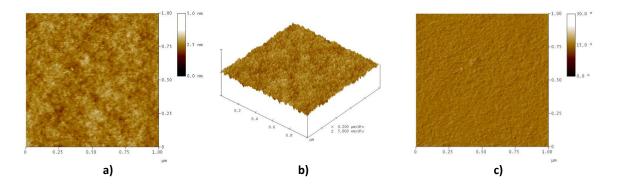

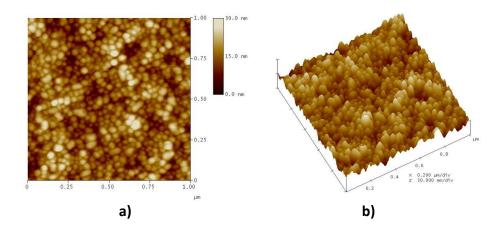

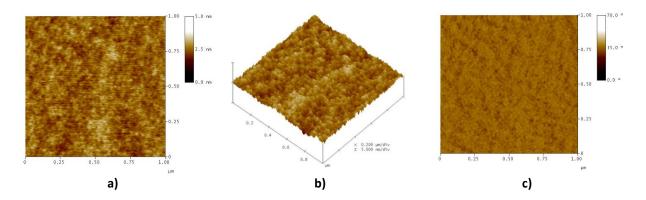

| Figure 3.4. AFM images of silver bottom contact printed on Teonex PEN substrate: a) 2D-height; b) 3D-height; c) 2D-phase; d) and e) section analysis                                                                                                                          |

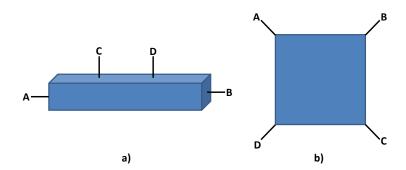

| Figure 3.5. a) Conventional resistivity measurement; and b) typical van der Pauw measurement 59                                                                                                                                                                               |

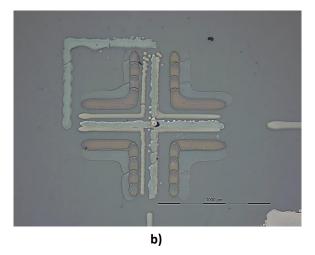

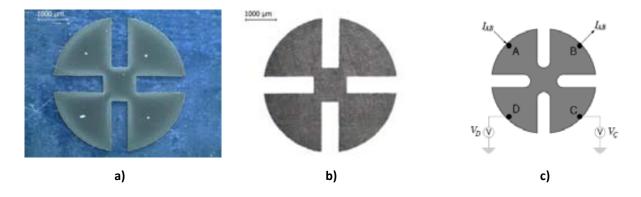

| Figure 3.6. Cloverleaf structure printed by inkjet: a) on PEN substrate, b) on paper substrate, c) cloverleaf characterization setup                                                                                                                                          |

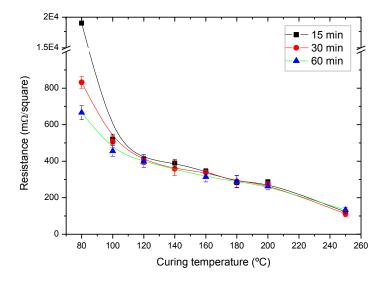

| Figure 3.7. Sheet resistance of inkjet silver-based thin films on a PEN substrate as a function of temperature and curing time.                                                                                                                                               |

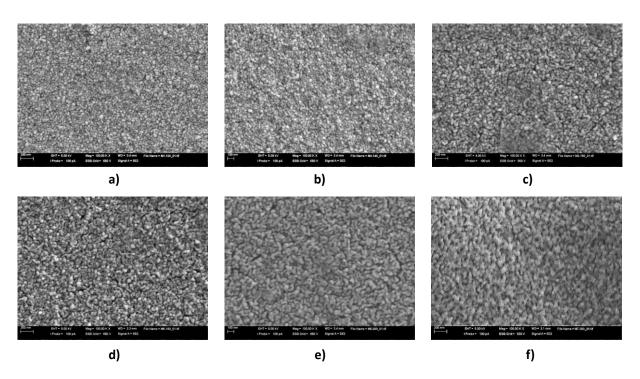

| Figure 3.8. SEM plan view of: a) 120°C, b) 140°C, c) 160°C, d) 180°C, e) 200°C and f) 250°C for 30 min annealed samples                                                                                                                                                       |

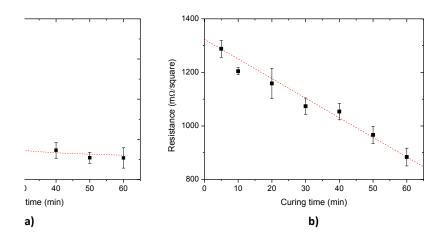

| Figure 3.9. Sheet resistance of the inkjet printed silver nanoparticle film as a function of curing time: a) on PEN substrate; and b) on paper                                                                                                                                |

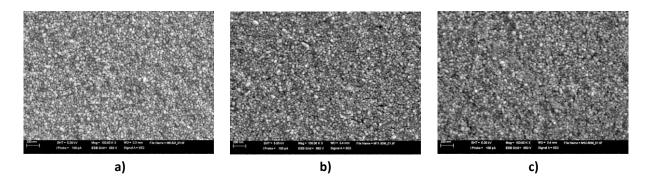

| Figure 3.10. SEM plan view of 130°C for: a) 5 min, b) 30 min, and c) 60 min annealed samples 63                                                                                                                                                                               |

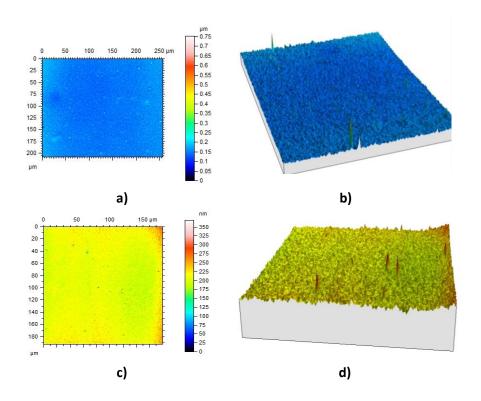

| Figure 3.11. 3D confocal microscope measurements                                                                                                                                                                                                                              |

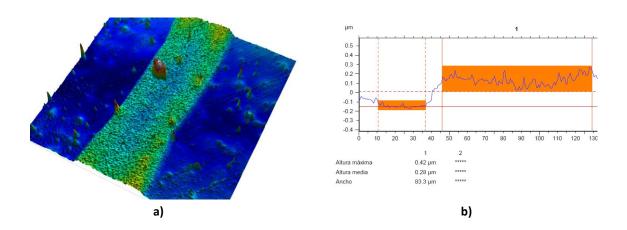

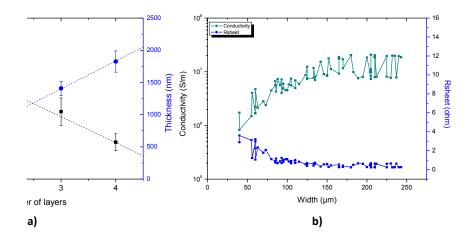

| Figure 3.12. a) Resistivity and thickness of the inkjet printed silver nanoparticle film on PEN as a function of the number of printed layers; and b) Conductivity and $R_{\square}$ measured in a one-layer inkjet printed lines as a function of linewidth.                 |

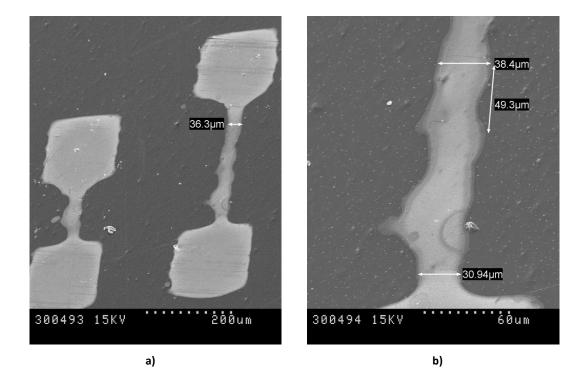

| Figure 3.13. SEM images of silver nanoparticle ink printed structures                                                                                                                                                                                                         |

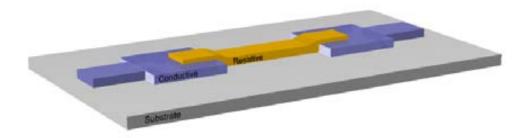

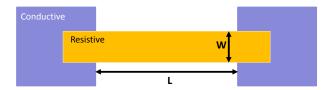

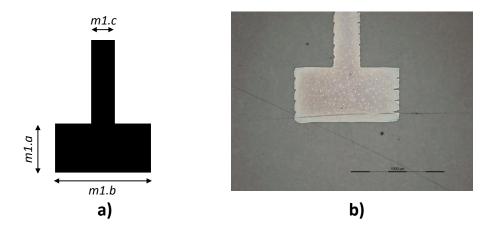

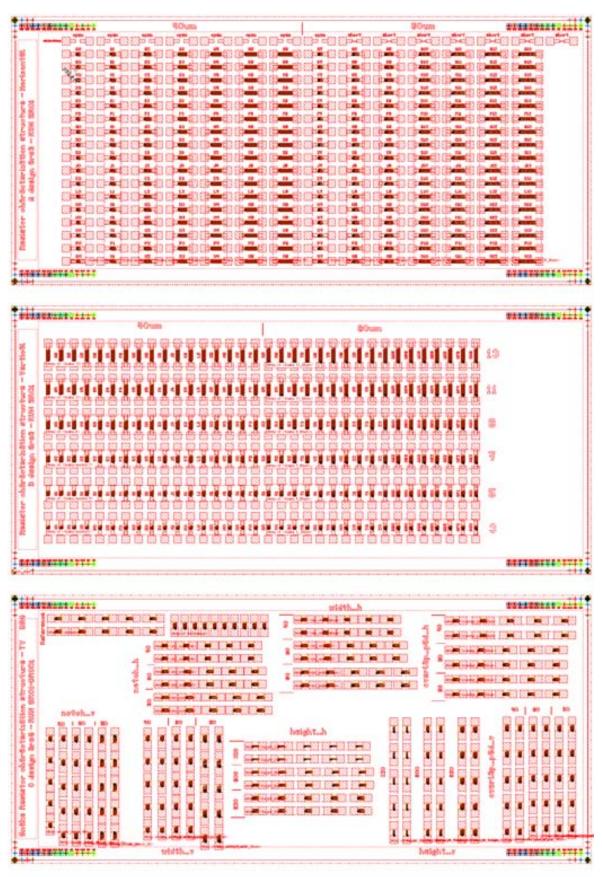

| Figure 3.14. Typical deposited/printed resistor structure and geometry                                                                                                                                                                                                        |

| Figure 3.15. Linear resistor structure and geometry.                                                                                                                                                                                                                          |

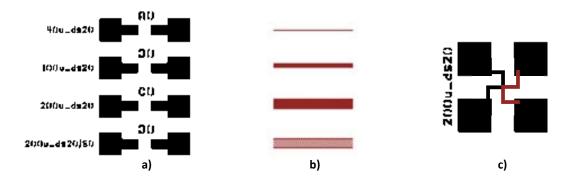

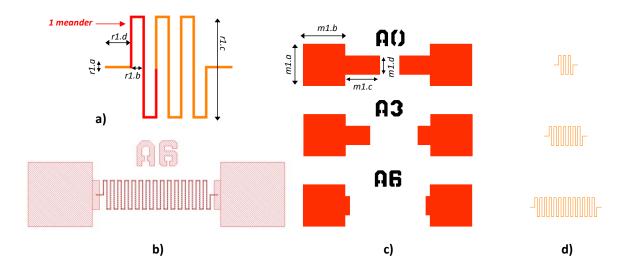

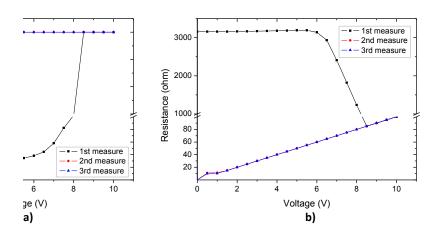

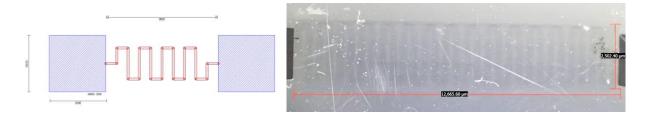

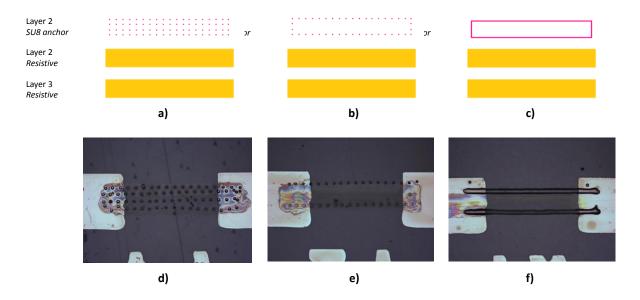

| Figure 3.16. a) Metal1 layer; b) resistive material layer; and c) greek-cross structures. Note: layers are not scale.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

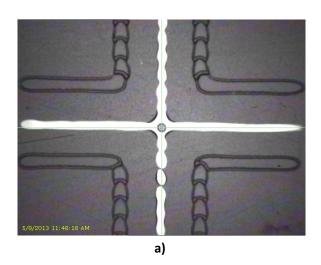

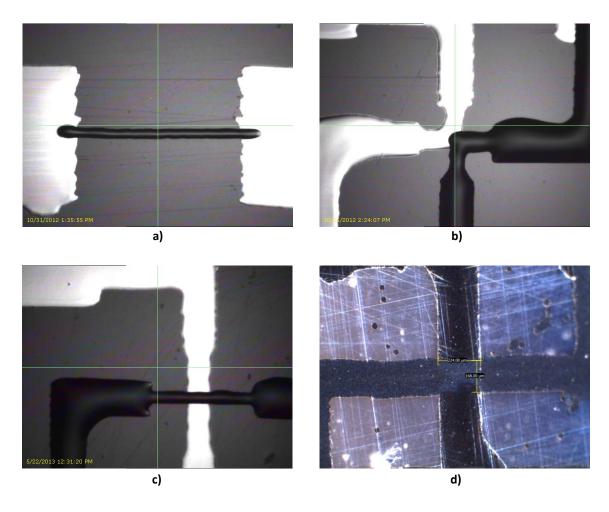

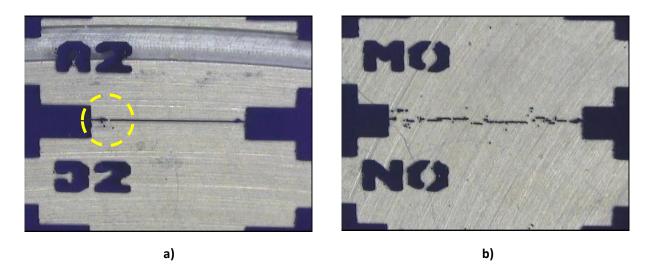

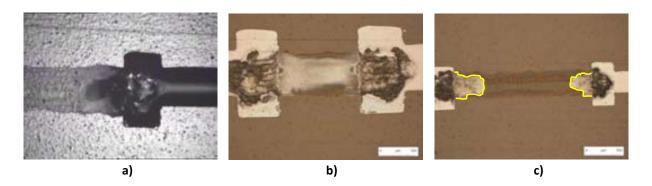

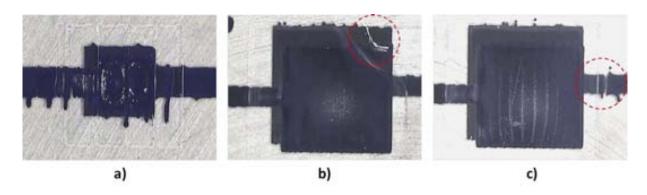

| Figure 3.17. a) and b) Examples of resistors printed where the second layer is not yet cured; c) greek cross structure to extract contact resistance; and d) improved greek cross structure to overcome misalignment problems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

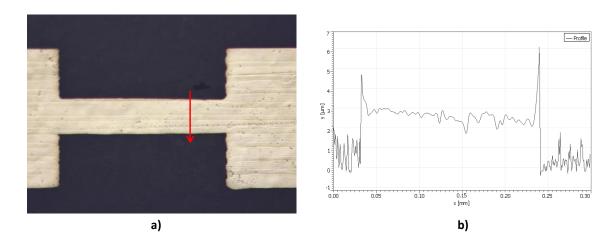

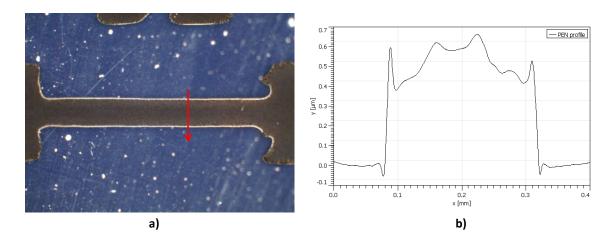

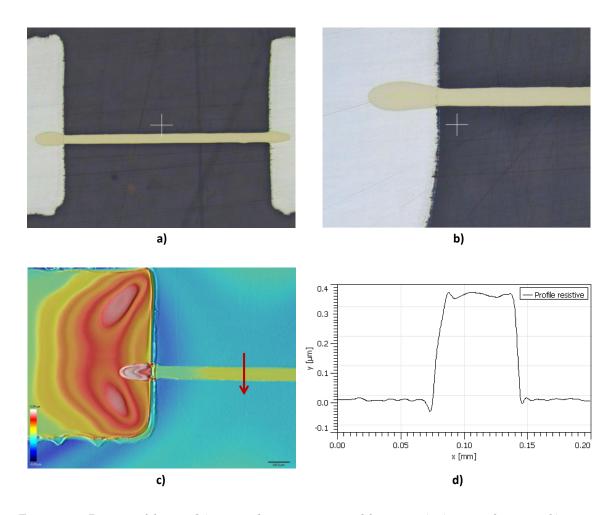

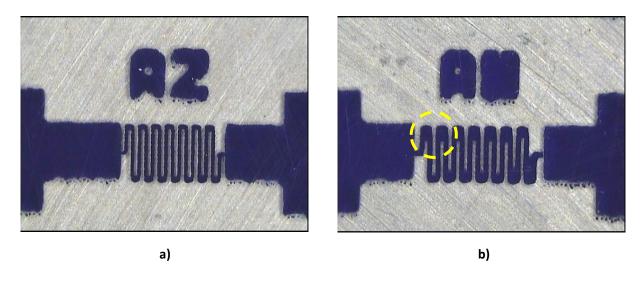

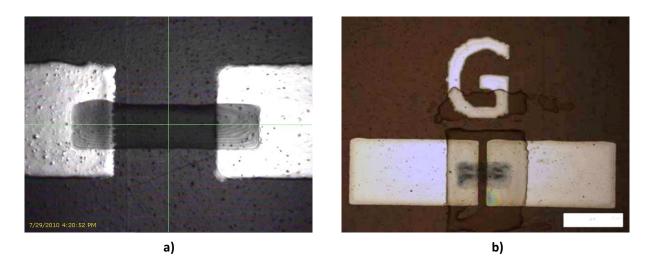

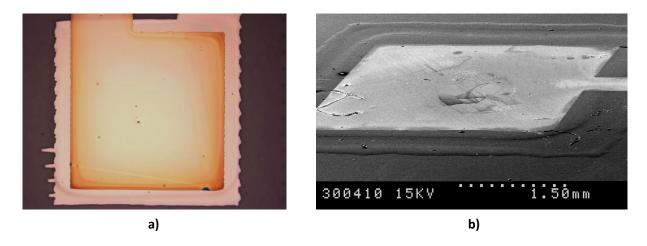

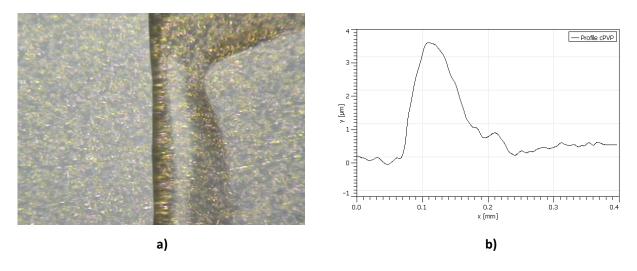

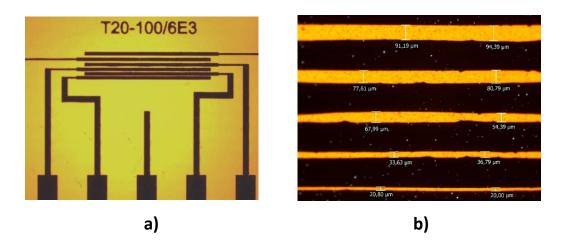

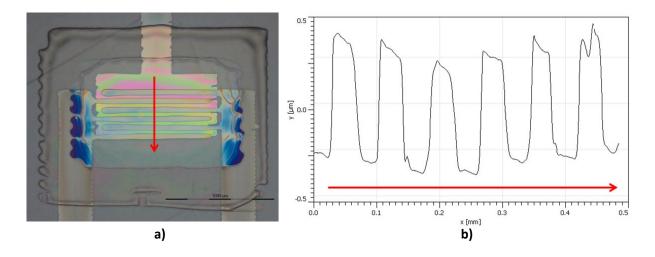

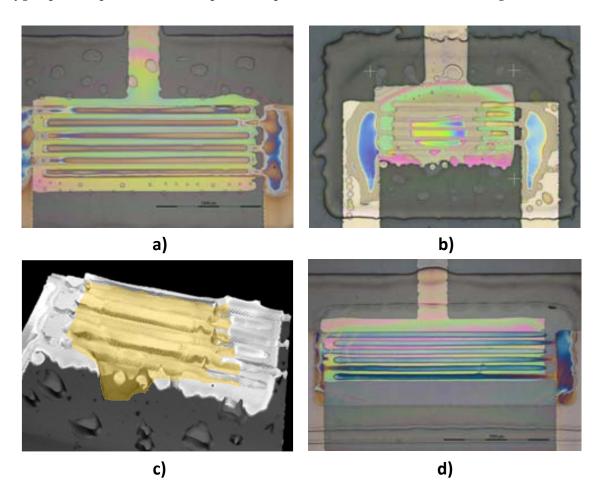

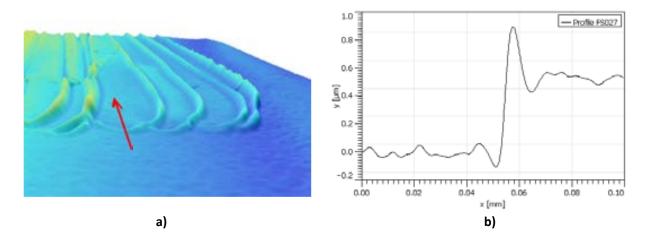

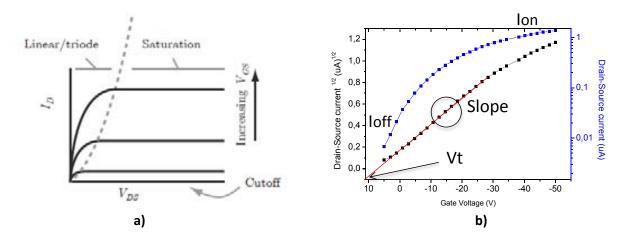

| Figure 3.18. Resistors fabricated (measured resistive strip width is 65 $\mu$ m): a) sintered resistor; b) contact resistance area of the resistor; c) confocal image of the resistor; and d) profile of the resistive track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 70 |

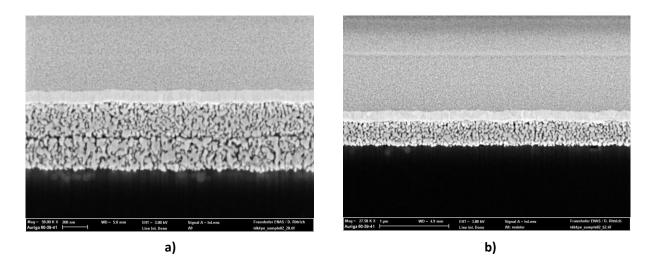

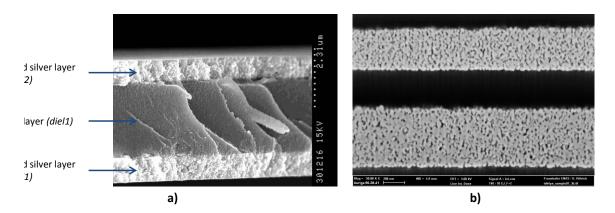

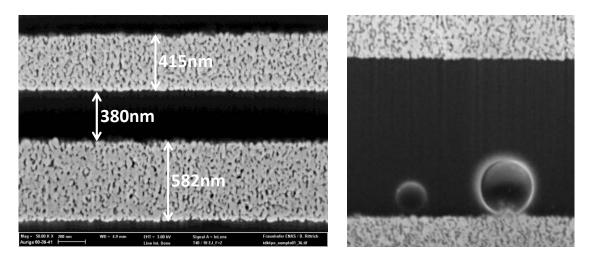

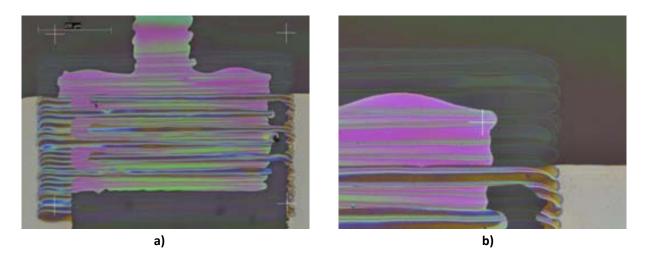

| Figure 3.19. FIB section of a resistor: a) section of the interface between conductive and resistive layers; a b) section of the resistive strip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

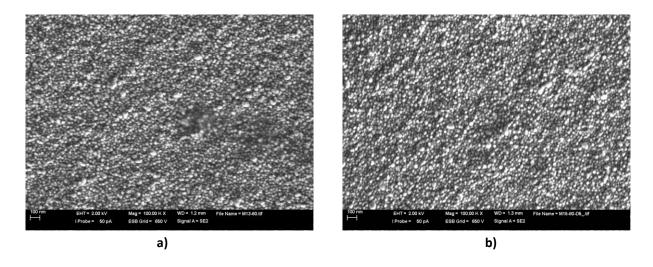

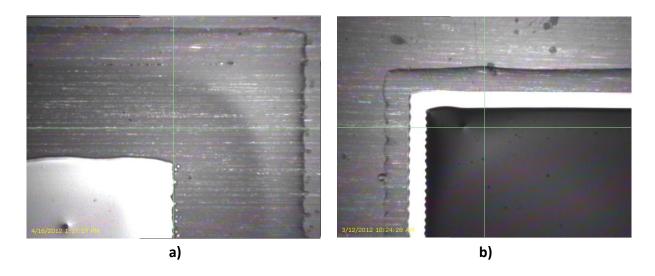

| Figure 3.20. SEM images using 100kX augmentation of silver lines: a) cured at 60°C during 2.5 minutes; because at 80°C during 10 minutes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

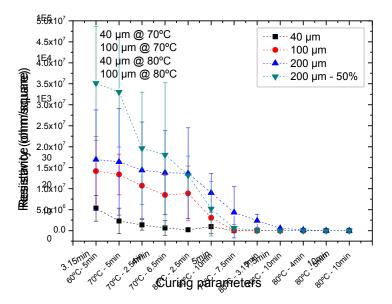

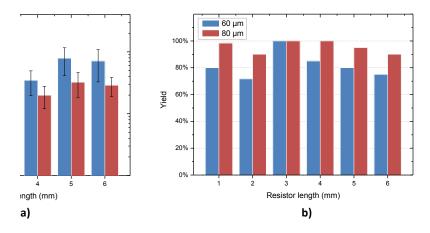

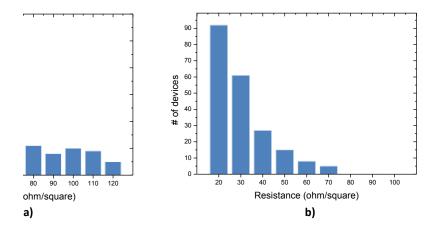

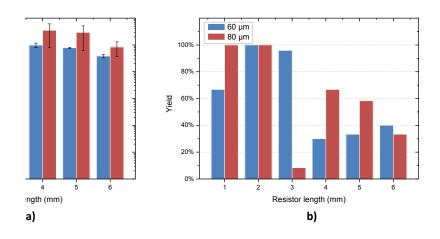

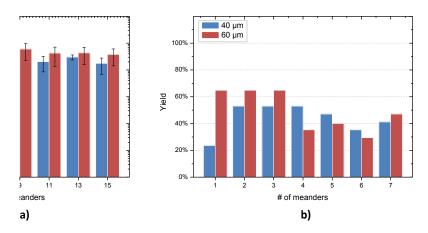

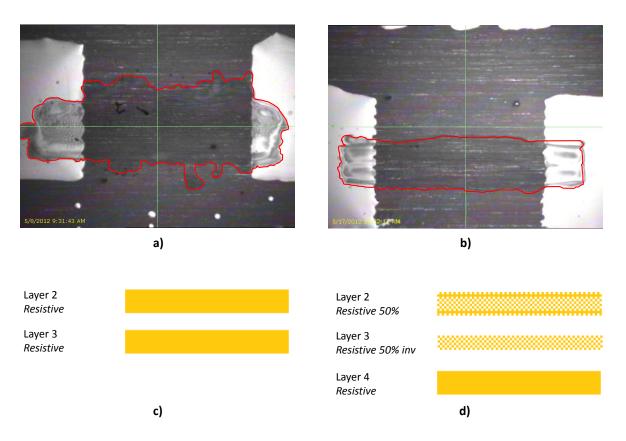

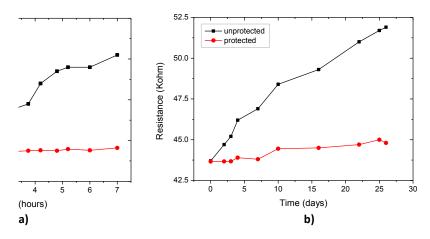

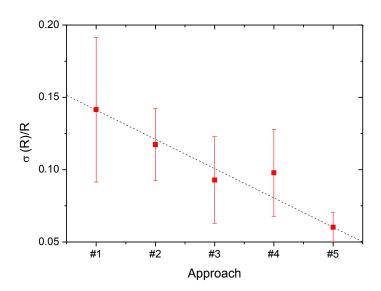

| Figure 3.21. Sheet resistance of resistors with different linewidth, patterns, curing times and temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

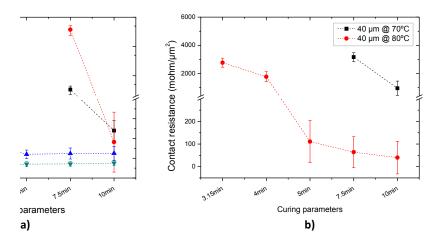

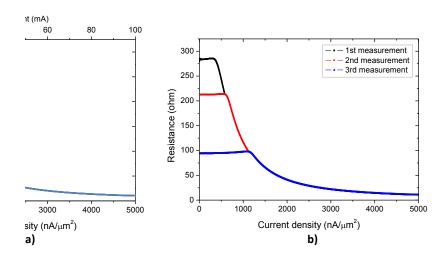

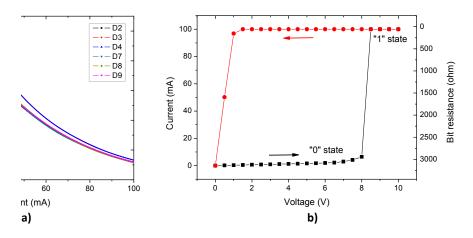

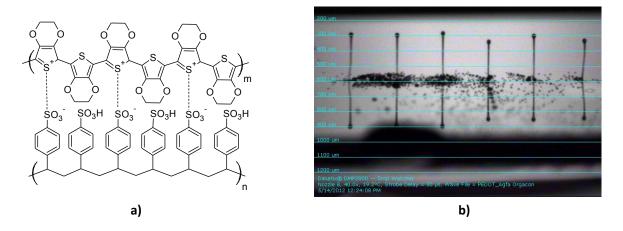

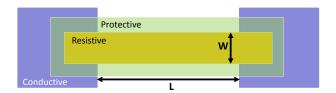

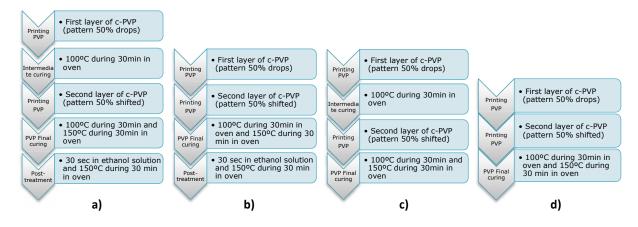

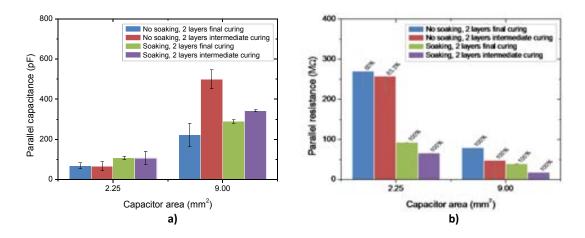

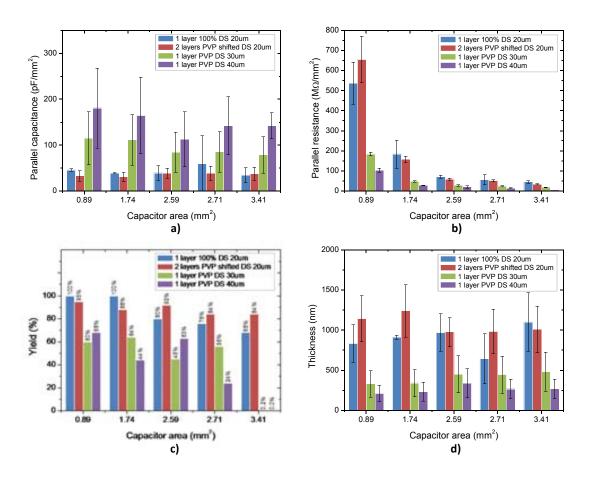

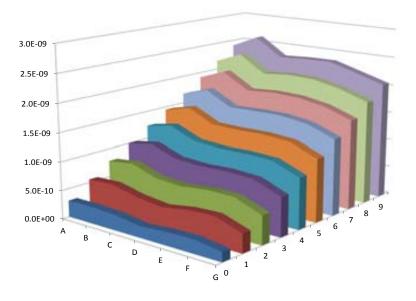

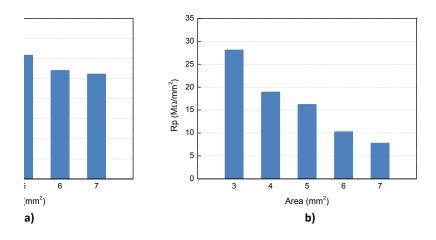

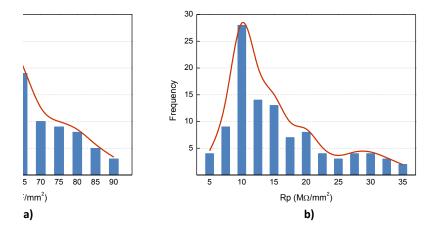

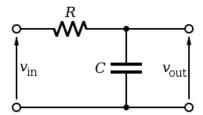

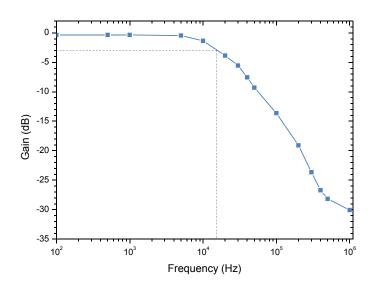

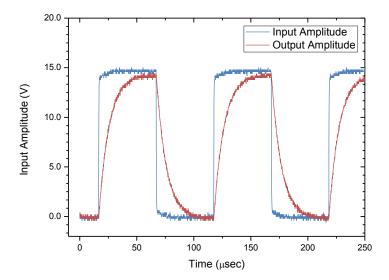

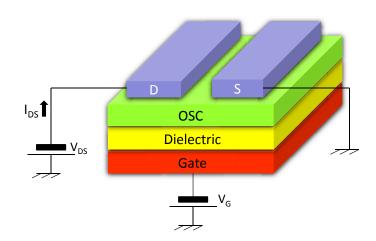

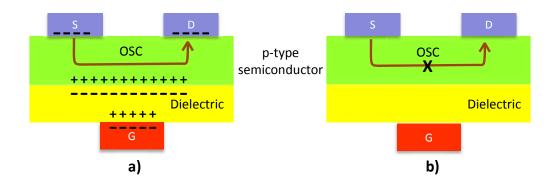

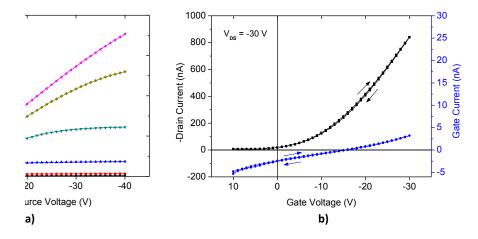

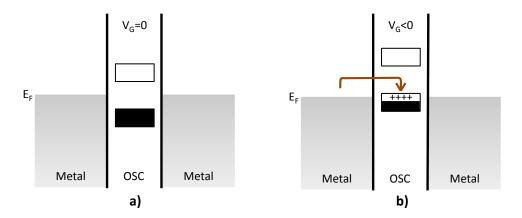

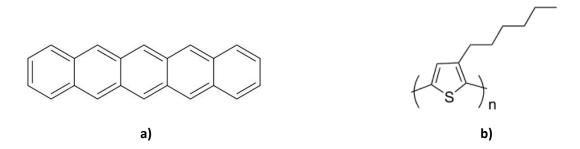

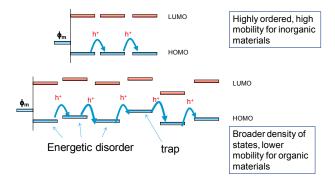

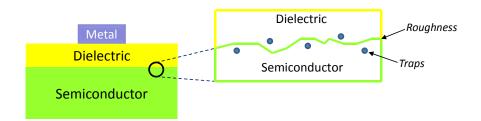

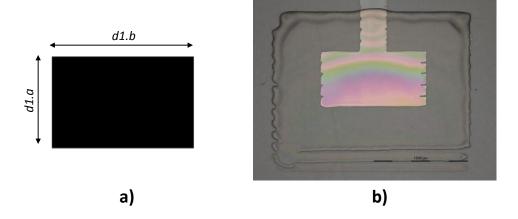

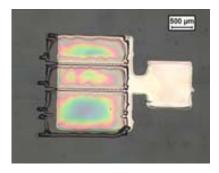

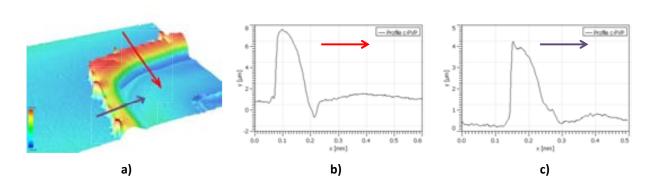

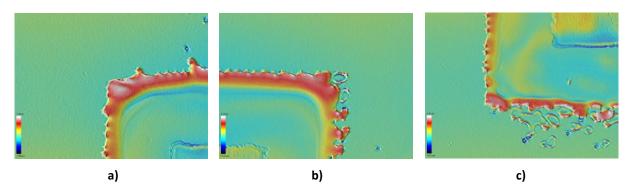

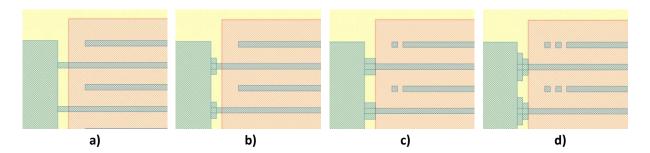

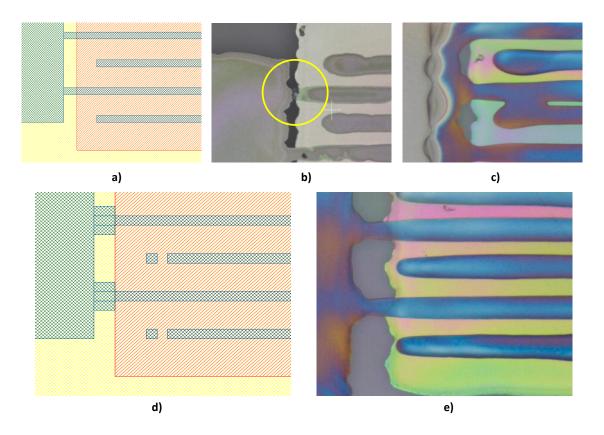

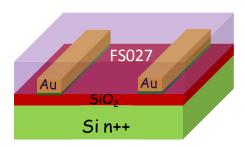

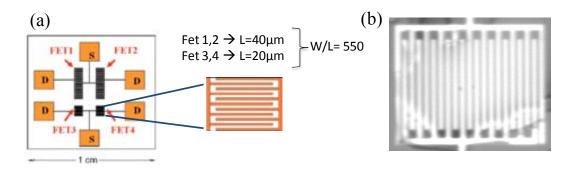

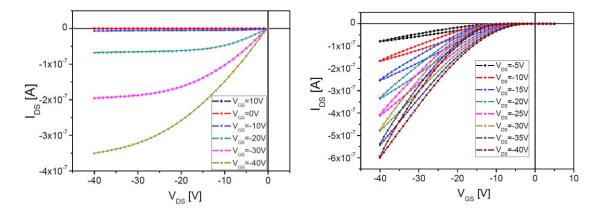

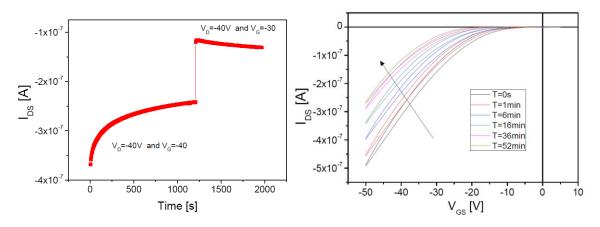

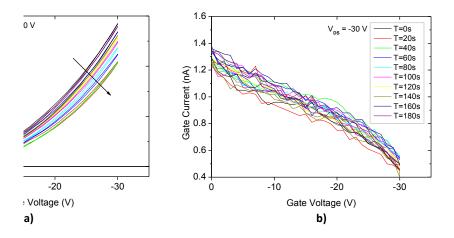

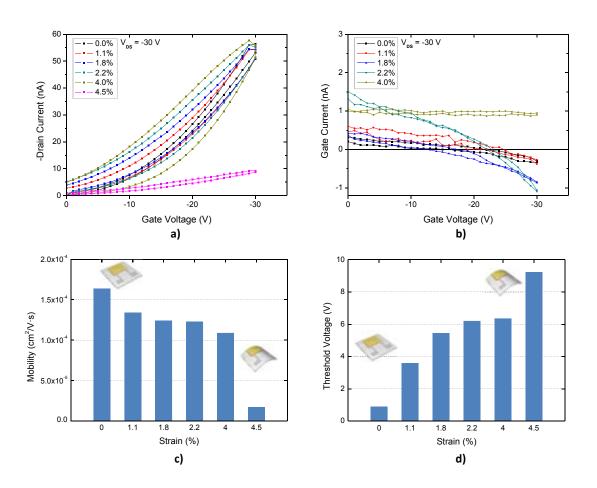

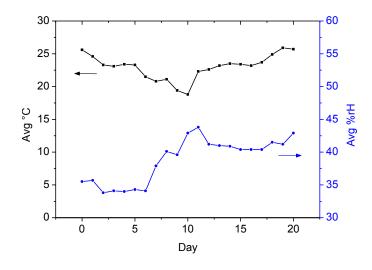

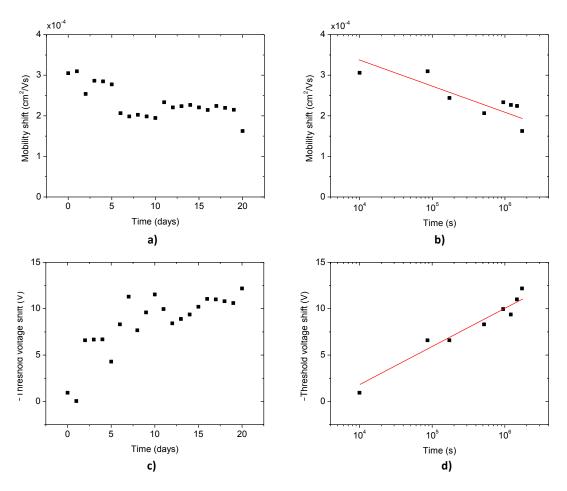

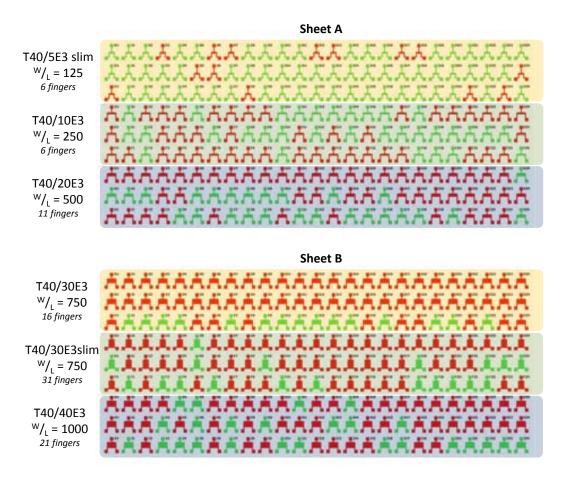

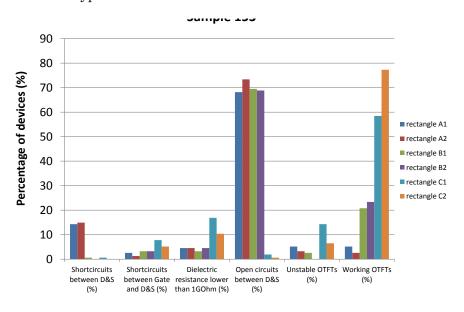

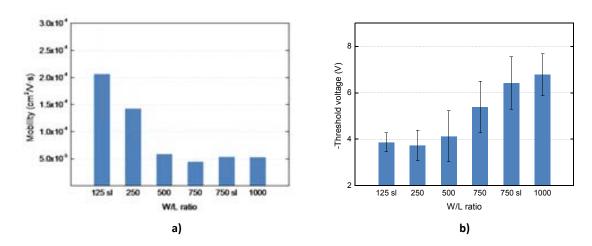

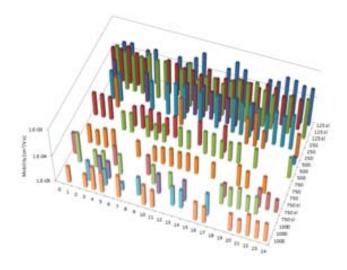

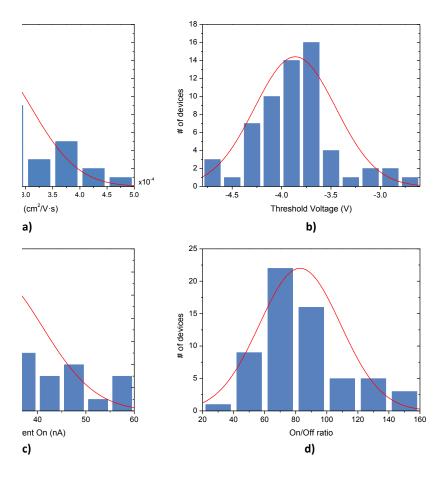

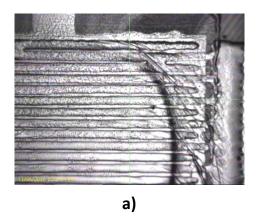

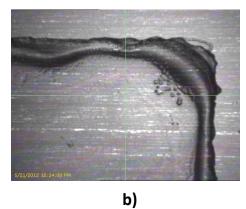

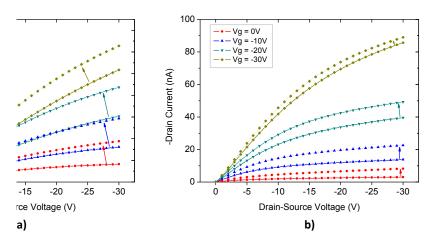

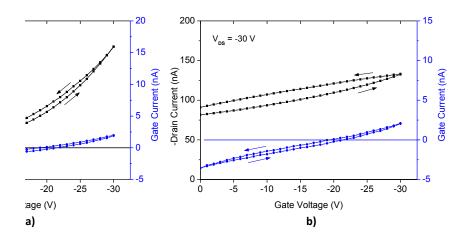

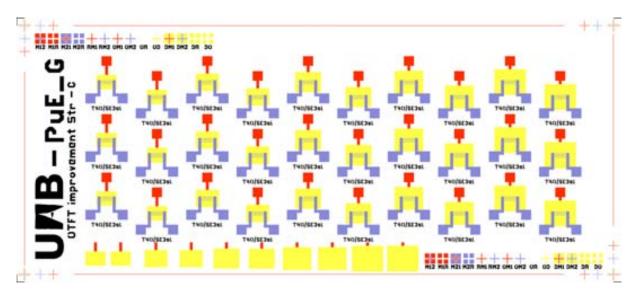

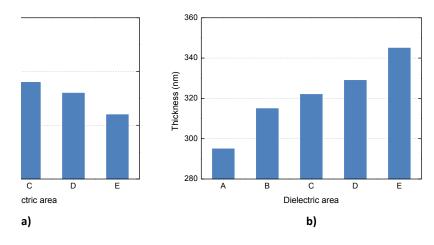

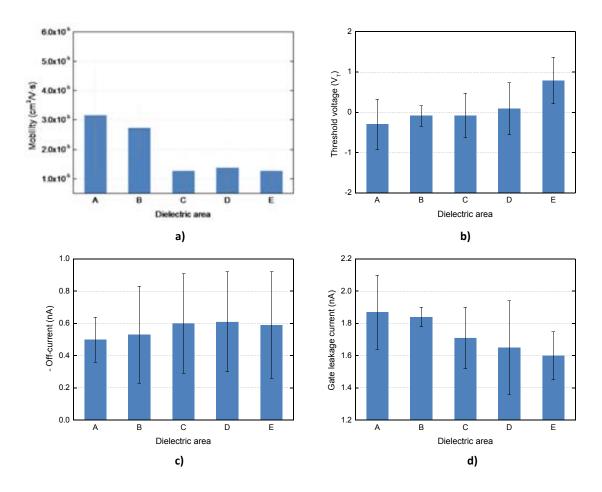

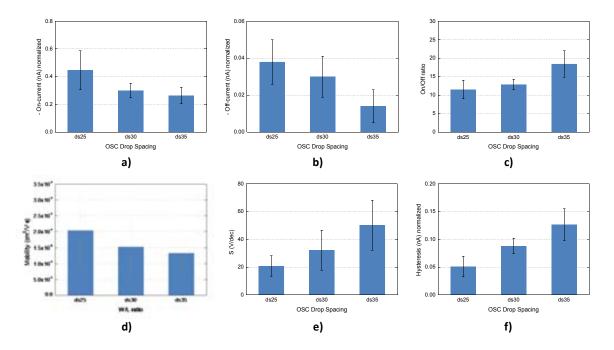

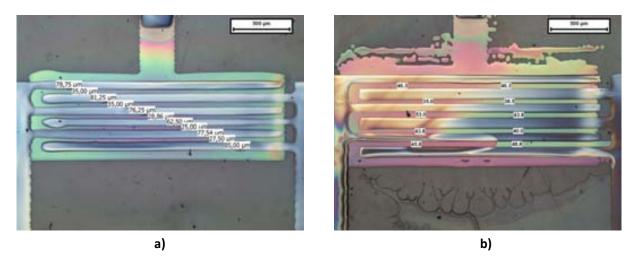

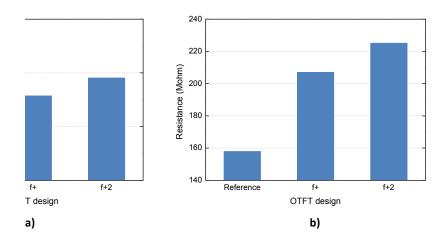

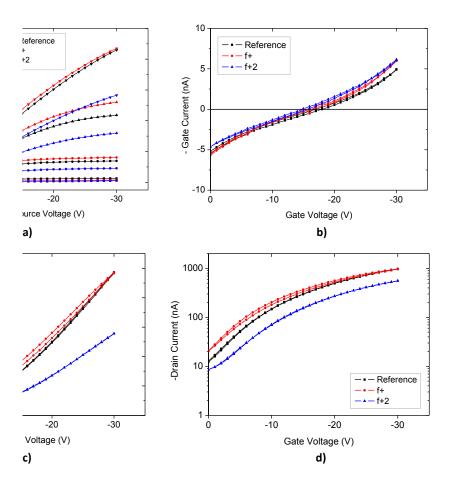

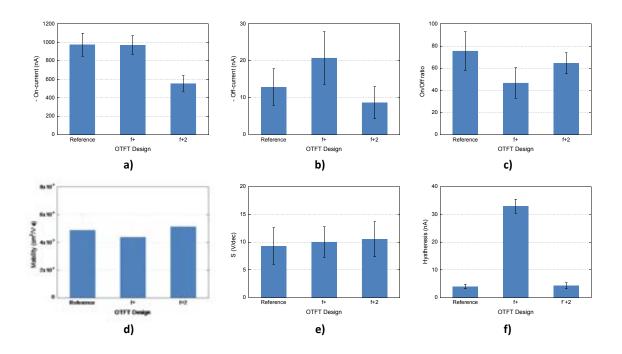

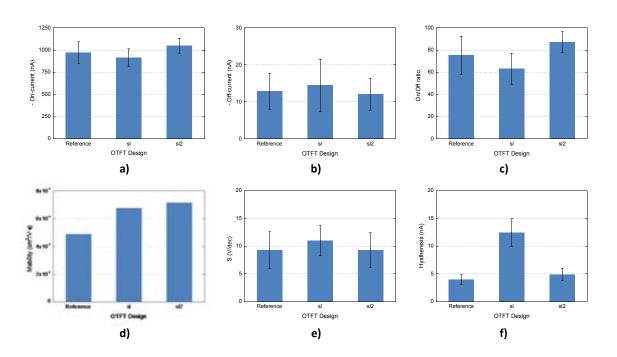

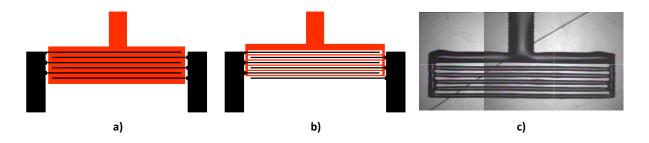

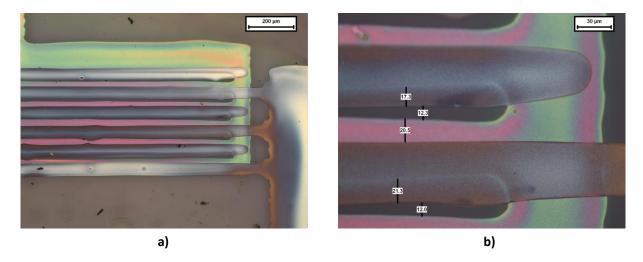

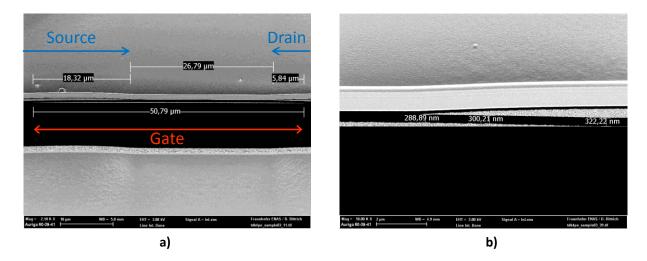

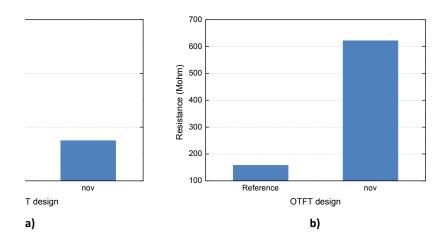

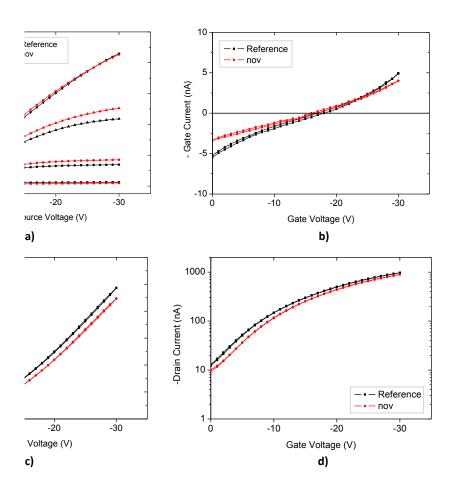

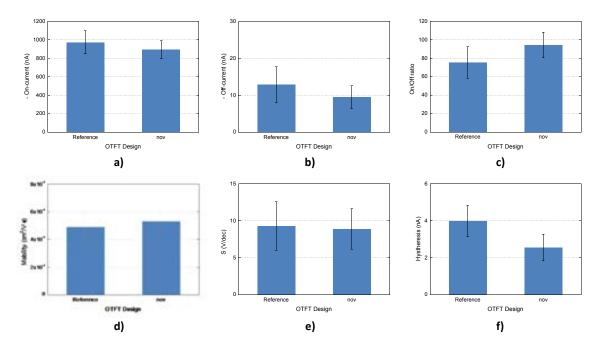

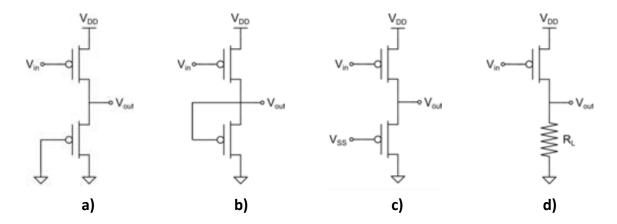

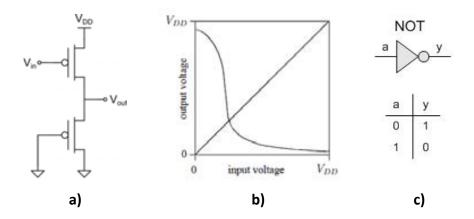

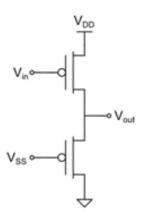

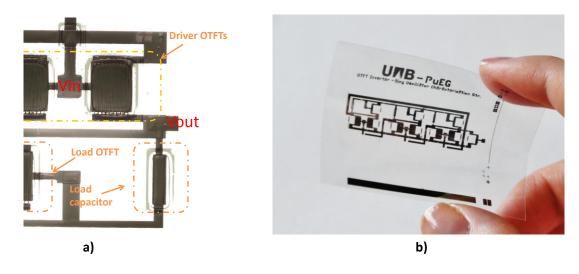

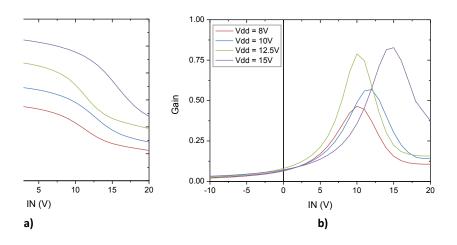

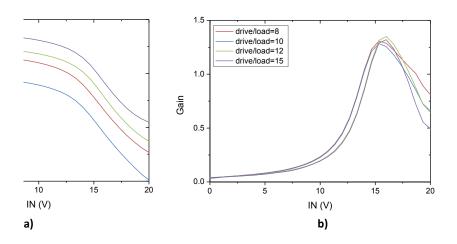

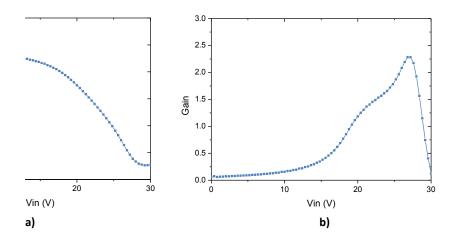

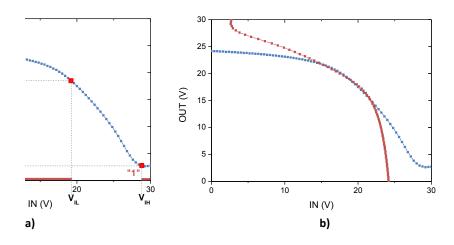

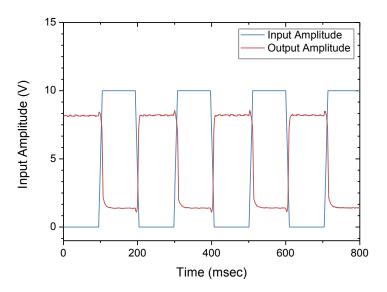

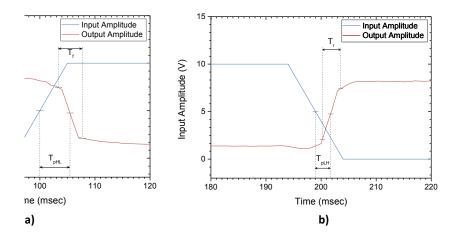

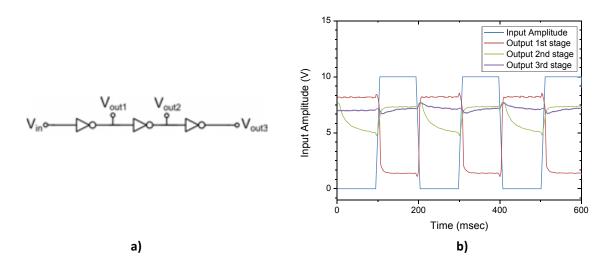

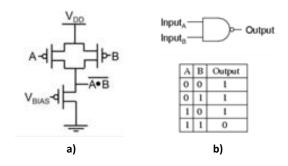

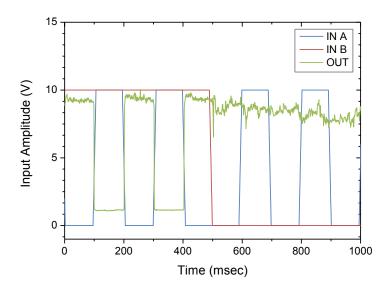

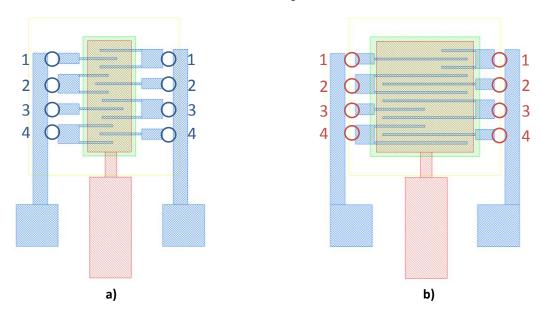

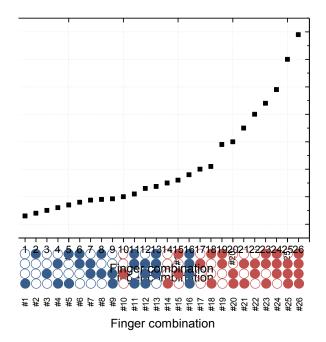

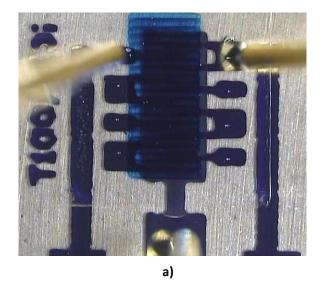

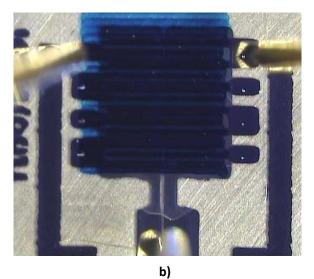

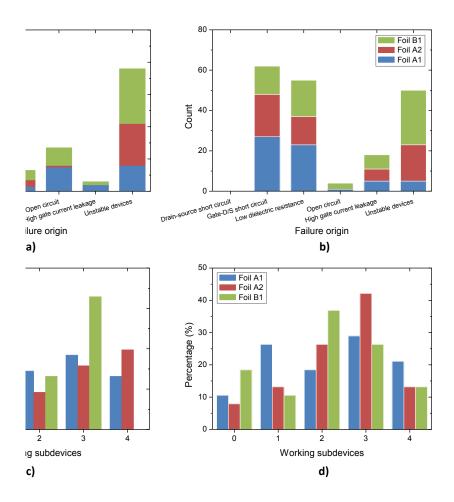

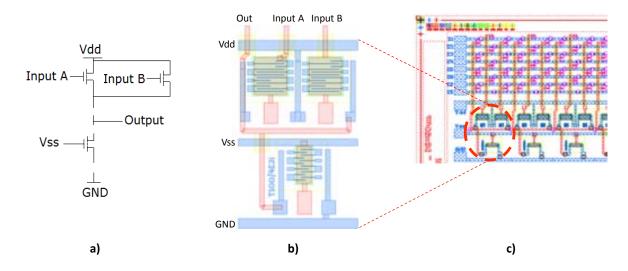

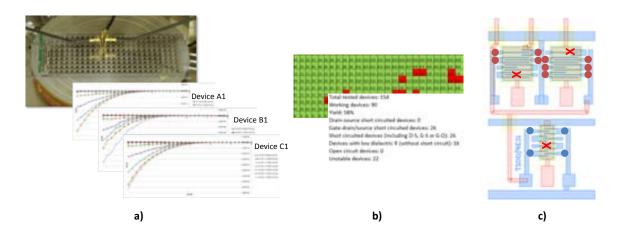

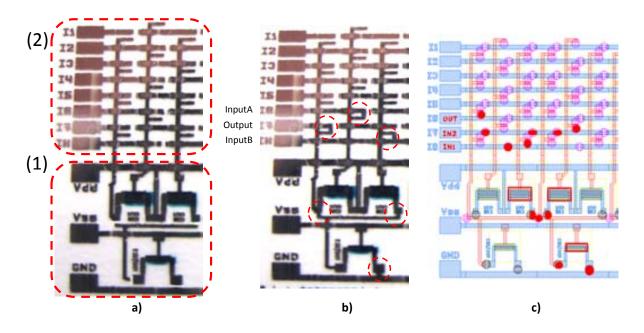

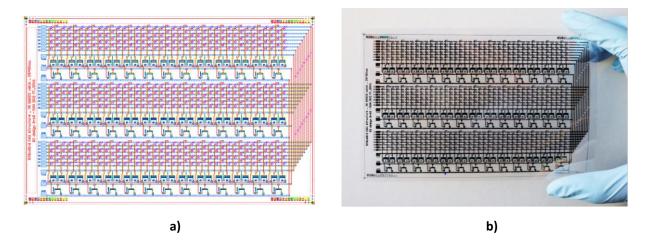

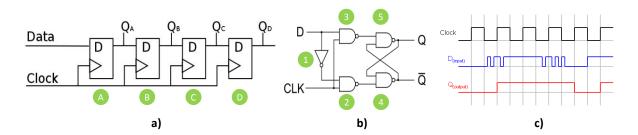

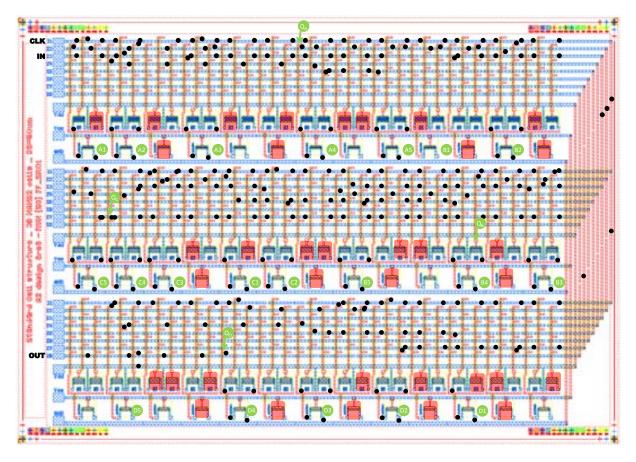

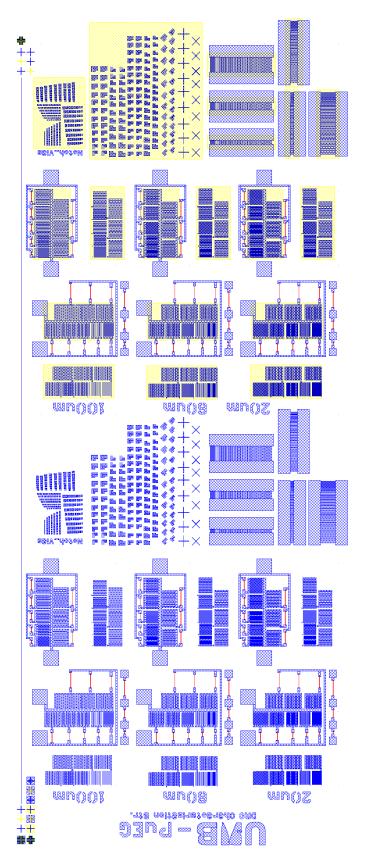

| Figure 3.22. a) Sheet resistance; and b) contact resistance of resistors with different linewidth, curing time and temperatures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | es   |