Departament d'Arquitectura de

Computadors i Sistemes Operatius

Màster en

Computació d'altes prestacions

FACTORES DE RENDIMIENTO EN ENTORNOS MULTICORE.

Memòria del trabajo de “Iniciación a la Investigación. Trabajo de Fin de Máster” del “Máster en Computació d'altes prestacions”, realizada por *César Allande Álvarez*, bajo la dirección de *Eduardo César Galobardes*. Presentada en la Escuela de Ingeniería (Departamento de Arquitectura de Computadores y Sistemas Operativos)

5 de Julio de 2010

## Resumen

Este documento refleja el estudio de investigación para la detección de factores que afectan al rendimiento en entornos multicore. Debido a la gran diversidad de arquitecturas multicore se ha definido un marco de trabajo, que consiste en la adopción de una arquitectura específica, un modelo de programación basado en paralelismo de datos, y aplicaciones del tipo Single Program Multiple Data. Una vez definido el marco de trabajo, se han evaluado los factores de rendimiento con especial atención al modelo de programación. Por este motivo, se ha analizado la librería de threads y la API OpenMP para detectar aquellas funciones sensibles de ser sintonizadas al permitir un comportamiento adaptativo de la aplicación al entorno, y que dependiendo de su adecuada utilización han de mejorar el rendimiento de la aplicación.

## Resum

Aquest document reflexa l'estudi d'investigació per a la detecció de factores que afecten al rendiment en entorns multicore. Degut a la gran quantitat d'arquitectures multicore s'ha definit un marc de treball acotat, que consisteix en la adopció d'una arquitectura específica, un model de programació basat en paral·lelisme de dates, i aplicacions del tipus Single Program Multiple Data. Una vegada definit el marc de treball, s'ha evaluat els factors de rendiment amb especial atenció al model de programació. Per aquest motiu, s'ha analitzat la llibreria de thread i la API OpenMP per a detectar aquelles funcions sensibles de ser sintonitzades, al permetre un comportament adaptatiu de l'aplicació a l'entorn, i que, depenent de la seva adequada utilització s'aconsegueix una millora en el rendiment de la aplicació.

## Abstract

This work reflects research studies for the detection of factors that affect performance in multicore environments. Due to the wide variety of multicore architectures we have defined a framework, consisting of a specific architecture, a programming model based on data parallelism, and Single Program Multiple Data applications. Having defined the framework, we evaluate the performance factors with special attention to programming model. For this reason, we have analyzed thread library and OpenMP API to detect those candidate functions to be tuned, allowing applications to behave adaptively to the computing environment, and based on their proper use will improve performance.

# Índice general

|                                                         |           |

|---------------------------------------------------------|-----------|

| <b>1. Introducción</b>                                  | <b>1</b>  |

| 1.1. Contexto . . . . .                                 | 2         |

| 1.2. Motivación . . . . .                               | 4         |

| 1.3. Objetivos . . . . .                                | 5         |

| 1.4. Trabajos Relacionados . . . . .                    | 7         |

| 1.5. Estructura del Documento . . . . .                 | 11        |

| <b>2. Entornos Paralelos de HPC</b>                     | <b>13</b> |

| 2.1. Arquitecturas paralelas . . . . .                  | 14        |

| 2.2. Modelos de programación paralelos . . . . .        | 15        |

| 2.2.1. Paralelismo de aplicación . . . . .              | 16        |

| 2.2.2. Paralelismo funcional . . . . .                  | 16        |

| 2.2.3. Paralelismo de datos . . . . .                   | 16        |

| 2.3. Aplicaciones Paralelas . . . . .                   | 16        |

| 2.3.1. Paradigmas de Programación Paralela . . . . .    | 17        |

| 2.4. Monitorización, Análisis y Sintonización . . . . . | 18        |

| <b>3. Entornos Multicore</b>                            | <b>21</b> |

| 3.1. Arquitectura de los cores . . . . .                | 22        |

| 3.2. Jerarquías de memoria . . . . .                    | 23        |

| 3.3. Redes de interconexión . . . . .                   | 24        |

| 3.4. Interfaz de acceso a memoria . . . . .             | 25        |

| <b>4. Marco de trabajo</b>                              | <b>27</b> |

| 4.1. Nivel de Arquitectura . . . . .                    | 27        |

| 4.2. Nivel de Modelo de programación . . . . .          | 28        |

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| 4.2.1. Threads . . . . .                                          | 29        |

| 4.2.2. OpenMP . . . . .                                           | 38        |

| <b>5. Análisis de los Factores de Rendimiento</b>                 | <b>51</b> |

| 5.1. Factores de Rendimiento . . . . .                            | 51        |

| 5.2. Caracterización de Aplicaciones Paralelas . . . . .          | 53        |

| 5.2.1. Segmentación de Imágenes de Resonancia Magnética . . . . . | 54        |

| 5.2.2. Multiplicación de Matrices . . . . .                       | 55        |

| 5.2.3. Multiplicación de Matrices por Bloques . . . . .           | 55        |

| 5.3. Experimentación . . . . .                                    | 56        |

| 5.3.1. Gestores de planificación . . . . .                        | 56        |

| 5.3.2. Acceso a memoria . . . . .                                 | 62        |

| 5.3.3. Localidad de los datos . . . . .                           | 64        |

| <b>6. Conclusiones</b>                                            | <b>69</b> |

| 6.1. Trabajo Futuro . . . . .                                     | 70        |

# Índice de figuras

|                                                                                                                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1. Utilización de tecnologías Multicore en sistemas HPC. Lista Top500 Junio 2010 .                                                                                                                             | 5  |

| 4.1. Modelo de thread M:N . . . . .                                                                                                                                                                              | 30 |

| 4.2. Estructura modular del compilador GCC . . . . .                                                                                                                                                             | 46 |

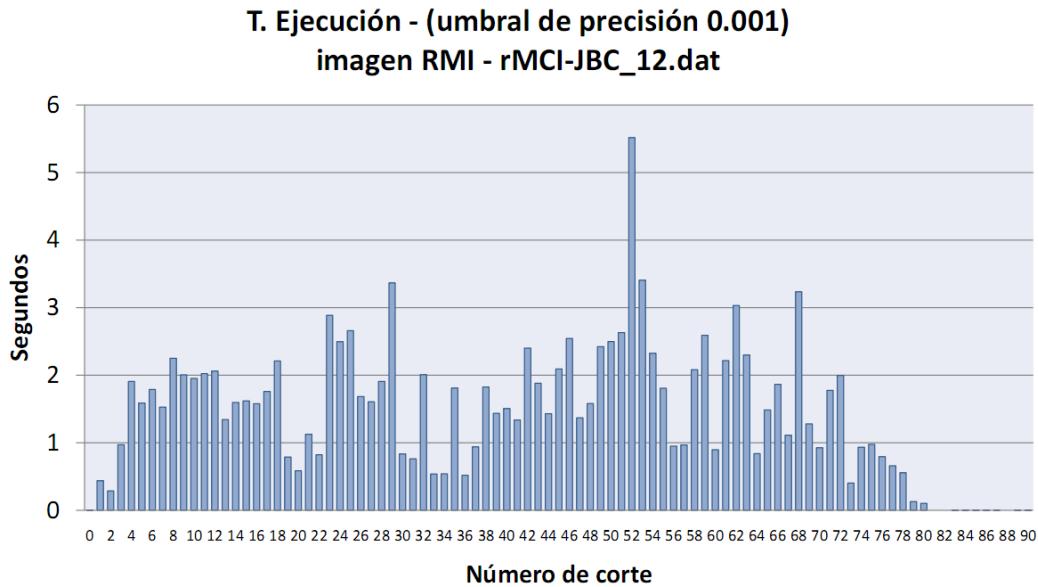

| 5.1. Tiempo de ejecución del proceso de segmentación de imágenes RMI, realizado por cortes de una imagen 3D . . . . .                                                                                            | 57 |

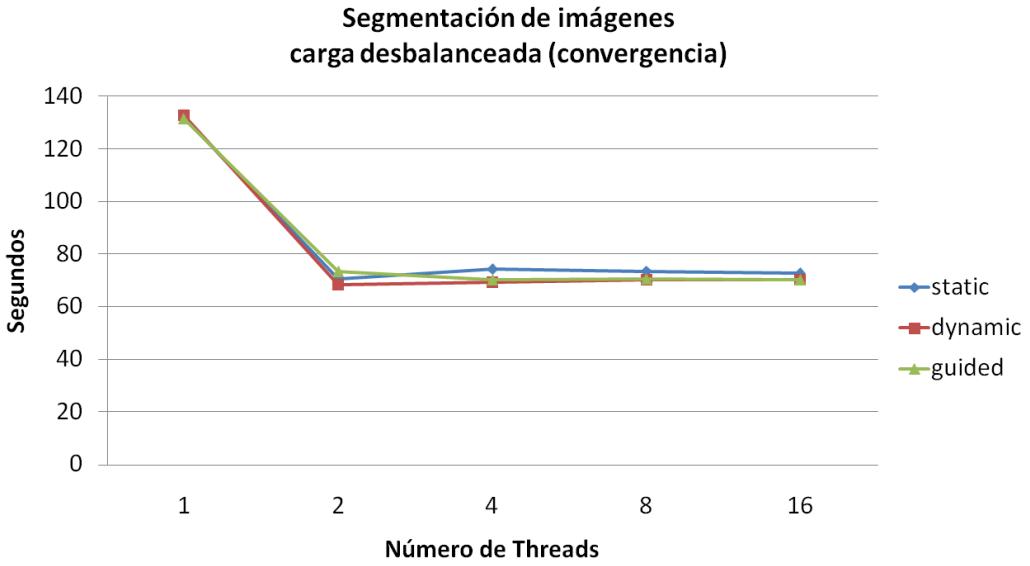

| 5.2. Tiempo de ejecución del proceso de segmentación de imágenes RMI, para diferentes políticas de planificación y número de threads . . . . .                                                                   | 58 |

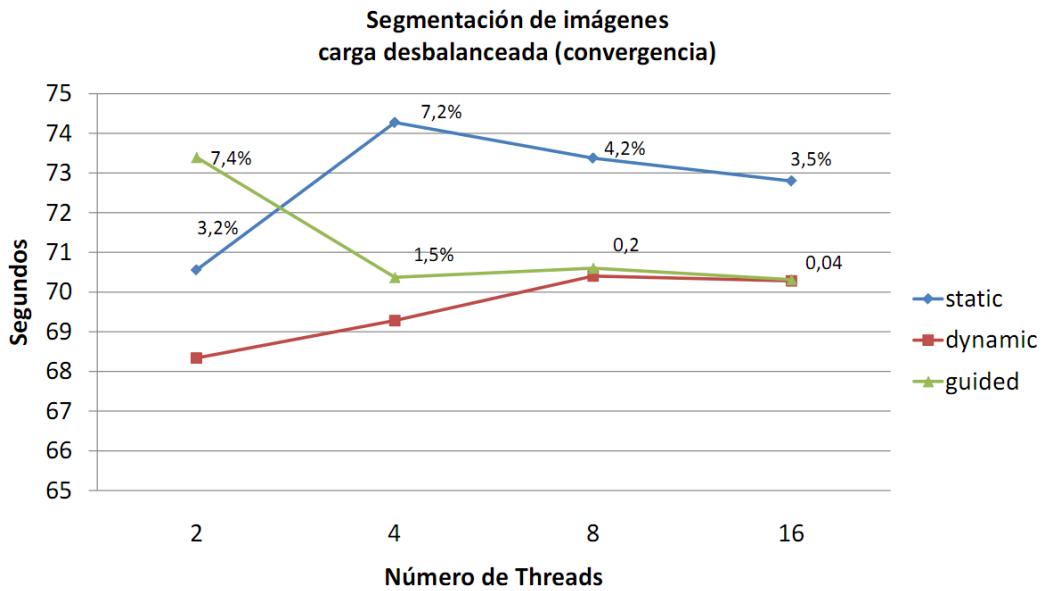

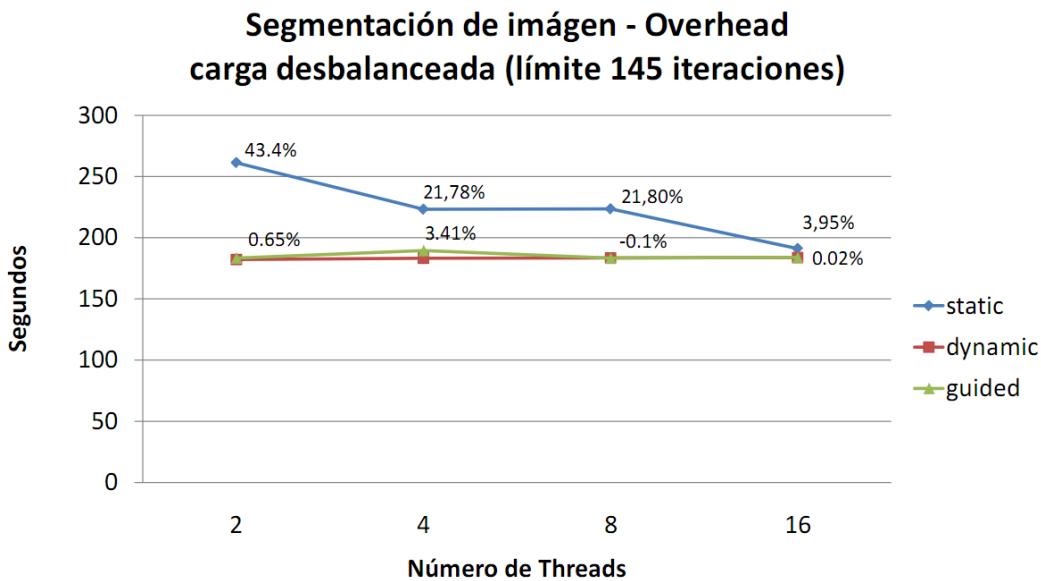

| 5.3. Detalle de los tiempos de ejecución paralelos de la segmentación de IRM. Se muestran los overheads de las políticas <i>guided</i> y <i>static</i> , respecto a la planificación dinámica. . . . .           | 59 |

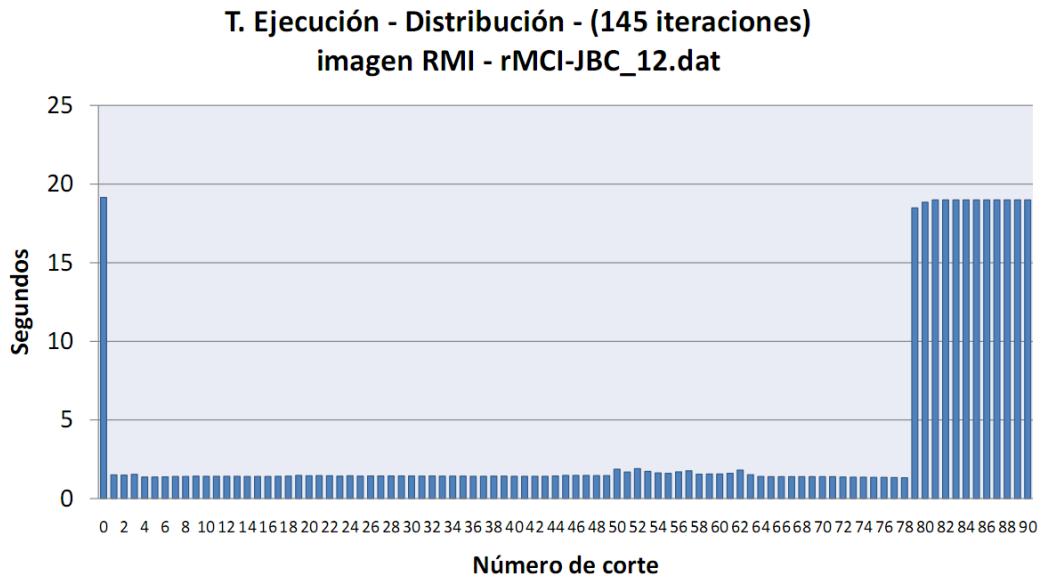

| 5.4. Esta gráfica muestra el desbalanceo de carga existente, para una imagen de entrada, para el proceso de segmentación modificado, sin evaluación de calidad. . . . .                                          | 60 |

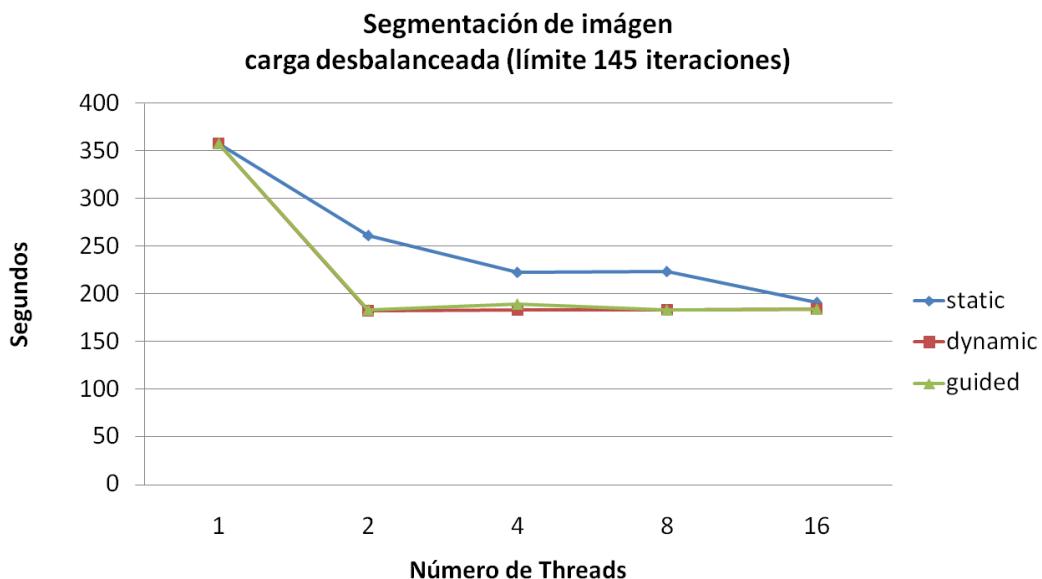

| 5.5. Tiempos de ejecución para el proceso de segmentación modificado. Se han eliminado el control de calidad, forzando un número de iteraciones constante para cada corte. . . . .                               | 60 |

| 5.6. Detalle de los tiempos de ejecución paralelos de la segmentación de IRM modificado. Se muestran los overhead de las políticas <i>guided</i> y <i>static</i> , respecto a la planificación dinámica. . . . . | 61 |

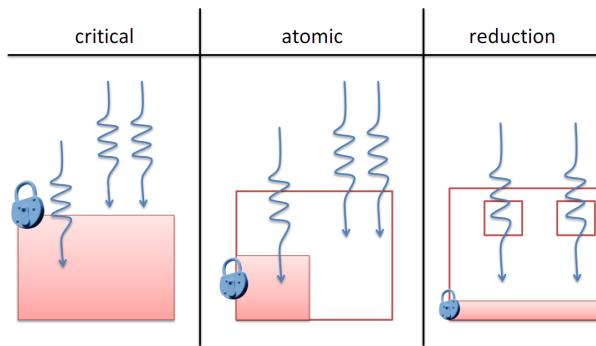

| 5.7. Representación esquemática de los tipos de herramientas de sincronización en el acceso definidos en OpenMP. . . . .                                                                                         | 63 |

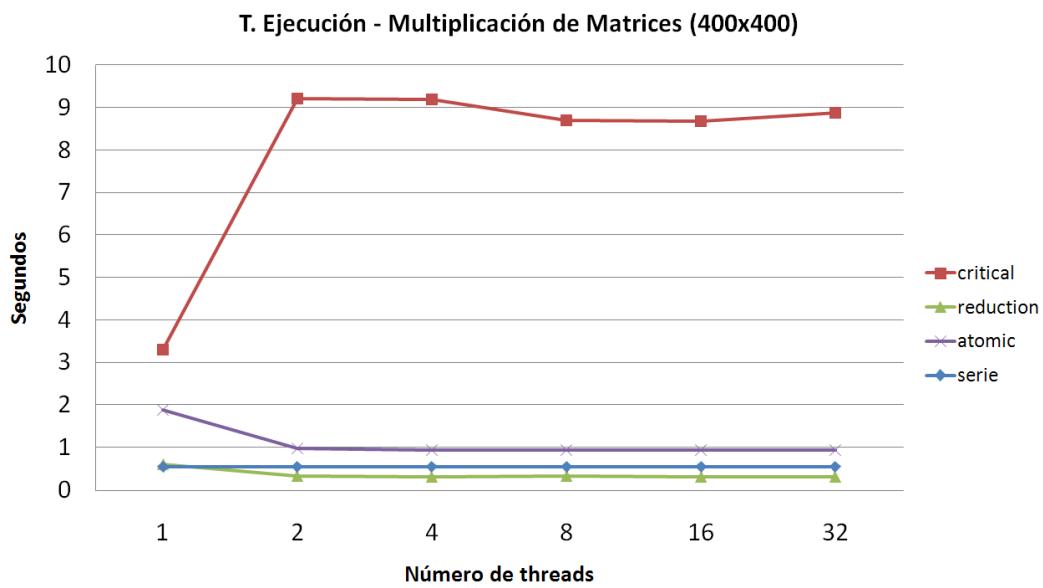

| 5.8. Tiempo de ejecución para la multiplicación de matrices, en una arquitectura de dos cores . . . . .                                                                                                          | 64 |

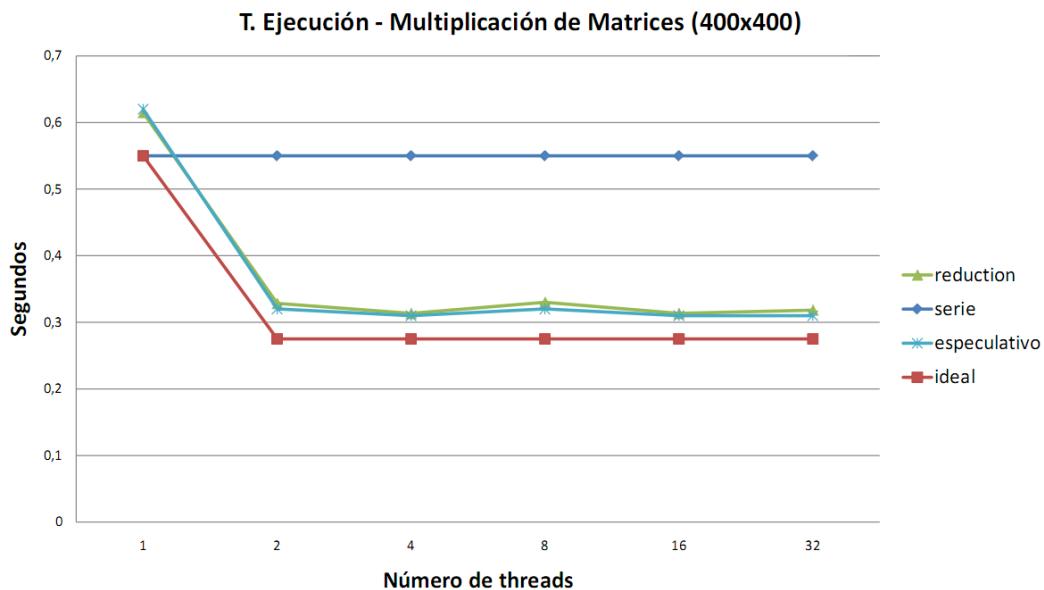

| 5.9. Detalle de tiempo de ejecución para la multiplicación de matrices, de la directiva <i>reduction</i> . . . . .                                                                                               | 65 |

|                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

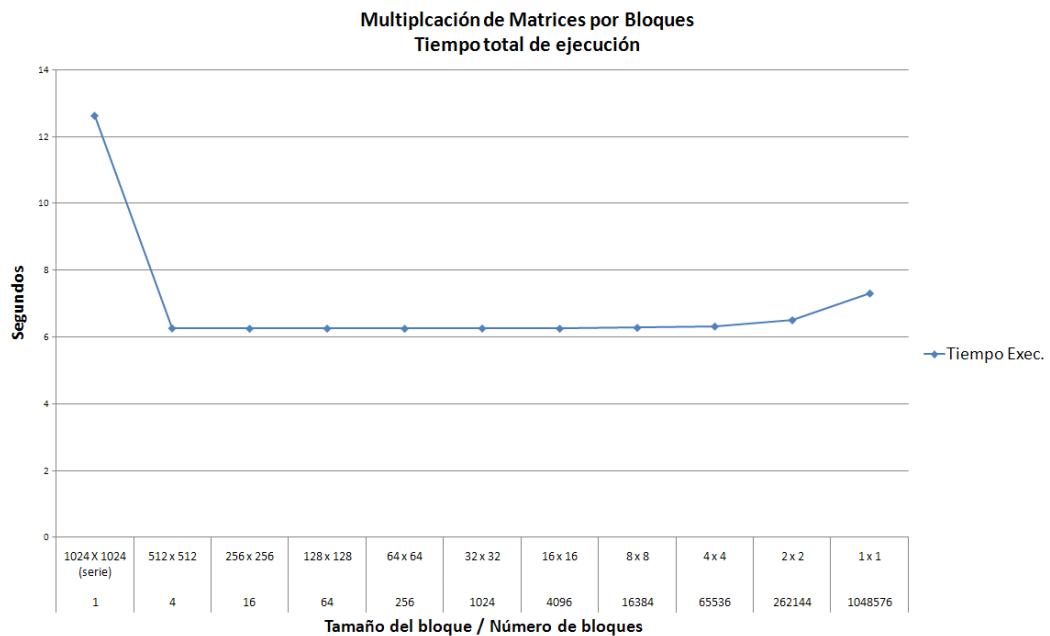

| 5.10. Tiempo de ejecución de la multiplicación de matrices por bloques, para una matriz de 1024 x 1024 . . . . .                                | 66 |

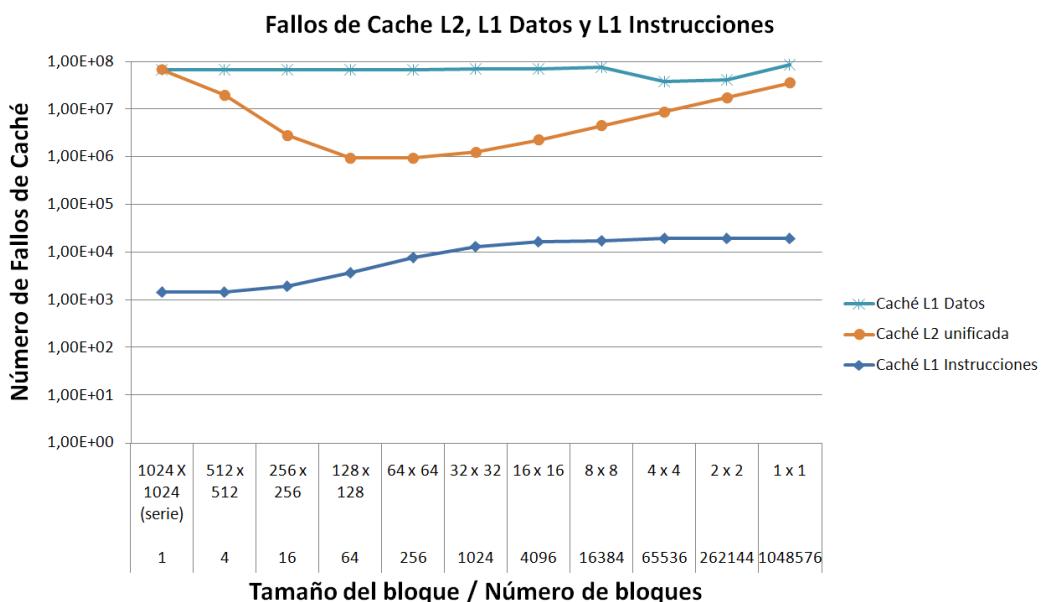

| 5.11. Número de fallos de caché para diferentes particiones de la matriz. . . . .                                                               | 66 |

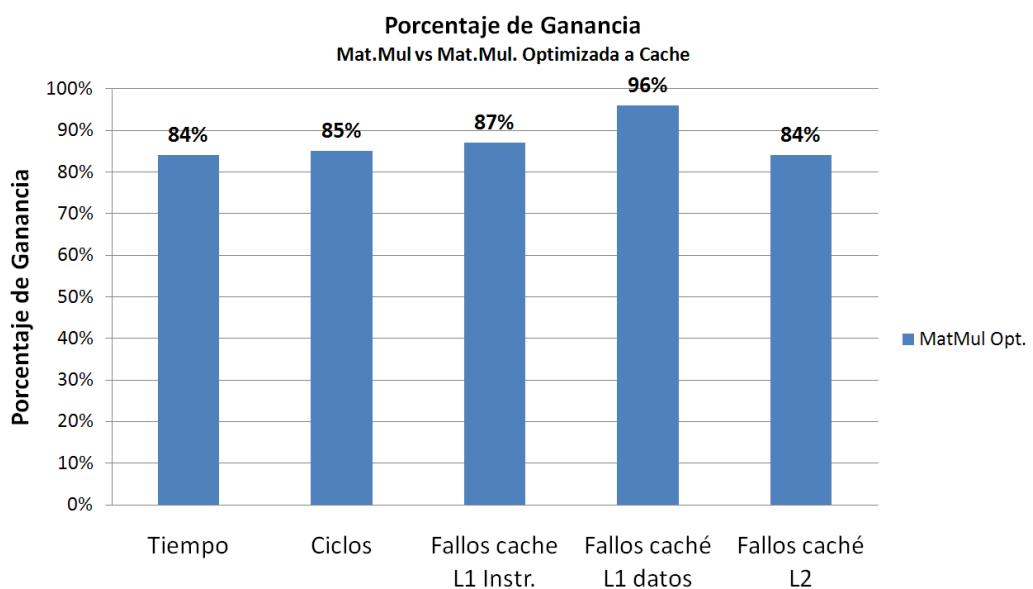

| 5.12. Ganancia con la versión adaptada a dos niveles de la jerarquía de caché, respecto a la versión adaptada al primer nivel de cache. . . . . | 68 |

# Índice de tablas

|                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------|----|

| 4.1. Resumen de primitivas de la librería POSIX . . . . .                                                  | 34 |

| 4.2. Compiladores con soporte OpenMP . . . . .                                                             | 39 |

| 4.3. Relaciones de sobreescritura de las Internal Control Variables . . . . .                              | 42 |

| 5.1. Comparativa entre multiplicación por bloques y multiplicación por bloques optimizada a caché. . . . . | 67 |

# Capítulo 1

## Introducción

Este documento está centrado en la detección de parámetros que afectan al rendimiento en entornos multicore dentro del ámbito de HPC. Existe gran variedad de sistemas multicore o CMP (Chip Multiprocessors) con diferencias en su arquitectura y modelos de programación que explotan sus capacidades. La implantación de sistemas multicore en HPC actualmente está ampliamente extendida, y estos nuevos recursos deben ser eficientemente utilizados. Para conseguir este objetivo se ha definido un marco de trabajo acotado, que ha de permitir sentar unas bases de conocimiento de estos entornos. El marco de trabajo ha definido una arquitectura real, un modelo de programación basado en el paralelismo de datos y aplicaciones del tipo SPMD (Single Program Multiple Data). Se ha elegido el modelo de programación OpenMP en su versión 2.5, debido a su extensa utilización, su sencillez para expresar paralelismo y por ser un modelo que permite expresar el paralelismo de datos.

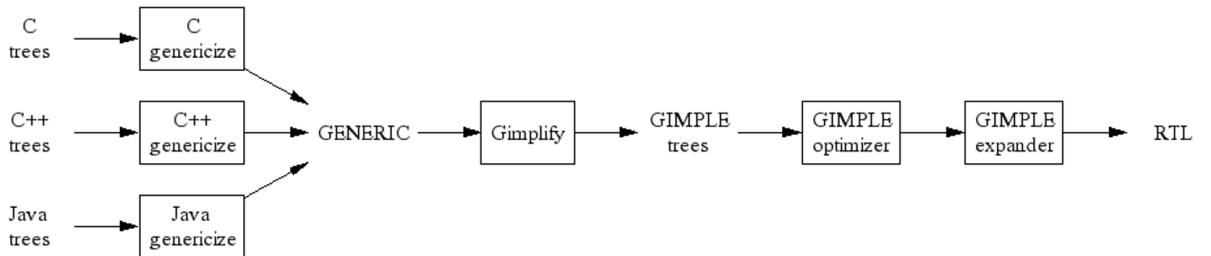

Una vez definido el marco se ha realizado un análisis de la implementación OpenMP de GNU. Esta implementación consiste en tres módulos, que son las directivas de precompilación, la librería en tiempo de ejecución (libgomp) y la API de bajo nivel de POSIX threads (pthread de GNU). Como resultado del análisis se han detectado varios factores OpenMP parametrizables que afectan al rendimiento, como son la gestión de la planificación en el reparto de cargas, el acceso concurrente a memoria y la influencia de localidad de los datos sobre una estructura de memoria jerárquica. Para evaluar estos factores se han seleccionados aplicaciones, adecuadas para cada uno de los factores, que reflejan la influencia en la ejecución de cada uno de ellos.

## 1.1. Contexto

El mundo de los microprocesadores ha sufrido una nueva revolución por causa de los procesadores multicore. Se ha diseñado un nuevo tipo de procesadores basados en la integración de dos o más unidades de proceso dentro de un mismo chip, el cual basa su aumento de prestaciones en la utilización de estrategias de paralelismo.

En el modelo anterior, los procesadores de un solo núcleo conseguían la mejora de prestaciones mediante el aumento de la frecuencia de reloj y aportes funcionales basados en estrategias como pipeline, cachés multinivel, branch prediction, unidades de cómputo superescalares, planificación estática (en orden), planificación dinámica (fuera de orden), etc.

Si una aplicación obtiene un tiempo de ejecución determinado en un entornos monocore, al aumentar la frecuencia de reloj de este procesador, por norma general el tiempo de ejecución se reduce de forma transparente al programador. Esto supone una gran ventaja ya que la aplicación es considerada una caja negra. Sin embargo, por razones técnicas ya no es posible seguir aumentando la frecuencia de reloj. La principal razón es el consumo, que se incrementa más que linealmente al aumentar la frecuencia y genera además problemas de disipación de calor; pero también existen límites físicos en los transistores MOS para frecuencias elevadas, que tienen un umbral máximo en la velocidad de comutación.

Por otra parte la capacidad de integración de transistores dentro del chip ha seguido aumentando, y estos nuevos recursos se han utilizado para crear copias de procesadores completos dentro de un mismo chip. Antes de llegar al modelo multicore han surgido algunos modelos que intentaban responder a la pregunta de ¿Cómo utilizar la alta capacidad de integración de transistores? Algunas de ellas:

- Incrementar el tamaño de la cache de segundo nivel, para mejorar los aciertos de cache. Sin embargo esta aproximación esta limitada por la cantidad de fallos de cache. Si la mitad de los ciclos son utilizados en esperas debidas a fallos de cache de segundo nivel, doblar la capacidad de esta memoria no puede conseguir más que una disminución del tiempo de ejecución a la mitad. Por otra parte, aumentar la cache de nivel 1 es inviable debido a que fuerza una reducción de la frecuencia de reloj.

- Explotar el paralelismo a nivel de instrucción, mediante la adición de las unidades funcionales. Sin embargo la limitación de este modelo reside en la cantidad limitada de instrucciones sensibles de ser paralelizables.

- Diseños de core capaces de ejecutar múltiples instrucciones de diferentes hilos de ejecución, mientras por otra parte se explota el ILP de cada thread,

- Explotación de recursos para la integración de múltiples procesadores dentro de un mismo chip (multicore).

A partir de esta última opción surgen las tecnologías multicore, y de esta forma los desarrolladores de hardware pretenden conseguir la meta de cumplir las expectativas de la Ley de Moore [1], basada en doblar las prestaciones cada 18 meses. No obstante, la percepción del usuario final es que no siempre se consigue un aumento en las prestaciones, ya que las aplicaciones no están respondiendo a este patrón de mejora.

Debido al aumento en el número de cores por chip, se dispone de más recursos que han de permitir aumentar las prestaciones, y para explotar estos recursos se deben utilizar estrategias de paralelismo y concurrencia. Sin embargo al utilizar estrategias de paralelismo, el rendimiento puede verse afectado por la fracción no paralelizable de la aplicación, tal como indica la ley de Amdahl [2]. El campo del paralelismo ha sido ampliamente estudiado en el ámbito de Computación de Altas Prestaciones (HPC-High Performance Computing), por lo que las estrategias utilizadas en HPC pueden trasladarse ahora a nivel de un procesador con múltiples cores. La primera consecuencia de este hecho es que las aplicaciones ya no pueden ser consideradas como una caja negra, en un entorno paralelo es necesario conocer la aplicación para poder sintonizarla y obtener el mejor rendimiento.

No obstante, aunque la ley de Amdahl especifica el límite de paralelización, normalmente será relevante sólo si la fracción serie es proporcional al tamaño del problema, esto raramente es así en aplicaciones HPC, afortunadamente como define la ley de Gustafson [3] la proporción de los cómputos secuenciales (no paralelos) normalmente decrece según el tamaño del problema se incrementa. Por tanto, sí podemos utilizar paralelismo en entornos HPC aprovechando los recursos multicore.

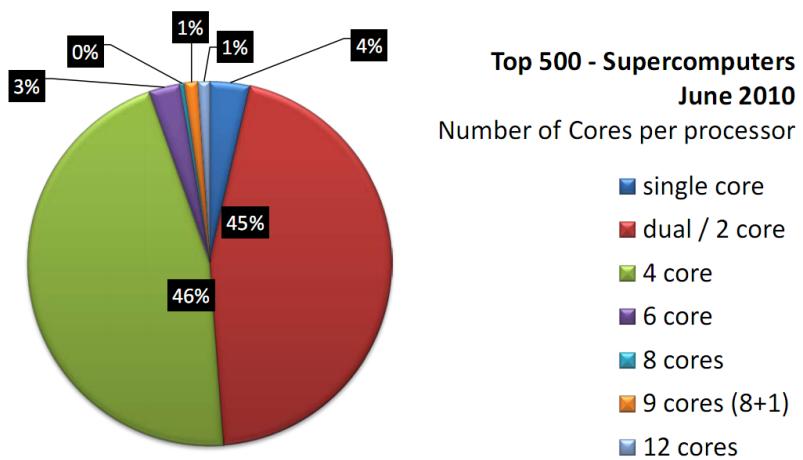

Actualmente los procesadores multicore están ampliamente implantados, desde equipos de sobremesa hasta en sistemas HPC (High Performance Computing). En la gráfica 1.1 se refleja el grado de implantación en los 500 supercomputadores más potentes de la actualidad para la lista del Top500 de Junio de 2010 [4], donde no únicamente los mejores supercomputadores disponen de sistemas multicore: Jaguar (Opteron 6 cores),[5], Nebulae (Intel Xeon 6 cores and Nvidia Tesla GPU)[6], Road Runner (PowerXCell 8i, 8+1 cores) [7], Kraken (Opteron 6 cores) [8], sino que el 96 % de estos computadores disponen de procesadores multicore. Por tanto únicamente 20 su-

percomputadores disponen de otras arquitecturas de procesador como single core o procesadores vectoriales, como por ejemplo el Earth Simulator de Japón (procesador vectorial NEC @ 3200 MHz) [9].

La utilización de estos procesadores plantea varias preguntas al respecto, ¿están siendo eficientemente utilizados?, ¿existe un aumento lineal en el rendimiento? o ¿cómo afecta al consumo del sistema?.

Las métricas utilizadas en entornos multicore tienen diferentes motivaciones: el consumo es un factor a tener en cuenta en sistemas de HPC cuando pretendemos optimizar la potencia consumida respecto al tiempo de ejecución, existe un campo centrado en este problema, el GreenComputing; La eficiencia nos indica si los recursos están siendo utilizados, es decir si para el coste de inversión de una máquina, sus recursos están siendo eficientemente utilizados; el rendimiento de una aplicación entendido como el tiempo de ejecución de la misma.

Normalmente al utilizar paralelismo se debe gestionar la concurrencia de los medios compartidos. es una necesidad el aprovechamiento de los recursos multicore, pero ¿Deben ser los programadores de aplicaciones, los diseñadores de sistemas operativos o los arquitectos hardware? Por eso se debe marcar una ruptura en el mundo de la computación y entrar plenamente en la era del reto multicore.

Hay que destacar que existe una gran brecha entre el estado de desarrollo hardware y software, en general el hardware está más avanzado que las herramientas software que los explotan. Sin embargo, el campo del paralelismo no empieza desde cero, se han heredado modelos y herramientas existentes en HPC. En particular, el modelo multicore actualmente se enmarca dentro del modelo de memoria compartida, debido a la arquitectura de los procesadores actuales, y correspondiendo a la taxonomía de Flynn [10] corresponde a un modelo de MIMD (Multiple-Instruction Multiple-Data), aunque en revisiones más recientes de la taxonomía se ha creado una extensión llamada SMP (Symmetric Multi-Processing), que corresponde a un modelo donde múltiples procesadores trabajan de forma conjunta. No obstante este modelo de procesadores multicore es dependiente de la tecnología actual, y no sabemos cómo van a evolucionar los procesadores, o si éstos van a continuar con este modelo.

## 1.2. Motivación

En la figura 1.1 se muestra el grado de implantación de procesadores multicore en los mejores sistemas de HPC. Se ha obtenido la información de la lista Top500 de Junio de 2010. Podemos

Figura 1.1: *Utilización de tecnologías Multicore en sistemas HPC. Lista Top500 Junio 2010*

observar como únicamente un 4 % de los Supercomputadores mantienen procesadores de mononúcleo y en cambio el resto utilizan procesadores de multicore.

Como los entornos de HPC integran procesadores multicore, es necesario que las aplicaciones HPC tengan conciencia de la arquitectura hardware del procesador. El tiempo de ejecución dependerá de la arquitectura hardware y de cuán eficientemente se utilicen los recursos. Además el comportamiento de la aplicación normalmente depende de los datos de entrada. Por este motivo, una aplicación debe adaptarse a la arquitectura y a los datos, es decir, ser sintonizada de acuerdo a sus características y a las del entorno en el que se ejecuta. Dicha sintonización puede realizarse antes de la ejecución, durante la ejecución (dinámicamente) o después de la ejecución, dependiendo de las características de la propia aplicación.

La definición de un modelo de rendimiento para entornos multicore supone una predicción del comportamiento de una aplicación. Para la creación de esta predicción resulta necesario caracterizar el comportamiento de la aplicación y la arquitectura hardware. Conociendo estos parámetros se puede inferir en puntos específicos de la aplicación, del hardware o en la capa que interconecta y gestiona estos dos elementos, el modelo de programación. Este proceso de sintonización necesita por tanto la definición de un modelo de rendimiento y debe aportar una metodología que permita adaptar la aplicación basada en la predicción del modelo de rendimiento.

### 1.3. Objetivos

El principal objetivo de esta tesina consiste en sentar las bases para la definición de un modelo de rendimiento en entornos multicore. Para la definición de un modelo de rendimiento se necesita

caracterizar la aplicación y la arquitectura. En el ámbito de esta tesina se pretenden caracterizar factores que afectan al rendimiento en entornos multicore, que han de permitir obtener indicadores de cómo se adapta la aplicación a un entorno multicore en un momento determinado de su ejecución.

Debido a la diversidad de elementos que intervienen en las aplicaciones multicore se ha definido un marco de trabajo acotado. De esta forma se pueden caracterizar tanto la aplicación como la arquitectura hardware. En este marco se definen los parámetros sintonizables de un modelo de programación que permita adaptar de la mejor forma posible una aplicación en un entorno multicore.

Una vez detectados los factores que afectan al rendimiento se evalúan en tiempo de ejecución para cada uno de los parámetros sintonizable del modelo de programación.

Situados en el contexto de los entornos multicore se describen a continuación los actuales objetivos de estudio desarrollados en este documento.

El objetivo de esta tesina es el estudio de los factores que afectan al rendimiento en entornos multicore. Descritos los factores se analizarán los parámetros que permitan la sintonización de aplicaciones paralelas. Los actores que intervienen en el rendimiento son la aplicación paralela, la arquitectura hardware y el paradigma de programación paralela.

- Como paradigma de programación paralela se ha elegido OpenMP por ser el estándar de facto en entornos de memoria compartida, por su capacidad de expresar el paralelismo de forma sencilla.

- Se han desarrollado dos toy benchmarks (Multiplicación de Matrices) y una benchmark de aplicación real basada en la segmentación de imágenes de resonancia magnética. Los tres benchmarks implementados corresponden a una aplicación con paradigma SPMD (Single Program Multiple Data).

- Las arquitectura disponible para la experimentación es una estación de trabajo con procesador Intel Core2Duo

En resumen, el contexto descrito indica la existencia de múltiples ámbitos en los que es necesario investigar para hacer frente a los retos planteados.

## 1.4. Trabajos Relacionados

Existen en la literatura gran cantidad de grupos investigando sobre el rendimiento de diferentes modelos de programación. En esta sección se introducen algunos de los trabajos más relevantes relacionados con esta Tesina.

La unidad de ejecución en entornos de memoria compartida, y como consecuencia en entornos multicore, son los threads. En los sistemas operativos existen dos claros niveles de implementación, los threads nivel de usuario y los threads del kernel. Los primeros tienen la ventaja de ser hilos muy ligeros y gestionados por un planificador a nivel de usuario, por el contrario los threads de kernel se gestionan por el planificador de sistema operativo. A la hora de utilizar unos u otros se debe tener en cuenta el rendimiento. En [11] se evalúa el rendimiento entre threads a nivel de kernel y threads a nivel de usuario. En el documento se resuelve que los threads a nivel de kernel tienen un rendimiento significativamente peor. Como conclusión se refleja cuán esencial es en HPC la utilización de threads a nivel de usuario. Existen en diversos grupos de investigación diferentes implementaciones propias de librerías que implementan threads a nivel de usuario. El nanos group del BSC (Barcelona Supercomputing Center) tiene su propia librería de threads, originalmente nanothreads, Nanos4 [12], una implementación de lighthead threads a nivel de usuario que dan soporte a diferentes lenguajes de programación. En el LaBRI (Laboratoire Bordelais de Recherche en Informatique) del INRIA han desarrollado otro modelo de librería de threads de nivel de usuario llamada Marcel [13], con un interfaz compatible con POSIX y un modelo de threads M:N (M threads de usuario asignados a N threads de kernel). En la librería Marcel hay que destacar el planificador BubbleSched que permite gestionar dinámicamente la asignación de threads sobre procesadores heterogéneos. El framework de BubbleSched permite que los desarrolladores creen su propia política de planificación así como de depuración ya que proporciona herramientas de rastreo (tracing tools).

No obstante, se considera que la programación con threads en aplicaciones paralelas es una programación a bajo nivel. Existen otros modelos de programación que abstraen la creación, gestión y eliminación de threads. Uno de los modelos más extendidos es OpenMP, que permite definir el paralelismo de una aplicación de forma bastante sencilla. En la literatura existen muchos estudios sobre el rendimiento obtenido con este modelo de programación paralela en diferentes arquitecturas de memoria compartida. En [14] se han evaluado diferentes benchmarks de OpenMP como el paquete de microbenchmarks OpenMP del EPCC (Edinburgh Parallel Computing Center) [15], NAS Parallel Benchmarks (NASA Advanced Supercomputing) [16] y SPEC (SPEC

OMPL2001) [17]. En este estudio se ha evaluado la ejecución de estos benchmarks sobre una máquina Sun Fire 15K SMP, con soporte de 72 a 102 procesadores y procesadores UltraSPARC III a 900MHz. En el estudio se utilizan los EPCC benchmarks para evaluar los overheads en la utilización de diferentes directivas OpenMP sobre un diferente número de threads (6,12,24,48,64 y 70) ejecutados en la máquina Sun Fire 15K. Sobre los benchmarks de aplicación de NAS y SPEC se evalúa la escalabilidad del sistema Sun Fire 15K. En este documento se concluye que el sistema escala bien en 5 de los 7 benchmarks evaluados del SPEC OMPL2001. Sobre el conjunto de NAS, se ha evaluado la clase B de los benchmarks CG con escalabilidad superlineal, LU con una escalabilidad perfecta (menos para 70 threads), los BT, SP i MG muestran un relativo buen rendimiento, y el rendimiento conseguido en FT resulta muy pobre. Con el paquete de microbenchmarks de EPCC han proporcionado una visión de escalabilidad de las directivas individuales de OpenMP y se ha medido el overhead de utilización de las directivas, para estimar el sobrecoste en benchmarks de aplicación como los SPEC OMPL2001, comprobando que el sobrecoste de utilización es muy pequeño, apenas representando el 1 % del tiempo de ejecución, con la excepción del CG del NAS, donde el overhead por la utilización de OpenMP alcanza un sobrecoste estimado del 12 %.

El modelo de programación OpenMP corresponde a arquitecturas de memoria compartida, y estas arquitecturas normalmente permiten poca escalabilidad, por tanto son muy comunes los estudios que evalúan arquitecturas con diferentes niveles de programación. Los nodos con modelos SMP (Symmetric Multi Processing) y de colaboración entre nodos en una arquitectura distribuida utilizando el modelo de programación MPI (Message Passing Interface) [18]. Por otro lado se puede simular un modelo de memoria compartida dentro de un sistema distribuido a través de una capa de software. El modelo de Software Distributed Shared Memory es evaluado en [19] sobre un modelo de programación OpenMP. Para la evaluación del modelo SDSM se han utilizado dos benchmarks NAS (EP y CG) y el Ocean Kernel del Splash2 benchmark suite [20]. En este estudio se proponen técnicas para mejorar el prefetching de páginas de memoria en regiones iterativas paralelas, detectando a qué páginas accede cada iteración y replanificando las iteraciones para favorecer la localidad espacial y temporal. Como conclusiones del estudio, se indica que algunas aplicaciones de benchmark consiguen un buen speedup, mientras que las que no consiguen un buen speedup tampoco consiguen mejoras en otros sistemas DSM. Por tanto, se concluye la necesidad de replantear algunos conceptos del sistema para mejorar el balanceo de carga, que resulta ser el factor que más está afectando al rendimiento.

Tal como se ha reflejado anteriormente OpenMP ha sido evaluado en numerosas arquitecturas. OpenMP es un modelo de programación que permite la definición de regiones de trabajo que se

van a ejecutar de forma paralela. Esta sección paralela es ejecutada con un patrón de tipo fork-join. En las nuevas revisiones de OpenMP se han creado nuevas funcionalidades como la definición de regiones paralelas anidadas o, ya más recientemente, con la inclusión de un modelo de programación funcional mediante la definición de tareas (Tasks) ejecutadas sobre un modelo DAGs (Grafos Acíclicos Dirigidos). En [21] se ha realizado un estudio de los sobrecostes obtenidos en la utilización de OpenMP con paralelismo anidado de regiones paralelas. La máquina utilizada para la evaluación ha sido un servidor Compaq Prolian ML570 modelo SMP con 4 procesadores Intel Xeon III single-core. En este estudio se ha evaluado la implementación de diferentes compiladores sobre la funcionalidad de paralelismo anidado. Los compiladores evaluados son algunos de los más extensamente utilizados como Intel C Compiler (ICC), Sun C Compiler (SUNCC), GCC (GNU C Compiler) y también los compiladores source-to-source Omni Compiler y OMPI. Este último permite la utilización de diferentes librerías de threads, por tanto se ha evaluado para diferentes librerías de threads, la primera es la librería por defecto basada en POSIX threads y la segunda un librería de threads de alto rendimiento basada en POSIX threads gestionados a nivel de usuario. El benchmark utilizado ha sido el EPCC. En cuanto a las conclusiones, se han evidenciado problemas de escalabilidad en la utilización del paralelismo anidado, si el número de threads creados aumenta respecto al número de procesadores disponibles. Se sugiere, que el modelo de threads a nivel de kernel utilizado en la mayoría de implementaciones, está generando una sobrecarga en la librería de tiempo de ejecución. Cuando el número de threads compitiendo por los recursos hardware excede significativamente el número de procesadores, el sistema se sobrecarga y los overheads de paralelización sobrepasan cualquier beneficio en el rendimiento esperado. La experimentación se ha limitado a dos niveles de anidamiento, quedando claro que añadir subniveles de anidamiento únicamente empeoraría la situación.

Cada implementación del modelo OpenMP tiene ciertas singularidades, ya que para la misma aplicación utilizando diferentes compiladores el tiempo de ejecución puede ser significativamente diferente. En [22] se evalúa el compilador de investigación OpenUH [23]. Este compilador es open source e implementa el modelo OpenMP v2.5, consiste en un compilador source-to-source que genera código C o Fortran77 portable entre plataformas. En este documento se evalúan las diferentes primitivas OpenMP para la sincronización de threads mediante el microbenchmark syncbench del paquete EPCC. Se han desarrollado diferentes implementaciones de las primitivas de barrera utilizando modelos clásicos [24] de la literatura como son las barreras centralizadas bloqueantes, barreras centralizadas, barreras diseminadas, barreras en árbol y barreras de torneo. Por tanto en este documento se refleja la afectación al rendimiento de las diferentes interpretaciones del estándar

OpenMP. Estos modelos se han evaluado en dos benchmarks kernel, el Additive Schwarz Preconditioned Conjugate Gradient (ASPCG), y el Generalized Incompressible Direct and Large-Eddy Simulations of Turbulence (GenIDLEST), ambos ejecutados con hasta 128 threads.

Si hasta ahora hemos visto estudios comparativos entre las diferentes implementaciones software respecto a una arquitectura común, existen estudios que intentan explotar las capacidades de la utilización de librerías que tienen en cuenta las arquitecturas multicore. En este grupo tenemos los modelos del BSC que consiguen explotar diferentes modelos de multiprocesadores, los Star Superscalar (\*Ss). Están basados en el compilador Mercurium que es un compilador source-to-source desarrollado por el NANOS group del BSC. Se ha generado un entorno para diferentes tipos de arquitecturas multicore. SMP SuperScalar está orientado a la optimización en entornos SMP [25], CellSs para los procesadores CellBE de IBM [26], GPUSs para entornos híbridos con CPU + GPU (Graphical Processing Units)[27]. El modelo StarSs se define en un modelo de paralelismo de tareas mediante DAGs y se ha planteado como unas extensiones del estándar OpenMP que son interpretadas por el compilador mercurium. Cada modelo de StartSs tiene en cuenta las características de la arquitectura hardware subyacente.

En estos trabajos se puede observar la importancia de caracterizar la arquitectura hardware. Las arquitecturas multicore son muy diversas y están en constante evolución, hemos pasado de arquitecturas dual core, modelos con poca complejidad de interconexión basada en un medio compartido y jerarquías de memoria, modelos sencillos de implementar pero que no proporcionan mucha escalabilidad, hasta modelos más elaborados como los procesadores Cell de IBM que integran hasta 9 cores en un chip, para los cuales se ha diseñado una red de interconexión en anillo que proporciona una mayor escalabilidad. Por tanto si hablamos de multicore hay que hablar de escalabilidad de los cores, y los problemas problemas de rendimiento son diferentes en procesadores con unidades de cores y procesadores con cientos o miles de cores. Se debe modelar una teoría o modelo de rendimiento sobre los sistemas concurrentes que considere las propiedades esenciales de los nuevos modelos de procesadores en la era de la revolución multicore [28], [29].

## 1.5. Estructura del Documento

En cuanto a la estructura del documento, en la **sección 2** se expone el contexto de los *Entornos Paralelos de HPC*, que es el ámbito dónde se desarrolla esta investigación, explicando las diferentes arquitecturas, modelos de programación y aplicaciones paralelas HPC.

En la **sección 3** se entra en detalle en las *Entornos Multicore*. Se reflejan las diferentes características de los modelos actuales de procesadores multicore.

En la **sección 4** entramos a definir un *Marco de Trabajo* acotado sobre el cuál se van a desarrollar las características más importantes de arquitectura, modelo de programación y aplicación.

La **sección 5** consiste en un *Análisis de los Factores de Rendimiento* detectados en el marco de trabajo y sobre los cuales se ha desarrollado la experimentación que ha permitido evaluar el impacto de cada uno de ellos.

Para finalizar, la **sección 6** refleja las *Conclusiones* del trabajo de investigación sobre los factores de rendimiento en entornos multicore, que ha de sentar las bases para el desarrollo de Tesis para la definición de un modelo de rendimiento en entornos multicore.

## Capítulo 2

# Entornos Paralelos de HPC

En este capítulo vamos a fijar el marco general de la investigación, que se ubica en un entorno de High Performance Computing. El ámbito de HPC esta centrado en la resolución de grandes problemas de cálculo científico que requieren una gran cantidad de cómputo y que utilizan estrategias de paralelismo para su resolución. Por tanto, para aquellos problemas que no pueden ser resueltos secuencialmente en un tiempo razonable, se utilizan múltiples recursos trabajando en paralelo de forma coordinada. Aplicaciones de múltiples campos científicos (biología, física, criptografía, inteligencia artificial, astronomía, astrofísica, etc.) tienen grandes necesidades de cómputo para la resolución de problemas de simulación y predicción de modelos climáticos, dinámica molecular, cromodinámica cuántica, simulaciones para la predicción de incendios forestales, etc.

En el entorno de HPC se deben tener en cuenta tres factores que actúan de forma combinada, estos son: la arquitectura del computador paralelo, el modelo de programación utilizado que permite explotar los recursos del computador y las características de la aplicación ejecutada en este entorno. A continuación se exponen diferentes sistemas HPC, explicando sus principales características, con el objetivo de situar los sistemas multicore dentro de las arquitecturas HPC, explicar los modelos de programación existentes en HPC para identificar un modelo adecuado para entornos multicore y los paradigmas de las aplicaciones HPC. Por último, se detallan metodologías y herramientas dedicadas a mejorar el rendimiento de aplicaciones paralelas, de ellas se identificar aquellas herramientas que han de permitir medir factores de rendimiento en entornos multicore, y se expone la dificultad y necesidad en la definición un modelo de rendimiento específico para entornos multicore.

## 2.1. Arquitecturas paralelas

Se debe tener en cuenta la arquitectura del computador ya que su naturaleza determina el tipo de cálculos, la cantidad de recursos de cómputo o la capacidad de paralelismo. Si tenemos que clasificar las arquitecturas podemos referir una visión general mediante la taxonomía de Flynn [10]. Esta taxonomía considera cuatro tipos de arquitecturas.

- SISD (Single Instruction, Single Data stream), este modelo no explota el paralelismo. Correspondiente a un modelo de monoprocesador.

- MISD (Multiple Instruction, Single Data stream), este modelo se utiliza en situaciones de paralelismo redundante, por ejemplo en sistemas duplicados para soportar Tolerancia a Fallas.

- SIMD (Single Instruction, Multiple Data stream), un procesador explota varios flujos de datos dentro de un único flujo de instrucciones para realizar operaciones que pueden ser paralelizadas de manera natural, por ejemplo, un procesador vectorial, como por ejemplo ILLIAC IV o hasta los actuales modelos de programación de propósito general que explotan los recursos vectoriales de las GPUs (Graphical Processing Units).

- MIMD (Multiple Instruction, Multiple Data stream), varios procesadores autónomos ejecutan simultáneamente instrucciones diferentes sobre conjuntos de datos diferentes.

De esta clasificación podemos relacionar las arquitecturas tipo con las arquitecturas reales existentes en la actualidad. Las arquitecturas SISD equivalen a un procesador mononúcleo y las MIMD con procesadores paralelos. Si bien el modelo MIMD encaja con los procesadores multicore, esta es una afirmación muy bastante general, así, las arquitecturas MIMD podemos clasificarlas en dos subtipos.

- Sistemas de Multicomputadoras de memoria distribuida. Estos sistemas están compuestos por nodos de procesamiento independientes, cada nodo con su propio espacio de memoria (NO Remote Memory Access), que trabajan de forma conjunta intercambiando información mediante una red dedicada de altas prestaciones como en los modelos MPP (Massive Parallel Processor), una red de comunicaciones de bajas prestaciones y alcance limitado (Clúster) o de jerarquía de redes con alcance de larga distancia (Grid). Estos modelos utilizan modelos de programación basados en el paso de mensajes como por ejemplo MPI o PVM.

- Sistemas de Multiprocesador de memoria compartida, en estos sistemas los procesadores tienen una visión global del espacio de memoria, estos sistemas pueden clasificarse a su vez como:

- UMA (Uniform Memory Access), en estas arquitecturas el tiempo de acceso a cualquier posición de la memoria tendrá la misma latencia. Corresponden a este modelo las arquitecturas PVP (Parallel Vector Processors) y SMP (Symmetric Multi Processors)

- NUMA (Non Uniform Memory Access), donde el tiempo de acceso dependerá de la localidad de los datos. Utilizan una capa DSM (Distributed Shared Memory) que puede estar implementada mediante hardware o software. Corresponden a este modelo COMA (Cache Only Memory Architecture), CC-NUMA (Cache Coherent) y NCC-NUMA (Non Cache Coherent)

## 2.2. Modelos de programación paralelos

Los modelos de programación paralelos permiten al usuario definir la utilización de los recursos paralelos y expresar el paralelismo de la aplicación. Para que un modelo de programación tenga éxito el modelo debería cumplir las siguientes características [30]:

1. **Fácil de programar.** Debe permitir al programador representar fácilmente la descomposición del problema, la asociación de threads a los procesadores, la comunicación y la sincronización entre threads.

2. **Proporcionar una metodología de desarrollo**, para incluir el paralelismo en la semántica del programa, así como técnicas de transformación.

3. **Independencia de la arquitectura**, para permitir la portabilidad del programa entre máquinas.

4. **Fácil de entender**, para facilitar la reutilización de código.

5. **Garantizar rendimiento**. Garantizar una buena ejecución sobre diferentes arquitecturas

La forma en que los modelos de programación paralela expresan el paralelismo se pueden clasificar según la granularidad de la región paralela:

### 2.2.1. Paralelismo de aplicación

Modelo de alta granularidad. El paralelismo a nivel de aplicación tiene independencia de datos entre aplicaciones. Éste ámbito está más orientado a sistemas de HTC (High Throughput Computers), donde la métrica de referencia es el throughput, es decir la cantidad media de trabajos servidos por unidad de tiempo para todo el sistema.

### 2.2.2. Paralelismo funcional

De granularidad media, el paralelismo de funcional (o de tareas) se centra en la distribución de procesos de ejecución entre los diferentes nodos de cómputo. En cuanto a los lenguajes de programación de tareas existen Cilk, Cilk++, y OpenMP en la versión 3.0.

### 2.2.3. Paralelismo de datos

Este paralelismo es de granularidad fina, las regiones paralelas dependen de los datos de entrada, como por ejemplo en regiones de bucles iterativos. El paralelismo de datos se centra en la distribución de los datos entre los diferentes nodos de cómputo y puede permitir anidamiento de regiones paralelas. Este modelo supone tres etapas de ejecución, el primero consiste en la descomposición y repartición de datos, el segundo es la replicación de tareas y ejecución paralela sobre el subconjunto de datos, y el tercero es la sincronización y actualización de datos entre los diferentes procesos. Existe gran diversidad de lenguajes de programación paralelos que explotan este tipo de paralelismo, los lenguajes explícitos de threads como POSIX Threads o JAVA threads, o implícitos como OpenMP v2.5,

## 2.3. Aplicaciones Paralelas

En la programación de aplicaciones paralelas se debe caracterizar el comportamiento de la aplicación, es decir, identificar las necesidades de paralelismo en el algoritmo. Afortunadamente la mayoría de las aplicaciones científicas presentan un comportamiento que puede clasificarse dentro de un conjunto reducido de patrones de comportamiento. Cada uno de estos patrones de comportamiento se puede identificar con un paradigma de programación paralela como por ejemplo: Master-Worker, SPMD (single program multiple data), pipeline y divide and Conquer.

### 2.3.1. Paradigmas de Programación Paralela

La clasificación de patrones de aplicaciones paralelas engloba a la mayoría de aplicaciones paralelas existentes. Entre los paradigmas de programación paralela más conocidos tenemos:

#### 2.3.1.1. Master-Worker

Este paradigma se compone de dos elementos, el máster y los workers. El máster se encarga de dividir las tareas y distribuir las cargas de trabajo. Los workers son entidades que reciben la información, la procesan y devuelven los resultados al máster. En este paradigma la repartición de carga se puede realizar de forma estática o dinámica. La repartición estática distribuye la totalidad de la carga sobre el conjunto de workers. En la repartición dinámica se asignan divisiones de los trozos de carga a los workers y cuando éstos finalizan el cómputo, el Máster asigna más carga disponible hasta completar toda la carga de trabajo.

Existe un overhead debido a la gestión de comunicación entre el máster y los workers, y en el caso de ser un sistema de memoria distribuida un overhead debido a la comunicación de las cargas de trabajo.

#### 2.3.1.2. SPMD

Este patrón Single Program Múltiple Data tiene dos características a evaluar, el programa y los datos. Cada nodo del sistema paralelo va a ejecutar el mismo programa sobre una descomposición del conjunto de datos de entrada. Sin embargo, puede existir una dependencia de datos entre los diferentes nodos, que hará necesaria la existencia de comunicaciones entre nodos para resolver las dependencias. Por lo tanto, existe una necesidad de sincronismo entre los procesos que puede ser resuelta mediante paso de mensajes, en entornos distribuidos, o mediante la definición de secciones críticas, en entornos de memoria compartida.

Por tanto la barrera de sincronización viene determinada por el nodo más lento y puede existir un desbalanceo de carga. Se pueden aplicar estrategias de planificación para minimizar este desbalanceo.

#### 2.3.1.3. Pipeline

El paralelismo de este tipo de paradigma está basado en la descomposición funcional del problema, por tanto se deben identificar las subtareas del algoritmo, que pueden ser ejecutadas de forma paralela. Cada una de estas etapas funcionales tiene dependencia de datos con la etapa an-

terior. Cada etapa alimenta a la siguiente, y los patrones de comunicación pueden ser síncronos o asíncronos. La eficiencia de ejecución de éste paradigma depende del balanceo de carga en cada una de las etapas del pipeline, ya que la etapa más lenta acostumbra a determinar el tiempo de ejecución de la aplicación.

#### 2.3.1.4. Divide and Conquer

En este paradigma, los problemas son subdivididos en subproblemas, lo cual permite que cada una de esta subdivisiones pueda ser resuelta independientemente. Al finalizar la ejecución se integran todos los resultados que corresponderán al resultado final de la aplicación. En el proceso de partición, distribución y reensamblado se utilizan los recursos paralelos. La estructura de ejecución del programa tiene forma de árbol, ya que el proceso raíz subdivide el trabajo para los  $N$  recursos y asigna a cada una de las  $N$  ramas una carga de trabajo, donde cada una de estas ramas subdividirá el trabajo de forma recursiva.

### 2.4. Monitorización, Análisis y Sintonización

Los modelos de rendimiento son modelos matemáticos que permiten evaluar costes de alternativas de diseño de las aplicaciones, que deben permitir explicar observaciones de comportamiento, predecir circunstancias futuras o abstraer un sistema. Los factores que intervienen en un modelo de rendimiento definen la precisión del modelo y deben incluir características de la aplicación tales como el paradigma de programación utilizado, la carga de trabajo o precisión del modelo de programación tales como la granularidad, y de la arquitectura tales como factores de latencias de memoria, latencias de cálculo, etc. Debido a la dificultad de generar un modelo de rendimiento general, es posible crear un modelo de rendimiento para un entornos específicos, como por ejemplo para un paradigma de programación paralela sobre un tipo de arquitectura determinada. Por eso, en [31] se define un modelo de rendimiento para aplicaciones de tipo Master-Worker.

Teniendo definido un modelo de rendimiento se puede adaptar el sistema a las necesidades específicas de la aplicación. Esta solución puede resultar económicamente costosa si se requiere la adquisición de nuevo hardware, o al revés, el modelo puede permitir adaptar la aplicación a los recursos del sistema disponible, solución costosa en cuanto a recursos humanos por la necesidad de reprogramación de la aplicación para adaptarla al sistema. Sin embargo, es posible utilizar técnicas de sintonización de aplicaciones, que permiten que una aplicación sea portable entre sistemas, ya que la sintonización ha de permitir adaptar la aplicación a los recursos disponibles.

Para generar una estimación de comportamiento de la aplicación en un momento determinado, el modelo de rendimiento necesita conocer los parámetros de rendimiento de la aplicación. Para obtener esta información se pueden utilizar diferentes herramientas de análisis de rendimiento.

En general, la mejora de rendimiento de aplicaciones paralelas requiere tres fases principales: la monitorización, el análisis y la sintonización.

Existen herramientas para la monitorización, que insertan código de instrumentación en la aplicación, que generará un fichero con información sobre el tiempo de ejecución, contadores, muestreo o eventos. Los aplicaciones de monitorización pueden o bien mostrar trazas de ejecución, o como los profilers, ofrecer resúmenes de los valores de muestreo. Existen diferentes herramientas de monitorización, generales como el profiler gprof [32], más específicas como POMP [33] o ompp [34], que son profilers para aplicaciones OpenMP. La herramienta ompp permite obtener información para cada thread de ejecución, como tiempo de ejecución, el grafo de llamadas. También permite la integración del interface PAPI (Performance Application Program Interface) [35] que permite monitorizar contadores hardware reales del procesador, como fallos/aciertos de cache, operaciones en punto flotante,etc.

El análisis del comportamiento de la aplicación puede realizarse antes de su ejecución, por ejemplo durante la compilación; después de la ejecución, basada en trazas generadas durante la monitorización; o en tiempo de ejecución, adaptando dinámicamente la aplicación a las condiciones actuales de ejecución.

Las herramientas de análisis clásico (post-mortem), utilizan las trazas para, mediante una base de conocimiento, mostrar los problemas de rendimiento. Las herramientas MPICL [36], Para-Graph [37], Pablo [38], Vampir, VampirServer o VampirTrace [39] [40] son ejemplos de herramientas de análisis post-mortem.

Las herramientas de análisis automático, detectan los problemas de rendimiento y ofrecen sugerencias al usuario. Las herramientas Scalasca [41], Periscope [42], Tau [43], Paraver [44] y Dimemas [45] o KappaPi [46] son ejemplos de herramientas que generan un análisis automático post-mortem basado en información de monitorización.

Las herramientas de análisis dinámico (en tiempo de ejecución) permiten instrumentar la aplicación de forma dinámica obteniendo información específica en tiempo de ejecución. La herramienta Paradyn [47] es la única que genera un análisis dinámico.

En cuanto a herramientas de sintonización, éstas son capaces de monitorizar y analizar dinámicamente la aplicación para adaptarla al sistema. Las herramientas Autopilot [48], Active Harmony [49], Perco [50] y MATE [51] permiten sintonizar aplicaciones.

## Capítulo 3

# Entornos Multicore

En este capítulo se describen las características de los sistemas multicore existentes, y se plantean algunas tendencias de desarrollo futuro de estos sistemas.

En la actualidad, podemos encontrar procesadores multicore en estaciones de trabajo, portátiles, sistemas de HPC (ya que utilizan componentes genéricos para abaratar el coste), y también en sistemas empotrados. Los procesadores multicore representan el nuevo modelo tecnológico que debe permitir escalar las prestaciones en el futuro. Actualmente, en la denominada era multicore, disponen de un número pequeño de cores y la escalabilidad se consigue utilizando estrategias ad hoc. Sin embargo, al aumentar cada vez más el número de cores, gracias a las capacidades de integración de los transistores, se plantea un problema acerca del diseño de la arquitectura de los cores. Los chips monocore aplicaban estrategias de pipelining, branch prediction, etc, y estas estrategias eran implementadas físicamente utilizando circuitos lógicos que consumen transistores y espacio en el chip. Los primeros sistemas multicore básicamente duplicaban un sistema monoprocesador dentro de un mismo chip agregando una pequeña lógica de control y obteniendo así un sistema dual. Si pretendemos escalar el número de cores, cientos o miles, el espacio dentro del chip supone un problema y la arquitectura interna de los cores debe ser replanteada ¿que beneficio obtenemos de los complejos módulos de microarquitectura respecto al aumento de la escalabilidad de cores más simples? Los novedosos modelos de sistemas multicore que integran decenas de cores utilizan la segunda estrategia, cores menos potentes pero con un número mayor de ellos.

Como consecuencia podemos intentar incluir el máximo número de cores posibles dentro de un chip, y suponer que las prestaciones van a aumentar de forma lineal. Sin embargo, esto no es así, existe un problema a la hora de escalar el número de cores, debido a unidades compartidas, como buses, memorias cache o interficies compartidas para el acceso a memoria principal. En [52] Anant Agarwal plantea la KILL Rule, que sugiere que los recursos de un sistema multicore deben

ser incrementados sólo si por cada 1 % de incremento del área del core se obtiene al menos un 1 % de aumento de rendimiento, por tanto al pretender aumentar el recurso debemos mejorar las prestaciones, de lo contrario “*Kill if Less than Linear*”.

A continuación mostramos una clasificación de algunos componentes de los procesadores multicore, como diferentes planteamientos de diseño, que han de permitir aumentar la escalabilidad de los sistemas CMP. Gracias a avances tecnológicos como las arquitecturas de procesadores y memorias 3D se consigue un mayor integración y cercanía entre componentes que reducen la latencia en las comunicaciones. Por tanto, gracias a nuevos diseños que permiten mayor escalabilidad y la alta capacidad de integración, podemos afrontar la próxima era tecnológica de los procesadores, manycore.

### 3.1. Arquitectura de los cores

Una forma de clasificar los procesadores multicore depende de la arquitectura interna de los cores, ya que la funcionalidad de estos módulos puede ser homogénea o heterogénea. La mayoría de los procesadores actuales integra cores idénticos, como los procesadores Intel Core 2 o Tilera 64 [53]. Existen otros modelos que, aunque implementan el mismo repertorio de instrucciones, tienen diferentes características no funcionales, como por ejemplo los procesadores Sun Niagara T1 [54], cuyos cores comparten una unidad de punto flotante entre los 8 cores de forma transparente. Modelos heterogéneos con cores que ejecutan diferentes repertorios de instrucciones como los procesadores Cell de IBM, donde un core realiza la función de frontend, con un repertorio de instrucciones de tipo PowerPC, y los otros 8 cores, llamados *synergistic processing elements*, interpretan un repertorio de instrucciones RISC diferente.

Sin embargo, los sistemas heterogéneos no se basan únicamente en el repertorio de instrucciones, ya que un sistema heterogéneo podría consistir en un procesador con cores trabajando a diferentes frecuencias, que permitirían diferenciar unidades de paralelismo limitado y unidades de alto paralelismo. Existe una arquitectura que se corresponde de forma aproximada a este modelo, los sistemas de aceleración por hardware GPU [55] utilizan los procesadores vectoriales de las tarjetas gráficas como unidades de soporte para la ejecución de alto cómputo numérico, donde las frecuencias de los cores difieren. Sin embargo este último ejemplo no siempre encaja dentro de un sistema multicore ortodoxo, ya que la comunicación entre el procesador interno y el procesador GPU (Graphical Processing Unit) no acostumbra a ser intra-core. Aunque cabe destacar la microarquitectura Larrabee de Intel [56], actualmente un proyecto cancelado, concebido como un

sistema híbrido CPU y GPU,

Los sistemas homogéneos tienen la ventaja de ser más simples a la hora de gestionar los recursos. Los modelos con unidades especializadas tienen la ventaja de ser más eficientes. Los enteramente heterogéneos prometen una alta escalabilidad siempre que la aplicación se puede adaptar de forma natural al hardware, por ejemplo, el procesador Cell [57] va a proporcionar buenas prestaciones sobre aplicaciones paralelas que utilicen un modelo masterizado.

La era manycore que basa la escalabilidad en el número de cores, debe tener en cuenta que existen unas implicaciones en el diseño de los CMP respecto a la capacidad de integración en el chip, por tanto las propuestas actuales van en el sentido de diseñar grupos de cores funcionales heterogéneos, de propósito cada vez más específico que como unidades independientes tienen una arquitectura cada vez más sencilla.

## 3.2. Jerarquías de memoria

Las primeras generaciones de sistemas multicore heredaron la jerarquía de cache multinivel de los sistema single core. Estos sistemas jerárquicos proporcionan un protocolo transparente de coherencia de memoria y permiten la comunicación entre cores mediante los niveles de cache compartida. Si bien desde entonces la evolución ha consistido mayormente en pequeñas modificaciones en cuanto a tamaños, alcance de la compartición y niveles de cache, podemos resumir este tópico en:

- Los primeros procesadores duales disponían de una cache de nivel 2 privada, y esencialmente eran un doble single core en un mismo chip con una mínima lógica de interconexión y un mecanismo de coherencia basado en el protocolo Snoopy. Éste, consiste en monitorizar el bus de acceso a memoria para comparar las direcciones de escritura de las operaciones de escritura con los bloques de memoria locales, y si detecta una escritura sobre un bloque de memoria local, entonces puede invalidar la operación. El modelo de compartición de caché de nivel 2 también existe en los procesadores más modernos, como el Tilera 64 aunque el protocolo de coherencia está basado en la gestión de un directorio de la interconexión en malla.

- Caches de segundo nivel compartida entre cores, como en los modelos Sun Niagara (3 MB L2 cache) [54], así como los Intel Core 2 (entre 2 y 6 MB) [58].

- Caches de segundo nivel separadas y una cache L3 compartida. Los procesadores AMD

Phenom (512 KB L2 per core y 8 MB compartidos de L3) [59] o los más recientes Intel Core i7 (256 KB L2 per core, compartida L3 de 8 MB) [60].

- Compartición por subconjuntos. Así como en los modelos iniciales, donde se duplican procesadores para integrarlos en el mismo chip, los procesadores Intel Core 2 Quad consisten en dos unidades Core 2 Duo en un mismo chip. Por tanto, tienen una caché de L2 compartida por conjuntos de 2 cores.

Por otro lado, los procesadores Cell implementan otro modelo, donde los cores especializados, synergistic processing elements, tienen una memoria local de 256 KB que se comunica con el sistema memoria mediante transferencias DMA.

Las jerarquías de memoria permiten particionar el conjunto de datos, los diferentes niveles de compartición con niveles de latencias más bajas según la cercanía de la memoria con el procesador, permiten mejorar el rendimiento gracias a la propiedad de localidad de datos. Sin embargo esta característica depende de la carga de trabajo y de la aplicación, ya que algunas aplicaciones tienen un alto grado de compartición y otras no comparten en absoluto, por tanto la jerarquía de memoria debe ser lo suficientemente inteligente para adaptar su comportamiento a muy diferentes condiciones. La tendencia es que los sistemas CMP es que éstos tienen cada vez procesadores, y para estas arquitecturas las capas de jerarquía de memoria son cada vez más fragmentadas, se proponen modelos capaces de adaptarse a las necesidades pudiendo cambiar su estado entre privado y compartido. En [61] se evalúan arquitecturas de memoria cache adaptativas. El modelo ESP-NUCA (Enhanced Shared-Private Non-Uniform Cache Architecture) evalúa diferentes políticas de gestión de estos recursos.

### 3.3. Redes de interconexión

La interconexión entre los nodos inicialmente ha consistido en el acceso a un medio compartido mediante una jerarquía de memoria, sin embargo este modelo presenta poca escalabilidad, y cuando hablamos de decenas de cores se precisa una interconexión más elaborada. Los procesadores Cell de IBM interconectan los 9 cores mediante una red en anillo de alta velocidad. Este modelo presenta ciertas ventajas respecto a los buses ya que requiere un menor consumo y permite frecuencias más elevadas debido al menor número de líneas de comunicación y a una simple política de arbitraje de acceso al medio. Existen modelos que proporcionan baja latencia y un alto ancho de banda, como las redes crossbar dedicadas de los procesadores Sun Niagara.

Si queremos entrar en la era manycore, donde el número de cores aumenta de decenas a cientos o miles de cores, entonces se debe aplicar un modelo de red altamente escalable. Por las necesidades de interconexión de estos sistemas multicore y la similitud con sistemas HPC se pueden utilizar estrategias utilizadas en HPC aplicadas en entornos multicore. Éstas redes de interconexión se llaman Network-On-Chip (NOC).

Por este motivo los procesadores Tilera utilizados en sistemas empotrados que disponen de hasta 100 cores implementan una Network-On-Chip basada en una red commutada con una topología de malla 2D.

Como modelos teóricos para sistemas manycore tenemos los modelos de fat trees, que son una solución para obtener mayor escalabilidad. Y como hemos hablado de sistemas multicore con cores heterogéneos, entonces la interconexión entre estas diferentes unidades funcionales podrían ser de forma diferente entre módulos y con una conexión global jerarquizada.

Al aumentar el número de cores en una Network-On-Chip se deben implementar protocolos de comunicación y encaminamiento dentro de la red, conformando un modelo intracore distribuido. Por este motivo en rMPI [62], existe una propuesta para integrar dentro del repertorio de instrucciones (ISA) primitivas del modelo de paso de mensajes que permitan la comunicación intracore de baja latencia. Para favorecer la compatibilidad, utiliza primitivas del modelo de programación MPI, que es el estándar *de facto* en entornos distribuidos. El repertorio de instrucciones del modelo rMPI ha de permitir al programador controlar todos los recursos del chip, incluyendo puertas, cables y pines. Es conocido que los sistemas distribuidos son altamente escalables, utilizando estas arquitecturas de interconexión, se consigue alta escalabilidad en sistemas CMP.

### 3.4. Interfaz de acceso a memoria

En los sistemas multicore el acceso a memoria principal es un cuello de botella, por causa de ser un medio compartido concurrentemente. El rendimiento puede verse afectado por la latencia de acceso a memoria. Para mejorar este cuello de botella se proponen diseños de memoria en 3D [63]. Estas memorias tienen menor latencia por estar más próximas al procesador, ya que se sitúan sobre la CPU, y utilizan canales de transmisión de alto ancho de banda. En la construcción de estas memorias, se superponen capas 2D de células DRAM encima del procesador. Los buses de comunicación, llamados TSV (Through Silicon Vias) son grabadas en el silicio durante el proceso de creación. Este tipo de arquitectura está siendo muy estudiada, gracias a que la tecnología permite crear estos diseños tridimensionales que consiguen integrar más elementos y mas cercanos entre

ellos.

# Capítulo 4

## Marco de trabajo

Debido a la diversidad de arquitecturas, modelos de programación y paradigmas de aplicación, para estudiar los factores que afectan al rendimiento en entornos multicore, se ha definido un marco de trabajo acotado para iniciar la investigación. En este capítulo se desarrollan los elementos del marco de trabajo evaluado, que consisten en la definición de una arquitectura multicore y el desarrollo de los fundamentos teóricos del modelo de programación utilizado para expresar el paralelismo de las aplicaciones.

### 4.1. Nivel de Arquitectura

Para la selección de la arquitectura de estudio se ha utilizado un procesador multicore. En entornos multiprocesador, como los sistemas SMP (Symmetric Multi Processor) de memoria compartida, tienen estructuras similares, sin embargo contienen elementos en la arquitectura que pueden afectar a la medición de los factores de rendimiento. El procesador corresponde a un modelo MIMD multiprocesador de memoria compartida con acceso a memoria de tipo UMA (Uniform Memory Access):

- Entorno 2 cores:

- Core2Duo E4700 @ 2.6GHz.

- Caché L1 Datos 32 KBytes. Tamaño de línea 64 Bytes. Número de líneas 512. Asociatividad de 8 vías.

- Caché L1 Instrucciones 32 KBytes. Tamaño de línea 64 Bytes. Número de líneas 512. Asociatividad de 8 vías.

- Caché L2 Unificada 2048 KBytes. Tamaño de línea 64 Bytes. Número de líneas 32768.

Asociatividad de 8 vías.

- Memoria RAM 2 GBytes.

## 4.2. Nivel de Modelo de programación

Existen diferentes modelos de programación; orientados al paralelismo funcional o al paralelismo de datos. Como cada uno de ellos tiene diferente problemática, el marco de trabajo ha elegido un modelo de programación basado en el paralelismo de datos.

Los lenguajes de programación dentro de este modelo pueden ser explícitos, como por ejemplo las librerías de threads, o explícitos como OpenMP. El estudio se ha centrado en OpenMP, por causa de múltiples ventajas: es un estándar muy extendido en entornos de memoria compartida, es un modelo ampliamente estudiado en HPC, existen implementaciones para diversos lenguajes de programación (C, C++, Fortran), además es un modelo que está en constante revisión y actualización, desde su aparición en 1997, ha evolucionado hasta la actual versión 3.0, en que el modelo permite expresar tanto el modelo de paralelismo de datos como el modelo de paralelismo funcional. Para ajustar el marco de trabajo, el estudio del modelo de programación se ha basado en la definición OpenMP en su versión 2.5 que corresponde a un modelo de paralelismo de datos.

Para poder evaluar los factores de rendimiento en aplicaciones que utilizan el modelo de programación OpenMP, se ha seguido la siguiente metodología:

- Estudio de la API de threads subyacente a OpenMP, que ha de permitir evaluar el alcance de la implementación OpenMP. Al ser los threads la unidad básica de ejecución en entornos paralelos de memoria compartida, se ha estudiado la API de los POSIX threads, para comprobar el nivel de abstracción de OpenMP sobre la librería de implementación de threads. Además el rendimiento de OpenMP vendrá determinado por su traducción a la librería de threads y el rendimiento obtenido con dicha librería.

- Estudio de la API OpenMP, esta fase de análisis ha permitido clasificar los elementos de la definición del estándar OpenMP para una implementación concreta (GCC libgomp). Se ha evaluado el alcance y capacidad de abstracción de la librería de threads.

- Análisis de factores de rendimiento, una vez analizados los componentes de la API de threads y de la API OpenMP, se han evaluado aquellos elementos de la API, que han de

permitir al programador expresar el paralelismo, y que dependiendo de su utilización pueden afectar al rendimiento de la aplicación. Este apartado está desarrollado en el capítulo siguiente.

En los siguientes apartados se desarrolla el contenido de los elementos explicados en la metodología anterior, y que han de permitir el análisis de los factores de rendimiento.

#### 4.2.1. Threads

Las unidades mínimas de ejecución en sistemas multicore son los threads. Existen dos tipos de threads, los threads creados a nivel de usuario, y los kernel threads o threads a nivel de sistema operativo.

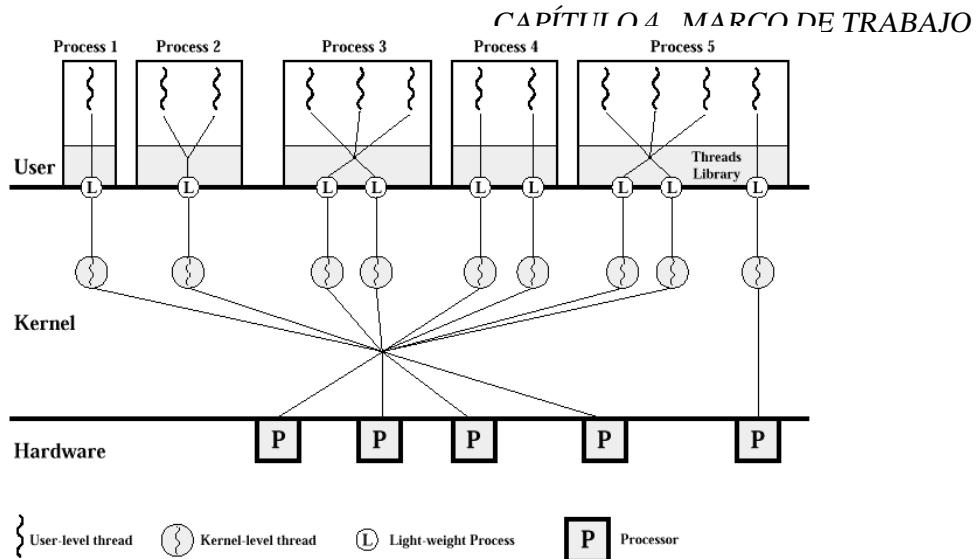

Los threads creados a nivel de usuarios se asocia en unidades planificables por el sistema operativo. Existe una capa que divide el espacio de memoria del sistema operativo entre espacio de usuario y espacio de kernel o núcleo. Los modelos de programación trabajan a nivel de usuario, por tanto los threads se asocia a procesos llamados LWP (Ligh Weight Processes) que proporcionan la interficie entre el contexto de la capa de usuario y la capa de núcleo. Los LWP son unidades planificadas por el sistema operativo, ya que éstos, están asociados a los kernel threads de la capa del kernel. Existen tres tipos de modelos de gestión de threads: los gestionados enteramente por el sistema operativo (modelo 1:1), donde cada thread asociado a un LWP se relaciona con un único kernel thread, los gestionados a nivel de usuario (N:1), que a través de un planificador de threads externo al kernel, son capaces de compartir una unidad planificable de LWP. Los últimos son los modelos híbridos (N:M) mostrado en 4.1, que permiten combinar la gestión de threads entre los niveles de usuario y kernel.

Los threads gestionados a nivel de usuario (modelos N:1 y N:M) tienen una menor latencia en la creación de threads y cambio de contexto, sin embargo, tienen un overhead en la gestión del planificador de threads de usuario. En el ámbito de HPC, existe diversidad de modelos de threads. Existen modelos de programación que utilizan threads gestionados a nivel de usuario (librería nanos4 del Barcelona Supercomputing Center, librería Marcel del centro LaBRI del INRIA) que como se ha comentado, proporcionan un menor coste de creación, y eliminación. Están librerías están específicamente diseñadas para modelos de paralelismo funcional, que requieren constantes replicaciones de tareas, por tanto, se benefician de un modelo de threads gestionado a nivel de usuario con menor overhead en la creación y cambio de contexto de los threads. Actualmente los sistemas operativos de forma general implementan por defecto el modelo (1:1) delegando la

Figura 4.1: *Modelo de thread M:N*

planificación de los threads al sistema operativo, como las Native POSIX Threads Library o Solaris Threads, que en aplicaciones de propósito general obtienen un mejor rendimiento del sistema.

Las liberías de threads más utilizadas son aquellas que están integrados por defecto en los diferentes sistemas operativos. En sistemas Linux se utiliza la implementación NPTL con threads estándar POSIX, implementada con un modelo (1:1). En sistemas Solaris, hasta la aparición de Solaris 8 el modelo de threads era multinivel, modelo N:M, pero a partir de esta versión se cambió por un modelo 1:1. El sistema Solaris incluye dos API de threads, la librería de Solaris threads y la alternativa libposix que permite portabilidad entre sistemas Unix Like.

Históricamente ha habido problemas de compatibilidad entre aplicaciones que utilizan threads, debido a que cada sistema operativo ha utilizado implementaciones de librerías de threads propias. En 1988 surgió el estándar POSIX (Portable Operating System Interface for Unix) [64], que define un modelo de interficie común para entornos Unix-Like, como consecuencia, permite la portabilidad de código entre diferentes sistemas operativos. Sin embargo, aunque se ha definido una interficie común, cada implementación tiene sus propias interpretaciones y particularidades que pueden afectar de diferente forma al rendimiento de una misma aplicación. Existen algunos estudios que reflejan diferencias significativas en tiempo de ejecución sobre diferentes implementaciones de threads [65]. Las librerías evaluadas en este estudio son Solaris threads, Provenzano threads, FSU\_threads, PCthreads, CLthreads, LinuxThreads. Las métricas que se han evaluado son:

- *Gestión de threads*, creación, sincronización y finalización de threads, tiempo de ejecución, y comparativas entre la utilización de threads y procesos, comparando los overhead de crea-

ción y overheads entre funciones de sincronización de threads y la función *wait* para la sincronización de procesos.

- *Gestión de la sincronización*, evaluación de las herramientas de sincronización y de exclusión mutua, como las funciones de lock/unlock, mutex lock/unlock sin contención, sobre variables condicionales en la generación de signal y broadcast, y tiempo de respuesta de variables condicionales.

Existe una gran diversidad de librerías que implementan threads, aquellas que cumplen con una definición estándar para ser más portables o aquellas que implementan funcionalidades específicas, íntimamente relacionadas con el sistema operativo o gestionadas a nivel de usuario, etc. Sin embargo, habiendo considerado los threads como la unidad de planificación básica en sistemas multicore, o de memoria compartida existen otras unidades de ejecución en los sistemas operativos como son los procesos. ¿qué motivos hay para la utilización de threads y no de procesos?, si decidimos utilizar threads existen diferentes modelos, de usuario o de kernel ¿qué modelo de threads es conveniente utilizar?. Una vez definido el modelo de threads, debemos tener en cuenta las características de la implementación ¿qué características implementa mi librería de threads? En los siguientes apartados se van a tratar de desarrollar alguno de estos contenidos, desde las preguntas surgidas en la definición del marco de trabajo de la tesis.

#### 4.2.1.1. Threads vs. Process

Existen diferencias entre los dos tipos de unidades ejecutables en los sistemas operativos, los hilos de ejecución (threads) y los procesos. Ambos permiten paralelizar aplicaciones, sin embargo, los threads se han convertido en estándar de facto. ¿Qué ventajas ofrecen respecto a los procesos?

Los threads no dejan de ser más que unidades de ejecución asociadas a un proceso, al crear un grupo de threads estos comparten el espacio de direccionamiento de usuario y bloque de control de proceso. De forma general cada thread tendrá su propio puntero a pila, registros de estado, propiedades de planificación (política y prioridad), conjuntos de señales pendientes y bloqueadas y los datos específicos de thread (Thread Specific Data). A diferencia de los threads, en la creación de procesos cada nuevo proceso tendrá que duplicar los recursos de memoria.

- Menor tiempo de creación para un hilo que para un proceso, debido a que la creación de un nuevo thread utiliza el espacio de memoria del actual proceso.

- Menor tiempo en la finalización de un thread

- Menor sobrecarga en la comunicación entre hilos que entre procesos, debido a la compartición del mismo espacio de memoria.

#### 4.2.1.2. User level threads vs. Kernel level threads

Como se ha comentado anteriormente los threads pueden ser gestionados en la capa de usuario o de núcleo del sistema operativo. Cada uno de estos modelos tienen características diferentes que se detallan a continuación y sus ventajas e inconvenientes:

##### *User level threads*

- El kernel del sistema no gestiona la actividad de los threads, aunque si la del Lighth Weight process asociado

- Cuando un threads realiza una llamada al sistema, todo el proceso se bloquea, pero para la librería de threads el thread continúa en el estado de ejecución.

- Los estados del thread son independientes de los estados del proceso

- Ventajas:

- El cambio de contexto entre threads no implica al kernel.

- La planificación de threads puede ser adaptada específicamente al tipo de aplicación.

- Los User level threads pueden ejecutarse en cualquier sistema operativo, ya que dependen de la librería.

- Inconvenientes

- La mayoría de las llamadas al sistema bloquean el proceso, y por tanto todos los threads asociados al LWP.

- Normalmente el kernel solo puede asociar procesos a procesadores, esto significa que dos threads en un mismo proceso se ejecutan simultáneamente sobre el mismo procesador

##### *Kernel level threads*

- La gestión de kernel threads es responsabilidad del kernel del sistema operativo.

- El kernel mantiene la información del contexto de threads y procesos, cambiar el contexto entre threads implica utilizar el planificador del kernel.

- Ventajas:

- El kernel puede planificar simultáneamente múltiples threads del mismo proceso en múltiples procesadores.

- El bloqueo se realiza a nivel de thread.

- Las rutinas del kernel pueden ser multithread

- Inconvenientes:

- El cambio de contexto entre threads involucra al kernel, y puede afectar al rendimiento.

#### 4.2.1.3. POSIX threads - implementación NPTL