Universitat

Autònoma

de Barcelona

3911

**DISEÑO Y EVALUACIÓN DE UN

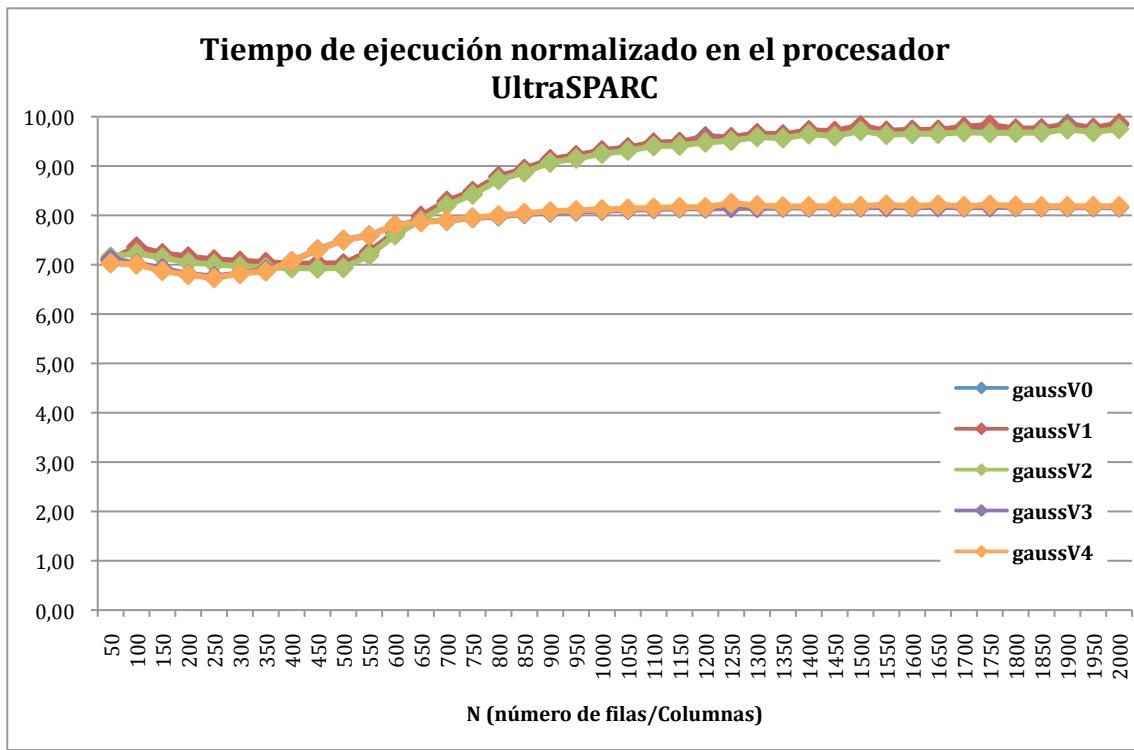

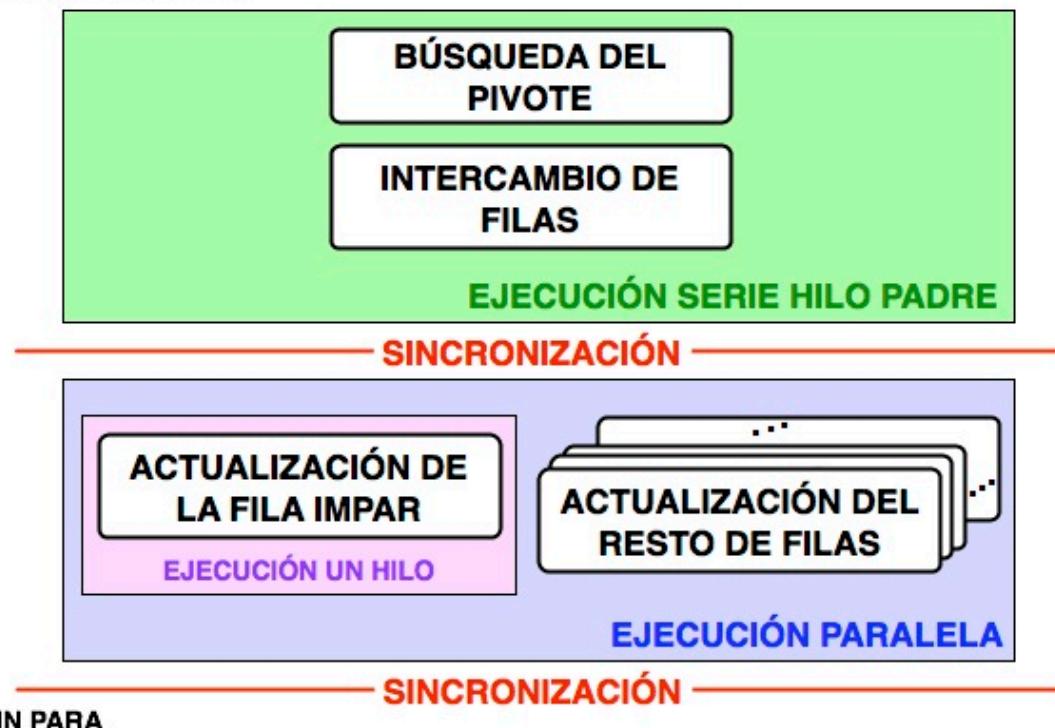

ALGORITMO PARALELO PARA

LA ELIMINACIÓN GAUSIANA EN

PROCESADORES MUTI-CORE**

Memoria del Proyecto Final de

Carrera de Ingeniería en Informática

realizado por Sergi Almazán

Sánchez y dirigido por

Juan Carlos Moure

Bellaterra, 2 de febrero de 2011

El abajo firmante, **Juan Carlos Moure López**

Profesor de la Escuela Técnica Superior de Ingeniería de la UAB,

**CERTIFICA:**

Que el trabajo que corresponde a esta memoria ha sido realizado bajo su dirección por **Sergi Almazán Sánchez**.

Y para que conste firma la presente,

Firmado: Juan Carlos Moure López

Bellaterra, 1 de febrero de 2011.

# Índice

|     |                                                                                   |    |

|-----|-----------------------------------------------------------------------------------|----|

| 1   | Introducción .....                                                                | 5  |

| 1.1 | Descripción del trabajo y objetivos .....                                         | 6  |

| 1.2 | Esquema de la memoria.....                                                        | 8  |

| 2   | Fundamentos teóricos.....                                                         | 9  |

| 2.1 | Evolución del procesador single-thread.....                                       | 9  |

| 2.2 | Limitaciones del procesador single-thread.....                                    | 12 |

| 2.3 | El procesador Multi-thread .....                                                  | 13 |

| 2.4 | El procesador Multi-core.....                                                     | 16 |

| 2.5 | Factores que impiden un alto rendimiento en sistemas multi-Core/multi-Thread..... | 21 |

| 2.6 | OpenMP .....                                                                      | 23 |

| 2.7 | PAPI (Performance Application Programming Interface).....                         | 26 |

| 3   | Descripción del problema: Eliminación Gaussiana .....                             | 27 |

| 3.1 | Resolución de sistemas lineales .....                                             | 27 |

| 3.2 | Descripción general del algoritmo de Eliminación Gaussiana .....                  | 30 |

| 3.3 | Pivotaje: estrategia para aumentar la precisión y estabilidad.....                | 33 |

| 4   | Análisis y Evaluación del algoritmo secuencial.....                               | 39 |

| 4.1 | Diseño del algoritmo serie .....                                                  | 39 |

| 4.2 | Análisis Computacional del Algoritmo .....                                        | 41 |

| 4.3 | Propuestas de Optimizaciones.....                                                 | 43 |

| 4.4 | Análisis del código Ensamblador .....                                             | 47 |

| 4.5 | Evaluación de las optimizaciones realizadas.....                                  | 51 |

| 5   | Diseño y análisis del algoritmo paralelo .....                                    | 65 |

| 5.1 | Diseño del algoritmo paralelo .....                                               | 65 |

| 5.2 | Análisis computacional del algoritmo paralelo .....                               | 69 |

| 5.3 | Resultados experimentales .....                                                   | 73 |

|     |                                                   |    |

|-----|---------------------------------------------------|----|

| 6   | Problemas encontrados.....                        | 87 |

| 6.1 | Selección de la métrica adecuada .....            | 87 |

| 6.2 | Problemas de paralelización.....                  | 88 |

| 6.3 | Anomalías de rendimiento .....                    | 89 |

| 7   | Conclusiones, líneas futuras y ampliaciones ..... | 91 |

| 7.1 | conclusiones.....                                 | 91 |

| 7.2 | Líneas futuras y ampliaciones.....                | 92 |

| 8   | Bibliografía.....                                 | 93 |

| 9   | Anexo I .....                                     | 94 |

| 9.1 | Código C versión base del algoritmo serie.....    | 94 |

| 9.2 | Código C versión 3 del algoritmo serie.....       | 95 |

| 9.3 | Código C versión 3 del algoritmo paralelo.....    | 96 |

## 1 Introducción

Dada la necesidad de computar cada vez problemas más grandes en un tiempo razonable, los desarrolladores de sistemas de computación comenzaron a unir sus máquinas existentes para trabajar como una sola. Este fue el inicio de la computación paralela. La computación paralela es la computación que enfatiza el tratamiento concurrente de un conjunto de datos para más de un procesador con el objetivo de resolver un único problema.

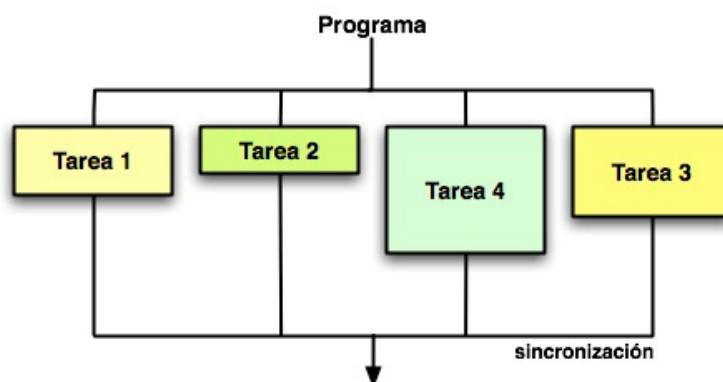

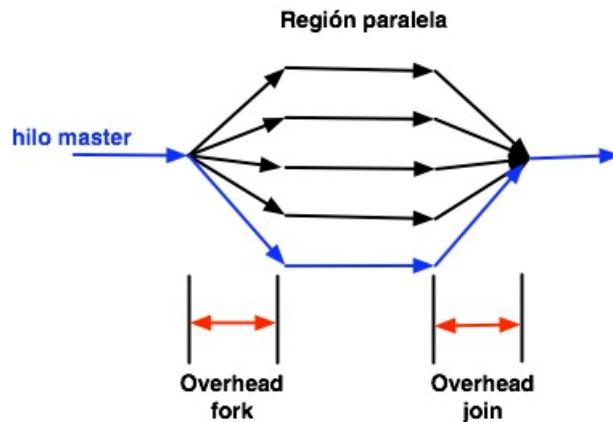

La programación paralela es una técnica de programación basada en la ejecución simultánea de varias tareas. Durante la última década se han aplicado sólo a la computación de altas prestaciones (HPC) pero últimamente el interés ha crecido debido a las restricciones físicas que impiden el escalado en frecuencia. A continuación podemos ver en la Figura 1, un diagrama donde se muestra la subdivisión de un programa en tareas para ejecutarlas de forma paralela en diferentes hilos de ejecución y como éstos se sincronizan después de acabar todas las tareas.

Figura 1. Ejecución de un programa paralelo

Hasta el momento el desarrollo tecnológico había permitido la integración de más transistores en un mismo procesador. Este aumento de la integración, el escalado en frecuencia, el aumento de las operaciones ejecutadas simultáneamente (procesadores superescalares) y la segmentación han otorgado esta capacidad necesaria de cómputo sin cambiar la interficie de programación secuencial.

Las mejoras del rendimiento mediante estas estrategias, empiezan a tocar techo. Este hecho ha provocado que la industria opte por aumentar el número de núcleos de procesamiento secuencial en el mismo chip para obtener futuros incrementos del rendimiento, en vez de diseñar un procesador con una única unidad de proceso más rápida y con mayor capacidad de cómputo. Debido a este cambio en el diseño es necesario un cambio de interficie de programación. Por este motivo nace el término “*multinúcleo*”.

## **1.1 Descripción del trabajo y objetivos**

A continuación , se detallan cronológicamente las tareas previstas para la realización del proyecto.

### **Búsqueda de la información necesaria para la comprensión de los trabajos a realizar.**

#### **Aprendizaje y estudio**

**Estudio y comprensión del hardware**

**Estudio y comprensión del algoritmo estudiado**

**Estudio y comprensión de la programación paralela**

**Estudio y comprensión de las herramientas de extracción de datos**

**Estudio y comprensión de la programación paralela mediante OpenMP**

#### **Instalación, familiarización y pruebas**

#### **Codificación**

**Paralelización y optimización de la aplicación**

Codificación de la versión secuencial

Optimización de la versión secuencial

Paralelización de la versión optimizada

#### **Obtención y estudio de resultados**

**Generación de scripts para la extracción de resultados de la aplicación serie**

**Generación de scripts para la extracción de resultados de la aplicación paralela**

**Obtención y estudios de resultados en el sistema A**

**Obtención y estudios de resultados en el sistema B**

**Obtención y estudios de resultados en el sistema C**

**Generación de excels para la generación de gráficas para el estudio**

**Obtención de resultados extras para corroborar conclusiones**

La metodología seguida para llevar a cabo la versión paralela del algoritmo escogido es la siguiente:

- **Obtención Algoritmo secuencial base:** Tras un estudio en profundidad del algoritmo se ha realizado una codificación inicial.

- **Optimización de la versión secuencial:** Después de la verificación del algoritmo base, se ha realizado un estudio del algoritmo serie en busca de los puntos débiles de la aplicación y zonas críticas para aumentar su rendimiento.

- **Estudio de la aplicación serie:** Una vez generadas las diferentes versiones de la aplicación serie con las optimizaciones propuestas. Se ha realizado un estudio del rendimiento de la aplicación ejecutada en los tres procesadores. Finalizado el estudio, se ha escogido la mejor versión para realizar la aplicación paralela.

- **Obtención de la versión paralela:** Después del estudio de la ejecución serie, y escogida la mejor versión, se realiza la paralelización de aplicación mediante OpenMP.

- **Estudio de la aplicación paralela:** Con la versión paralela generada, se realiza un estudio en profundidad de la ejecución paralela multihilo en los diferentes procesadores seleccionados para extraer las conclusiones finales.

El objetivo de este proyecto, es el aprendizaje de una metodología de diseño y evaluación de aplicaciones paralelas multithread/multihilo para computadores multicore/multinúcleo. Para conseguir este objetivo, se ha realizado el estudio, optimización y paralelización de un importante algoritmo con infinidad de aplicaciones en el campo de la ingeniería como es el algoritmo de la Eliminación Gaussiana. La Eliminación Gaussiana es un eficiente algoritmo de resolución de sistemas de ecuaciones lineales. Para evaluar la ejecución multinúcleo se ha efectuado un estudio del comportamiento del algoritmo en tres procesadores totalmente diferentes. Dos procesadores fuera de orden con una configuración multicore diferente y un procesador en orden.

## 1.2 Esquema de la memoria

La memoria está compuesta por ocho capítulos, que se detallan brevemente a continuación.

**Capítulo 1:** En este capítulo se realiza una breve introducción, se muestran los objetivos del proyecto, la descripción de los trabajos a realizar y la metodología que se seguirá.

**Capítulo 2:** En este capítulo se definen los conceptos necesarios para la comprensión del proyecto. Se introducen los conceptos tales como la evolución del procesador single-thread, los procesadores multicore multithread, los factores que limitan el rendimiento de los sistemas multicore/multithread, la programación OpenMP y la extracción de datos de los contadores hardware mediante PAPI.

**Capítulo 3:** En este capítulo se describe el problema de la Eliminación Gaussiana.

**Capítulo 4:** En este capítulo se realiza el análisis y evaluación del algoritmo secuencial de la Eliminación Gaussiana con pivotaje parcial por filas. Se realiza una primera codificación del algoritmo serie y tras el análisis computacional, se realiza una serie de optimizaciones que acaban generando 4 nuevas versiones de la aplicación. Cada una de estas versiones es ejecutada en los sistemas considerados y se extraen los resultados del rendimiento. Como resultado de este capítulo, se identifica la versión secuencial con un mejor rendimiento que se usará como base en el capítulo siguiente para la versión paralela.

**Capítulo 5:** En este capítulo se realiza el análisis y diseño del algoritmo paralelo. Primeramente se realiza un estudio de la versión serie y su división en tareas independientes para ser ejecutadas simultáneamente y se diseña el algoritmo paralelo. A continuación se efectúa un análisis computacional del algoritmo independiente del procesador. Por último se ejecuta la versión paralela en los diferentes sistemas considerados para la extracción de resultados del rendimiento. Tras la muestra de los resultados se extraen las conclusiones del estudio.

**Capítulo 6:** En este capítulo se describe, de forma cronológica, los diferentes problemas encontrados a lo largo del proyecto y lo que se ha aprendido de ellos.

**Capítulo 7:** En este capítulo se incluyen las conclusiones finales del proyecto, las líneas futuras de investigación y ampliaciones.

**Capítulo 8:** Bibliografía.

**Capítulo 9:** Anexo I.

## 2 Fundamentos teóricos

En este capítulo se describen los conceptos básicos que se emplearan durante el desarrollo del proyecto. Se explicará la evolución del procesador desde single-thread hasta llegar al procesador multicore. Finalmente se realizará una breve introducción a la programación mediante OpenMP y la extracción de prestaciones mediante contadores hardware con PAPI.

### 2.1 Evolución del procesador single-thread

En un procesador clásico podemos dividir el proceso de ejecución de una instrucción en cuatro etapas:

1. Búsqueda de la instrucción (prefetch y fetch)

2. Decodificación de la instrucción

3. Búsqueda de los operandos

4. Ejecución de la instrucción y escritura de los resultados.

Para cada etapa se emplea un tiempo denominado un ciclo. En la figura 2 se muestra las diferentes ciclos que emplea un procesador clásico en ejecutar dos instrucciones. Se puede apreciar que hasta que la primera instrucción no finaliza, no se puede realizar la búsqueda de la segunda instrucción.

| Ciclos                     | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      |

|----------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Búsqueda Instrucción       | INST 1 |        |        |        | INST 2 |        |        |        |

| Decodificación Instrucción |        | INST 1 |        |        |        | INST 2 |        |        |

| Búsqueda operandos         |        |        | INST 1 |        |        |        | INST 2 |        |

| Ejecución Instrucción      |        |        |        | INST 1 |        |        |        | INST 2 |

**Figura 2.** Etapas empleadas para la ejecución de dos instrucciones en un procesador clásico.

El tiempo de ejecución de un programa ( $T_e$ ) se puede expresar con la siguiente ecuación de rendimiento:

$$T = N \times CPI \times t$$

donde **N** es el número total de instrucciones ejecutadas por el programa, **CPI** es el número de ciclos por instrucción capaz de ejecutar el procesador y **t** el tiempo de un ciclo de reloj del procesador.

Para minimizar el tiempo de ejecución existen dos alternativas que son, reducir el número de instrucciones y/o reducir el CPI.

### 2.1.1 Procesamiento segmentado

En el procesamiento segmentado se adopta una nueva estrategia con el objetivo de disminuir el tiempo medio de ejecución por instrucción de una aplicación. Se divide internamente el computador en segmentos individuales, cada uno especializado en una de las etapas.

A diferencia del procesador clásico donde todas las etapas tenían que completarse antes de buscar la instrucción siguiente, ahora la existencia de segmentos especializados permite el solapamiento en la ejecución de las instrucciones. Así, un segmento puede empezar a trabajar con una nueva instrucción sin la necesidad de que la instrucción anterior haya finalizado todas las etapas.

El resultado es un aumento del numero de instrucciones ejecutadas por ciclo. Como se observa en la Figura 3, con la ejecución segmentada de instrucciones, un procesador segmentado de K etapas en un caso ideal pasa de ejecutar una instrucción cada K ciclos a una instrucción por ciclo. No obstante, los saltos y las dependencias de datos limitan esta ganancia. En el caso de los saltos, las instrucciones de bifurcación condicional pueden derivar en diferentes caminos a seguir por lo que no es posible conocer la siguiente instrucción a ejecutar hasta que no se haya ejecutado completamente la instrucción de salto. En el caso de dependencia de datos una instrucción puede quedar detenida en una etapa a la espera del dato que otra instrucción anterior debe calcular.

| Ciclos                     | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      |

|----------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Búsqueda Instrucción       | INST 1 | INST 2 | INST 3 | INST 4 | INST 5 |        |        |        |

| Decodificación Instrucción |        | INST 1 | INST 2 | INST 3 | INST 4 | INST 5 |        |        |

| Búsqueda operandos         |        |        | INST 1 | INST 2 | INST 3 | INST 4 | INST 5 |        |

| Ejecución Instrucción      |        |        |        | INST 1 | INST 2 | INST 3 | INST 4 | INST 5 |

**Figura 3.** Ejecución segmentada de varias instrucciones.

### 2.1.2 Memoria Cache

La memoria cache es una memoria de alta velocidad y menor tamaño que la memoria principal, situada entre el procesador y la memoria principal. Su misión es almacenar temporalmente los contenidos de la memoria principal que estén siendo utilizados por el procesador. De esta forma se reduce el número de operaciones de acceso a memoria principal, disminuyendo el número de ciclos dedicados a acceso a memoria, y reduciéndose por tanto el CPI.

La posibilidad de aumentar las prestaciones incorporando memoria cache se debe a la localidad temporal y a la localidad espacial. Estas son características del comportamiento de las aplicaciones. En el caso de la localidad temporal existe una alta probabilidad de acceder a posiciones de memoria a las que ya se ha accedido anteriormente. En el caso de la localidad espacial existe una alta probabilidad que de una vez accedida a una posición de memoria, se acceda a las posiciones de memoria cercanas, en un futuro inmediato.

[1]

### 2.1.3 El procesador superescalar

Un procesador superescalar es capaz de ejecutar más de una instrucción en cada etapa del pipeline del procesador. El número máximo de instrucciones en cada etapa depende del número y del tipo de las unidades funcionales de que disponga el procesador. Sin embargo, un procesador superescalar sólo es capaz de ejecutar más de una instrucción simultáneamente si las instrucciones no presentan ningún tipo de dependencia. Las dependencias que pueden aparecer son:

- **Dependencias estructurales:** cuando dos instrucciones requieren el mismo tipo de unidad funcional pero su número no es suficiente.

- **Dependencias de datos:**

- Lectura después de Escritura: cuando una instrucción necesita el resultado de otra para ejecutarse.

- Escritura después de Lectura o Escritura: cuando una instrucción necesita escribir en un registro sobre el que otra instrucción previamente debe leer o escribir.

- **Dependencias de control:** cuando existe una instrucción de salto que puede variar la ejecución de la aplicación

Podemos distinguir diferentes tipos de procesadores por la forma de actuar ante una dependencia estructural o de datos. En un procesador con ejecución **en orden** las instrucciones quedarán paradas a la espera de que se resuelva la dependencia. Mientras que en un procesador con ejecución **fuerza de orden** las instrucciones dependientes quedarán paradas pero será posible solapar parte de la espera con la ejecución de otras instrucciones independientes que vayan detrás.

En el caso de las dependencias de control, se conoce como **ejecución especulativa** de instrucciones a la ejecución de instrucciones posteriores a la instrucción de salto (antes de que el contador del programa (PC) llegue a la instrucción de salto).

[2-3]

## 2.2 Limitaciones del procesador single-thread

A continuación describiremos una serie de factores que limitan el rendimiento de la ejecución de una aplicación en un procesador single-thread.

### 2.2.1 Problema de la memoria

La diferencia de velocidad entre procesador y memoria, limita el rendimiento del procesador. Las operaciones de memoria son lentes comparadas con la velocidad del procesador. Los accesos a memoria, por ejemplo en un fallo de cache, pueden consumir de 100 a 1000 ciclos de reloj, durante los cuales el procesador debe esperar a que el acceso a memoria finalice.

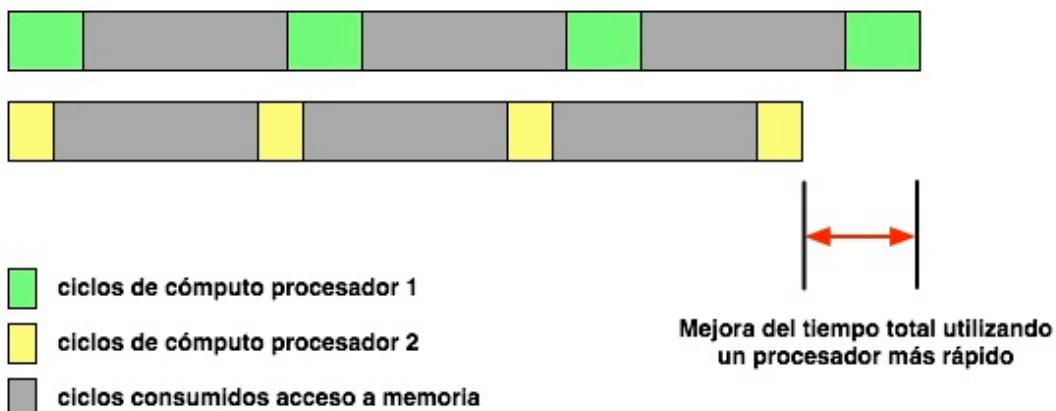

Por tanto, un aumento de la frecuencia de reloj del procesador sin incrementar la velocidad de la memoria solamente mejoraría el rendimiento en un pequeño porcentaje. Los ciclos de cómputo se realizarían más rápido pero el tiempo de acceso a memoria continuaría siendo el mismo. Esto se puede apreciar en la figura 4 que representan las fases de ejecución de un programa single-thread en dos procesadores con distinta frecuencia de reloj. En la figura, el procesador 2 tiene el doble de frecuencia de reloj que el procesador 1 y consume los mismos ciclos en el acceso a memoria que el procesador 1.

**Figura 4.** Fases de ejecución de un programa single-thread en dos procesadores con distinta frecuencia de reloj.

Además hay que tener en cuenta que a los cientos de ciclos que se consumen en cada acceso a memoria hay que sumarle decenas de ciclos extra, por cada acceso a nuevos niveles de cache (provocados por fallos en el nivel anterior).

La solución para aprovechar los ciclos en los que el procesador esta esperando a que finalice la operación de memoria es el “*multithreading*” por hardware. El “*multithreading*” por hardware es una propiedad que permite al procesador alternar de un hilo a otro hilo cuando el hilo que esta ocupando el procesador queda parado. Esta solución se analizará en profundidad más adelante.

### 2.2.2 Calor y coste asociado

El incremento de la frecuencia de reloj del procesador implica un aumento de la potencia consumida y del calor generado. En la actualidad los altos valores de frecuencia de reloj de los procesadores suponen un problema, tanto económico por el consumo eléctrico, y gasto dedicado a la disipación del calor y refrigeración del procesador, como tecnológico por la dificultad para disipar la gran cantidad de calor generado, de la pequeña superficie de un procesador. Por estos motivos, se ha abandonado la idea de aumentar la frecuencia de reloj del procesador para aumentar el rendimiento, y se ha optado continuar aumentando el nivel de integración sin aumentar la frecuencia de reloj y en el mismo espacio añadir más procesadores en un mismo chip. Con esta solución el calor se incrementa de forma lineal y no exponencial como ocurre con el aumento de frecuencia de reloj.

## 2.3 El procesador Multi-thread

Para entender conceptos como el *multithreading* por software, el *multithreading* por hardware y las ventajas de los procesadores multi-thread/multi-hilo es necesario conocer la diferencia entre hilo y proceso.

### 2.3.1 Thread/Hilo y Proceso

Un proceso es secuencia de código ejecutable en ejecución. Cada proceso posee un espacio de direccionamiento propio para almacenar sus estructuras de datos asociados. Un proceso está formado por uno o más threads o hilos de ejecución. Un hilo es la unidad mínima de procesamiento. Los hilos existen dentro de un proceso y comparten recursos como el espacio de memoria, la pila de ejecución y el estado de la CPU. Un proceso con múltiples hilos tiene tantos flujos de control como hilos. Cada hilo se ejecuta con su propia secuencia de instrucciones de forma concurrente e independiente.

### 2.3.2 Multi-threading por Software

Debemos distinguir entre multi-programación y aplicaciones paralelas.

La multi-programación es una técnica de planificación que permite tener varios hilos (o procesos) en estado de ejecución. Los hilos comparten los recursos del sistema como la memoria principal y el procesador. Existe la falsa apariencia de que los hilos se están ejecutando simultáneamente, esto es debido a que el sistema operativo es de tiempo compartido. En un escenario de tiempo compartido cada hilo se ejecuta durante un breve intervalo de tiempo. El cambio de contexto se realiza lo suficientemente rápido como para simular la ejecución de varios hilos simultáneamente.

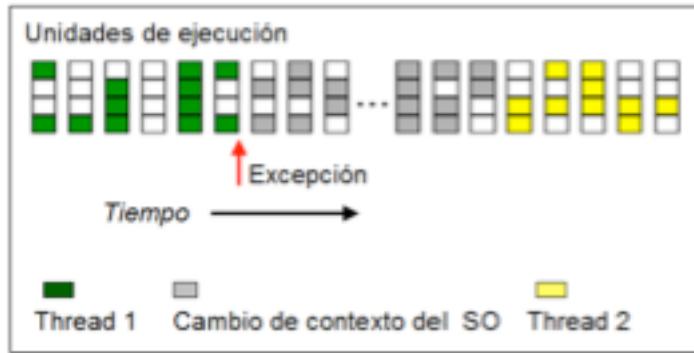

En la figura 5 se observa como el Hilo 1, se para al producirse una excepción que requiere esperar un tiempo. Inmediatamente el Sistema Operativo cambia de contexto y ejecuta otro hilo. Cada columna de la figura representa una instrucción de las cuatro que se pueden llegar a ejecutar en cada ciclo (ejecución superescalar de grado 4).

**Figura 5:** Cambio de Hilo del SO en un entorno multiprogramado.

El *multithreading* por software posibilita la realización de aplicaciones paralelas. Es un nuevo modelo de programación que permite a múltiples hilos existir dentro de un proceso. Los hilos comparten los recursos del proceso pero se ejecutan de forma independiente. El hecho de que sean independientes permite la concurrencia (es decir su ejecución simultánea), y si el procesador lo soporta se podrán ejecutar en paralelo.

Las ventajas de realizar la concurrencia a nivel de hilo en lugar de a nivel de proceso son varias. Los hilos se encuentran todos dentro de un mismo proceso y por lo tanto pueden compartir los datos globales. Además, una petición bloqueante de un hilo no parará la ejecución de otro hilo. Por último, si el procesador lo soporta, los diferentes hilos están asociados a diferentes conjuntos de registros, por lo que el cambio de contexto del procesador podrá realizarse de forma eficiente.

### 2.3.3 Multithreading por Hardware

El *multithreading* por Hardware es una técnica que incrementa la utilización de los recursos del procesador. A continuación se analizarán diferentes tipos de multithreading por Hardware.

#### Large-Grain Multithreading

En el modelo *large-grain multithreading* el procesador ejecuta el hilo de forma habitual y solamente realiza un cambio de contexto cuando ocurre un evento de larga duración (como un fallo de caché). Para que el cambio de contexto sea eficiente es necesario que exista una copia del estado de la arquitectura (PC, registros visibles) para cada hilo. Este método tiene la ventaja de ser sencillo de implementar.

En la Figura 6 se muestra la ejecución de los diferentes hilos en la que el procesador cambia de hilo cuando se produce un evento que requiere un tiempo de espera por ejemplo un fallo de cache.

**Figura 6:** Ejecución de hilos siguiendo el modelo Large-Grain Multithreading.

### Fine-grained Multithreading

El *fine-grained multithreading* se basa en un cambio “rápido” entre hilos, ejecutando en cada ciclo un hilo diferente. Es un mecanismo que tiene como base una planificación de la ejecución de las instrucciones en orden. Con el fin de evitar largas latencias por hilos bloqueados, se ejecutan instrucciones de diferentes hilos. Este enfoque tiene la ventaja de eliminar las dependencias de datos que paran el procesador. Al pertenecer las instrucciones a diferentes hilos, las dependencias de datos y de control desaparecen.

En la figura 7 se muestra como en cada ciclo se ejecutan instrucciones de hilos diferentes. El procesador no espera a que se produzca una interrupción (fallo de caché,...) para saltar al siguiente hilo.

**Figura 7:** Ejecución de hilos siguiendo el modelo Fine-grained Multithreading.

### Simultaneous Multithreading

La filosofía de *simultaneous multithreading* (SMT) consiste en poder ejecutar instrucciones de diferentes hilos, en cualquier momento y en cualquier unidad de ejecución. Desarrollar esta tecnología requiere un hardware adicional para toda la lógica. Como consecuencia, su realización para un gran número de hilos aumentaría la complejidad y, por tanto el coste. Por este motivo en las implementaciones SMT se opta por reducir el número de hilos.

*Simultaneous multithreading* muestra a un procesador físico como dos o más procesadores lógicos. Los recursos físicos son compartidos y el estado de la arquitectura es copiada para cada uno de los dos procesadores lógicos. El estado de la arquitectura está formado por un conjunto de registros: registros de propósito general, registros de control, registros del controlador de interrupciones (APIC) y registros de estado.

Los programas verán a los procesadores lógicos como si se tratara de dos o más procesadores físicos diferentes. Sin embargo, desde el punto de vista de la microarquitectura, las instrucciones de los procesadores lógicos se ejecutarán simultáneamente compartiendo los recursos físicos.

## 2.4 El procesador Multi-core

Los procesadores multi-core o multi-núcleo combinan dos o más procesadores, a los que nos referiremos como núcleos o cores, en un mismo chip. Estos procesadores mejoran el rendimiento de las aplicaciones paralelas. Las aplicaciones paralelas están compuestas por múltiples hilos independientes, de forma que es posible la concurrencia. Es decir, los hilos se pueden ejecutar al mismo tiempo y en paralelo.

Como consecuencia el rendimiento de las aplicaciones paralelas puede teóricamente escalar linealmente con el número de procesadores. En la práctica existen factores que lo impiden, como los overheads por creación/eliminación de hilos, las comunicaciones entre las memorias de los procesadores, y el posible desbalanceo en las aplicaciones del volumen de cómputo por hilo (hilos esperando a que otros hilos finalicen). Describiremos estos factores con más detalle, más adelante. Otra de las ventajas es poder aplicar el diseño de un núcleo ya probado a los demás núcleos del procesador. Así se evita el coste que supondría el diseño de nuevos núcleo. Como inconveniente, las aplicaciones han de ser correctamente parallelizadas para aprovechar todo el potencial de los procesadores multi-núcleo.

### 2.4.1 Arquitectura de los procesadores multi-core

Los procesadores de una arquitectura multi-núcleo comparten la memoria principal. Existen dos alternativas para compartir la memoria principal, el acceso uniforme a memoria y el acceso no uniforme a memoria.

En la primera los procesadores del sistema tienen el mismo tiempo de acceso a memoria, a esta arquitectura se la conoce como arquitectura UMA (Acceso uniforme a memoria). En la segunda el acceso parcial o total a la memoria es controlado por un único procesador, lo que provoca que este procesador tenga un tiempo de acceso menor, a la memoria controlada por él, que el resto de procesadores. El resto de procesadores debe interactuar con el procesador que controla la memoria para acceder a ella, a esta arquitectura se la conoce como arquitectura NUMA. (Acceso no uniforme a memoria).

En cuanto a la organización de las memorias caché de un multi-núcleo existen varias opciones. En algunas arquitecturas se opta por mantener todos los niveles de cache privados a cada núcleo, mientras que en otras arquitecturas se comparte el último nivel de cache.

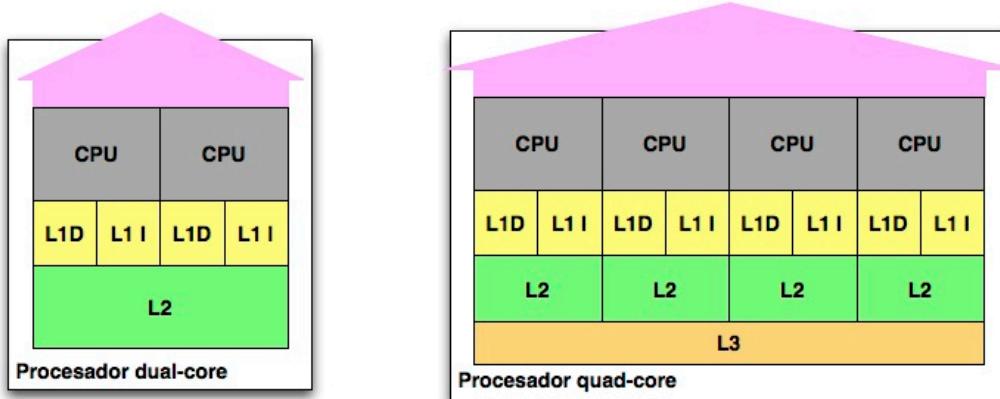

Las figura 8 muestra el esquema de un procesador dual-core, en el que las memorias cache de nivel 1 de instrucciones y de datos son privadas, la memoria cache de nivel 2 es compartida, y el acceso a memoria principal es de tipo UMA. En la misma figura, se muestra el esquema de un procesador quad-core, en el que las memorias cache de nivel 1 y de nivel 2 son privadas, la memoria cache de nivel 3 es compartida, y el acceso a memoria principal es de tipo UMA.

**Figura 8.** Esquema de los procesadores de doble y cuádruple núcleo

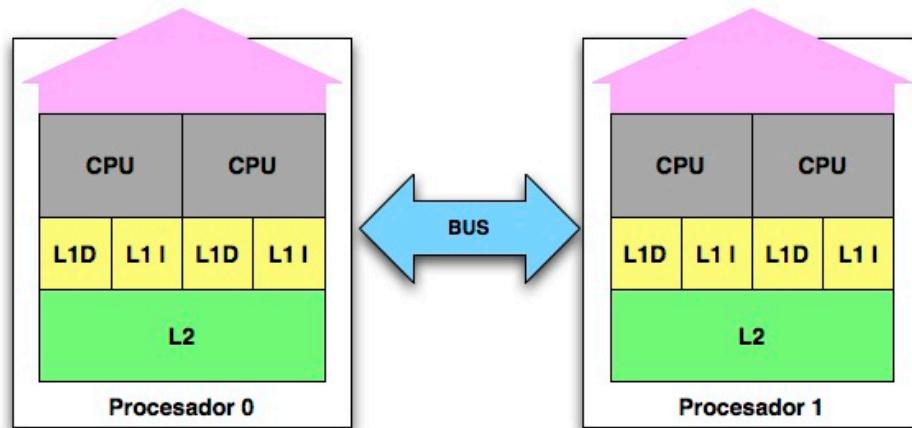

La figura 9 muestra el esquema de una arquitectura NUMA, formada por dos procesadores dual-core. Cada uno de los procesadores accede directamente a su memoria principal y para acceder a la memoria principal del otro procesador tiene que interactuar con él. Como en la figura 8, los núcleos de cada uno de los procesadores tienen memorias cache de nivel 1 privadas y comparten la memoria cache de nivel 2 y la memoria principal que corresponde al procesador.

**Figura 9.** Esquema de la arquitectura NUMA con dos procesadores dual-core

Las principales ventajas de compartir la memoria cache son las siguientes:

1. **Uso eficiente del último nivel de cache:** Si un núcleo está inactivo el otro núcleo puede utilizar toda la cache compartida. Si los dos núcleos trabajan en paralelo, la memoria cache se reparte proporcionalmente en función de la frecuencia de solicitudes de cada núcleo. Incrementa la utilización de los recursos.

2. **Reducción del almacenamiento de los datos:** Los mismos datos utilizados por dos núcleos que comparten memoria cache, serán almacenados una única vez.

3. **Reducción de la complejidad de la coherencia en la memoria cache:**

- Reduce el problema de *false-sharing*

- Menor carga de trabajo para mantener la coherencia, comparado con la arquitectura de memoria cache privada.

[1]

#### 2.4.2 Procesador SUN UltraSPARC T2

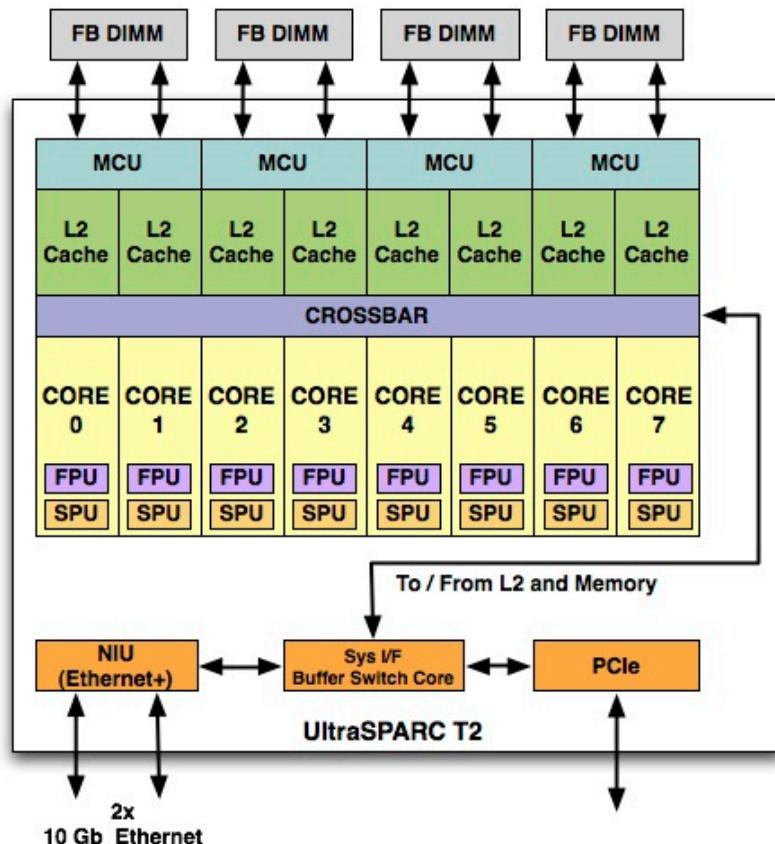

Siguiendo esta línea SUN ha diseñado un conjunto de procesadores multi-núcleo y multi-hilo. De este conjunto estudiaremos el denominado proyecto Niágara II: El UltraSPARC T2. A continuación nos encontramos en la Figura 10, el esquema principal de este procesador multi-núcleo y sus unidades funcionales.

Figura 10. Diagrama de componentes del procesador Multi-núcleo UltraSPARC T2 (8 núcleos)

El procesador UltraSPARC T2 dispone de 4 a 8 núcleos de procesamiento capaces de manipular hasta 8 hilos de ejecución cada uno. Cada núcleo dispone a su vez de dos memorias cache de primer nivel (L1) de 16KB para instrucciones y 8KB para datos, una unidad para operaciones en punto flotante y una unidad de cifrado.

La jerarquía de memoria del T2 es de dos niveles. Todos los núcleos disponen de 4MB de memoria cache de segundo nivel organizada en 8 bancos asociativos de 16 vías compartida a través de una red de interconexión de tipo “crossbar” donde todos los núcleos puede acceder a todos los bancos simultáneamente (todas las parejas no conflictivas pueden acceder al mismo tiempo).

Además el UltraSPARC T2 incorpora 4 controladores de memoria de doble canal denominados FB-DIMM integrados para bajar la latencia hacia la memoria principal y dos interficies de red accesibles a través del crossbar, dos puertos 10GB Ethernet y 8 puertos de entrada/salida del tipo PCIe integrados también.

En el diseño del UltraSPARC T2 se ha buscado la máxima eficiencia energética. Una de las grandes características que tiene este procesador es su reducido consumo, tan sólo 95w. Además tiene la posibilidad de encender/apagar los hilos por software o reducir la frecuencia de los núcleos para minimizar el consumo. [4]

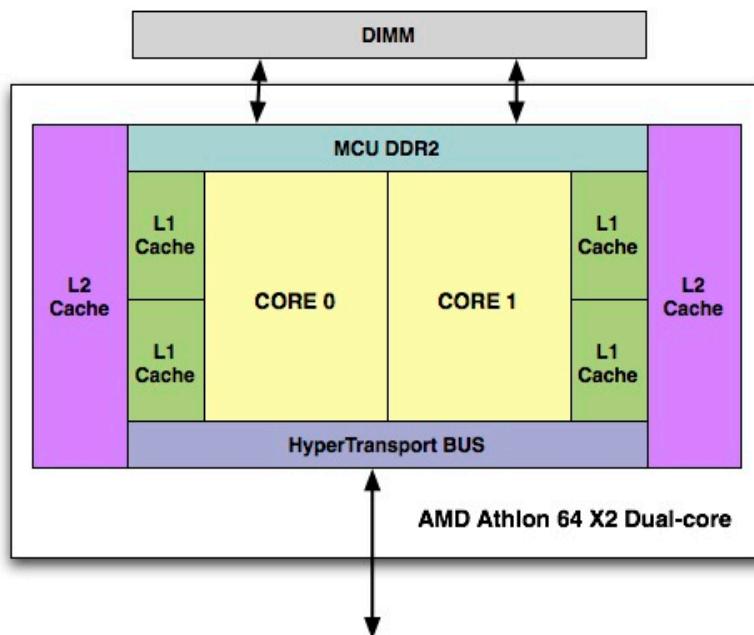

#### 2.4.3 Procesador AMD Dual-Core

Siguiendo esta línea AMD ha diseñado un conjunto de procesadores multi-núcleo y multi-hilo. De este conjunto estudiaremos AMD Athlon 64 X2 Dual-core. A continuación nos encontramos en la Figura 11, el esquema principal de este procesador multi-núcleo y sus unidades funcionales.

**Figura 11.** Diagrama de componentes del procesador Multi-núcleo AMD Athlon 64 X2 Dual-core

El procesador AMD Athlon 64 dispone de 2 núcleos con tecnología *AMD64* que proporciona soporte a plena velocidad para x86.

La jerarquía de memoria del AMD Athlon 64 es de dos niveles. Cada núcleo dispone a su vez de dos memorias cache de primer nivel (L1) de 64KB para instrucciones y 64KB para datos. Cada núcleo disponen de 1MB de memoria cache de segundo nivel (L2).

Además el AMD Athlon 64 incorpora 1 controlador de memoria de doble canal denominados DIMM integrados para bajar la latencia hacia la memoria principal y un bus con tecnología *HyperTransport* de 8GB/s, para lograr unas comunicaciones de entrada/salida de alta velocidad.

En el diseño del AMD Athlon 64 se ha buscado la máxima eficiencia energética. Una de las grandes características que tiene este procesador es su reducido consumo, tan sólo 89w. Además posee la tecnología *Cool'N'Quiet* con lo que es capaz de reducir la velocidad y el voltaje de los núcleos para minimizar el consumo reduciendo el consumo a tan sólo 22w.

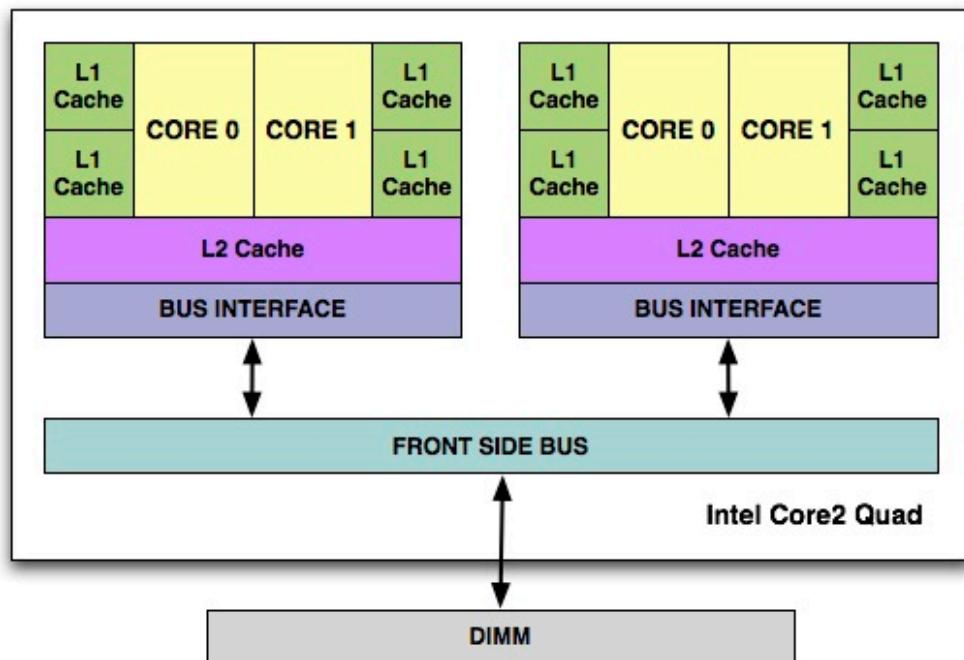

#### 2.4.4 Procesador Intel Core2 Quad

Siguiendo esta línea Intel ha diseñado un conjunto de procesadores multi-núcleo y multi-hilo. De este conjunto estudiaremos Intel Core2 Quad. A continuación nos encontramos en la Figura 12, el esquema principal de este procesador multi-núcleo y sus unidades funcionales.

Figura 11. Diagrama de componentes del procesador Multi-núcleo Intel Core2 Quad

El procesador Intel Core2 Quad está formado por dos procesadores Intel Core2 Duo cada uno con de 2 núcleos de procesamiento empaquetados en un mismo chip. Los dos procesadores de doble núcleo están interconectados mediante un bus frontal y la memoria principal.

La jerarquía de memoria del Intel Core2 Quad es de dos niveles. Cada núcleo dispone a su vez de dos memorias cache de primer nivel (L1) de 32KB para instrucciones y 32KB para datos. Cada uno de los procesadores de doble núcleo que hay dentro del chip dispone de una memoria cache de segundo nivel (L2) de 3MB.

Además el Intel Core 2 Quad incorpora un bus frontal (*Front Side Bus*), que interconecta los dos procesadores de doble núcleo entre ellos y con la memoria principal, capaz de ofrecer un ancho de banda de 12.4GB/s, para lograr unas comunicaciones de entrada/salida de alta velocidad. [5-6]

## 2.5 Factores que impiden un alto rendimiento en sistemas multi-Core/multi-Thread

Como hemos visto hasta el momento podría parecer que el aumento paulatino del número de núcleos de un procesador parece la solución a la necesidad de aumentar la capacidad de procesamiento en los procesadores, pero no es así. El rendimiento de las aplicaciones en entornos multi-núcleo/multi-hilo no escala linealmente, y al aumentar el número de hilos con los que se ejecuta la aplicación no se reduce linealmente el tiempo de cómputo de manera transparente al programador. A continuación enunciaremos los principales factores que impiden esta escalabilidad lineal en los entornos de programación multi-núcleo/multi-hilo.

### 2.5.1 Overheads por creación/eliminación de hilos

Uno de los factores que impiden la escalabilidad lineal en sistemas multi-núcleo/multi-hilo, es el proceso de creación y eliminación de hilos que trabajan en dicho sistema paralelo, que supone un coste de tiempo extra (“overhead”) sobre el total del tiempo de ejecución.

Este “overhead” ha de ser mucho menor al tiempo total de ejecución para que sea práctico paralelizar una aplicación. La importancia de este “overhead” dependerá de la relación entre el tiempo de ejecución de la zona paralela por un hilo entre el número total de hilos y el tiempo empleado en la creación, eliminación de hilos, el reparto del cómputo y la obtención del resultado final. A continuación en la figura 13 mostramos de manera gráfica este “overhead”.

**Figura 13.** Paradigma fork-join en la computación paralela

### 2.5.2 Balanceo incorrecto del volumen de cómputo

Otro de los factores que impiden la escalabilidad lineal en sistemas multi-núcleo/multi-hilo es la incorrecta distribución del volumen de cómputo por hilo, que implica que algunos hilos finalicen sus tareas antes que el resto y por tanto tendrán que esperar a que el resto acabe para proseguir la ejecución.

Esta espera supone un coste en ciclos de reloj del procesador desaprovechados y por lo tanto un *overhead*. En el diseño de aplicaciones paralelas es muy importante una óptima asignación del trabajo a realizar a cada uno de los hilos. A la hora de programar una aplicación paralela uno de los puntos a tener en cuenta es como de bien se reparte el cómputo entre los diferentes hilos (*computation load balance*).

Este *overhead* se puede reducir aunque no eliminar totalmente, asignando el trabajo dinámicamente entre los diferentes hilos que participan en la ejecución. Por contrapartida se genera otro pequeño *overhead* asociado al cómputo necesario para gestionar la asignación dinámica.

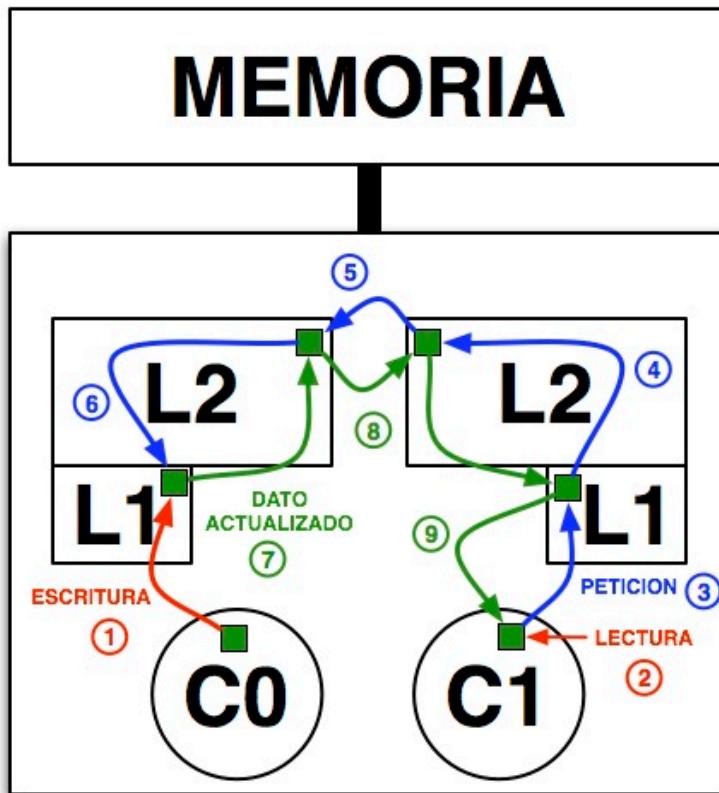

### 2.5.3 Las comunicaciones entre hilos de ejecución

Otro de los factores que impiden la escalabilidad lineal en sistemas multi-núcleo/multi-hilo es la comunicación entre los núcleos. En una región paralela los hilos de una ejecución multi-hilo trabajan de manera independiente y con datos independientes, pero por las características de las aplicaciones, en algún momento necesitarán intercambiar estos datos entre ellos. Este intercambio de datos se realiza de manera transparente al hilo ya que éste únicamente accederá a unas posiciones de memoria que previamente otro hilo habrá modificado. Esto aunque es transparente para el hilo no está libre de coste en tiempo. Los datos que hayan sido modificados en la cache de un hilo tendrán que ser copiados a la cache del hilo que los necesita en ese momento.

Hay que tener en cuenta que el coste de comunicar datos modificados por hilos que se ejecutan dentro de un mismo procesador es muy inferior al coste de comunicar datos entre hilos que se ejecutan en núcleos de diferentes procesadores.

Estos costes suponen un *overhead* a considerar a la hora de diseñar una aplicación multi-hilo. Habrá que prestar especial atención a la localidad temporal y espacial de la aplicación y a la descomposición por dominio, intentando primero minimizar las comunicaciones entre hilos que se ejecutan en distintos procesadores y segundo minimizar las comunicaciones entre hilos que se ejecutan en el mismo procesador.

## 2.6 OpenMP

A continuación en este apartado se describirá OpenMP y se darán algunos ejemplos de uso, únicamente para que el lector tenga una visión general. Este apartado es una breve introducción, y en ningún momento pretende ser un manual.

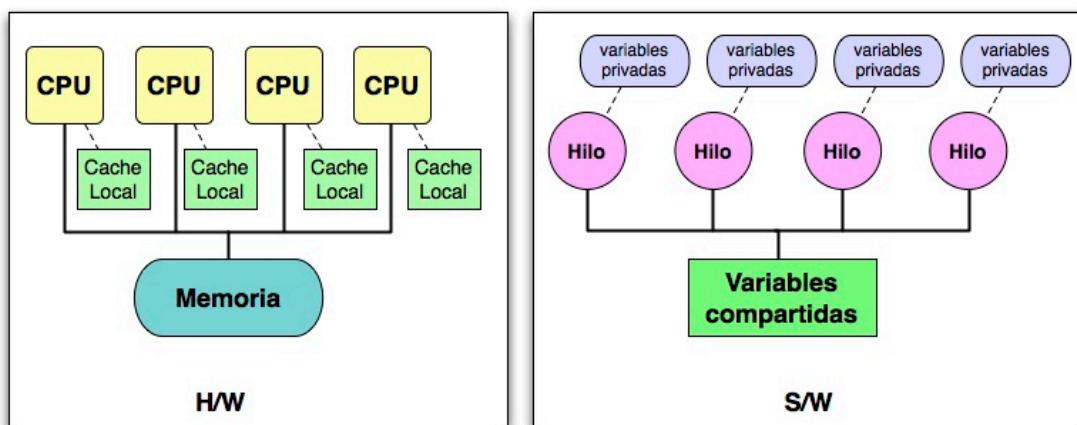

OpenMP es un modelo de programación paralela para procesadores de memoria compartida y distribuida. OpenMP es el estándar de “facto” para aplicaciones paralelas donde los diferentes hilos de ejecución colaboran para realizar una misma tarea en paralelo. En el modelo de memoria compartida que mostramos en la figura 14 los diferentes hilos de ejecución comparten un único espacio de direcciones, se comunican y se sincronizan entre ellos mediante variables compartidas.

En el modelo de variables compartidas la visión estándar del paralelismo es el fork/join. Cuando un programa empieza la ejecución, un único hilo, llamado “master” está activo. El master ejecuta toda la parte secuencial del algoritmo. En el momento que el programador especifica que pueden hacer operaciones en paralelo, el master hace un “fork”, (crea o despierta) un conjunto hilos de ejecución adicionales. El hilo master y el resto de hilos creados trabajan concurrentemente durante la sección paralela definida y una vez acabada esta sección, los hilos creados mueren o se suspenden, i el flujo de control vuelve hacia un único hilo, el master. A esta última acción se le llama “join”.

**Figura 14.** Modelo de programación paralela de memoria compartida

OpenMP no es un nuevo lenguaje de programación, consiste en un conjunto de directivas para el compilador, un conjunto de funciones de soporte y variables de entorno para el tratamiento de hilos de ejecución (comunicación y sincronización de hilos). Estas directivas se añaden al código fuente y describen el paralelismo de éste para que las interprete el compilador. Actualmente estas directivas están definidas para los lenguajes Fortran, C y C++.

La sintaxis básica de OpenMP es: # **pragma omp <directiva> [clausula, ...]** Podemos ver en la Figura 15, un ejemplo de código en C donde se marcan a estas directivas de OpenMP en azul. Este código define 3 vectores de 10.000 posiciones. Inicializa el primer vector con la suma de los valores del segundo y el tercer vector. Podemos ver justamente antes de la instrucción *for* del bucle, la directiva OpenMP “#*pragma omp for*”. Con esta directiva explicitamos la paralelización del bucle de manera que se dividirán las iteraciones del bucle entre los diferentes hilos de ejecución de forma equitativa.

```

int a[10000], b[10000], c[10000] ;

#pragma omp parallel

#pragma omp for

for (i = 0; i < 10000; i++) {

a[i] = b[i] + c[i];

}

```

**Figura 15.** Código C con las directivas OpenMP para la paralelización de un bucle for

A continuación citaremos las directivas, cláusulas y funciones de OpenMP más usadas en el desarrollo de aplicaciones paralelas y adjuntaremos una breve explicación.

### 2.6.1 Directivas

A continuación en este apartado citamos las directivas OpenMP más usadas en el desarrollo de aplicaciones paralelas.

- **parallel:** Indica la parte del código que se podrá ejecutar por varios hilos

- **for:** Indica que a cada hilo se le asigna una parte del for a ejecutar (paralelismo de datos).

- **sections:** Indica que cada sección será ejecutada por un hilo (paralelismo funcional).

- **single:** Indica que esta sección será ejecutada por un único hilo.

- **master:** Indica que esta sección será ejecutada por el master-hilo.

- **parallel for**: Combinación de parallel (fork) + for (repartición del for entre los hilos).

- **parallel sections**: Combinación de parallel (fork) + sections (asignación de cada sección a un hilo).

- **critical**: Indica que la sección será de exclusión mutua.

- **barrier**: Indica la necesidad de una sincronización de los hilos en este punto.

## 2.6.2 Cláusulas

En este apartado citamos las cláusulas OpenMP más usadas en el desarrollo de aplicaciones paralelas.

- **schedule** (static | dynamic | guided | runtime [, chunk]): Determina de que forma se realizará la asignación del trabajo a los hilos.

- **private** (variable [,variable, ...]): Indica que las variables que aparecen en la cláusula serán privadas, cada hilo tendrá una copia independiente.

## 2.6.3 Funciones

En este apartado citamos las cláusulas OpenMP más usadas en el desarrollo de aplicaciones paralelas.

- **omp\_set\_num\_thread**: Fija el número de hilos que se crearán en los forks de las regiones paralelas de código.

- **omp\_get\_num\_threads**: Devuelve el número de hilos activos en la región paralela actual.

- **omp\_get\_thread\_num**: Devuelve el identificador del hilo que lo ejecuta.

- **omp\_get\_num\_procs**: Devuelve el número de cores del multi-core en el que se está ejecutando el hilo.

[7]

## 2.7 PAPI (Performance Application Programming Interface)

De la misma forma que en el apartado anterior, se realizará una breve descripción, sin que ésta pretenda ser un manual. El objetivo es únicamente que el lector tenga una visión general de PAPI.

PAPI es una API para acceder a los contadores hardware de rendimiento, disponibles en la mayoría de los procesadores actuales. Estos contadores son un conjunto de registros que cuentan la ocurrencia de determinados eventos en el procesador y nos ayudan a conocer de manera más fidedigna el comportamiento de nuestra aplicación al ejecutarse en el sistema.

El kernel del sistema operativo puede necesitar algunas modificaciones para permitir acceder a los contadores hardware mediante el uso de PAPI. Dependiendo del procesador y del sistema operativo puede llegar a ser necesario aplicar un parche (PerfCtr o perfmon2) y recompilar el kernel.

Una aplicación compilada en un sistema cuyo kernel tiene PAPI instalado, puede ser ejecutada en cualquier sistema con el parche (PerfCtr o perfmon2), siempre que ambos sistemas tengan una arquitectura y sistema operativo compatibles.

Al incorporar PAPI a una sección de código, es posible pasar (como parámetro) a la aplicación, los nombres de los contadores hardware de los que se quiere obtener información. La extracción de esta información de los contadores hardware nos ayudará posteriormente al análisis del rendimiento de nuestras aplicaciones en los diferentes sistemas paralelos ayudándonos a localizar la causa real de los diferentes overheads que aparezcan. En la figura 16 mostramos algunos de los contadores hardware a los que se puede acceder mediante la utilización de PAPI.

[8]

| Nombre de contador | Descripción                          |

|--------------------|--------------------------------------|

| PAPI_L1_DCM        | Level 1 data cache                   |

| PAPI_L1_ICM        | Level 1 instruction cache            |

| PAPI_L2_DCM        | Level 2 data cache                   |

| PAPI_L2_ICM        | Level 2 instruction cache            |

| PAPI_L3_DCM        | Level 3 data cache                   |

| PAPI_L3_LDM        | Level 3 load misses                  |

| PAPI_L1_LDM        | Level 1 load misses                  |

| PAPI_L2_LDM        | Level 2 load misses                  |

| PAPI_TOT_INS       | Instructions completed               |

| PAPI_INT_INS       | Integer instructions                 |

| PAPI_FP_INS        | Floating point instructions          |

| PAPI_BR_INS        | Branch instructions                  |

| PAPI_TOT_CYC       | Total cycles                         |

| PAPI_FML_INS       | Floating point multiply instructions |

| PAPI_FAD_INS       | Floating point add instructions      |

### **3 Descripción del problema: Eliminación Gaussiana**

La resolución de sistemas lineales es uno de los problemas más antiguos de la matemática. Muchos de los problemas actuales de la ingeniería y la ciencia pueden modelarse como un complejo sistema de ecuaciones lineales.

La resolución de sistemas de ecuaciones lineales posee una infinidad de aplicaciones: análisis estructural, estimación, predicción y más generalmente en la aproximación de problemas no lineales de análisis numérico. Las aplicaciones de la programación Lineal son muy extensas entre ellas destacan los problemas de flujos de redes y problemas de flujos de mercancías, problemas relacionados con la economía (gestión de inventarios, la cartera, planificación de campañas de publicidad, reducir gastos y maximizar ingresos...). El análisis numérico se encarga de modelar a través de reglas matemáticas simples procesos matemáticos más complejos utilizados en la vida real por físicos e ingenieros para todo tipo de resolución y aproximación de problemas reales.

Es por este motivo que se dedican muchos esfuerzos en desarrollar algoritmos eficientes que resuelvan estos problemas en un lapso de tiempo menor con una mayor precisión para obtener la solución más adecuada.

La Eliminación Gaussiana es un eficiente algoritmo para la resolución de sistemas de ecuaciones lineales  $Ax=b$ . Este algoritmo está dividido en dos fases: La Eliminación hacia delante y la sustitución inversa. En el apartado siguiente (1.1) se definirán una serie de conceptos que se necesitarán más adelante. Y en el apartado 1.2 se realizará una descripción general del algoritmo y en el 1.3 se describirán las diferentes estrategias a seguir para generar el código serie del algoritmo.

#### **3.1 Resolución de sistemas lineales**

Una ecuación es la expresión matemática de una condición de igualdad. Un sistema de “k” ecuaciones es la expresión matemática de un conjunto de “k” condiciones de igualdad. Una ecuación lineal de “n” variables  $x_0, x_1, \dots, x_{n-1}$  es una ecuación que puede ser representada de la forma  $a_0x_0 + a_1x_1 + \dots + a_{n-1}x_{n-1} = b$ , donde  $a_0, a_1, \dots, a_{n-1}$  y  $b$  son constantes.

Por tanto llamamos sistema de ecuaciones lineal o sistema lineal a un conjunto de ecuaciones lineales finito. Y llamamos solución  $(S_0, S_1, \dots, S_{n-1})$  de un sistema de ecuaciones al conjunto de valores que al realizar las sustituciones  $x_0 = S_0, x_1 = S_1, \dots, x_{n-1} = S_{n-1}$  satisface todas las ecuaciones del sistema lineal.

Un sistema lineal de “m” ecuaciones y “n” variables puede representarse de la siguiente forma:

$$\begin{aligned}

a_{0,0}x_0 + a_{0,1}x_1 + \cdots + a_{0,n-1}x_{n-1} &= b_0 \\

a_{1,0}x_0 + a_{1,1}x_1 + \cdots + a_{1,n-1}x_{n-1} &= b_1 \\

a_{2,0}x_0 + a_{2,1}x_1 + \cdots + a_{2,n-1}x_{n-1} &= b_2 \\

&\vdots \\

a_{m-1,0}x_0 + a_{m-1,1}x_1 + \cdots + a_{m-1,n-1}x_{n-1} &= b_m

\end{aligned}$$

**Figura 17.** Sistema de ecuaciones

y se suele representar de la forma  $Ax = b$  donde  $A$  es una matriz  $n \times m$ ,  $x$  es el vector columna de incógnitas de longitud  $n$  y  $b$  es el vector de columna términos independientes de longitud  $m$ .

$$\left( \begin{array}{ccc|c} a_{0,0} & \cdots & a_{0,n-1} & b_0 \\ \vdots & \ddots & \vdots & \vdots \\ a_{m-1,0} & \cdots & a_{m-1,n-1} & b_{m-1} \end{array} \right) \cdot \left( \begin{array}{c} x_0 \\ \vdots \\ x_{n-1} \end{array} \right) = \left( \begin{array}{c} b_0 \\ \vdots \\ b_{m-1} \end{array} \right)$$

**Figura 18.** Sistema lineal de ecuaciones

El sistema lineal asociado también puede representarse a través de su matriz ampliada, que no es más que la matriz asociada al sistema de coeficientes añadiéndole la columna de términos independientes. En la figura 19 se muestra un ejemplo de una matriz ampliada en la que aparece la columna final con los términos independientes de cada ecuación del sistema.

$$\left[ \begin{array}{cccc|c} 4 & 6 & 2 & -2 & 8 \\ 2 & 0 & 5 & -2 & 4 \\ -4 & -3 & -5 & 4 & 1 \\ 8 & 18 & -2 & 3 & 40 \end{array} \right]$$

**Figura 19.** Ejemplo de una matriz ampliada.

Una matriz  $A$ , es una matriz banda de anchura  $w$  si :  $i - j > w \rightarrow a_{ij} = 0$  y  $j - i > w \rightarrow a_{ij} = 0$ . Es decir si todos los elementos no nulos de  $A$  se encuentran en la diagonal cuyo rango lo marca la constante  $w$ .

$$\begin{bmatrix} a_{00} & a_{01} & 0 & 0 & 0 \\ a_{10} & a_{11} & a_{12} & 0 & 0 \\ 0 & a_{21} & a_{22} & a_{23} & 0 \\ 0 & 0 & a_{32} & a_{33} & a_{34} \\ 0 & 0 & 0 & a_{43} & a_{44} \end{bmatrix}$$

**Figura 20.** Representación de una matriz banda con  $W = 1$

La matriz será triangular superior si :  $i > j \rightarrow a_{ij} = 0$ .

$$\begin{bmatrix} a_{00} & 0 & 0 & 0 & 0 \\ a_{10} & a_{11} & 0 & 0 & 0 \\ a_{20} & a_{21} & a_{22} & 0 & 0 \\ a_{30} & a_{31} & a_{32} & a_{33} & a \\ a_{40} & a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix}$$

**Figura 21.** Representación de una matriz triangular superior

La matriz será triangular inferior si:  $i < j \rightarrow a_{ij} = 0$ .

$$\begin{bmatrix} a_{00} & a_{01} & a_{02} & a_{03} & a_{04} \\ 0 & a_{11} & a_{12} & a_{13} & a_{14} \\ 0 & 0 & a_{22} & a_{23} & a_{24} \\ 0 & 0 & 0 & a_{33} & a_{34} \\ 0 & 0 & 0 & 0 & a_{44} \end{bmatrix}$$

**Figura 22.** Representación de una matriz triangular inferior

La matriz será estrictamente diagonal dominante si  $|a_{i,j}| > \left| \sum_{i \neq j}^n a_{i,j} \right| ; 0 \leq i \leq n$ .

$$\begin{bmatrix} 5 & 2 & 1 & -1 & 0 \\ 1 & 9 & 0 & -2 & 3 \\ 2 & -1 & -6 & 0 & 2 \\ 1 & 0 & 2 & 5 & -1 \\ 3 & 2 & -1 & 1 & -9 \end{bmatrix} \quad \begin{aligned} |5| &> (2 + 1 + |-1| + 0) \\ |9| &> (1 + 0 + |-2| + 3) \\ |-6| &> (|-1| + 2 + 0 + 2) \\ |5| &> (0 + 2 + 1 + |-1|) \\ |-9| &> (2 + |-1| + 1 + 3) \end{aligned}$$

**Figura 23.** Representación de una matriz diagonal dominante

## 3.2 Descripción general del algoritmo de Eliminación Gaussiana

La eliminación Gaussiana es un eficiente algoritmo para la resolución de sistemas lineales  $Ax=b$ . Este algoritmo consta de dos fases. La primera fase llamada “Forward elimination” (o Eliminación hacia delante) reduce el sistema lineal mediante transformaciones elementales transformándolo en un sistema triangular superior o genera una ecuación sin solución indicando que el sistema lineal no tiene solución. En la segunda fase se emplea el algoritmo llamado “back substitution” (o sustitución inversa), para encontrar la solución del sistema  $Ax=b$ , cuando la matriz A es triangular superior.

La Eliminación Gaussiana es *numéricamente estable*<sup>1</sup> para matrices diagonal dominantes y para matrices *definidas positivas*<sup>2</sup>. Para las matrices en general, la Eliminación Gaussiana suele ser estable si se usa el pivotaje total o parcial que describiremos más adelante en el apartado 3.2, aunque existen ejemplos para estos métodos que son inestables.

### 3.2.1 Primera Fase: Eliminación (Forward Elimination)

Durante la primera fase del algoritmo las transformaciones elementales nos ayudan a simplificar el sistema sin variar su solución y son las siguientes:

- Multiplicar cada término de una ecuación por una constante no nula.

- Intercambiar dos ecuaciones.

- Añadir un múltiple de una ecuación a otra ecuación del sistema.

A continuación mostramos un ejemplo gráfico de la aplicación del algoritmo de resolución de la Eliminación Gaussiana sin pivotaje sobre un sistema de ecuaciones lineales, representados mediante su matriz ampliada.

---

<sup>1</sup> En el análisis numérico, la estabilidad numérica es una propiedad de los algoritmos numéricos. Describe cómo los errores en los datos de entrada se propagan a través del algoritmo. En un método estable, los errores debidos a las aproximaciones se atenúan a medida que la computación procede. En un método inestable, cualquier error en el procesamiento se magnifica conforme el cálculo procede. Métodos inestables generan rápidamente basura y son inútiles para el procesamiento numérico.

<sup>2</sup> Una matriz definida positiva es una matriz cuadrada de elementos complejos que tiene la característica de ser igual a su propia traspuesta conjugada.

$$\begin{array}{c}

\left[ \begin{array}{cccc|c} 4 & 6 & 2 & -2 & 8 \\ 2 & 0 & 5 & -2 & 4 \\ -4 & -3 & -5 & 4 & 1 \\ 8 & 18 & -2 & 3 & 40 \end{array} \right] \xrightarrow{\substack{F2 + 1/2F1 \\ F3 + F1 \\ F4 - 2F1}} \left[ \begin{array}{cccc|c} 4 & 6 & 2 & -2 & 8 \\ 0 & -3 & 4 & -1 & 0 \\ 0 & 3 & -3 & 2 & 9 \\ 0 & 6 & -6 & 7 & 24 \end{array} \right] \xrightarrow{\substack{F3 + F2 \\ F4 + 2F2}} \\

(a) \qquad \qquad \qquad (b)

\end{array}$$

$$\begin{array}{c}

\left[ \begin{array}{cccc|c} 4 & 6 & 2 & -2 & 8 \\ 0 & -3 & 4 & -1 & 0 \\ 0 & 0 & 1 & 1 & 9 \\ 0 & 0 & 2 & 5 & 24 \end{array} \right] \xrightarrow{F4 - 2F3} \left[ \begin{array}{cccc|c} 4 & 6 & 2 & -2 & 8 \\ 0 & -3 & 4 & -1 & 0 \\ 0 & 0 & 1 & 1 & 9 \\ 0 & 0 & 0 & 3 & 6 \end{array} \right] \\

(c) \qquad \qquad \qquad (d)

\end{array}$$

**Figura 24.** Ejemplo del algoritmo de Eliminación Gaussiana.

La figura 24 muestra el proceso de la primera fase del algoritmo la “eliminación hacia delante”. La matriz (a) representa el sistema original de ecuaciones lineales. El primer paso transforma la matriz (a) en la matriz (b) usando el primer elemento de la primera fila de la matriz 4 y con este valor como referencia transforma la matriz para convertir en ceros todos los elementos que están por debajo de éste. A la fila dos le resta un medio de la fila 1( $f_2 - \frac{1}{2}f_1$ ). A la fila 3 le suma la fila (  $\cancel{f_3}$  ). Y a la fila cuatro le resta dos veces la primera fila (  $\cancel{f_4}$  ).

El segundo paso transforma la matriz (b) en la matriz (c) usando el siguiente elemento de la diagonal -3 para aplicar las trasformaciones oportunas para triangular la matriz hasta llegar a la matriz (d). Una vez ha aplicado todas las transformaciones necesarias para convertir el sistema de ecuaciones lineal en una matriz triangular superior es cuando podemos aplicar el algoritmo sustitución inversa para resolver el sistema.

### 3.2.2 Segunda Fase: Sustitución inversa (Back substitution)

El algoritmo de sustitución inversa es un algoritmo que resuelve sistemas lineales  $Ax=b$ , cuando la matriz A es triangular superior. En la figura 25 mostramos el pseudocódigo de la sustitución inversa que aplicaremos seguidamente en el siguiente ejemplo.

```

A[0..n-1,0..n-1] //matriz de coeficientes

b[0..n-1] //vector de constantes

x[0..n-1] //vector de soluciones

for i = n-1 down to 1 do

x[i] = b[i]/A[i][i]

for j = 0 to i-1 do

b[j] = b[j] - x[i]*A[i][j]

A[i][j] = 0 //línea opcional

end for

end for

```

**Figura 25.** Pseudo código del algoritmo de sustitución inversa.

Supongamos que tenemos el siguiente sistema de ecuaciones lineal triangulado previamente en la primera fase del algoritmo de la Eliminación Gaussiana, eliminación hacia delante siguiente:

**Figura 26.** Sistema de ecuaciones

|                                                                                                                                                    |                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| $\left[ \begin{array}{cccc c} 1 & 1 & -1 & 4 & 8 \\ 0 & -2 & -3 & 1 & 5 \\ 0 & 0 & 2 & -3 & 0 \\ 0 & 0 & 0 & 2 & 4 \end{array} \right]$ <p>(a)</p> | $\left[ \begin{array}{cccc c} 1 & 1 & -1 & 0 & 0 \\ 0 & -2 & -3 & 0 & 3 \\ 0 & 0 & 2 & 0 & 6 \\ 0 & 0 & 0 & 2 & 4 \end{array} \right]$ <p>(b)</p> |

| $\left[ \begin{array}{cccc c} 1 & 1 & 0 & 0 & 3 \\ 0 & -2 & 0 & 0 & 12 \\ 0 & 0 & 2 & 0 & 6 \\ 0 & 0 & 0 & 2 & 4 \end{array} \right]$ <p>(c)</p>   | $\left[ \begin{array}{cccc c} 1 & 0 & 0 & 0 & 9 \\ 0 & -2 & 0 & 0 & 12 \\ 0 & 0 & 2 & 0 & 6 \\ 0 & 0 & 0 & 2 & 4 \end{array} \right]$ <p>(d)</p>  |

**Figura 27.** Ejemplo de la fase de sustitución inversa del algoritmo de Eliminación Gaussiana.

La figura 27 muestra el proceso de la segunda fase del algoritmo la “sustitución inversa” del sistema anterior. La matriz (a) representa el sistema original de ecuaciones lineales. La primera iteración transforma la matriz (a) en la matriz (b) resolviendo la última ecuación de forma directa ya que sólo tenemos una incógnita.

De la última ecuación obtenemos la solución de la variable  $x_3$ . Con el valor de ésta variable  $\boxed{x_3}$  se simplifican el resto de ecuaciones sustituyendo el valor de la variable y sumándose al término independiente cada ecuación.

La segunda iteración transforma la matriz (b) en la matriz (c) resolviendo esta vez, la tercera ecuación que tras la primera iteración se ha sustituido el valor de la variable  $x_3$  y ahora sólo posee una incógnita, de forma directa. De esta tercera ecuación obtenemos el valor de la variable  $x_2$ . Con el valor de ésta última variable obtenida se vuelven a actualizar el resto de ecuaciones que se encuentran por encima de la tercera ecuación, simplificándolas con el valor X del mismo modo que en la iteración anterior.

La tercera y última iteración transforma la matriz (c) en la matriz (d) resolviendo con en las iteraciones anteriores la segunda ecuación, obteniendo así de esta forma el valor de la variable  $x_1$ . Con el valor de X se sustituye la primera ecuación dejándola con una sola incógnita. De este último paso obtenemos directamente el valor de la variable X, de manera que ya hemos resuelto el sistema.

### 3.3 Pivoteo: estrategia para aumentar la precisión y estabilidad

Como ya comentábamos con anterioridad, la Eliminación Gaussiana es numéricamente estable para matrices diagonal dominantes y definidas positivas, ya que los pivotes se encuentran en la diagonal. Cuando estos valores de la diagonal tienen un valor pequeño se pueden producir grandes errores de redondeo y divisiones por cero provocando una inestabilidad del algoritmo e imprecisando el resultado final. Esta inestabilidad se resuelve empleando la estrategia del pivotaje total o parcial.

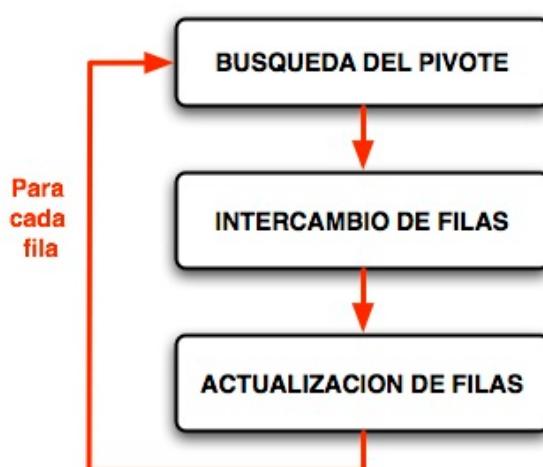

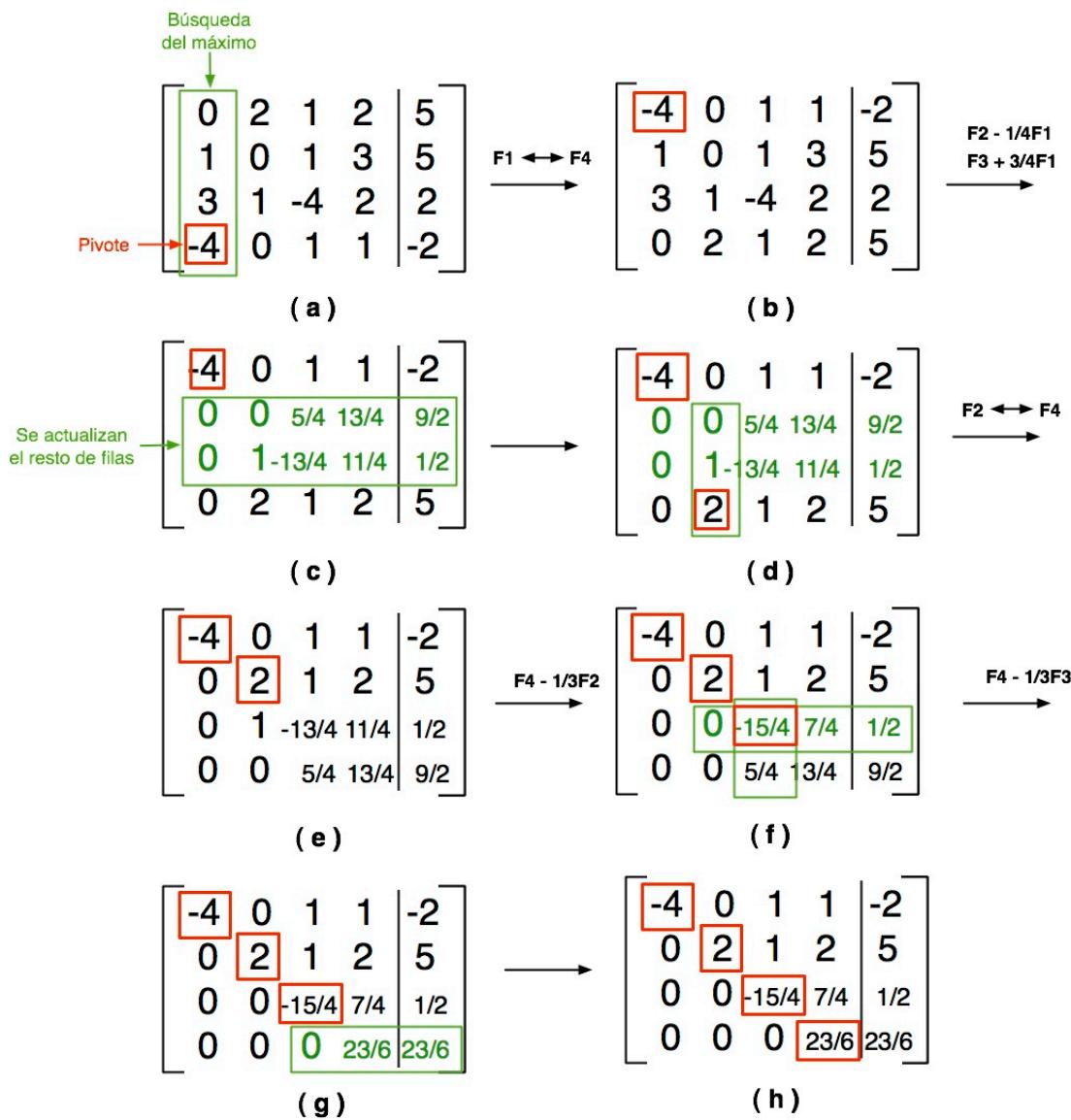

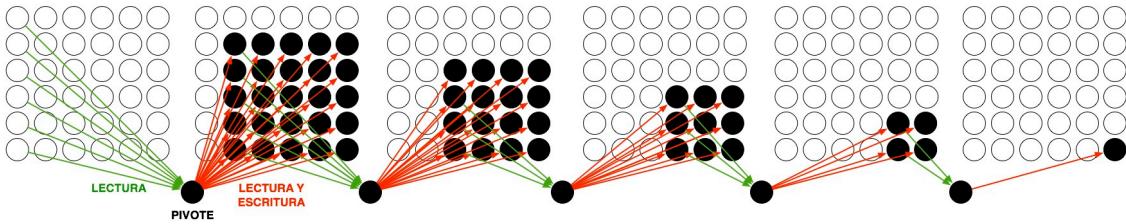

En la figura 28 podemos observar una representación gráfica simplificada de la estrategia del pivotaje. El pivotaje está formado por tres fases bien diferenciadas. La búsqueda del pivote, dónde se selecciona el valor absoluto más grande. El intercambio de filas i/o columnas para colocar el nuevo pivote en la diagonal de la matriz y la actualización de filas, dónde se aplica la Eliminación hacia delante escalonando la matriz.

**Figura 28.** Representación simplificada del algoritmo de Eliminación Gaussiana con pivotaje por filas.

El pivotaje total selecciona la posición de la fila o columna con el valor absoluto más grande e intercambia las filas y columnas situando el elemento escogido en la diagonal de la matriz, la posición del pivote.

El pivotaje parcial se puede realizar por filas o por columnas. Con el pivotaje parcial, el algoritmo selecciona la posición con el valor absoluto más grande de la columna intercambiando las filas de la matriz para colocar este valor en la diagonal de la matriz, si nos referimos al pivotaje parcial por filas o la posición con el valor absoluto más grande de la fila e intercambiado las columnas, si nos referimos al pivotaje parcial por columnas.

El pivotaje parcial se diferencia del pivotaje total en que el pivotaje total intercambia las filas y columnas para colocar los valores absolutos más grandes en la diagonal de la matriz mientras que el parcial tan sólo selecciona los valores absolutos e intercambia valores para filas o columnas según de que pivotaje parcial estemos hablando.

En la práctica el pivotaje total puede consumir mucho tiempo computacionalmente hablando ya que para cada iteración se debe buscar el máximo entre todas las posiciones de las filas y columnas de la matriz sin escalar. El pivotaje parcial es generalmente suficiente para reducir de manera adecuada el error del algoritmo.

Seguidamente mostramos dos ejemplos gráficos de la aplicación sobre un sistema de ecuaciones lineales, representados mediante la matriz ampliada de éste, del algoritmo de resolución de la Eliminación Gaussiana con pivotaje parcial. En el primer ejemplo se muestra la resolución mediante el pivotaje por filas y en el segundo se muestra la resolución mediante el pivotaje por columnas.

En la figura 29 se muestra un ejemplo del algoritmo de Eliminación Gaussiana con pivotaje parcial por filas.

La matriz (a) representa el sistema original de ecuaciones lineal. El primer paso de la primera fase del algoritmo es la búsqueda del pivote, el elemento con el valor máximo de la primera columna, en este caso el  $| -4 |$ .

Este valor pasará a ser el pivote. El segundo paso de la primera fase del algoritmo es el intercambio de filas, en este caso, de la primera fila por la fila del pivote para colocar de esta forma el pivote en la diagonal de la matriz para mejorar la estabilidad del algoritmo, este paso lo podemos observar en la matriz (b). El tercer y último paso de la primera fase del algoritmo es la actualización de las filas posteriores a la fila pivote, con éste. Como se observa en la matriz (c) se han eliminando todos los valores de la primera columna con el pivote.

En la siguiente iteración se selecciona el máximo valor de la siguiente columna entre las filas restantes como se observa en la matriz (d). Esta vez en nuevo pivote se encuentra en la cuarta fila de la matriz, con el valor  $| 2 |$ . De nuevo se intercambian la segunda fila con la cuarta para colocar el nuevo pivote en la diagonal de la matriz como se observa en la matriz (c) y se procede a actualizar las filas restantes obteniendo la matriz (f). En este caso sólo se actualiza la tercera fila, ya que el valor de la cuarta fila ya es un 0.

Una vez actualizadas las filas se procede con la tercera iteración del algoritmo. En esta

iteración el pivote seleccionado,  $|-\frac{15}{4}|$ , se encuentra en la tercera fila por lo que no es necesario intercambiar filas, ya que el pivote se encuentra en la diagonal. Con el nuevo pivote seleccionado se procede a actualizar la última fila de la matriz, dejando por tanto la matriz finalmente escalonada como se observa en la matriz (g).

La matriz resultado de la primera fase del algoritmo la eliminación hacia delante, matriz (h), es una matriz triangular superior, en la que la diagonal está formada por todos los pivotes calculados en las diferentes iteraciones. Una vez aplicadas todas las transformaciones elementales de la primera fase del algoritmo, en la segunda fase, se le aplica el algoritmo de sustitución inversa a la matriz diagonal superior (h) obtenida para resolver el sistema.

**Figura 29.** Ejemplo del algoritmo de Eliminación Gaussiana con pivotaje por filas

A continuación se muestra paso a paso como se aplica esta segunda fase del algoritmo a la matriz obtenida en la primera fase (h) en la figura 30.

|                                                                                                                                                     |                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| $\left[ \begin{array}{cccc c} -4 & 0 & 1 & 1 & -2 \\ 0 & 2 & 1 & 2 & 5 \\ 0 & 0 & -15/4 & 7/4 & 1/2 \\ 0 & 0 & 0 & 23/6 & 23/6 \end{array} \right]$ | <b>(a)</b><br>$x_3$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                                                                                                    |                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| $\left[ \begin{array}{cccc c} -4 & 0 & 1 & 0 & -3 \\ 0 & 2 & 1 & 0 & 3 \\ 0 & 0 & -15/4 & 0 & 15/4 \\ 0 & 0 & 0 & 23/6 & 23/6 \end{array} \right]$ | <b>(b)</b><br>$x_2$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                                                                                                    |                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| $\left[ \begin{array}{cccc c} -4 & 0 & 0 & 0 & -2 \\ 0 & 2 & 0 & 0 & 4 \\ 0 & 0 & -15/4 & 0 & 15/4 \\ 0 & 0 & 0 & 23/6 & 23/6 \end{array} \right]$ | <b>(c)</b><br>$x_1$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                                                                                                    |                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| $\left[ \begin{array}{cccc c} -4 & 0 & 0 & 0 & -2 \\ 0 & 2 & 0 & 0 & 4 \\ 0 & 0 & -15/4 & 0 & 15/4 \\ 0 & 0 & 0 & 23/6 & 23/6 \end{array} \right]$ | <b>(d)</b><br>$x_0$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

**Figura 30.** Ejemplo de la fase de sustitución inversa del algoritmo de Eliminación Gaussiana.

La figura 30 muestra el proceso de la segunda fase del algoritmo la “sustitución inversa” del sistema anterior.

La matriz (a) representa la matriz ampliada del sistema original de ecuaciones lineales reducida mediante la primera fase del algoritmo de la Eliminación Gaussiana con pivotaje parcial por filas. En la primera iteración de la sustitución inversa, transforma la matriz (a) en la matriz (b) resolviendo la última ecuación de forma directa ya que sólo tenemos una incógnita. De la última ecuación obtenemos la solución de la variable  $x_3$ . Con el valor de ésta variable  $x_3 = 1$  se simplifican el resto de ecuaciones sustituyendo el valor de la variable  $x_3$  y sumándoselo al término independiente cada ecuación.

La segunda iteración transforma la matriz (b) en la matriz (c). Tras la primera iteración, la tercera ecuación sólo posee una incógnita al el valor de la variable  $x_3$  se resuelve de forma directa. De esta tercera ecuación obtenemos el valor de la variable  $x_2$ . Con el valor de ésta última variable obtenida se vuelven a actualizar el resto de ecuaciones que se encuentran por encima de la tercera ecuación, simplificándolas con el valor X del mismo modo que en la iteración anterior.

La tercera iteración transforma la matriz ( en la matriz (d) resolviendo con en las iteraciones anteriores la segunda ecuación, obteniendo así de esta forma el valor de la la variable  $x_1$ . Con el valor de  $x_1 = 2$  se sustituye la primera ecuación dejándola con una sola incógnita, por lo que no es necesario una iteración más. De este último paso obtenemos directamente el valor de la variable X, de manera que ya se ha obtenido la solución al sistema de ecuaciones lineal.

La figura 31 muestra un ejemplo del algoritmo de Eliminación Gaussiana con pivotaje parcial por columnas donde la matriz (a) representa el sistema original de ecuaciones lineal.

En la primera iteración se localiza el valor máximo de la primera fila,  $|6|$ . Este pasará a ser el nuevo pivote. En la matriz (b) se observa el intercambio de la primera columna por la columna del pivote para colocar de esta forma el pivote en la diagonal de la matriz  $\boxed{\text{X}}$ . Una vez está colocado el pivote se aplica la actualización de las filas posteriores a la fila pivote eliminando todos los valores de la primera columna con el pivote, escalonando así la matriz. El resultado se observa en la matriz (c).

En la siguiente iteración se selecciona el máximo valor de la siguiente fila  $|5|$ , entre las columnas restantes como se observa en la matriz (d). Esta primera fase del algoritmo de Eliminación Gaussiana con pivotaje parcial por columnas se repite para todas las filas hasta obtener la matriz (h), triangular superior, en la que la diagonal está formada por todos los pivotes calculados anteriormente.

Una vez finalizada la primera fase del algoritmo, se promediaría a aplicar la segunda fase del algoritmo, “la sustitución inversa”, a la matriz diagonal superior obtenida (h) para encontrar la solución al sistema de ecuaciones lineal.

The diagram illustrates the Gaussian Elimination process with column pivoting for a 4x5 matrix. The steps are as follows:

- (a)**: Initial matrix with the first column highlighted. A green arrow labeled "Búsqueda del máximo" points to the first column. A red arrow labeled "Pivote" points to the first element of the first column (6).

- (b)**: Result of swapping column 1 and column 2. A green arrow labeled "c<sub>1</sub> ↔ c<sub>2</sub>" indicates the swap. Row operations: F<sub>3</sub> + 1/2F<sub>1</sub> and F<sub>4</sub> - 3F<sub>1</sub>.

- (c)**: Result of eliminating the first column from rows 3 and 4. A green arrow labeled "Se actualizan el resto de filas" indicates the update. Row operations: F<sub>3</sub> + 1/2F<sub>1</sub> and F<sub>4</sub> - 3F<sub>1</sub>.

- (d)**: Matrix after row operations. A green arrow labeled "c<sub>2</sub> ↔ c<sub>3</sub>" indicates the swap of columns 2 and 3.

- (e)**: Result of eliminating the second column from rows 3 and 4. Row operations: F<sub>3</sub> + 4/5F<sub>2</sub> and F<sub>4</sub> - 8/5F<sub>2</sub>.

- (f)**: Result of row operations 5F<sub>3</sub> and 5F<sub>4</sub>. A green arrow labeled "c<sub>3</sub> ↔ c<sub>4</sub>" indicates the swap of columns 3 and 4.

- (g)**: Result of eliminating the third column from row 4. Row operation: F<sub>4</sub> - 31/7F<sub>3</sub>.

- (h)**: Final upper triangular matrix (echelon form) with the diagonal elements highlighted in red. A green arrow labeled "7F<sub>4</sub>" indicates the final row operation.

Figura 31. Ejemplo del algoritmo de Eliminación Gaussiana con pivotaje por columnas.

En resumen, muchos de los problemas actuales de la ingeniería y la ciencia pueden modelarse como un complejo sistema de ecuaciones lineales, por ello la resolución de sistemas de ecuaciones lineales posee una infinidad de aplicaciones y es por este motivo que se existe mucho interés en el desarrollo de aplicaciones eficientes que resuelvan estos complejos sistemas lineales en un lapso de tiempo menor con una mayor precisión para obtener la solución más adecuada.

La Eliminación Gaussiana es un eficiente algoritmo para la resolución de sistemas de ecuaciones lineales dividido en dos fases la primera llamada “Eliminación hacia delante” en la que se reduce la matriz ampliada del sistema a una matriz diagonal superior y la segunda fase llamada “sustitución inversa” en la que partiendo de la matriz diagonal superior, se obtienen los valores de las diferentes incógnitas resolviendo así el sistema lineal. La Eliminación Gaussiana, es más estable en las matrices diagonal dominantes, es por este motivo por el cual se aplica la estrategia del pivotaje total o parcial para precisar el resultado.

Una vez descrito el problema, en el capítulo siguiente, se realizará un estudio en profundidad del algoritmo secuencial de la Eliminación Gaussiana con pivotaje parcial independiente del procesador. Se codificará el algoritmo serie y se propondrán una serie de posibles optimizaciones a realizar para ser más tarde evaluadas en diferentes microprocesadores.

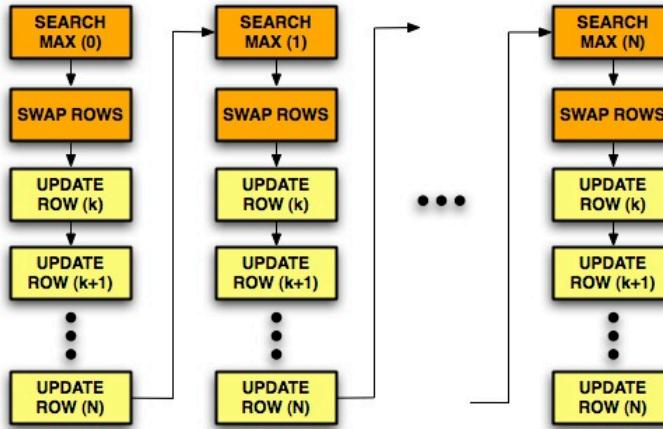

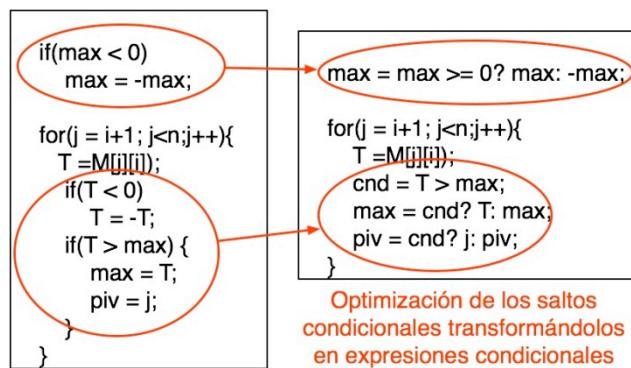

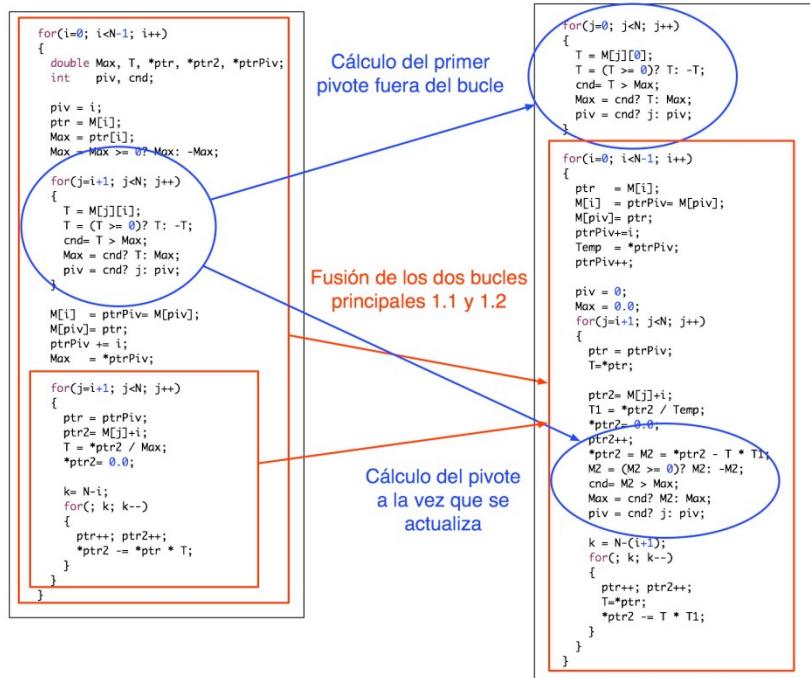

[2,9]

## 4 Análisis y Evaluación del algoritmo secuencial

En este capítulo se realizará el estudio del algoritmo secuencial para la Eliminación Gaussiana. En el apartado 4.1 efectuará el diseño del algoritmo serie de la aplicación. Mostraremos el pseudocódigo del algoritmo que más tarde se implementará en código C y las mejoras introducidas para realizar la versión base de la aplicación. Para ello se realizará en el apartado 4.2 un análisis computacional del algoritmo independiente del procesador, para determinar los parámetros que determinan el problema, las zonas de mayor peso computacional, para ser optimizadas. A continuación en el apartado 4.3 se realizarán, a partir de los datos obtenidos en el estudio anterior, una serie de propuestas de optimizaciones. Estas optimizaciones darán lugar a diferentes versiones de la aplicación, que se ejecutarán en cada uno de los procesadores considerados, tomando medidas del tiempo de ejecución y de valores de ciertos contadores hardware del procesador.

En este capítulo se considerará la ejecución sobre un único núcleo de procesamiento. Será en el capítulo siguiente donde se estudiará la ejecución en un procesador multi-núcleo del algoritmo de Eliminación Gaussiana. Para ello, habrá que dividir la ejecución en múltiples hilos de procesamiento.

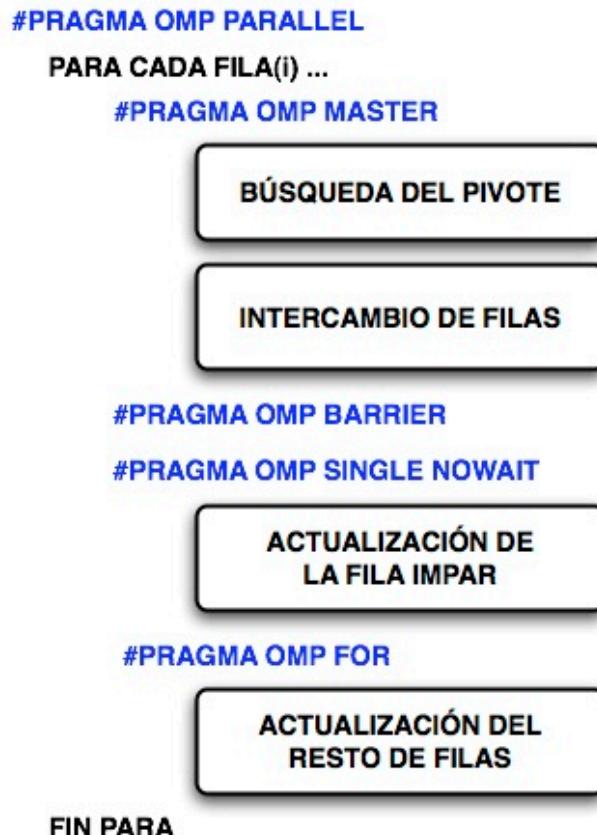

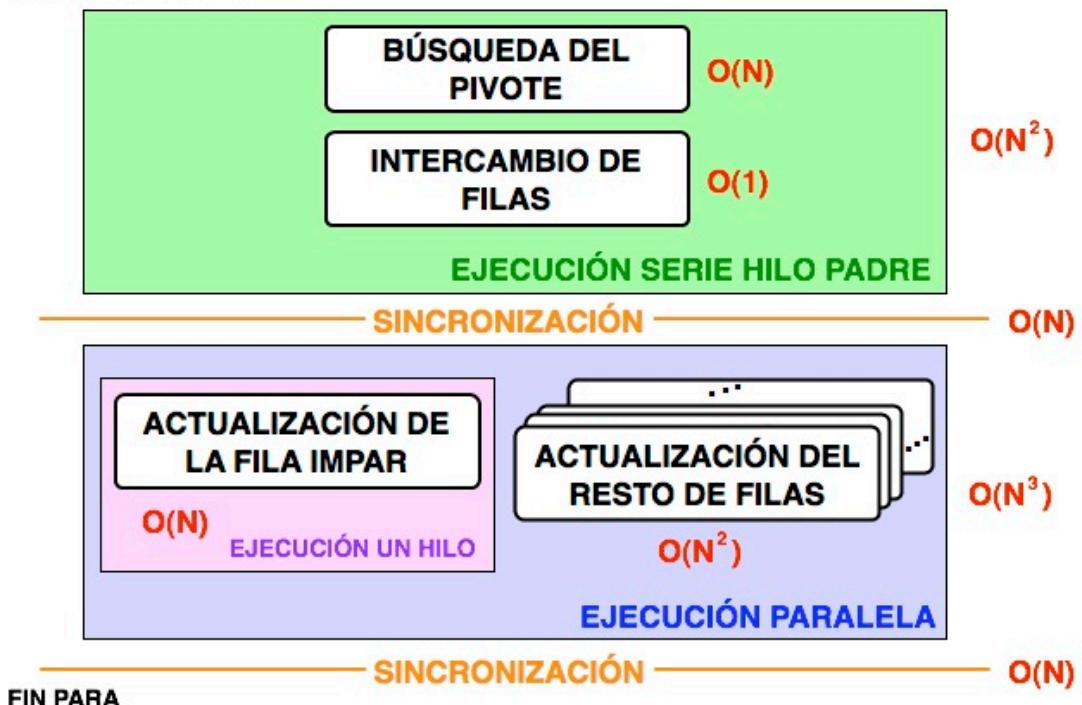

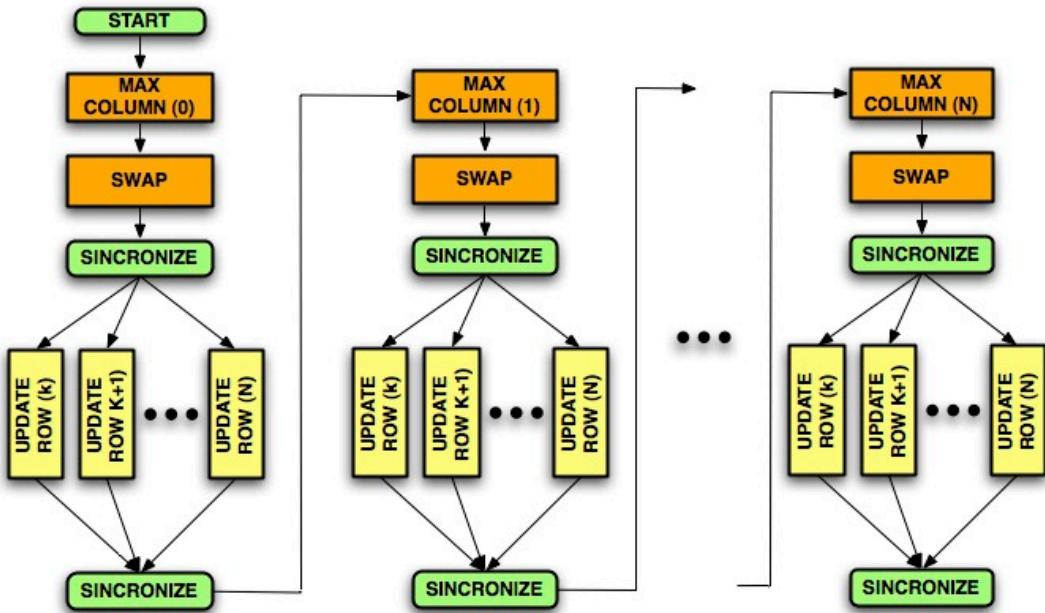

### 4.1 Diseño del algoritmo serie