## Correlation between the nanoscale electrical and morphological properties of crystallized hafnium oxide-based metal oxide semiconductor structures

V. Iglesias, M. Porti, M. Nafría, X. Aymerich, P. Dudek, T. Schroeder, and G. Bersuker

Citation: Applied Physics Letters 97, 262906 (2010); doi: 10.1063/1.3533257

View online: http://dx.doi.org/10.1063/1.3533257

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/97/26?ver=pdfcov

Published by the AIP Publishing

## Re-register for Table of Content Alerts

Create a profile.

Sign up today!

## Correlation between the nanoscale electrical and morphological properties of crystallized hafnium oxide-based metal oxide semiconductor structures

V. Iglesias, <sup>1,a)</sup> M. Porti, <sup>1</sup> M. Nafría, <sup>1</sup> X. Aymerich, <sup>1</sup> P. Dudek, <sup>2</sup> T. Schroeder, <sup>2</sup> and G. Bersuker <sup>3</sup>

(Received 20 May 2010; accepted 2 December 2010; published online 30 December 2010)

The relationship between electrical and structural characteristics of polycrystalline  $HfO_2$  films has been investigated by conductive atomic force microscopy under ultrahigh vacuum conditions. The results demonstrate that highly conductive and breakdown (BD) sites are concentrated mainly at the grain boundaries (GBs). Higher conductivity at the GBs is found to be related to their intrinsic electrical properties, while the positions of the electrical stress-induced BD sites correlate to the local thinning of the dielectric. The results indicate that variations in the local characteristics of the high-k film caused by its crystallization may have a strong impact on the electrical characteristics of high-k dielectric stacks. © 2010 American Institute of Physics. [doi:10.1063/1.3533257]

Electrical characteristics of highly scaled devices may exhibit significant device-to-device variability, which is ultimately associated with the discrete nature of charge and matter. Several variability sources, such as random dopant distribution, line edge roughness, gate oxide roughness, and granularity of the poly-Si gate (either during deposition or fabrication), have been identified. In particular, as modeling results have shown, these may lead to variations in threshold voltage and mobility values.<sup>2</sup> Crystallization of the high-k gate dielectrics may also be expected to affect the electrical properties of scaled devices, leading-for instance-to device-to-device variations in the gate leakage current that influences device reliability. However, since standard characterization techniques can provide only averaged information about the electrical properties of devices, addressing the origin of the variability in the nanoscale requires advanced characterization methods with a high lateral resolution. In this respect, scanning probe microscopes have been shown to be powerful tools for characterizing the electrical properties of dielectrics.<sup>3–7</sup> Conductive atomic force microscopy (CAFM) has been widely used to evaluate the electrical conduction of polycrystalline high-k dielectrics. Whereas some studies have suggested that conduction through the polycrystalline films occurs primarily through the bulk of the grains, 8,9 others have demonstrated that the leakage current flows preferentially through the grain boundaries (GBs), 3,7,10,11 which agrees with the results of ab initio calculations. 12 Besides generally expected differences associated with the intrinsic properties of the studied materials, such a discrepancy could be caused by the limits of the CAFM lateral resolution, which are close to the characteristic GB width. As a consequence, topography can be directly correlated with current maps only under carefully selected measurement conditions. In this work, CAFM used under ultrahigh vacuum (UHV) conditions, which improve lateral resolution, has been employed to evaluate, at the nanoscale,

the impact of crystallization of the high-k material in  $HfO_2/SiO_2/Si$  structures on the morphological and electrical properties (and their relation, if any) of the stack.

Gate stack dielectrics consisting of a 5 nm thick atomic layer deposition  $HfO_2$  film and a 1 nm  $SiO_2$  interface layer grown on a Si epitaxial P-substrate were investigated. The gate stack was annealed at  $1000\,^{\circ}$ C, which induced the crystallization of the high-k layer. Following earlier suggestions <sup>13</sup> to achieve the high lateral resolution required to correlate the morphological and electrical properties of the nanocrystalline dielectric, CAFM measurements were performed in UHV ( $\sim 10^{-10}$  mbar). Current and topography maps were obtained in contact mode by applying a constant voltage to the tip (substrate grounded). Since under UHV conditions higher resistant tips are necessary to improve the lateral resolution, <sup>13</sup> although their radius is larger than that of other conductive tips, diamond-coated silicon tips were used for the conductivity measurements. <sup>14</sup>

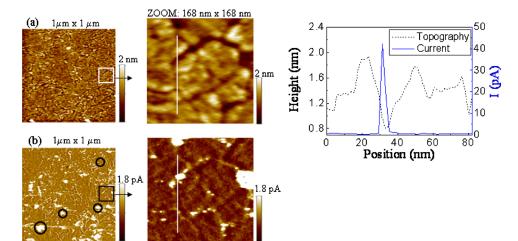

The morphology of the high-k layer was investigated first. Figure 1(a) presents a topographical image showing a surface  $(1 \times 1 \ \mu m^2)$  with a granular structure. A statistical analysis of the grains shows that their average size is  $\sim$ 15 nm, <sup>15</sup> information that is compatible with the grain size obtained from transmission electron microscope images. This granular structure has been attributed to the crystallization of the high-k layer after annealing; grains in the image correspond to individual (or a cluster of) randomly oriented nanocrystals separated by GBs (depressions in the image). Note that direct information about the oxide thickness tox cannot be obtained from this image because tox depends not only on the morphology of the scanned top (dielectric/gate) interface [Fig. 1(a)], but also on that of the dielectric/ substrate interface, and this information is not independently available in this experiment. However, it is reasonable to assume a similar grain morphology at both interfaces. Therefore, Fig. 1 suggests that  $t_{ox}$  is less at the grain boundaries (depression). The width of the GBs has been statistically estimated to be ~4 nm. This value is slightly higher than what is obtained from ab initio calculations (<2 nm),

<sup>&</sup>lt;sup>1</sup>Dept. Enginyeria Electrònica, Universitat Autònoma de Barcelona, Edifici Q, 08193 Bellaterra, Spain <sup>2</sup>Innovations for High Performance Microelectronics (IHP), Frankfurt (Oder), Germany <sup>3</sup>SEMATECH, Austin, Texas, 78741 USA

$<sup>^{\</sup>rm a)}$  Electronic mail: vanessa.iglesias@uab.es. Tel.: +34935813521. FAX: +34935812600.

FIG. 1. (Color online) (a) Topographical and (b) current images obtained at 6.5 V of the  $HfO_2/SiO_2/Si$  structure (area of  $1\times1~\mu m^2$ ). A granular pattern is associated with the presence of nanocrystals. A zoom-in of both images is also shown. Circles in the current image correspond to the BD sites. (c) Topographical (dashed line) and current (continuous line) profiles obtained along the white lines in the zoom-in images show higher leakage current at the topographical depressions associated with the grain boundaries.

probably because we are close to the resolution limits of this technique.

Bias voltage applied: 6.5V

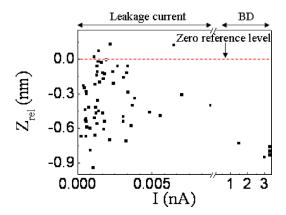

The effect of the high-k crystallization on the electrical properties of the gate stack was investigated based on the image of the leakage current through the film [Fig. 1(b)] measured at 6.5 V at the same surface region as in Fig. 1(a). Note that in Fig. 1(b) a granular pattern overlaps with that of the topographical image (an enlargement of both images is also shown); leakage sites with current values on the order of picoamperes above the background level, which was measured over the nanocrystals, are mainly located at GBs. 16,17 For example, Fig. 1(c) shows topographical (dashed line) and current (continuous line) profiles across the white line plotted in Figs. 1(a) and 1(b) (zooms). Note that the positions with higher currents (leakage sites) are located along the topographical depressions associated with GBs. This qualitative observation has been verified statistically. Figure 2 shows the Z-axis relative position  $(Z_{rel})$  of more than 70 leakage spots (exhibiting a current greater than 0.5 pA) with respect to the Z-axis mean value of the image, which has been arbitrarily considered to be the zero-reference level (dashed line) versus their maximum current. Note that most of the leakage sites are below this reference level (i.e., in the topographical depressions and, therefore, in the GBs). The average size of the leakage sites, those with current values of

FIG. 2. (Color online) Z-axis relative position ( $Z_{\rm rel}$ ) of more than 70 leakage spots (with currents greater than 0.5 pA) vs their maximum current.  $Z_{\rm rel}$  of a leakage site is defined as the Z-position with respect to Z-axis mean value of the image, which has been arbitrarily considered to be the zero-reference level (dashed line). Note that most are located in topographical depressions

picoamperes, was also statistically estimated to be  $\sim 3$  nm, which is comparable to the width of the GBs, consistent with the suggestion that they are confined within the GB region. In addition to these leakage sites, breakdown (BD) sites [in circles in Fig. 1(b), with currents greater than nanoamperes, can also be identified. These BD events were probably triggered by the constant voltage applied during the scan to obtain the topographical and the current image. Note that the BD spots are much larger ( $\sim$ 20 nm) than the leakage spots, suggesting that BD may affect a larger area surrounding the GB. However, within the BD spot, the current measured over the GB region ( $\sim$ nA) is much greater than the current through the adjacent nanocrystals ( $\sim$ pA). Therefore, the results show a clear correlation between the oxide morphology (determined by the crystallization of the high-k layer) and the electrical properties of the gate dielectric: conductivity through the dielectric film is higher along the GBs, and the leakage and BD sites are mostly located near the GBs.

The localization of leakage and BD spots around the GBs could be related to (1) a decrease in the dielectric thickness, as observed on the topographical images, or (2) a higher density of traps at the GB, which could support the trap-assisted tunneling (TAT) current. To determine which factor dominates (if any), we investigated whether there is any correlation between the current through the leakage or BD sites and their  $Z_{\text{rel}}$ , which reflects the dielectric thickness at a given location: lower Z<sub>rel</sub> values correspond to thinner dielectrics. Note that, in Fig. 2, two groups of sites can be distinguished. The first corresponds to the sites with the currents in the picoampere-range, where there is no apparent correlation between the leakage currents and dielectric thicknesses. This suggests that the conductivity of the leakage sites is primarily determined by the electrical properties of the GBs, which could be related to the O-vacancies accumulated at the GBs, as pointed out in other works, 12,18 rather than the dielectric thickness across the GB area. The second group in Fig. 2 includes the sites with the current values in the nanoampere-range (BD spots). These sites exhibit lower Z<sub>rel</sub>'s, which correspond to the locations with smaller dielectric thicknesses. These results indicate that BD in the HfO<sub>2</sub>/SiO<sub>2</sub>/Si stack is assisted by the higher electric field across the stack. However, the exact mechanism of the BD remains unclear. One of the possible scenarios is that a lodrop across the underlying SiO<sub>2</sub> film, causing its BD and, subsequently, overall stack BD, at this location. <sup>19</sup> Further studies of the HfO<sub>2</sub>/metal stacks will help address the role of the electric field in the BD process.

In conclusion, the results show that crystallization of the HfO<sub>2</sub> layer is an important source of the nanoscale variability that affects the electrical properties of the material. As follows from the topography maps, the GBs correspond to the regions of thinner dielectrics. The accompanied current maps demonstrate that the leakage (in the picoampere-range) and BD (in the nanoampere-range) sites are concentrated mostly near the GBs. While the size of the leakage sites is comparable to the width of the GBs, the BD sites seem to encompass much larger areas reaching into the adjacent nanocrystals, although the conductivity across the BD area is still much higher over the GB. The analysis shows that the electrical properties of the GBs (e.g., the presence of the TAT defects) are responsible for their higher conductance than that of the grains. The BD sites were found to be induced primarily at the strongly depressed GB sites, suggesting a significant contribution from the electric field to the overall BD of the multilayer dielectric stack. Further work is needed to clarify the role of the dielectric thickness in the BD mechanism.

This work was partially supported by the Spanish MICINN (Grant Nos. TEC2007-61294/MIC and BES-2008-007974) and the Generalitat de Catalunya (Grant No. 2009SGR-783).

- <sup>4</sup>K. S. Yew, Y. C. Ong, D. S. Ang, K. L. Pey, G. Bersuker, P. S. Lysaght, and D. Heh, Proceedings of the Solid-State Device Research Conference, Tokyo, 2009.

- <sup>5</sup>P. Fiorenza, W. Polspoel, and W. Vandervorst, Appl. Phys. Lett. **88**, 222104 (2006).

- <sup>6</sup>W. Frammelsberger, G. Benstetter, J. Kiely, and R. Stamp, Appl. Surf. Sci. **252**, 2375 (2006).

- <sup>7</sup>V. Yanev, M. Rommel, M. Lemberger, S. Petersen, B. Amon, T. Erlbacher, A. J. Bauer, H. Ryssel, A. Paskaleva, W. Weinreich, C. Fachmann, J. Heitmann, and U. Schroeder, Appl. Phys. Lett. **92**, 252910 (2008).

- <sup>8</sup>N. Menou, M. Popovici, S. Clima, K. Opsomer, W. Polspoel, B. Kaczer, G. Rampelberg, K. Tomida, M. A. Pawlak, C. Detavernier, D. Pierreux, J. Swerts, J. W. Maes, D. Manger, M. Badylevich, V. Afanasiev, T. Conard, P. Favia, H. Bender, B. Brijs, W. Vandervorst, S. Van Elshocht, G. Pouertois, D. J. Wouters, S. Biesemans, and J. A. Kittl, J. Appl. Phys. 106, 094101 (2009).

- <sup>9</sup>N. Menou, X. P. Wang, B. Kaczer, W. Polspoel, M. Popovici, K. Opsomer, M. A. Pawlak, W. Knaepen, C. Detavernier, T. Blomberg, D. Pierreux, J. Swerts, J. W. Maes, P. Favia, H. Bender, B. Brijs, W. Vandervorst, S. Van Elshocht, D. J. Wouters, S. Biesemans, and J. A. Kittl, IEEE International Electron Devices Meeting (IEDM), 2008, Vol. 1, p. 929.

- <sup>10</sup>O. Bierwagen, L. Geelhaar, X. Gay M. Piešinš, H. Riechert, B. Jobst, and A. Rucki, Appl. Phys. Lett. **90**, 232901 (2007).

- <sup>11</sup>J. Y. Son and Y. H. Shin, Appl. Phys. Lett. **92**, 222106 (2008).

- <sup>12</sup>K. McKenna and A. Shluger, Appl. Phys. Lett. **95**, 222111 (2009).

- <sup>13</sup>M. Lanza, M. Porti, M. Nafría, X. Aymerich, E. Whittaker, and B. Hamilton, Microelectron. Reliab. **50**, 1312 (2010).

- K. Kyuno, K. Kita, and A. Toriumi, Appl. Phys. Lett. 86, 063510 (2005).

M.-Y. Ho, H. Gong, G. D. Wilk, B. W. Busch, M. L. Green, P. M. Voyles, D. A. Muller, M. Bude, W. H. Lin, A. See, M. E. Loomans, S. K. Lahiri, and P. I. Räisänen, J. Appl. Phys. 93, 1477 (2003).

- <sup>16</sup>X. Yu, J. Huang, M. Yu, and C. Zhu, IEEE Electron Device Lett. 28, 373 (2007).

- <sup>17</sup>Y. Kim, G. Gebara, M. Freiler, J. Barnet, D. Riley, J. Chen, K. Torres, J. Lim, B. Foran, F. Shaapur, A. Agarwal, P. Lysaght, G. A. Brown, C. Young, S. Bothakur, H.-J. Li, B. Nguyen, P. Zeitzoff, G. Bersuker, D. Derro, R. Bergmann, R. W. Murto, A. Hou, H. R. Huff, E. Shero, C. Pomarede, M. Givens, M. Mazanec, and C. Werkhoven, IEEE International Electron Devices Meeting (IEDM), 2001, pp. 455–458.

- <sup>18</sup>G. Bersuker, J. Yum, V. Iglesias, M. Porti, M. Nafría, K. McKenna, A. Shluger, P. Kirsch, and R. Jammy, Proceedings of the European Solid-State Device Research Conference, 2010, pp. 333–336.

- <sup>19</sup>L. Aguilera, M. Porti, M. Nafría, and X. Aymerich, IEEE Electron Device Lett. 27, 157 (2006).

<sup>&</sup>lt;sup>1</sup>International Technology Roadmap for Semiconductors, Semiconductor Industry Association, http://public.itrs.net.

<sup>&</sup>lt;sup>2</sup>A. Asenov, S. Roy, R. A. Brown, G. Roy, C. Alexander, C. Riddet, C. Millar, B. Cheng, A. Martinez, N. Seoane, D. Reid, M. F. Bukhori, X. Wang, and U. Kovac, Electron Device Meeting Technical Digest, 2008, Vol. 1, p. 421.

<sup>&</sup>lt;sup>3</sup>M. Lanza, M. Porti, M. Nafría, X. Aymerich, G. Benstetter, E. Lodermeier, H. Ranzinger G. Jaschke, S. Teichert, L. Wilde, and P. Michalowski, IEEE Trans. Nanotechnol. **PP**, 1 (2010).