## Degradation of polycrystalline HfO2-based gate dielectrics under nanoscale electrical stress

V. Iglesias, M. Lanza, K. Zhang, A. Bayerl, M. Porti, M. Nafría, X. Aymerich, G. Benstetter, Z. Y. Shen, and G. Bersuker

Citation: Applied Physics Letters 99, 103510 (2011); doi: 10.1063/1.3637633

View online: http://dx.doi.org/10.1063/1.3637633

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/99/10?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Photo-induced tunneling currents in MOS structures with various HfO2/SiO2 stacking dielectrics AIP Advances **4**, 047112 (2014); 10.1063/1.4871407

Publisher's Note: "Degradation of polycrystalline HfO2-based gate dielectrics under nanoscale electrical stress" [Appl. Phys. Lett. 99, 103510 (2011)]

Appl. Phys. Lett. 99, 239901 (2011); 10.1063/1.3666227

Breakdown and degradation of ultrathin Hf-based ( Hf O 2 ) x ( Si O 2 ) 1 x gate oxide films

J. Vac. Sci. Technol. B 27, 443 (2009); 10.1116/1.3025822

Current conduction mechanisms in atomic-layer-deposited HfO 2 / nitrided SiO 2 stacked gate on 4H silicon carbide

J. Appl. Phys. 103, 084113 (2008); 10.1063/1.2908870

Statistics of electrical breakdown field in Hf O 2 and Si O 2 films from millimeter to nanometer length scales Appl. Phys. Lett. **91**, 242905 (2007); 10.1063/1.2822420

## Degradation of polycrystalline HfO<sub>2</sub>-based gate dielectrics under nanoscale electrical stress

V. Iglesias, <sup>1</sup> M. Lanza, <sup>1,a)</sup> K. Zhang, <sup>2</sup> A. Bayerl, <sup>1</sup> M. Porti, <sup>1</sup> M. Nafría, <sup>1</sup> X. Aymerich, <sup>1</sup> G. Benstetter, <sup>3</sup> Z. Y. Shen, <sup>2,a)</sup> and G. Bersuker <sup>4</sup>

(Received 28 April 2011; accepted 12 August 2011; published online 9 September 2011; corrected 16 September 2011)

The evolution of the electrical properties of  $HfO_2/SiO_2/Si$  dielectric stacks under electrical stress has been investigated using atomic force microscope-based techniques. The current through the grain boundaries (GBs), which is found to be higher than thorough the grains, is correlated to a higher density of positively charged defects at the GBs. Electrical stress produces different degradation kinetics in the grains and GBs, with a much shorter time to breakdown in the latter, indicating that GBs facilitate dielectric breakdown in high-k gate stacks. © 2011 American Institute of Physics. [doi:10.1063/1.3637633]

Intrinsic process variability and aging mechanisms can strongly affect the performance and reliability of MOS devices. The polycrystallization of high-k-based gate dielectrics, which can occur even during relatively low temperature device fabrication steps (e.g., atomic layer deposition, forming gas anneal), has been identified as one of the device-to-device variability sources. Conductive atomic force microscope (CAFM) experiments, which may address nanoscale topographical and electrical properties of dielectric stacks, 2-5 reveal significantly higher leakage currents through the grain boundaries (GBs) than through nanocrystal (NC) grains.<sup>3,6</sup> Theoretical models' suggest that the current through the GBs could be related to a large concentration of oxygen vacancies at the GBs, which might effectively act as conductive paths through the dielectric film.8 However, the relative role of the vacancies vs. topological factors (e.g., the dielectric thickness at the GB region) as well as the evolution of GB electrical properties under electrical stress remains unexplored. In this work, a CAFM technique has been applied to investigate conduction characteristics of the GBs in polycrystalline HfO<sub>2</sub> gate dielectrics. Kelvin probe force microscope (KPFM) measurements were used to assess the charge state of defects in these structures.

The dielectric stack under investigation consists of a 5 nm atomic layer deposited (ALD)  $HfO_2$  film (annealed at  $1000\,^{\circ}$ C to induce polycrystallization) and a  $\sim 1$  nm  $SiO_2$  interfacial layer grown on a Si substrate. Gate stack properties were investigated using CAFM (air conditions and contact mode). Current and topography maps were measured by applying voltage between the tip and the substrate, and current-voltage (*I-V*) data were collected in a ramped voltage mode at different oxide locations (GBs and grains). Some *I-V* characteristics were

also measured with a modified CAFM approach to provide a larger current dynamic range (enhanced-CAFM (Ref. 9)). KPFM (air conditions) was employed to obtain topography and the probe tip-sample contact potential difference (CPD) map, which is proportional to the amount of charge trapped in the dielectric at the probe tip position. <sup>10</sup>

Topographical (a) and CPD (b) images obtained with the KPFM on a fresh (before electrical stress) gate stack are shown in Fig. 1. The map of the topographical depressions associated with the GBs (Ref. 3) and higher CPD signals overlap. A higher CPD signal can be interpreted as downward band bending, 11,12 which indicates a larger concentration of positive charges at a given location. Note that the concentration of positive charges (based on the CPD signal) at the GBs does not depend on the magnitude of the surface depression at the GB, as can be seen in Fig. 1(c). Therefore, GB electrical properties are not caused by the thinner dielectric that is characteristic of the GB region. Fig. 2 shows three consecutive current maps obtained with CAFM on the same area at 4.2 V. The images again exhibit a clear granular structure (dashed lines), related to the polycrystallization of the high-k dielectric, with leaky sites (brighter areas) concentrated around the GBs. The width of the GBs (Fig. 2(a), fresh oxide) was measured to be  $\sim$ 15 nm, which is wider than simulation-based estimations, <2 nm, 8 probably due to the limited CAFM resolution in air,  $\emptyset \sim 10$  nm. <sup>13</sup> This could also explain why the grains are larger ( $\emptyset \sim 100$  nm in Fig. 2) than the size obtained by transmission electron microscopy (TEM) experiments ( $\sim$ 15 nm); the grains shown in Fig. 2 could correspond to only a subset of larger grains out of all grains in the sample. However, the limited resolution does not impede the ability of CAFM to clearly distinguish the most conductive GBs. Fig. 2 also shows larger ( $\emptyset \sim 50$  nm) leaky sites. These sites are the breakdown (BD) spots (indicated by arrows) that are centered at the GBs and laterally propagate into the surrounding grains as was discussed in Ref. 14. The evolution of the leakage current with

$<sup>^1</sup>$ Dept. Enginyeria Electrònica, Universitat Autònoma de Barcelona, Edifici Q, 08193 Bellaterra, Spain

<sup>&</sup>lt;sup>2</sup>Key Laboratory for the Physics and Chemistry of Nanodevices, Department of Electronics, Peking University, Beijing 100871, People's Republic of China

<sup>&</sup>lt;sup>3</sup>Electrical Engineering Department, University of Applied Sciences Deggendorf, Deggendorf 94469, Germany <sup>4</sup>SEMATECH, Austin, Texas 78741, USA

a) Authors to whom correspondence should be addressed. Electronic addresses: mario.lanza@uab.cat (Tel.: +34935868463, FAX: +34935812600) and zyshen@pku.edu.cn (Tel.: +861062762444, FAX: +861062759444).

FIG. 1. (Color online) Topographical (a) and CPD (b) 1  $\mu$ m  $\times$  1  $\mu$ m images. Dark lines in (a) and brighter lines in (b) correspond to GBs and higher CPD, respectively. (c) Statistical analysis of the CPD signal showing the potential on the GB sites ( $V_{GB}$ ) vs. the depth of these sites with respect to the surface of the adjacent grains ( $h_{NC}-h_{GB}$ ). Absence of a correlation between the CPD signal and magnitude of the GB recess indicates that the CPD profile is not caused by the surface topography.

subsequent scans over the same area is equivalent to that caused by electrical stress of different durations. The conductivity of the leakiest spots is observed to gradually increase under subsequent CAFM scans of the dielectric surface; in other words, under continuous stress, the GBs become more conductive. These qualitative results have been further verified by analyzing the evolution of the maximum current through different GBs as the stress proceeds. As an example, Fig. 2 shows that the maximum current through the GB crossing the A-B line for scans 1, 2, and 3 is 2.1 pA, 2.4 pA, and 4.0 pA, respectively. On the other hand, the magnitude of the background current in Fig. 2 (grains, dark areas) seems to be very stable under electrical stress

FIG. 2. (Color online) Changes of the current through the  $HfO_2$  polycrystalline layer (with the grains clearly distinguishable) obtained by three consecutive current scans of the same area (750 nm  $\times$  400 nm). The current through the GBs (outlined by the dashed lines) increases with each subsequent scan, i.e., with longer stress time. In particular, the maximum values of the current measured along the A-B line during the scans 1, 2, and 3 are 2.1 pA, 2.4 pA, and 4.0 pA, respectively. Arrows indicates BD spots, which propagate into the surrounding grains.

(0.5 pA for all images), and no new conductive spots were generated. As a result, the overall inhomogeneity of the electrical conduction through the gate stack increases with stress time, which can also be quantitatively observed from the current dispersion magnitudes after different scans. Hence, the gate stack around the grain boundary regions becomes more conductive than the grain regions under the stress.

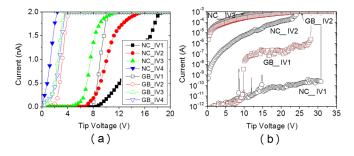

A comparative analysis of conduction characteristics of the GBs and grains used I-V curves measured on fresh and electrically stressed sites. Figure 3(a) shows typical sets of four I-V curves subsequently measured on the NCs (filled symbols) and GBs (open symbols) regions. By comparing the first measurements on the fresh locations (NC\_IV1 and GB\_IV1), it appears that the grains are less conductive than the GBs, in agreement with Ref. 15. Qualitatively different I-V dependencies measured on the GB and grain sites indicate that conduction through these structural features might be governed by different mechanisms. For the GBs, a dielectric BD was triggered by the first I-V sweep (Fig. 3(a), see differences between GB\_IV1 and GB\_IV2). On the contrary, when bias is applied to the grains (Fig. 3(a), NC\_IV1-NC\_IV4), the I-V curves progressively shift to lower voltages (stress-induced leakage current 15) and BD is not triggered until several I-V sweeps have been applied. However, when BD is reached, it seems stronger than on the GBs: NC\_IV4 exhibits an ohmic characteristic indicating its metallic nature. 16

To further analyze electrical conduction at these locations, the *I-V* curves were measured with the enhanced-CAFM (having a larger dynamic range) on both GBs and grains (Fig. 3(b)). Again, the fresh *I-V* curves show greater currents at the GB locations (with two conduction regimes,

FIG. 3. (Color online) A typical example of the evolution of the current through the grain (NC IV) and GB (GB IV) during the sequential CAFM (a) and ECAFM (b) *I-V* measurements on the same spot. The maximum currents, which can be measured by CAFM and ECAFM, are 2 nA and 1 mA in (a) and (b), respectively. The first *I-V* curves (IV1) were taken on a fresh site.

similar to those observed in other HfO<sub>2</sub>-based stacks<sup>17,18</sup>), at which the BD generally occurs at lower voltages. For grains, the initial current is, as a rule, lower, and the pattern of the two conduction regimes is not seen. Moreover, the BD is triggered only after several I-V sweeps, indicating greater grain robustness to electrical stress. 19 Higher initial currents at the GBs could be related to the higher concentration of positive charges there (Fig. 1(b)), likely associated with the segregation of positively charged oxygen vacancies at the GBs. This conclusion is consistent with earlier reported simulations of the trap-assisted tunneling current through these defects. Since the GBs in the HfO<sub>2</sub> film are more conductive, more of the voltage applied to the dielectric stack drops across the region of the interfacial SiO2 layer overlaid by the GBs than the SiO<sub>2</sub> region under the grains. This leads to greater degradation of the former, <sup>20</sup> resulting in a gradual increase in the current measured at the GBs as the stress proceeds and eventual BD of the entire gate stack.

In conclusion, analysis of the electrical properties of GBs and crystal grains in Si/SiO<sub>2</sub>/HfO<sub>2</sub> stacks before and after electrical stress demonstrates that the GBs are more conductive than the bulk of the grains. This higher electrical conductivity is caused by a different conduction mechanism through the GBs rather than the thinner dielectric regions associated with the GBs. This conclusion is supported by the observation of an elevated concentration of positive charges at GB locations, presumably due to the segregation of positively charged oxygen vacancies near the GBs, which were shown to form a conductive path through the HfO<sub>2</sub> dielectric. Under electrical stress, the GBs degrade faster than the grains, which may be attributed to the degradation of the underlying SiO<sub>2</sub> interfacial layer, eventually leading to the dielectric breakdown of the entire stack.

This work has been partially supported by the Spanish MICINN (TEC2010-16126) and the Generalitat de Catalunya (2009SGR-783).

- <sup>1</sup>A. Bayerl, M. Lanza, M. Porti, F. Campabadal, M. Nafría, and X. Aymerich, Microelectron. Eng. **88**, 1334 (2011).

- <sup>2</sup>M. Porti, M. Nafria, X. Aymerich, A. Olbrich, and B. Ebersberger, Appl. Phys. Lett. **78**(26), 4148 (2001).

- <sup>3</sup>V. Iglesias, M. Porti, M. Nafría, X. Aymerich, P. Dudek, T. Schroeder, and G. Bersuker, Appl. Phys. Lett. 97, 262906 (2010).

- <sup>4</sup>P. Fiorenza, W. Polspoel, and W. Vandervorst, Appl. Phys. Lett. **88**(22), 222104 (2006).

- <sup>5</sup>Y. L. Wu, S. T. Lin, T. M. Chang, and J. Liou, IEEE Trans. Device Mater. Reliab. **7**(2), 351 (2007).

- <sup>6</sup>V. Yanev, M. Rommel, M. Lemberger, S. Petersen, B. Amon, T. Erlbacher, A. J. Bauer, H. Ryssel, A. Paskaleva, W. Weinreich, C. Fachmann, J. Heitmann, and U. Schroeder, Appl. Phys. Lett. **92**(25), 252910 (2008).

- <sup>7</sup>K. McKenna and A. Shluger, Appl. Phys. Lett. **95**, 222111 (2009).

- <sup>8</sup>G. Bersuker, J. Yum, V. Iglesias, M. Porti, M. Nafría, K. McKenna, A. Shluger, P. Kirsch, and R. Jammy, in *Proceedings of the European 2010 Solid-State Device Research Conference*, Sept 13–17, 2010 (IEEE, Seville, Spain, 2010), pp. 333–336.

- <sup>9</sup>X. Blasco, M. Nafria, and X. Aymerich, Rev. Sci. Instrum. **76**, 016105 (2005).

- <sup>10</sup>M. Porti, M. Nafria, M. C. Blum, X. Aymerich, and S. Sadewasser, Surf. Sci. 532–535, 727 (2003).

- <sup>11</sup>C. S. Jiang, R. Noufi, J. A. AbuShama, K. Ramanathan, H. R. Moutinho, and J. Pankow, Appl. Phys. Lett. 84(18), 3477 (2004).

- <sup>12</sup>Th. Glatzel, S. Sadewasser, R. Shikler, Y. Rosenwaks, and M. Ch. Lux-Steiner, Mat. Sci. Eng. B 102, 138 (2003).

- <sup>13</sup>W. Frammelsberger, G. Benstetter, J. Kiely, and R. Stamp, Appl. Surf. Sci. 253(7), 3615 (2007).

- <sup>14</sup>V. Iglesias, M. Porti, M. Nafría, X. Aymerich, P. Dudek, and G. Bersuker, J. Vac. Sci. Technol. B 29, 01AB02 (2011)

- <sup>15</sup>K. Shubhakar, K. L. Pey, S. S. Kushvaha, S. J. O'Shea, N. Raghavan, M. Bosman, M. Kouda, K. Kakushima, and H. Iwai, Appl. Phys. Lett. 98, 072902 (2011).

- <sup>16</sup>K. Szot, W. Speier, G. Bihlmayer, and R. Waser, Nature Mater. 5, 312 (2006).

- <sup>17</sup>H. Uppal, I. Z. Mitrovic, S. Hall, B. Hamilton, V. Markevich, and A. R. Peaker, J. Vac. Sci. Technol. B 27(1), 443 (2009).

- <sup>18</sup>L. Aguilera, M. Porti, M. Nafría, and X. Aymerich, IEEE Electron Device Lett. 17(3), 157 (2006).

- <sup>19</sup>M. Lanza, M. Porti, M. Nafría, X. Aymerich, G. Benstetter, E. Lodermeier, H. Ranzinger G. Jaschke, S. Teichert, L. Wilde, and P. Michalowski, IEEE Trans. Nanotechnol. 10(2), 344 (2011).

- <sup>20</sup>G. Bersuker, D. Heh, C. D. Young, L. Morassi, A. Padovani, L. Larcher, K. S. Yew, Y. C. Ong, D. S. Ang, K. L. Pey, and W. Taylor, in *Proceedings of the 2010 International Reliability Physics Symposium*, Apr 10–14, 2011 (IEEE, Monterey, CA, 2011), pp. 373–378.