# Injected Charge to Recovery as a parameter to characterize the breakdown reversibility of ultrathin HfSiON gate dielectric

- 1 Departantenceptiggggeptsdr. PRiviantica Majativa St. Auch social de Barcolongo (CABA a Sala Ballet X. a Aymerich Spain.

- 2 IMEC Kapeldref 75, 3001 Leuven, Belgium.

Abstract— The injected charge to recovery  $(Q_R)$  is presented as a parameter to characterize the dielectric breakdown (BD) reversibility in MOSFETs with ultrathin high-k hafnium based gate dielectric. The procedure to recover the dielectric is explained and the dependences of  $Q_R$  with the current limit during BD, the polarity of the BD-recovery stresses and the number of stress cycles are analyzed.

*Index Terms*—dielectric breakdown (BD), BD reversibility, high-k, reliability, resistive switching, CMOS.

## I. INTRODUCTION

Gate dielectric breakdown (BD) is one of the most important failure mechanisms in CMOS technologies [1] and it is characterized by a change of the insulator conductivity state from a low (pre-BD state) to a higher one (post-BD condition) whose currents can differ in several orders of magnitude. Traditionally, the conductivity change due to the BD has been considered to be irreversible. However, several years ago it was shown that in SiO2, in some occasions, BD could be reversible [2], i.e., a low conductivity state could be reached after BD. More recently, we have reported the presence of two interchangeable conductivity states after BD in ultrathin Hf based gate stacks [3], when the current during the BD transient is limited. This phenomenology has strong similarities with the resistive switching (RS) effect [4-6], typically observed in MIM structures with a thicker insulator (several tenths of nm) [5] which today is having an increasing interest for its applications in RRAM devices [6]. From the reliability point of view, the existence of two conductivity states indicates that the insulator properties of the dielectric can be at least partially recovered [7, 8], and consequently, a partial restoration of the device and circuit functionality is produced [8]. However, a better understanding of the reversibility of the dielectric breakdown phenomenon needs large modelling and characterization efforts [9].

In this work, a methodology to study the BD reversibility is described and the charge-to-recovery  $(Q_{\text{R}})$  parameter is presented as a magnitude to characterize the phenomenon.

The procedure to recover the low-conductivity state of the dielectric is explained and the dependences of  $Q_{\mathbb{R}}$  and gate current with some of the electrical parameters of the BD reversibility tests analysed.

# II. SAMPLES AND EXPERIMENTAL PROCEDURE

The samples used in this work were pMOSFETs with FUSI gate electrode and a dielectric stack (EOT=1.9 nm) formed by a HfSiON film (physical thickness of 2.9 nm, 60% Hf) on top of a 1.2 nm SiO<sub>2</sub> interfacial layer. The channel length of the transistors ranges from 1  $\mu m$  to 0.15  $\mu m$ , with a fixed channel width of 0.15  $\mu m$ , which results in area values between  $\sim 0.15 \mu m^2$  to  $\sim 0.025 \ \mu m^2$ .

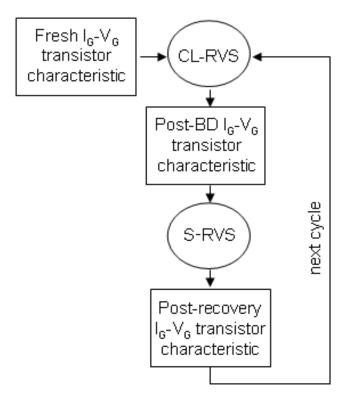

A methodology to study the BD reversibility has been developed (Figure 1). Current Limited - Ramped Voltage Stresses (CL-RVS) were applied to the gate to provoke the dielectric BD, followed by a Stepped Ramp Voltage Stress (S-RVS) [10] without current limitation, to recover the dielectric, following an iterative sequence, as shown in Figure 1. During the S-RVS the gate voltage is increased in aprox. 0.1 V every ~150 seconds. In all cases, the duration of the S-RVS was 1200s. Although the BD reversibility can be observed during constant-voltage stresses as well [8], S-RVS were chosen instead to warrant the BD recovery in a reasonable testing time, because the selection of the voltage at which the recovery can be observed during the stress time is critical. Negative voltage CL-RVS were always applied whereas the polarity of the S-RVS could be either positive or negative. The fresh I<sub>G</sub>-V<sub>G</sub> transistor characteristic was registered after each stress to observe the differences in the gate current between the broken-down (BD) and recovered (R) states.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TDMR.2010.2098032, IEEE Transactions on device and materials reliability

© 2011 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Figure 1: Iterative stress-measurement sequence designed to analyze the BD reversibility.

# III. BD REVERSIBILITY PHENOMENOLOGY

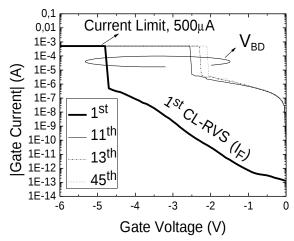

Figure 2 shows typical gate currents measured during the CL-RVS stresses used to provoke the dielectric BD. Curve  $I_{\rm F}$  corresponds to the gate current registered during the first CL-RVS (thick line). At breakdown voltage ( $V_{\rm BD}$ ), the current grows quickly up to the current limit (500uA in this case) and the BD state is reached.

Figure 2:  $I_G$ - $V_G$  curves measured during the CL-RVS that lead to the BD state after different cycles of the measurement sequence shown in Fig. 1. At  $V_{BD}$ , BD is produced and a high current level is reached (BD state).

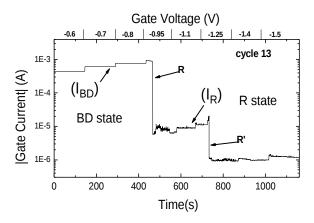

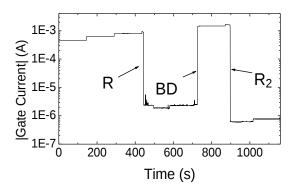

A typical example of the gate current (I<sub>G</sub>) evolution during the S-RVS is shown in Figure 3, which corresponds to I<sub>G</sub> during the S-RVS of the 13<sup>th</sup> cycle of the sequence. The voltage during the S-RVS, which starts at -0.6V and decreases every 150s until reaching -1.5V, is also indicated in the upper axis of the figure. Initially,  $I_G$  is high (~400 $\mu$ A) due to the breakdown provoked during the previous CL-RVS, and increases with the stress voltage at each voltage step (BD state). However, after  $\sim$ 420s of S-RVS, when  $V_G$ =-0.95V, I<sub>G</sub> suddenly decreases three orders of magnitude, i.e., the dielectric BD recovery (R) is observed, which indicates that the previously 'opened' BD path has been 'closed'[8]. In some cases, as in Figure 3, new recoveries can be observed (R'). If a new CL-RVS is applied after the S-RVS, the current trend shown in Figure 2 is again observed (thin curves) and a high current level will be measured in the next S-RVS until a new recovery is reached. This behaviour is observed for many iterations of the stress sequence shown in Figure 1. Moreover, the phenomenon is qualitatively repetitive from sample to sample. This result indicates that after the first current limited BD is produced, two conductive states are present in the dielectric: a high conductivity one (BD state, with gate current  $I_{BD}$ ), and a low one (R state, with gate current  $I_{R}$ ). The conduction in both states is local and controlled by the same BD path [4]. Switching between both states takes place by applying the adequate gate voltages and only if the BD is produced under current limited conditions.

Figure 3:  $I_G$  obtained during the  $13^{th}$  cycle S-RVS of the sequence shown in Fig. 1. BD was provoked during the previous CL-RVS. Different recoveries (R and R') can be clearly observed.

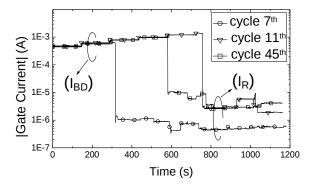

Other examples that illustrate different aspects of the  $I_G$  evolution during the S-RVS are represented in Figure 4 and Figure 5.  $I_G$  during the S-RVS corresponding to the  $7^{th}$ ,  $11^{th}$  and  $45^{th}$  cycles in the same sample are shown in Figure 4. As expected, when the oxide remains in the BD state, the current through the gate dielectric stack increases with the gate voltage, with a resistive-like behaviour. However, after the BD reversibility takes place (R state) the gate current seems to be independent of the gate voltage and shows fluctuations that

could be caused by electronic instabilities in the previously opened conductive path [11]. Since the voltage during the S-RVS increases continuously until the end of the stress (1200s), the appearance of new BD events after reaching the R state (Figure 5) is possible. In some cases, the new BD can be recovered again, as it is shown in Figure 5 (R<sub>2</sub>), which indicates that the path (or another path), has been 'opened' and 'closed' again. However, in other cases, the new BD event reaches higher currents than the ones corresponding to the BD state (because the S-RVS is not a current limited stress) and BD becomes irreversible, being impossible to observe the BD reversibility anymore [3].

Figure 4:  $I_G$  evolution during the  $7^{th}$ ,  $11^{th}$  and  $45^{th}$  S-RVS of the sequence in the same sample.

Figure 5: Example of  $I_G$  evolution during a S-RVS. New BD and recovery ( $R_2$ ) events can appear during the S-RVS after the first recovery (R).

# IV. CHARGE-TO-RECOVERY ANALYSIS

In order to characterize the BD reversibility, in analogy to the charge-to-BD as the parameter to characterize the BD events [1], we propose to use the charge-to-recovery, Q<sub>R</sub>, defined as the charge injected in the dielectric until the first

recovery event is observed in each of the S-RVS (R in Figure 3 and 5). In the next paragraphs, the dependence of  $Q_R$  on the polarity of the S-RVS and the current limit during the CL-RVS will be analysed.

# S-RVS polarity dependence of $Q_R$

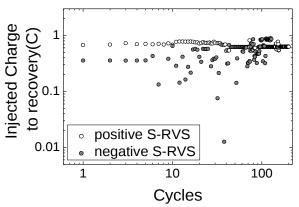

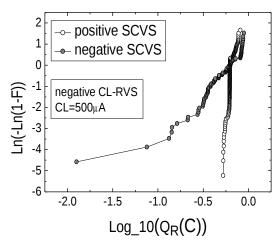

To analyse the dependence of  $Q_R$  on the S-RVS polarity BD was always produced by a negative CL-RVS whereas positive or negative S-RVS were applied to reverse BD. Figure 6 shows the Q<sub>R</sub> values obtained after successive cycles in two samples, one of them subjected to positive S-RVS (open symbols) and the other to negative S-RVS (solid symbols). In the case of positive S-RVS, the BD-recovery sequence was reproducible during more than 600 cycles. From our measurements, no dependence of  $Q_R$  on the number of stress cycles was inferred, independently of the polarity of the S-RVS. However, lower dispersion of Q<sub>R</sub> values is obtained when the polarity of the CL-RVS and the S-RVS are opposite. To show more clearly this result, the  $Q_R$ distributions of the data shown in Figure 6 were drawn in a Weibull plot (Figure 7). A larger dispersion of  $Q_R$  can be clearly observed for the samples subjected to negative voltage S-RVS (same polarity as the CL-RVS).

Figure 6:  $Q_R$  as a function of the number of cycles. BD state was reached applying a negative CL-RVS in all the cases. However, positive (open cycles) or negative (close circles) S-RVS were applied to induce BD recovery.

Figure 7: Weibull plot of the  $Q_R$  data shown in Figure 6. Samples were subjected to negative CL-RVS followed by positive (open symbols) or negative (solid symbols) S-RVS. Lower dispersion is observed when the polarities of the CL-RVS and S-RVS are opposite.

# Dependence of $Q_R$ on the CL-RVS current limit

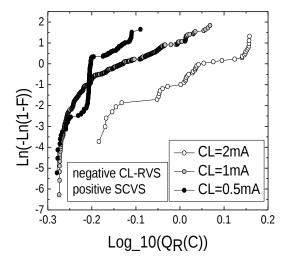

The dependence of  $Q_R$  on the current limit fixed during the CL-RVS has been analyzed. In this study, the samples were subjected to negative CL-RVS to provoke BD (changing the current limit from sample to sample) followed by a positive S-RVS to reverse BD. Figure 8 shows the  $Q_R$  distributions obtained in three different samples after successive cycles, whose BD was induced using different current limits. A clear increase of the average value of  $Q_R$  with the current limit can be observed.

Figure 8:  $Q_R$  distributions obtained in samples broken down during CL-RVS with three different current limits. The polarity of the CL-RVS and the S-RVS was negative and positive, respectively. Higher current limit means larger average  $Q_R$ .

Dependence of post-BD and post-recovery  $I_G$  on the CL-RVS current limit

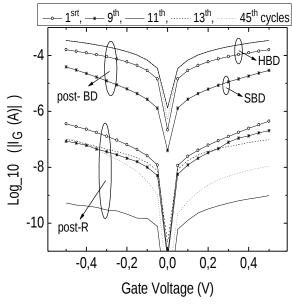

Figure 9 shows the  $I_G$ - $V_G$  characteristics after the dielectric BD (post-BD) and after the BD recovery (post-R in Figure 9) for several cycles of the stress-measurement sequence shown in Figure 1. Several orders of magnitude between the post-BD and the recovered (post-R) gate currents can be observed. On the other hand, for the post BD gate currents represented in Figure 9, two BD modes can be distinguished: SBD (in the  $9^{th}$  cycle) and HBD (rest of the cycles)

Figure 9: Typical  $I_G$ - $V_G$  characteristics registered after the dielectric BD (post-BD) and after the BD Recovery (post-R) for different cycles on the same sample. For the post BD currents, two BD modes are distinguished, SBD (in 9<sup>th</sup> cycle) and HBD (rest of the cycles).

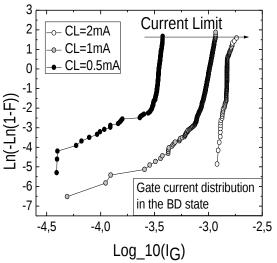

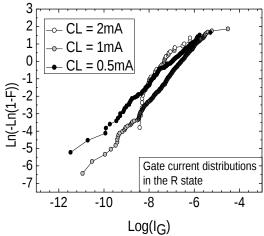

We have also investigated the dependence of the post-BD and recovered gate currents on the CL-RVS current limit, from the I<sub>G</sub>-V<sub>G</sub> characteristic registered after each CL-RVS (BD state) and S-RVS (R state). The post-BD and recovered gate currents were measured at  $V_G = -0.5V$  in the same samples where the Q<sub>R</sub> distributions in Figure 8 were obtained. Figure 10 and Figure 11 show the post-BD and recovered gate current distributions, respectively, for CL-RVS current limits of 0.5, 1 and 2 mA. At the BD state (Figure 10), the gate current clearly increases with the current limit established during the CL-RVS, as has been observed for Q<sub>R</sub> (Figure 8). Two regions can be clearly distinguished in Figure 10 for the distributions with the lower current limits of the CL-RVS: on one hand a region with a larger slope which corresponds to higher post-BD gate currents and on the other hand a second region with a lower slope which corresponds to lower post-BD gate currents. Note that these lower current levels correspond to the BD state. In previous papers about dielectric BD, when the dielectric soft BD (SBD) takes place, as in the 9th cycle of Fig.9, lower gate current is observed than for hard BD (HBD) [12]. For this reason, the current levels in the tails of the distribution shown in Figure 10 have been attributed to SBD events, whereas larger currents in the higher slope regions correspond to HBD. Note that we have used the terms SBD and HBD to refer to the different BD modes observed during the BD state. Therefore, from Figure 10, it can be deduced that the probability to get Hard BD events increases with the current limit used to provoke the BD, as expected. On the contrary, at the R state (Figure 11) no relevant dependences of the gate current with the current limit are inferred. In summary, the current limit used to switch the sample to the BD state will influence  $Q_{\rm R}$ , the BD mode and, consequently, the post-BD gate current, but it will not affect the current at the R state.

Figure 10: Post-BD  $I_{\rm G}$  distributions, obtained after each CL-RVS for three different current limits, in the same samples of Figure 8.

Figure 11: Recovered  $I_G$  distribution, obtained after each S-RVS, in the same samples of Figure 8 and Figure 10.

# V. CONCLUSIONS

A procedure to analyse the gate dielectric BD recovery in transistors with ultrathin high-k gate dielectric has been presented, which allows to switch between the two post-BD

conduction modes: BD and R states with the current during the BD state larger than during the R state. To switch to the BD state, current limited ramp voltage stresses (CL-RVS) are applied whereas to provoke the BD recovery the samples are subjected to a non-limited current S-RVS stress. The injected charge to the first recovery (Q<sub>R</sub>) during the S-RVS has been proposed as a parameter to describe the BD reversibility phenomenon. The methodology has been applied to study some details of the BD-recovery process from the dependences of Q<sub>R</sub> on the electrical test parameters. No dependence of  $Q_R$  with the number of iterations of the BD-recovery sequence has been observed. In addition, lower Q<sub>R</sub> dispersion is obtained when the polarities of the CL-RVS and the S-RVS are opposite. On the other hand,  $Q_R$  and the BD state current increase with the current limit fixed during the CL-RVS. At the BD state, SBD and HBD modes can be observed and the probability of HBD increases with the current limit. However, a negligible dependence of the current during the R state with the CL-RVS current limit has been measured. How all these properties of the BD-recovery process affect the overall reliability of the device should be the aim of further analyses.

### ACKNOWLEDGMENT

This work has been partially supported by the Spanish MICINN (TEC2007-61294/MIC) and the Generalitat de Catalunya (2009SGR-783).

### REFERENCES

- [1] E. Y. Wu, J. Suñe, "Power low voltage acceleration: A key element for ultra-thin gate oxide reliability," *Microelectronics Reliability*, vol. 45, pp. 1809-1834, 2005.

- [2] M. Nafria, J. Suñe, X. Aymerich, "Exploratory observations of post-breakdown conduction in polycrystalline-silicon and metal-gate thin-oxide metal-oxide-semiconductor capacitors," *Journal of Applied Physics*, vol. 73, pp. 205-215, 1993.

- [3] A. Crespo-Yepes, J. Martin-Martinez, R. Rodriguez, M. Nafria, X. Aymerich, "Reversible dielectric breakdown in ultrathin Hf based high-k stacks under current limited stresses," *Microelectronics Reliability*, vol. 49, pp. 1024-1028, 2009.

- [4] A. Crespo-Yepes, J. Martin-Martinez, R. Rodriguez, M. Nafria, X. Aymerich and A. Rostchild, "Resistive switching-like behaviour of the dielectric breakdown in ultra-thin Hf based gate stacks in MOSFETs", 40<sup>th</sup> European Solid-State Device Research Conference (ESSDERC 2010), pp. 138-141, 2010.

- [5] W. Guan, S. Long, Q. Liu, M. Liu, W. Wanmg, "Nonpolar non-volatile resistive switching in cu doped ZrO2", IEEE Electron Device Letters, vol. 29 (5), pp. 434-437, 2008.

- [6] R. Waser, M. Aono, "Nanoionics-based resistive switching memories," Nature Materials, vol. 6, pp. 833-840, 2007.

- [7] W. H. Liu, K. L. Pey, X. Li, M. Bosman, "Observations of switching behaviors in post-breakdown conduction in NiSi-gat stacks," *International Electron Devices Meeting*, pp. 1-4, 2009.

- [8] A. Crespo-Yepes, J. Martin-Martinez, A. Rothschild, R. Rodriguez, M. Nafria, X. Aymerich, "Recovery of the

- MOSFET and circuit functionality after the dielectric breakdown of ultra-thin high-k gate stacks," IEEE *Electron Device Letters*, vol. 31 (6), pp. 543-545, 2010.

- [9] N. Raghavan, K.L. Pey, W.H. Liu, X. Wu and X. Li. "Unipolar recovery of dielectric breakdown in fully silicided high-kappa gate stacks devices and its reliability implications" Applied Physics Letters, vol. 96, Article number 142901, 2010.

- [10] A. Martin, P. O'Sullivan and Alan Mathewson "Dielectric Reliability Measurement Methods: A Review". Microelectronics Reliability, vol. 38 (1) pp. 37-72; 1998.

- [11] R. Degraeve, Ph. Roussel, M. Cho, B. Kaczer, T. Kauerauf, F. Crupi, G. Groeseneken, "Explaining 'voltage-driven' breakdown statistics by accurately modeling leakage current increase in thin SiON and SiO<sub>2</sub>/high-k stacks", IEEE International Reliability Physics Symposium, IRPS 2006, pp. 82-89.

- [12] R. Degraeve, M. Aoulaiche, B. Kaczer, Ph. Roussel, T. Kauerauf, S. Sahhaf, G. Groeseneken, Review of reliability issues in high-k/Metal gate stacks, International Symposium on the Physical and Failure analysis of Integrated Circuits, 2008. IPFA 2008.