This is the accepted version of the article:

Russell S.A.O., Perez-Tomas A., McConville C.F., Fisher C.A., Hamilton D.P., Mawby P.A., Jennings M.R.. Heteroepitaxial Beta-Ga2O3 on 4H-SiC for an FET with Reduced Self Heating. IEEE Journal of the Electron Devices Society, (2017). 5. 7932063: 256 - . 10.1109/JEDS.2017.2706321.

Available at: https://dx.doi.org/10.1109/JEDS.2017.2706321

# Heteroepitaxial beta-Ga<sub>2</sub>O<sub>3</sub> on 4H-SiC for an FET with Reduced Self Heating

Stephen A. O. Russell, Amador Pérez-Tomás, Christopher F. McConville, Craig A. Fisher, Dean P. Hamilton, Philip A. Mawby, *Senior Member*, *IEEE*, and Michael R. Jennings, *Member*, *IEEE*

Abstract—A method to improve thermal management of  $\beta\text{-}Ga_2O_3$  FETs is demonstrated here via simulation of epitaxial growth on a 4H-SiC substrate. Using a recently published device as a model, the reduction achieved in self-heating allows the device to be driven at higher gate voltages and increases the overall performance. For the same operating parameters an 18% increase in peak drain current and 15% reduction in lattice temperature is observed. Device dimensions may be substantially reduced without detriment to performance and normally off operation may be achieved.

Index Terms—FET, Gallium Oxide, Molecular Beam Epitaxy, Normally-Off, Self-Heating, Silicon Carbide, Threshold Voltage

# I. INTRODUCTION

Wide band-gap semiconductor materials commonly thought of for use in power electronic devices include silicon carbide (SiC) [1-2], gallium nitride (GaN) [3] and diamond. SiC has shown the greatest potential to date in replacing silicon for DC power applications, indeed 4H-SiC diodes and MOSFETs are today commercially available. Diamond has been touted as the ideal material for high power electronics due to its large thermal conductivity, high breakdown field and high bulk carrier mobility. It has the potential to compete with both SiC for high voltage DC applications and GaN for RF power applications [4-6]. However despite recent advances, doping and substrate cost remains an issue [7-8].

In contrast, beta-Gallium Oxide  $(\beta\text{-Ga}_2O_3)$  could offer an alternative to 4H-SiC for power applications. Its key intrinsic material properties are competitive with diamond e.g. a bandgap of 4.8 eV and high breakdown field 8 MVcm<sup>-1</sup> [9-10]. Large scale growth is also far less challenging and possible at a fraction of the cost [11].

Despite the material structure being first investigated in the 1960s [12] it is only much more recently this material has been suggested for application in power electronic devices. Indeed, Ga<sub>2</sub>O<sub>3</sub> thin-films have been successfully employed for a variety of applications including a window layer for solar cells and a transparent conductive oxide [13-15]. This holds promise for a larger degree of integration compared with traditional wide

band-gap semiconductors e.g. into display screens or transparent electronics [16].

In recent years basic FET devices have been demonstrated [17-20], although p-type doping (which is notoriously difficult in wide band-gap semiconductors) is still a practical challenge. The best oxide solution is yet to be settled upon with work to date mainly focusing on Al<sub>2</sub>O<sub>3</sub>, although in theory SiO<sub>2</sub> provides a greater band off-set and hence reduced gate leakage [21-22].

In this paper a SILVACO Atlas non-isothermal model for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> demonstrated in a recent paper is employed to recreate a device demonstrated by Higashiwaki *et al* [23, 18]. The low thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (~0.2 Wcm<sup>-1</sup>K<sup>-1</sup>) [10] can be regarded as perhaps the most severe drawback for very high voltage applications. We demonstrate via simulation the advantages of engineering a thin film of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> onto a good thermal conductor such as SiC (~5 Wcm<sup>-1</sup>K<sup>-1</sup>) to increase the thermal performance of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.

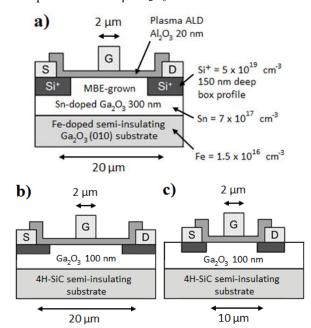

Fig. 1. Schematic showing the structure and doping of a) original MOSFET device based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [18] and b) & c) adaptations made in this paper

Manuscript received November 23, 2016. The authors gratefully acknowledge the financial support from the Advanced Propulsion Centre and the 'Preparing for the Grand Challenge' scheme. Project Number PGC007.

S. A. O. Russell, C. A. Fisher, D. P. Hamilton, P. A. Mawby and M. R. Jennings are with the University of Warwick, School of Engineering, Coventry, CV4 7AL, UK. (e-mail: S.Russell@warwick.ac.uk).

A. Pérez-Tomás is with Catalan Institute of Nanoscience and Nanotechnology (ICN2), CSIC and the Barcelona Institute of Science and Technology, Campus UAB, Bellaterra, 08193 Barcelona, Spain.

C. F. McConville is with RMIT University, College of Science, Engineering and Health, GPO Box 2476, Melbourne, Vic 3001, Australia.

# II. SIMULATION

Fig. 1 shows a cross-section of the FET modelled here. The semi-insulating β-Ga<sub>2</sub>O<sub>3</sub> substrate material is detailed in the original paper as having a doping of 1.5 x 10<sup>16</sup> cm<sup>-3</sup>, while the dopant in the Molecular Beam Epitaxy (MBE) layer is 7 x 10<sup>17</sup> cm<sup>-3</sup> with half considered activated. The Si ohmic dopant is 5 x  $10^{19}$  cm<sup>-3</sup> with 3 x  $10^{19}$  cm<sup>-3</sup> activated. A 20 nm Al<sub>2</sub>O<sub>3</sub> Atomic Layer Deposited (ALD) oxide layer covers the device with a source-drain spacing of 20 µm and gate length 2 µm. This device (Fig. 1a) suffers from self-heating effects due to the relatively poor thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub> which reduces the saturated drain current value. One way to mitigate this is to use a substrate with a high thermal conductivity such as 4H-SiC. A recent study has shown the positive impact this can have even on Si based devices [24]. The lattice match of β-Ga<sub>2</sub>O<sub>3</sub> to 4H-SiC is close at 3.04Å compared to 3.07Å respectively, allowing for low defect density materials to be grown and interfaces to be formed between β-Ga<sub>2</sub>O<sub>3</sub> and 4H-SiC by growth methods such as MBE used in this instance.

A simple constant thermal conductivity and low-field mobility model was used for this study with main parameters

TABLE I SIMULATION PARAMETERS

| DIMEDITION THE INDICE. |                                  |                                                |

|------------------------|----------------------------------|------------------------------------------------|

| Material               | Parameter                        | Value                                          |

| β-Ga2O3                | Bandgap Energy                   | 4.8 eV                                         |

| •                      | Thermal Conductivity             | 0.13 Wcm <sup>-1</sup> K <sup>-1</sup>         |

|                        | Effective Mass                   | $0.28 m_0$                                     |

|                        | Local Conduction Band Density of | $3.72 \times 10^{18}  \text{cm}^{-3}$          |

|                        | States                           |                                                |

|                        | Epitaxial Layer Mobility         | $118 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ |

|                        | Epitaxial Layer Dopant           | $7 \times 10^{17} \text{ cm}^{-3}$             |

|                        | Concentration                    | $(3.5 \times 10^{17} \text{ cm}^{-3})$         |

|                        |                                  | activated)                                     |

|                        | Substrate Mobility               | $20 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  |

|                        | Substrate Dopant Concentration   | $1.5 \times 10^{16}  \text{cm}^{-3}$           |

| 4H-SiC                 | Bandgap Energy                   | 3.23 eV                                        |

|                        | Thermal Conductivity             | 3.7 Wcm <sup>-1</sup> K <sup>-1</sup>          |

|                        | Effective Mass                   | $0.41 \ m_0$                                   |

|                        | Local Conduction Band Density of | 5 x 10 <sup>18</sup> cm <sup>-3</sup>          |

|                        | Stateas                          |                                                |

|                        | Substrate Mobility               | $460 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ |

|                        | Substrate Dopant Concentration   | $1.5 \times 10^{16}  \text{cm}^{-3}$           |

|                        |                                  |                                                |

$\beta\text{-}Ga2O3$  parameters taken from [12 & 25] whereas standard SILVACO parameters are used in the case of the 4H-SiC substrate

# summarised in Table 1.

As many  $\beta$ -Ga2O3 parameters are not fully established yet care is needed to not pick unrealistic values. Electron effective mass is taken to be 0.28 m<sub>o</sub> giving a calculated local conduction band density of states  $N_c = 3.72 \times 10^{18}$  cm<sup>-3</sup>, mobility of the channel layer and mobility of the semi-insulating substrate are set to be 118 and 20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> respectively [25].

A parameter (LAT.TEMP) was added to the model to account for poor heat flow in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material. The lattice temperature coefficient for the temperature dependence of electron mobility TMUN=2.0 was used as seen in Equation 1.

$$\mu_{n0} = MUN\left(\frac{T_L}{300}\right)^{-TMUN} \tag{1}$$

Where  $\mu_{n0}$  represents electron mobility adjusted for lattice temperature, MUN the originally input mobility value,  $T_L$  lattice temperature and TMUN the temperature dependence coefficient.

The material parameters of 4H-SiC are much better established and standard SILVACO parameters were used for this material.

# III. RESULTS & DISCUSSION

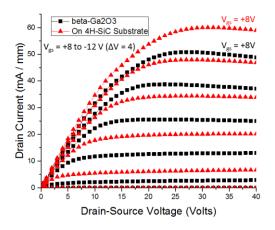

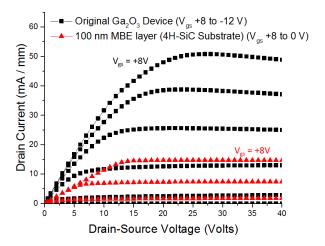

Fig. 2 demonstrates the immediate benefit of switching to a 4H-SiC substrate for this technology, output characteristics are displayed for the original device as well as the modelled version on a 4H-SiC substrate simulated to have the same doping level (1.5 x 1016 cm $^{-3}$ ) as the original  $\beta$ -Ga2O3 substrate. Peak drain current increases for all gate bias points, an increase of 19% is seen for  $V_{\rm gs}=+8V$  with peak lattice temperature reducing by 15% at this bias point, far extending the realm of operation of the original device.

Fig. 2. Comparison of the output characteristics from a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET and the same on a 4H-SiC substrate, both are simulated to have a 300 nm thick epitaxial layer

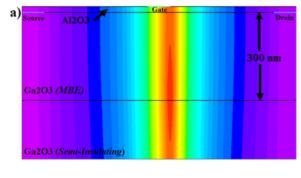

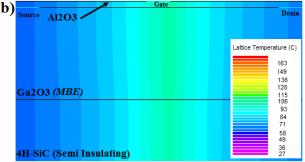

A visual comparison is shown in the form of a heat contour map for the original device and the 4H-SiC substrate version in Fig. 3. For the  $\beta\text{-}Ga_2O_3$  device at a  $V_{gs}$  of +8V and  $V_{ds}$  of +40V the lattice temperature reaches a peak of 166° C, for the same bias on a 4H-SiC substrate the peak lattice temperature reaches only  $98^{\circ}$  C.

Fig. 3. Lattice temperature at  $V_{gs} = 8V$  for  $\beta\text{-Ga}_2O_3$  (a) and 4H-SiC (b) substrate

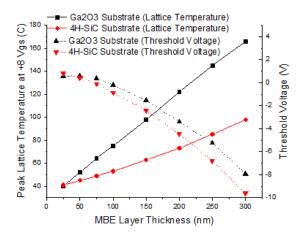

The 4H-SiC version remains normally-on although this can be shifted in both cases by a reduction in thickness of the epilayer. Fig. 4. Shows the shift in threshold voltage  $(V_T)$  for modelled devices as the simulated epitaxial layer thickness is reduced, there is also an associated reduction in temperature.

Fig. 4. Comparison of transfer characteristics for  $\beta\text{-}Ga_2O_3$  MOSFET and the same on a 4H-SiC substrate

Fig. 5 shows the output characteristic of a 100 nm epitaxial layer FET on 4H-SiC device compared to the original  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET. Self-heating is virtually eliminated at this gate voltage (V<sub>gs</sub>) of +8 V (lattice temperature = 53° C). Peak drain current is understandably reduced due to the more restricted and hence resistive route but the nature of this design and its improved thermal conductivity allows a much higher V<sub>gs</sub> to be used.

Fig. 5. Output characteristic for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate with 100 nm layer thickness.

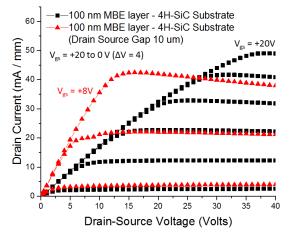

Fig. 6. Output characteristic for 4H-SiC substrate with 100 nm layer thickness, Vgs up to +20 (lattice temp max 71° C)

Fig. 6 shows how this device may be driven easily to  $V_{gs} = 20~V$ . A similar peak drain current to the original device is achieved although on-resistance of the device is increased. If however the source-drain gap is reduced to  $10~\mu m$  a similar output characteristic to the original device may be seen with a substantially reduced  $V_T$  and a lower lattice temperature (91° C at  $V_{GS} = +8~V$ ).

Analyzing current density for the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET at voltages close to  $V_T$  the current path is partially forced through the semi-insulating substrate, albeit at a much reduced level due to the lower mobility of this layer. Reducing the MBE layer thickness ensures this occurs at a more positive  $V_{gs}$  and impacts upon the threshold voltage. On the 4H-SiC substrate the heterojunction present means negligible charge will migrate in to this layer giving rise to the marginal difference in  $V_T$  between substrates. This is visualized in Fig. 7.

Fig. 7. Current route at Vgs = -8V for  $\beta\text{-}Ga_2O_3$  (a) and 4H-SiC (b) substrate

Below a thickness of 100 nm the device becomes normally-off (below 75 nm for the 4H-SiC substrate). As the MBE layer thickness approaches 100 nm the shift in  $V_{\rm T}$  plateaus and reducing beyond this point has little benefit and begins to severely limit current performance. With this reduced layer thickness less drain current is possible for the same gate voltage as the restricted route increases the resistance of the  $\beta\text{-Ga}_2O_3$  MBE layer.

A source-drain distance of 20 microns is relatively large even for a power FET and utilising the 4H-SiC substrate allows further device scaling to increase current performance. Halving this to 10 microns and biasing at +8  $V_{\rm gs}$  a similar current level to the original device is obtained, still with a lower peak lattice temperature of 91° C. This scaling will of course put further stress on the dielectric layer. Simulation shows a maximum electric field of 1.22  $MVcm^{-1}$  even at +20  $V_{\rm gs}$  on the gate dielectric for the 100 nm on 4H-SiC device with reduced source-drain dimension. This is well within the remit of either  $Al_2O_3$  or  $SiO_2$  as a gate dielectric.

This demonstration allows many further routes to be taken in terms of scaling, the suitable lattice match of these two materials make it the perfect complement. Improvements in processing of this technology will undoubtedly yield more improvements from this promising material. It is accepted that 4H-SiC substrates are expensive however recent technological innovations such as those offered by Siltectra GmbH mean substrates may be split and recycled many times over [26]. The ability to grow high quality large area substrates of  $\beta\text{-}Ga_2O_3$  also raises the possibility of wafer bonding to high thermal conductivity substrates.

# IV. CONCLUSION

The replacement of the semi-insulating β-Ga<sub>2</sub>O<sub>3</sub> substrate

with a 4H-SiC alternative in this device yields two improvements. Firstly the reduction in self-heating due to the order of magnitude thermal conductivity of 4H-SiC compared to  $\beta\text{-}Ga_2O_3$ . Secondly due to this it is possible to scale the device in reducing the MBE layer thickness and reducing the source-drain gap, giving overall the same current performance with a drastically reduced  $V_T$ .

Future work should focus on the best gate oxide for this technology. Characterization of interface traps will shed some light on this matter and the best route to practically scaling these FETs. Attention also needs to be payed to ohmic metallization stacks as even in 4H-SiC devices stability of these at elevated temperature can still be an issue [27].

# REFERENCES

- [1] J. Rabkowski, P. Dimosthenis and N. Hans-Peter, "Silicon carbide power transistors: a new era in power electronics is initiated," *IEEE Ind. Electr. Mag.*, vol. 6, no. 2, pp. 17-26, Jun. 2012, doi: 10.1109/MIE.2012.2193291

- [2] U. K. Mishra, L. Shen, T. E. Kazior, Y. F. Wu, "GaN-based RF power devices and amplifiers", *Proc. IEEE*, vol. 96, no. 2, pp. 287-305, Feb. 2008, doi:10.1109/JPROC.2007.911060

- [3] A. Fontserè, Amador Pérez-Tomás, M. Placidi, P. Fernández-Martínez, N. Baron, S. Chenot, Y. Cordier, J. C. Moreno, P. M. Gammon and M. R. Jennings, "Temperature dependence of Al/Ti-based ohmic contact to GaN devices: HEMT and MOSFET," *Micr. Eng.*, vol. 88, no. 10, pp. 3140-3144, Oct. 2011, doi: 10.1016/j.mee.2011.06.015

- [4] K. Hirama, H. Takayanagi, S. Yamauchi, Y. Jingu, H. Umezawa and H. Kawarada, "High-performance p-channel diamond MOSFETs with alumina gate insulator," in *IEDM Tech. Dig.*, 2007, pp. 873–876, doi: 10.1109/IEDM.2007.4419088

- [5] D. A. J. Moran, S. A. O. Russell, S. Sharabi and A. Tallaire, "High frequency hydrogen-terminated diamond field effect transistor technology," in 12th IEEE Conference on Nanotechnology, Birmingham, UK, 2012, pp. 1-5, doi: 10.1109/NANO.2012.6321925

- [6] S. Russell, S. Sharabi, A. Tallaire and D. A. J. Moran, "RF operation of hydrogen-terminated diamond field effect transistors: A comparative study," *IEEE Trans. Electr. Dev.*, vol. 62, no. 3, pp. 751-756, Mar. 2015, doi: 10.1109/TED.2015.2392798

- [7] F. Cappelluti, G. Ghione, S. A. O. Russell, D. A. J. Moran, C Verona and E Limiti, "Investigating the properties of interfacial layers in planar Schottky contacts on hydrogen-terminated diamond through direct current/small-signal characterization and radial line small-signal modelling," *Appl. Phys. Lett.*, vol. 106, no. 10, pp. 103504, Sep. 2015, doi: 10.1063/1.4915297

- [8] S. A. O. Russell, L. Cao, D. Qi, A. Tallaire, K. G. Crawford, A. T. S. Wee and D. A. J. Moran, "Surface transfer doping of diamond by MoO<sub>3</sub>: A combined spectroscopic and Hall measurement study," *Appl. Phys. Lett*, vol. 103, no. 20, pp. 202112, Nov. 2013, doi: 10.1063/1.4832455

- [9] H. H. Tippins, "Optical absorption and photoconductivity int the band edge of β-Ga<sub>2</sub>O<sub>3</sub>," *Phys. Rev.*, vol. 140, pp. A316-A319. Oct. 1965, doi: 10.1103/PhysRev.140.A316

- [10] M. D. Santia, N. Tandon and J. D. Albrecht, "Lattice thermal conductivity in β-Ga2O3 from first principles," *Appl. Phys. Lett.*, vol. 107, no. 4, pp. 041907, Jul. 2015, doi: 10.1063/1.4927742

- [11] Z. Galazka, R. Uecker, K. Irmscher, M. Albrecht, D. Klimm, M. Pietsch, M. Brützam, R. Bertram, S. Ganschow, and R. Fornari, "Czochralski growth and characterization of β-Ga2O3 single crystals," *Cryst. Res. Technol.*, vol. 45, pp. 1229-1236, Dec. 2010, doi: 10.1002/crat.201000341

- [12] S. Geller, "Crystal structure of β-Ga<sub>2</sub>O<sub>3</sub>," J. Chem. Phys., vol. 33, no. 3, pp. 676-684, Sep. 1960, doi: 10.1063/1.1731237

- [13] Y. S. Lee, D. Chua, R. E. Brandt, S. C. Siah, J. V. Li, J. P. Mailoa, S. W. Lee, R. G. Gordon and T. Buonassisi, "Atomic layer deposited gallium oxide buffer layer enables 1.2V open-circuit voltage in cuprous oxide solar cells," *Adv. Mat.*, vol. 26, no. 27, pp. 4704-4710, Jul. 2104, doi: 10.1002/adma.201401054

- [14] T. Minami, Y. Nishi and T. Miyata, "Heterojunction solar cell with 6% efficiency based on an N-type aluminium-gallium-oxide thin film and P-type sodium-doped Cu2O sheet," *Appl. Phys. Exp.*, 8, no. 2, pp. 022301, Jan. 2015, doi: 10.7567/APEX.8.022301

- [15] M. Orita, H. Ohta, M. Hirano and H. Hosono, "Deep-ultraviolet transparent conductive β-Ga<sub>2</sub>O<sub>3</sub> thin films," Appl. Physl Lett., vol. 77, no. 25, pp. 4166-4168, Dec. 2000, doi: 10.1063/1.1330559

- [16] X. Yu, T. J. Marks and A. Facchetti, "Metal oxides for optoelectronic applications," *Nat. Mater.*, vol. 15, no. 4, pp. 383-396, Mar. 2016, doi: 10.1038/nmat4599

- [17] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui and S. Yamakoshi, "Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates," *Appl. Phys. Lett.*, vol. 100, no. 1, pp. 013504, Jan. 2012, doi: 10.1063/1.3674287

- [18] M. Higashiwaki, K. Sasaki, T. Kamimura, M. H. Wong, D. Krishnamurthy, A. Kuramata, T. Masui and S. Yamakoshi, "Depletion-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs," in 71<sup>st</sup> Dev. Res. Conf., 2013, pp. 1-2, doi: 10.1109/DRC.2013.6633890

- [19] M. Higashiwaki, K. Sasaki, T. Kamimura, M. H. Wong, D. Krishnamurthy, A. Kuramata, T. Masui and S. Yamakoshi, "Depletion-mode  $Ga_2O_3$  metal-oxide.semiconductor field-effect transistors on  $\beta$   $Ga_2O_3$  (010) substrates and temperature dependence of their characteristics," *Appl. Phys. Lett.*, vol. 103, no. 12, pp. 123511, Sep. 2013, doi: 10.1063/1.4821858

- [20] M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi and M. Higashiwaki, "Field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of 750 V," *IEEE Electr. Dev. Lett.*, vol. 37, no. 2, pp. 212-215, Feb. 2016, doi: 10.1109/LED.2015.2512279

- [21] T. Kamimura, K. Sasaki, M. H. Wong, D. Krishnamurth, A. Kuramata, T. Masui, S. Yamakoshi and M. Higashiwaki, "Band alignment and electrical properties of Al<sub>2</sub>O<sub>3</sub>/β-Ga<sub>2</sub>O<sub>3</sub> heterojunctions," *Appl. Phys. Lett.* vol. 104, no. 19, pp. 192104, May. 2014, doi: 10.1063/1.4876920

- [22] K. Konishi, T. Kamimura, M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi and M. Higashiwaki, "Large conduction band offset at SiO2/β-Ga<sub>2</sub>O<sub>3</sub> heterojunction determined by X-ray photoelectron spectroscopy," *Phys. Status Solidi B*, vol. 253, no. 4 pp. 623-625, Feb. 2016, doi: 10.1002/pssb.201552519

- [23] ATLAS SILVACO "Atlas simulation of a wide bandgap Ga2O3 MOSFET," The Simulation Standard, vol. 23, no. 4, pp 7-9, Oct-Dec 2013

- [24] C. Chan, P. A. Mawby and P. M. Gammon, "Analysis of linear-doped Si/SiC power LDMOSFETs based on device simulation," *IEEE Trans. Electr. Dev.*, vol. 63, no. 6, pp. 2442-2448, Jun. 2016, doi: 10.1109/TED.2016.2550865

- [25] K. Irmscher, Z. Galazka, M. Pietsch, R. Uecher, and R. Fornari, "Electrical properties of β-Ga2O3 single crystals grown by the Czochralski method", J. Appl. Phys. vol. 110, pp. 063720 Sep 2011 doi: 10.1063/1.3642962

- [26] http://www.siltectra.com/

- [27] D. P. Hamilton, M. R. Jennings, A. Perez-Tomas, S. A. O. Russell, C. A. Fisher and P. A. Mawby, "High temperature electrical and thermal aging performance and application considerations for SiC power DMOSFETs," *IEEE Transactions on Power Electronics*, vol. 32. no. 10, pp. 7967-7979, Oct 2017, doi: 10.1109/TPEL.2016.2636743