This is the **accepted version** of the article:

Aguirre, Fernando Leonel; Rodríguez Fernández, Alberto; Pazos, Sebastián Matías; [et al.]. «Study on the Connection Between the Set Transient in RRAMs and the Progressive Breakdown of Thin Oxides». IEEE Transactions on Electron Devices, Vol. 66, Issue 8 (August 2019), p. 3349-3355. DOI 10.1109/TED.2019.2922555

This version is avaible at https://ddd.uab.cat/record/215344 under the terms of the  $\bigcirc^{\mbox{\tiny IN}}$  copyright license

Study on the connection between the set transient in RRAMs and the progressive breakdown of thin

# oxides

Fernando Leonel Aguirre, *Member, IEEE*, Alberto Rodriguez-Fernandez, Sebastián Matías Pazos, *Member, IEEE*, Jordi Suñé, *Fellow, IEEE*, Enrique Miranda, *Senior Member, IEEE*, Félix Palumbo, *Member, IEEE*

Abstract—In this paper, the transition rate (TR) from the high to the low resistance state of a HfO<sub>2</sub>-based Resistive Random Access Memory (RRAM) is investigated. TR is statistically characterized by applying constant voltage stresses in the range from 0.45V to 0.65V. It is found that TR follows a voltage dependence that closely resembles that exhibited by MIS/MIM structures when subjected to constant electrical stress but with remarkably different fitting parameters. This result suggests a common underlying mechanism in both evolutionary behaviors. Furthermore, the investigation provides additional evidence supporting the micro-structural changes in the oxide after the forming step as well as the role played by the atomic species during the SET event.

Index Terms—RRAM, Resistive-Switching, High-k, Progressive oxide breakdown

#### I. INTRODUCTION

Resistive-switching random access memory (RRAM) is attracting a considerable interest as a promising future technology for scalable memory [1] and neuromorphic computing systems [2]. RRAM relies on the formation and dissolution of a nanoscale conductive filament (CF) spanning an insulating layer, typically a binary transition-metal oxide such as NiO [3], TiO<sub>x</sub> [4], HfO<sub>x</sub> [5], TaO<sub>x</sub> [6], among others. The CF is initially generated by a forming operation, namely, a controlled dielectric breakdown (BD) of the insulating layer using an appropriate current compliance level [7]. A small gap in the localized CF, which is responsible for the low-resistance state (LRS) in the memory device, is then opened through a RESET operation causing the transition from the LRS to the high resistance state (HRS), and closed with a SET operation (HRS to LRS transition). SET/RESET operations can be achieved via electrical pulses of the same or opposite polarities (unipolar/bipolar switching modes, respectively). The RS mechanism has been widely studied in the last years [1]-[12], and many authors claim that SET/RESET processes are described through ion migration induced by the local electric field and

(Corresponding author: F. Palumbo)

F. L. Aguirre, S. M. Pazos and F. Palumbo are with the Unidad de Investigación y Desarrollo de las Ingenierías, Facultad Regional Buenos Aires, Universidad Tecnológica Nacional, Medrano 951 (C1179AAQ), Buenos Aires, Argentina, and with Consejo Nacional de Investigaciones Científicas y Técnicas, Godoy Cruz 2290 (C1425FQB), Buenos Aires, Argentina. (aguirref@ieee.org, spazos@frba.utn.edu.ar and felix.palumbo@conicet.gov.ar)

A. Rodriguez-Fernandez, J. Suñé and E. Miranda are with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, Cerdanyola del Vallès 08193, Spain. (alberto.rodriguez@uab.cat, jordi.sune@uab.cat and enrique.miranda@uab.cat)

the temperature increase associated with Joule heating [10]. Ion migration is modeled by diffusion and drift components, where both rely on hopping mechanisms. Ions move along an energy landscape of potential wells, which provide states for ion localization [11], [12].

On the other hand, the main physical mechanism behind the BD dynamics of ultra-thin dielectrics (Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, SiO<sub>2</sub>, Si<sub>2</sub>N<sub>4</sub>) used in CMOS technology was recently identified [13], [14]. Briefly, the energy transfer from the CF to its surroundings promotes the diffusion of the fastest atomic species, which gradually enlarges the CF connecting the electrodes of the stack causing a progressive increase in the leakage current. Remarkably, SET and BD events show the same statistical behavior [9], and similar micro structural changes in the dielectric [15]-[19]. Several authors [15]-[17] showed that the BD spot is characterized by the formation of a Sirich (for poly-Si/SiO<sub>x</sub>N<sub>v</sub>/Si stacks) or a metal-rich region (for metal gate/high-K/Si stacks) in the gate dielectric. In this regard, Privitera et al. [18] have shown the presence of metallic species in the oxide for the case of HfO<sub>2</sub>-based RRAM MIM devices after forming.

In particular, a huge amount of research has been carried out regarding the static I-V characteristics of the RRAMs. However, the time evolution of the switching phenomenon is not completely understood yet. In this context, it is clear that despite the recent advances regarding the modelling of the current-voltage behaviour of the RS devices [9], [20], more information about the SET event in RRAM devices is needed. A detailed knowledge of the evolution of the CF morphology during forming and SET transitions as well as the corresponding shape of the I-V curves are needed for accurately model the switching phenomena and to make reliability predictions. Ultimately, the study of the voltage-time dependence of RS is needed to estimate the minimum time required for writing a bit in a RRAM cell [21]. In this paper, the HRS to LRS transition is studied as a function of time and switching voltage using a large number of measurements. Based on a physical description of the BD dynamics in dielectrics of common use in CMOS processes and the aforementioned similarities to the SET event in RRAM, a model for the time evolution of the resistive state of the RRAM as a function of the switching voltage is proposed.

1

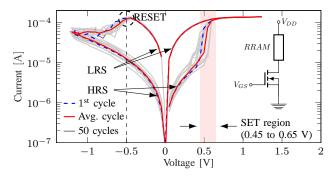

Fig. 1. I-V characteristics for the samples under test (50 curves). The red solid line is the average curve and the blue dashed one stands for the 1<sup>st</sup> cycle. The inset in the right side shows the 1T1R assembly, comprising the RRAM structure and its driving N-MOS transistor.

# II. EXPERIMENTAL

Experimental data were obtained from HfO2-based RRAM cells. The MIM structure consists in a 10 nm thick atomic layer-deposited HfO<sub>2</sub> film sandwiched between Ti and TiN electrodes. The cell is connected in series with an n-type MOSFET, embedding a 1 Transistor - 1 Resistor (1T1R) structure, as shown in the inset of Fig. 1. The transistor controls the maximum current that can flow through the memory cell which in turn determines the resistance window of the device [7], [22]. All the measurements where performed by applying a gate-source voltage  $(V_{GS})$  of 1.2V. Quasi-static I-V-t measurements were performed using a Keithley 4200-SCS equipped with a Fast Measurement and Pulse Generator Unit (4225-RPM) capable of providing an appropriate time resolution (down to 200 ns in Fig. 2b). As reported in a previous work considering similar samples [20], the forming event takes place at  $\approx 3.8V$  and the devices exhibit bipolar switching characteristics. Notice that the average SET and RESET voltages are almost symmetric ( $\approx \pm 0.5$ V). This indicates voltage controlled processes for HfO2 in agreement with previously reported results [23]. Further details about the devices and experimental setup can be found in Ref. [9].

# III. RESULTS

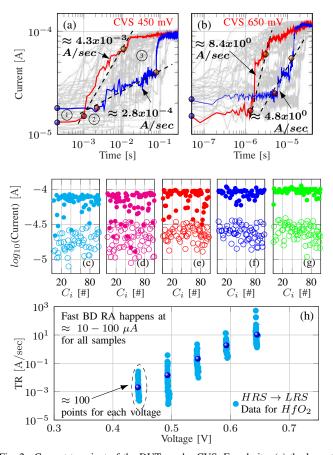

In order to study the SET event, the whole process including the wear-out phase and the transition from HRS to LRS must be explored. Therefore, current-time (I-t) measurements at constant bias were performed using the high-bandwidth setup mentioned in Sec. II until the fast HRS to LRS transition occurred or in other words, until the current through the device reaches the compliance limit ( $\sim 100~\mu A$ ). I-t measurements were performed under Constant Voltages Stress (CVS) of 450 mV, 500 mV, 550 mV, 600 mV and 650 mV. For clarity, only the transients corresponding to the 450 mV and 650 mV stresses are shown in Figs. 2a and 2b. Such stress voltages were applied in the HRS state and were chosen after the I-V curves depicted in Fig. 1, where the HRS to LRS transition occurs for voltages ranging from 0.45 to 0.65 V.

Current through the MIM stack during the HRS to LRS transition  $(I_{Tr})$  increases gradually with time [24], evidencing the progressive nature of the SET event (see Figs. 2a and 2b). It is a noisy and progressive process well in agreement

with the literature [7], [9], [10], [25] whose duration shows a strong voltage dependence and dispersion. Such dispersion will be discussed in Sec. IV-A. The maximal current growth rate is limited by the bandwidth of the equipment. Figures 2c to 2g show the initial ( $I_{init}$ , empty symbols) and end ( $I_{end}$ , filled symbols) currents of the acquired transients, including those shown in Fig. 2a and 2b. It is worth mentioning that the initial current matches the I-V data shown in Fig. 1, where the SET region shows initial currents around 10  $\mu$ A.  $I_{end}$ current represents the level from which the acquired transient exhibits a jump to the compliance level (see Fig. 2), leaving the sample in LRS. The time evolution of the HRS to LRS transition is quantified by the slope  $dI_{Tr}/dt$ , as defined in Ref. [13], [26], [27]. Such metric will be subsequently referred to as Transition Rate (TR) [A/s]. TR values were experimentally evaluated through measurements such as those of Fig. 2a and 2b and it is reported for approx. 100 measurements for each voltage value (see Fig. 2h). The comparison between the TR in Figs. 2a and 2b and the trend in Fig. 2h suggest a strong voltage dependence, as the TR increases almost four orders of

Fig. 2. Current transient of the DUTs under CVS. For clarity, (a) the lowest -450 mV- and (b) highest -650 mV- voltages are shown. Ball markers 1,2 and 3 point out the initial current ( $I_{init}$ ), the onset of the progressive increase of current ( $I_{on}$ ) and the final jump to the compliance level ( $I_{end}$ ), respectively. Initial currents (empty markers) and end currents ( $I_{end}$ ) (filled markers) at (c) 450 mV, (d) 500 mV, (e) 550 mV, (f) 600 mV and (g) 650 mV.  $C_i$  in figs (c) to (g) stands for the cycle number. (h) Transition Rate (TR,  $dI_{Tr}/dt$ ) of the samples under test. Approx. 100 transients and the mean value are reported for each voltage condition (450, 500, 550, 600 and 650 mV). The mean value increases roughly 1 order of magnitude every 50 mV.

magnitude in between these two cases. Similar measurements of the HRS-LRS transition have been previously reported [25], showing a comparable voltage dependence (TR increases as the applied voltage increases).

### IV. ANALYSIS AND DISCUSSION

It has been experimentally shown that both the SET and forming event in RRAM devices [9], [25] and the dielectric BD of gate oxides [13], [14] share some common aspects. Aside from the noisy and progressive increase of the leakage current, whose increase rate depends on the stressing voltage, further insight into these events reveals a few other common points. Previously reported current compliance studies have shown a clear dependence of the CF characteristics on the maximal current flowing through the device, both for the BD of gate oxides [7] and the SET event in RRAM devices [22]. In addition, TEM imaging of Si-based MOS capacitors prior to and post dielectric BD [15]–[17] and HfO<sub>2</sub>-based RRAM cells after forming and cycling [18], [19] show comparable microstructural changes in the oxide, suggesting the diffusion of the anodic atomic species into the oxide layer during both events.

Thus, there are not only similar electrical characteristics between the SET event and the gate oxide BD, but also comparable micro-structural changes and the combination of both points towards a common underlying physical mechanism. In such scenario, we propose to model the results for the SET event in RRAM devices similarly to the gate-oxide BD in MOSFETs. In this regard, Palumbo et al. have presented in Ref. [13] a model describing the gate oxide BD phenomenon in ultra-thin, bulk dielectrics considering SiO<sub>2</sub> and various high-k dielectrics with different thermal conductivities deposited on III-V and Si substrates as well as in 2D layered materials [28], providing good understanding of the experimental data. Such model accounts for the progressive nature of the BD event and quantifies it in terms of  $dI_{BD}/dt$  (namely the Degradation Rate, DR), where  $I_{BD}$  is the current through the device during the Progressive Breakdown (PBD). Regarding the physics behind this evolution, the model assumes that the BD process is closely linked to the energy transfer from the CF itself to its surrounding atomic network. According to this idea, the high temperature associated with the localized current flow (current density of a few MA/cm<sup>2</sup> through a BD spot area of 1-50 nm<sup>2</sup> [13], [15], [16]) would promote the electromigration of the fastest available atomic species, thus contributing to the enlargement of the BD filament connecting the electrodes of the stack. Such electro-migration phenomena have been shown to exist in RRAM by Tang et al. [29]. This interpretation of the BD phenomena accounts for the dependence of the CF features on the current compliance and the presence of the anodic species in the oxide layer after BD, and therefore, it could be used to model the SET event in RRAMs.

It is worth pointing out that TR shows an evident voltage dependence (four orders of magnitude in 200 mV) much stronger than the DR reported for the BD event ( $dI_{BD}/dt$ , 3-5 orders of magnitude per volt) [13]. To understand such a big difference, a detailed explanation of the proposed model will

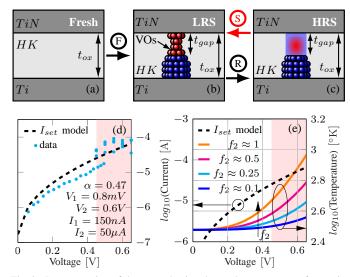

Fig. 3. Representation of the  $t_{ox}$  reduction due to the appearance of a gap in the CF: (a) Before forming step, (b) LRS and (c) HRS. Blue balls represent the electrode's atomic species, and red balls stands for the oxygen vacancies (VOs). (d)  $I_{SET}$  model described by Eq. 2 vs. measurements. (e) Temperature calculations as function of voltage and the energy loss in the CF constriction. In both (d) and (e) plots the red shaded zone indicates the voltages employed for the CVS (0.45 to 0.65 V)

be given in the following sections, as well as an explanation about the parameters' change from the gate oxide BD to the SET event case.

# A. Model of the Transition Rate (TR) for HRS to LRS as function of voltage

Based on the experimental results and the common underlying physical mechanism that seems to governs both SET and oxide BD, a diffusion phenomenon driven by the energy transfer from the CF to its surroundings is proposed, including the voltage and oxide thickness dependence. In this context, and considering the model reported in Ref. [13] for the BD transient, it is possible to express the TR for the HRS to LRS as in Eq. 1

$$TR = \frac{dI_{Tr}}{dt} = \frac{qVf_1}{k_B T t_{or}^2} DI_{SET}$$

(1)

where  $t_{ox}$  is the oxide thickness, T is the temperature at the gap in the CF (see Fig. 3c),  $k_B$  is the Boltzmann constant, D is the diffusion constant of the atomic species responsible for the HRS to LRS transition, V is the applied voltage,  $I_{SET}$  is the current level at the onset of the HRS to LRS transition (SET event) as expressed in Eq. 2 and  $f_1 = n_e \lambda_e \sigma_e$ , with being  $n_e$  the electron density,  $\lambda_e$  the electron mean free path and  $\sigma_e$  the cross-section for the electron-atom collision (responsible for the momentum transfer).  $f_1$  is around the unity value since the defect concentration in the CF is most likely very high [18].

From Eq. 1,  $dI_{Tr}/dt$  is proportional to  $D \times I_{SET}$ . This means that the CF growth rate increases either by increasing  $I_{SET}$ , the electron current, or the dominant diffusivity D. There is also a dependence on  $t_{ox}$ , V and T. So, to use Eq. 1 we need to model  $I_{SET}$  and D. Additionally, the effective value of  $t_{ox}$  as well as the atomic species involved in the HRS

to LRS transition will be further discussed in Sections IV-B and IV-C, respectively.

SET processes were shown to be controlled by the device I-V characteristics, which dictates the local temperature [13], [22] and drives the completion and rupture of a nano-scale CF through the insulating layer [10] (see Figs. 3b and 3c). This accounts for the compliance current used to control the resistance in the SET state [10].  $I_{SET}$  can be described by modeling the discontinuous CF (see Fig. 3c) as a quantum size filament with a constriction, according to the Landauer-Buttiker formalism [8] as we have previously reported [7]. However, for simplicity we have preferred to model the  $I_{SET}-V$  characteristic of the CF in HRS by assuming an interpolation equation (Eq. 2) [13], [28]. This avoids the use of more parameters. The fitting of our experimental data is shown in Fig. 3d.  $I_1,V_1$  and  $I_2,V_2$  represents two points in the experimental  $I_{SET} - V$  curve (see HRS curves in Fig. 1) at low and high voltages, respectively, while  $\alpha$  is a fitting constant.

$$I_{SET} = I_1 exp \left( log \left( \frac{I_2}{I_1} \right) \left( \frac{V - V_1}{V_2 - V_1} \right)^{\alpha} \right)$$

(2)

To model D we need first to model the temperature T in the constriction/discontinuity of the CF. To do so the heat diffusion equation was solved. We assumed a simplification of spherical symmetry around the CF constriction and considered the source power density to be constant over the inner surface of the sphere. The result is Eq. 3, where  $f_2$  is the fraction of the energy qV per electron lost at the constriction, the dissipated power at the CF constriction is proportional to  $I_{SET} \times V$ ,  $T_{amb}$  the room temperature and k is the thermal conductivity of the dielectric.

$$T = \frac{f_2 V I_{SET}}{2\pi t_{ox} k} + T_{amb} \tag{3}$$

The assumption of power dissipation taking place inside the dielectric layer is reasonable. It has been shown by Takagi *et al.* [30] for the case of gate oxide BD in MOSFETs that electrons tunneling through defects responsible for stress induced leakage current (SILC) in thin oxynitrides do lose a large fraction of their energy in the oxide, which suggests an inelastic process. This behavior has been explained to be a consequence of defect relaxation [31] and was recently confirmed by Lombardo *et al.* [32] for ultra-thin MOS devices.

$f_2$  represents the fraction of energy qV lost by the carriers injected into the dielectric, which ranges from 0 to 1. While at a large applied voltage,  $f_2$  tends to 1 in agreement with the electron's high energy loss, for low voltages  $f_2$  decreases, tending to zero for V=0.  $f_2$  also depends on the temperature, mainly because of phonon-electron scattering [32]. Therefore,  $f_2$  is a function of voltage and temperature whose behavior is found by a best fit procedure. The influence of  $f_2$  on the temperature is shown in Fig. 3e for different  $f_2$  values.

Once T at the CF constriction is estimated, then the diffusivity D can be modeled by the exponential law given by Eq. 4 where  $D_0$  is a pre-exponential term and  $E_{act}$  is the diffusion activation energy. It is worth noting that as shown by Lombardo *et al.* [32] substituting Eq. 4 and 3 into 1, an exponential dependence of TR on  $f_2$  shows off. This may be

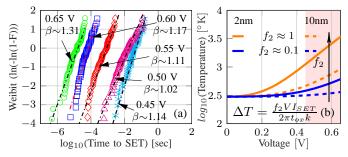

Fig. 4. (a)  $t_s$  distributions for CVS experiments for  $\sim$ 100 transitions for each voltage. Symbols are experimental data. Dash-dotted lines are Weibull fitting results. (b) Temperature in the CF constriction versus the stressing voltage, the resulting  $t_{ox}$  and the energy loss; the red shaded zone indicates the stressing voltage range (0.45-0.65 V).

helpful to explain the remarkable dispersion shown in Figs 2a and 2b. If for example  $f_2$  has a 20% dispersion, then TR may present a standard deviation of up to 2 orders of magnitude.

$$D = D_0 e^{\frac{-E_{act}}{k_B T}} \tag{4}$$

# B. Effect of the $t_{ox}$ reduction after the forming step

To implement this model for the SET event, the thickness of the dielectric needs to be considered in detail. In a first step, the CF is created through the fresh insulating layer (HfO<sub>2</sub> in Fig. 3a) by a forming operation (a controlled dielectric BD, Fig. 3b). Then, the switching mechanism relies on the creation of a gap (RESET) and the restoration of the CF (SET). The width  $(t_{gap})$  of such gap is independent of the oxide layer thickness  $(t_{ox})$  (see Fig. 3c) but dependent on the current compliance used during the SET event [11], [12], [15].

In a dielectric layer, BD is attributed to the formation of a percolative path between anode and cathode due to the generation of defects of size of  $\sim 1$  nm [15], and it is statistically described using the Weibull distribution, an extremevalue distribution appropriate for a weakest-link problem such as dielectric BD. Being the probability of forming such a path throughout the oxide bulk dependent of the oxide thickness [34], it is possible to use the statistics of the SET switching time  $(t_s)$  (i.e. the time to complete the HRS to LRS transition) under constant bias to estimate the effective thickness of the oxide layer after the forming event  $(t_{qap})$ . Figure 4a shows the Weibull plots for  $t_s$ , where the slope (marked as  $\beta$ , and constant through out all the voltages considered) is  $\sim$ 1.2. This suggests a HfO<sub>2</sub> film of ~2 nm from its comparison with literature [34], [35]. From the model viewpoint, this can be regarded in Eq. 1 as a reduction in the physical thickness  $t_{ox}$ , as illustrated in Figs. 3a and 3c. From Eq. 3, it is clear that such  $t_{ox}$  reduction causes a significant increase in the temperature at the CF constriction, as shown in Fig. 4b by the dashed and solid lines for the case of  $t_{ox} \approx 10$  nm (fresh device) and  $t_{ox} \approx t_{qap} \approx 2$  nm. It is worth mentioning that the local reduction of the thickness caused by the creation of a metal rich region in the oxide has been observed using cross section HRTEM [17], [18], [36].

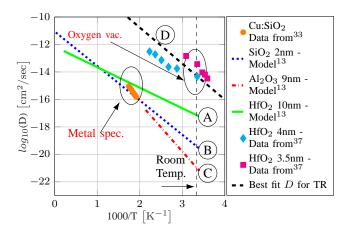

Fig. 5. Diffusivity of the dominant atomic species in the CF vs. reciprocal of temperature. VOs diffusivity [37] is  $\sim 10^4$  times higher than for the metallic species [13].  $E_{act}$  ranges from 0.3 to 0.7 eV. The diffusivity D required for fitting the TR results is shown to be in the same range as the VOs diffusivity.

# C. Increase in the diffusivity of the species involved

In the model proposed by Palumbo *et al.* in Ref. [13] the creation and growth of the CF connecting anode and cathode (Progressive BD) are due to the diffusion of the anode/cathode atomic species into the gate dielectric, creating a metallic filamentary path. This has been shown [13] by fitting the DR observed in both  $SiO_2$ - and High-K stacks with Eq. 1 and evaluating the required diffusivity D as function of temperature with Eq. 4 as presented in Fig. 5 (see curves A, B and C). Although quite large (of the order of  $10^{-13}$  cm<sup>2</sup>/sec at 1000 °K, with low activation energies ranging from 0.7 to 0.3 eV), such values are in a range compatible with the diffusivity of metals in dielectrics for conditions similar to those adopted here (e.g. the case of Cu diffusion into  $SiO_2$  layers [33]).

In the same way, the diffusivity required to fit the TR vs. voltage data has been calculated with Eq. 1-4 assuming the same values for the fitting parameters [13] ( $E_{act}$  ranging from 0.3 to 0.7 eV,  $f_2 \sim 0.1$  and  $f_1 \sim 1$ ) and is also plotted against the temperature in Fig. 5 (Curve D). The obtained value for D is quite larger ( $\sim 10^{-6}$  cm²/sec at 1000 °K) than the fitted diffusivities for the case of gate oxide BD. It should be mentioned that even in an unlikely scenario in which 100% of the electron's energy is lost at the BD spot (i.e.:  $f_2 = 1$ ), the required diffusivity to fit the TR data is significantly higher than the diffusivity obtained from fitting the progressive BD of gate oxides (for clarity, such fitting results are not shown).

At this point it is worth recalling that the transition from HRS to LRS has been explained as the vanishing of the gap in the filamentary path. During the forming operation, the CF is jointly created by the migration of the conductive species from the electrodes (blue balls) into the dielectric and the dissociation of oxygen ions (O<sup>2-</sup>), which drift to the top electrode generating positively charged oxygen vacancies (red balls) in the oxide layer and a reservoir of O<sup>2-</sup> ions in the Top Electrode (TE) (see Figs. 3a and 3b) [12], [38]. Then, the RESET process opens a gap in the CF due to the recombination of the oxygen vacancies in the CF with the O<sup>2-</sup> ions that diffuses back from the TE into the oxide (Fig. 3c).

The sample is then in HRS, with a ruptured CF that consists mainly of the anodic atomic species (blue balls) that diffused during the forming. Under such scheme, the SET event is explained as the completion of the gap due to the migration of  ${\rm O}^{2-}$  ions towards the TE through a field-assisted and thermally-activated effect, which creates the oxygen vacancies that fill the gap within the CF (see Fig. 3b) [20], [38], [39]. This is quite a relevant point to notice, as the diffusivity of oxygen vacancies (VOs), or equivalently the  ${\rm O}^{2-}$  ions, in a HfO<sub>2</sub> layer of thickness similar to  $t_{gap}$  spread over a range similar to the fitted diffusivity for the TR [37] (see curve D in Fig. 5). Therefore it might, altogether with the mentioned "reduction" of  $t_{ox}$ , explain the higher TR for these samples.

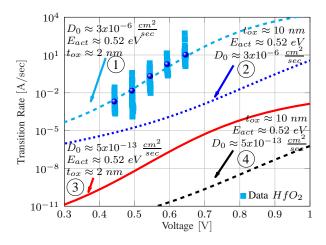

## D. Fitting results

The fitting results for TR as function of the applied voltage obtained with the proposed model in Eqns. 1-4 are illustrated in Fig. 6 (see curve n°1). These results have been superimposed to the scatter plot of the experimental TR data (see the square symbols), showing good agreement with the mean value for each voltage (indicated by the ball markers). The proposed fit accounts for both the  $t_{ox}$  reduction ( $t_{ox}$  considered is equal to  $t_{gap} \sim 2$  nm) and the increase in diffusivity ( $D_0$  is in the order of  $\sim 10^{-6}$  cm²/sec as other species are considered to complete the CF, i.e. oxygen vacancies). The rest of the parameters involved remain as previously mentioned ( $E_{act} \sim 0.3$ -0.7 eV,  $f_2 \sim 0.1$  and  $f_1 \sim 1$ ).

In order to make clear the impact of both the  $t_{ox}$  reduction and the diffusivity increase  $(D_0)$ , alternative fitting values are used to plot curves n°2, n°3 and n°4. Curve n°2 shows TR as function of voltage assuming fixed  $t_{ox}$  to the nominal oxide thickness  $(t_{ox} \sim 10 \text{ nm})$  but an increase in the atomic species diffusivity  $(D_0 \sim 10^{-6} \text{ cm}^2/\text{sec})$ . Curve n°3 presents the resulting curve when only the  $t_{ox}$  reduction is considered (i.e.  $t_{ox} \sim t_{gap} \sim 2 \text{ nm}$  and  $D_0$  corresponding to the metal

Fig. 6. TR data (square markers -ball markers stands for the mean value-) fitted assuming oxygen vacancies and  $t_{gap}=t_{ox}$  (cyan dashed line -curve  ${\rm n}^{\circ}1$ -). Additionally, TR assuming the values reported in the literature for  $t_{ox}$  and D is plotted -curves  ${\rm n}^{\circ}2$ , 3 and 4-. TR increases almost one order of magnitude for every 50 mV step, with a mean value of  $2{\rm x}10^{-3}$  A/sec,  $1.4{\rm x}10^{-2}$  A/sec,  $2.1{\rm x}10^{-1}$  A/sec,  $1.8{\rm x}10^{0}$  A/sec and  $1{\rm x}10^{1}$  A/sec for 450 mV, 500 mV, 550 mV, 600 mV and 650 mV, respectively

diffusion in oxides  $\sim 10^{-13}~\rm cm^2/sec)$ . Finally, curve n°4 presents TR as function of the applied voltage considering the same parameter values as in the gate oxide BD transients, i.e. diffusivity of metals in oxide layers ( $D_0 \sim 10^{-13}~\rm cm^2/sec)$  and no  $t_{ox}$  reduction ( $t_{ox} \approx 10~\rm nm$ ). This coincides with the DR for gate oxide BD.

The comparison of curves  $n^{\circ}1$  and  $n^{\circ}4$  evidences that TR is significantly higher than the DR expected for the voltage range considered. It is also worth noticing that TR calculated considering only a  $t_{ox}$  reduction or an increase in diffusivity  $(D_0)$  cannot meet the experimental data (see curve  $n^{\circ}1$  vs. curve  $n^{\circ}3$  and curve  $n^{\circ}1$  vs. curve  $n^{\circ}2$ , respectively). This suggests that TR as function of voltage is jointly determined by a combination of both effects, as none of them can fit the results independently.

#### V. SUMMARY

In this work, we showed that the High-Resistance-State (HRS) to Low-Resistance-State (LRS) transition (SET) in HfO<sub>2</sub>-based MIM stacks acting as Resistive Random Access Memories (RRAM) is a progressive phenomenon whose voltage dependence can be modeled in a similar fashion to the progressive breakdown (PBD) of thin oxides [13] by taking into account a proper adjustment of parameters. In this regard, the time required for the SET transition is studied as function of the switching voltage considering Constant Voltage Stress (CVS). As well as in the case of PBD, we propose that HRS to LRS transition is due to the energy transfer from a conductive filament (CF) to its surroundings which promotes the electromigration of the fastest available atomic species, enlarging the CF. Although the magnitude and voltage acceleration of degradation Rate (DR) during PBD (forming process) and Transition Rate (TR) during the SET event are different, in the framework of the model proposed in this work such differences are explained as a consequence of an increase in the diffusivity and a reduction of the effective oxide thickness. Diffusivity increases as the HRS to LRS transition (caused by the completion of the CF) is due to the migration of oxygen vacancies (VOs), whose diffusion coefficient is higher than that from electrode's atoms that diffuses during PBD. Secondly, the reduction in the effective  $t_{ox}$  should be considered as the SET event takes place in a previously degraded oxide layer and this increases the speed of the transition. The model presented here accounts for such effects and is in agreement with previous results reported [18], [20], [38], which presented experimental evidence of both the  $t_{ox}$  reduction and the influence of the VOs.

Finally it is worth mentioning that, by relating the Transition Rate with the temperature and thermal conductivity of the dielectric considered, TR could be potentially sped up by increasing the temperature at the CF, whether by increasing the SET voltage or by using a material with lower thermal conductivity [40]. As the reduction in the supply voltage is common in current CMOS processes, the second option could eventually lead to shorter writing times for the RRAM devices, which have been proposed as future non-volatile memories.

#### VI. ACKNOWLEDGEMENTS

This work has been funded by both Argentinean and European institutions. Argentine funding provided by MINCyT (Contracts PICT2013/1210, PICT2016/0579 and PME2015-0196), CONICET (Project PIP-11220130100077CO) and UTN.BA (Projects PID-UTN EIUTIBA4395TC3, CCUTIBA4764TC, MATUNBA4936 and CCUTNBA5182). On the other hand, the participation of E.M. and J. S. in this work has been developed within the WAKeMeUP 783176 project, co-funded by grants from the Spanish Ministerio de Ciencia, Innovación y Universidades and the ECSEL EU Joint Undertaking. E.M. acknowledges C. Cagli for data provision and discussion.

## REFERENCES

- R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-Based Resistive Switching Memories Nanoionic Mechanisms, Prospects, and Challenges," *Advanced Materials*, vol. 21, no. 25-26, pp. 2632–2663, jul 2009, doi: 10.1002/adma.200900375.

- [2] Y. Shi, X. Liang, B. Yuan, V. Chen, H. Li, F. Hui, Z. Yu, F. Yuan, E. Pop, H.-S. P. Wong, and M. Lanza, "Electronic synapses made of layered two-dimensional materials," *Nature Electronics*, vol. 1, no. 8, pp. 458–465, aug 2018, doi: 10.1038/s41928-018-0118-9.

- [3] D. Ielmini, R. Bruchhaus, and R. Waser, "Thermochemical resistive switching: materials, mechanisms, and scaling projections," *Phase Transitions*, vol. 84, no. 7, pp. 570–602, jul 2011, doi: 10.1080/01411594.2011.561478.

- [4] J. Park, S. Jung, J. Lee, W. Lee, S. Kim, J. Shin, and H. Hwang, "Resistive switching characteristics of ultra-thin TiO<sub>x</sub>," *Microelectronic Engineering*, vol. 88, no. 7, pp. 1136–1139, jul 2011, doi: 10.1016/J.MEE.2011.03.050.

- [5] G. Bersuker, D. C. Gilmer, D. Veksler, P. Kirsch, L. Vandelli, A. Padovani, L. Larcher, K. McKenna, A. Shluger, V. Iglesias, M. Porti, and M. Nafría, "Metal oxide resistive memory switching mechanism based on conductive filament properties," *Journal of Applied Physics*, vol. 110, no. 12, p. 124518, dec 2011, doi: 10.1063/1.3671565.

- [6] L. Zhang, R. Huang, M. Zhu, S. Qin, Y. Kuang, D. Gao, C. Shi, and Y. Wang, "Unipolar TaO-Based Resistive Change Memory Realized With Electrode Engineering," *IEEE Electron Device Letters*, vol. 31, no. 9, pp. 966–968, sep 2010, doi: 10.1109/LED.2010.2052091.

- [7] F. Palumbo, E. Miranda, G. Ghibaudo, and V. Jousseaume, "Formation and Characterization of Filamentary Current Paths in HfO<sub>2</sub>-Based Resistive Switching Structures," *Ieee Electron Device Letters*, vol. 33, no. 7, pp. 1057–1059, 2012, doi: 10.1109/led.2012.2194689.

- [8] E. Miranda and J. Suñé, "Electron transport through broken down ultrathin SiO<sub>2</sub> layers in MOS devices," *Microelectronics Reliability*, vol. 44, no. 1, pp. 1–23, 2004, doi: 10.1016/j.microrel.2003.08.005.

- [9] A. Rodriguez-Fernandez, C. Cagli, L. Perniola, J. Suñé, and E. Miranda, "Identification of the generation/rupture mechanism of filamentary conductive paths in ReRAM devices using oxide failure analysis," *Microelectronics Reliability*, vol. 76-77, pp. 178–183, sep 2017, doi: 10.1016/J.MICROREL.2017.06.088.

- [10] D. Ielmini, "Modeling the Universal Set/Reset Characteristics of Bipolar RRAM by Field- and Temperature-Driven Filament Growth," *IEEE Transactions on Electron Devices*, vol. 58, no. 12, pp. 4309–4317, dec 2011, doi: 10.1109/TED.2011.2167513.

- [11] S. Larentis, F. Nardi, S. Balatti, D. C. Gilmer, and D. Ielmini, "Resistive Switching by Voltage-Driven Ion Migration in Bipolar RRAM—Part II: Modeling," *IEEE Transactions on Electron Devices*, vol. 59, no. 9, pp. 2468–2475, sep 2012, doi: 10.1109/TED.2012.2202320.

- [12] F. Nardi, S. Larentis, S. Balatti, D. C. Gilmer, and D. Ielmini, "Resistive Switching by Voltage-Driven Ion Migration in Bipolar RRAM—Part I: Experimental Study," *IEEE Transactions on Electron Devices*, vol. 59, no. 9, pp. 2461–2467, sep 2012, doi: 10.1109/TED.2012.2202319.

- [13] F. Palumbo, S. Lombardo, and M. Eizenberg, "Physical mechanism of progressive breakdown in gate oxides," *Journal of Applied Physics*, vol. 115, no. 22, 2014, doi: 10.1063/1.4882116.

- [14] F. Palumbo, P. Shekhter, K. Cohen Weinfeld, and M. Eizenberg, "Characteristics of the dynamics of breakdown filaments in Al<sub>2</sub>O<sub>3</sub>/InGaAs stacks," *Applied Physics Letters*, vol. 107, no. 12, p. 122901, sep 2015, doi: 10.1063/1.4931496.

- [15] S. Lombardo, J. H. Stathis, B. P. Linder, K. L. Pey, F. Palumbo, and C. H. Tung, "Dielectric breakdown mechanisms in gate oxides," *Journal of Applied Physics*, vol. 98, no. 12, p. 121301, dec 2005, doi: 10.1063/1.2147714.

- [16] C. H. Tung, K. L. Pey, L. J. Tang, M. K. Radhakrishnan, W. H. Lin, F. Palumbo, and S. Lombardo, "Percolation path and dielectric-breakdown-induced-epitaxy evolution during ultrathin gate dielectric breakdown transient," *Applied Physics Letters*, vol. 83, no. 11, pp. 2223–2225, sep 2003, doi: 10.1063/1.1611649.

- [17] F. Palumbo, G. Condorelli, S. Lombardo, K. Pey, C. Tung, and L. Tang, "Structure of the oxide damage under progressive breakdown," *Microelectronics Reliability*, vol. 45, no. 5-6, pp. 845–848, may 2005, doi: 10.1016/J.MICROREL.2004.11.034.

- [18] S. Privitera, G. Bersuker, B. Butcher, A. Kalantarian, S. Lombardo, C. Bongiorno, R. Geer, D. Gilmer, and P. Kirsch, "Microscopy study of the conductive filament in HfO<sub>2</sub> resistive switching memory devices," *Microelectronic Engineering*, vol. 109, pp. 75–78, sep 2013, doi: 10.1016/J.MEE.2013.03.145.

- [19] H. Du, C. L. Jia, A. Koehl, J. Barthel, R. Dittmann, R. Waser, and J. Mayer, "Nanosized Conducting Filaments Formed by Atomic-Scale Defects in Redox-Based Resistive Switching Memories," *Chemistry of Materials*, vol. 29, no. 7, pp. 3164–3173, apr 2017, doi: 10.1021/acs.chemmater.7b00220.

- [20] A. Rodriguez-Fernandez, C. Cagli, J. Sune, and E. Miranda, "Switching Voltage and Time Statistics of Filamentary Conductive Paths in HfO<sub>2</sub>based ReRAM Devices," *IEEE Electron Device Letters*, pp. 1–1, 2018, doi: 10.1109/LED.2018.2822047.

- [21] S. S. Sheu, K. H. Cheng, M. F. Chang, P. C. Chiang, W. P. Lin, H. Y. Lee, P. S. Chen, Y. S. Chen, T. Y. Wu, F. T. Chen, K. L. Su, M. J. Kao, and M. J. Tsai, "Fast-write resistive RAM (RRAM) for embedded applications," *IEEE Design and Test of Computers*, vol. 28, no. 1, pp. 64–71, jan 2011, doi: 10.1109/MDT.2010.96.

- [22] D. Ielmini, "Resistive switching memories based on metal oxides: mechanisms, reliability and scaling," *Semiconductor Science and Technology*, vol. 31, no. 6, p. 063002, jun 2016, doi: 10.1088/0268-1242/31/6/063002.

- [23] A. Fantini, D. J. Wouters, R. Degraeve, L. Goux, L. Pantisano, G. Kar, Y.-Y. Chen, B. Govoreanu, J. A. Kittl, L. Altimime, and M. Jurczak, "Intrinsic Switching Behavior in HfO<sub>2</sub> RRAM by Fast Electrical Measurements on Novel 2R Test Structures," in 2012 4th IEEE International Memory Workshop. IEEE, may 2012, pp. 1–4, doi: 0.1109/IMW.2012.6213646.

- [24] B. P. Linder, S. Lombardo, J. H. Stathis, A. Vayshenker, and D. Frank, "Voltage dependence of hard breakdown growth and the reliability implication in thin dielectrics," *IEEE Electron Device Letters*, vol. 23, no. 11, pp. 661–663, nov 2002, doi: 10.1109/LED.2002.805010.

- [25] Y. Nishi, K. Fleck, U. Bottger, R. Waser, and S. Menzel, "Effect of RESET Voltage on Distribution of SET Switching Time of Bipolar Resistive Switching in a Tantalum Oxide Thin Film," *IEEE Transactions on Electron Devices*, vol. 62, no. 5, pp. 1561–1567, 2015, doi: 10.1109/TED.2015.2411748.

- [26] S. Pazos, F. L. Aguirre, E. Miranda, S. Lombardo, and F. Palumbo, "Comparative study of the breakdown transients of thin Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> films in MIM structures and their connection with the thermal properties of materials," *Journal of Applied Physics*, vol. 121, no. 9, p. 094102, mar 2017, doi: 10.1063/1.4977851.

- [27] R. Pagano, S. Lombardo, F. Palumbo, P. Kirsch, S. Krishnan, C. Young, R. Choi, G. Bersuker, and J. Stathis, "A novel approach to characterization of progressive breakdown in high-k/metal gate stacks," *Microelectronics Reliability*, vol. 48, no. 11-12, pp. 1759–1764, nov 2008, doi: 10.1016/J.MICROREL.2008.07.071.

- [28] F. Palumbo, C. Wen, S. Lombardo, S. Pazos, F. Aguirre, M. Eizenberg, F. Hui, and M. Lanza, "A Review on Dielectric Breakdown in Thin Dielectrics: Silicon Dioxide, High- k, and Layered Dielectrics," Advanced Functional Materials, p. 1900657, apr 2019, doi: 10.1002/adfm.201900657.

- [29] K. Tang, A. C. Meng, F. Hui, Y. Shi, T. Petach, C. Hitzman, A. L. Koh, D. Goldhaber-Gordon, M. Lanza, and P. C. McIntyre, "Distinguishing Oxygen Vacancy Electromigration and Conductive Filament Formation in TiO<sub>2</sub> Resistance Switching Using Liquid Electrolyte Contacts," *Nano Letters*, vol. 17, no. 7, pp. 4390–4399, jul 2017, doi: 10.1021/acs.nanolett.7b01460.

- [30] S. Takagi, N. Yasuda, and A. Toriumi, "Experimental evidence of inelastic tunneling in stress-induced leakage current," *IEEE Transactions on Electron Devices*, vol. 46, no. 2, pp. 335–341, 1999, doi: 10.1109/16.740899.

- [31] P. E. Blöchl and J. H. Stathis, "Hydrogen Electrochemistry and Stress-Induced Leakage Current in Silica," *Physical Review Letters*, vol. 83, no. 2, pp. 372–375, jul 1999, doi: 10.1103/PhysRevLett.83.372.

- [32] S. Lombardo, E. Y. Wu, and J. H. Stathis, "Electron energy dissipation model of gate dielectric progressive breakdown in n- and p-channel field effect transistors," *Journal of Applied Physics*, vol. 122, no. 8, p. 085701, aug 2017, doi: 10.1063/1.4985794.

- [33] Y. Shacham-Diamand, A. Dedhia, D. Hoffstetter, and W. G. Oldham, "Copper Transport in Thermal SiO<sub>2</sub>," *Journal of The Electrochemical Society*, vol. 140, no. 8, p. 2427, aug 1993, doi: 10.1149/1.2220837.

- [34] E. Y. Wu, J. H. Stathis, and L.-K. Han, "Ultra-thin oxide reliability for ULSI applications," Semiconductor Science and Technology, vol. 15, no. 5, pp. 425–435, may 2000, doi: 10.1088/0268-1242/15/5/301.

- [35] Young Hee Kim, K. Onishi, Chang Seok Kang, Hag-Ju Cho, Rino Choi, S. Krishnan, M. Akbar, and J. Lee, "Thickness dependence of Weibull slopes of HfO<sub>2</sub> gate dielectrics," *IEEE Electron Device Letters*, vol. 24, no. 1, pp. 40–42, jan 2003, doi: 10.1109/LED.2002.807314.

- [36] S. Slesazeck and T. Mikolajick, "Nanoscale resistive switching memory devices: a review," *Nanotechnology*, may 2019, doi: 10.1088/1361-6528/ab2084

- [37] S. Zafar, H. Jagannathan, L. F. Edge, and D. Gupta, "Measurement of oxygen diffusion in nanometer scale HfO<sub>2</sub> gate dielectric films," *Applied Physics Letters*, vol. 98, no. 15, p. 152903, apr 2011, doi: 10.1063/1.3579256.

- [38] P. Huang, X. Y. Liu, B. Chen, H. T. Li, Y. J. Wang, Y. X. Deng, K. L. Wei, L. Zeng, B. Gao, G. Du, X. Zhang, and J. F. Kang, "A Physics-Based Compact Model of Metal-Oxide-Based RRAM DC and AC Operations," *IEEE Transactions on Electron Devices*, vol. 60, no. 12, pp. 4090–4097, dec 2013, doi: 10.1109/TED.2013.2287755.

- [39] M. Bocquet, D. Deleruyelle, H. Aziza, C. Muller, J.-M. Portal, T. Cabout, and E. Jalaguier, "Robust Compact Model for Bipolar Oxide-Based Resistive Switching Memories," *IEEE Transactions on Electron Devices*, vol. 61, no. 3, pp. 674–681, mar 2014, doi: 10.1109/TED.2013.2296793.

- [40] M. A. Villena, M. B. González, J. B. Roldán, F. Campabadal, F. Jiménez-Molinos, F. M. Gómez-Campos, and J. Suñé, "An in-depth study of thermal effects in reset transitions in HfO<sub>2</sub> based RRAMs," *Solid-State Electronics*, vol. 111, pp. 47–51, sep 2015, doi: 10.1016/j.sse.2015.04.008.