This is the **accepted version** of the article:

Nafria, Montserrat; Crespo Yepes, Albert; Rodriguez Martinez, Rosana; [et al.]. «DC characterization and fast small-signal parameter extraction of organic thin film transistors with different geometries». IEEE Electron Device Letters, Vol. 41, Issue 10 (October 2020), p. 1512-1515. DOI 10.1109/LED.2020.3021236

This version is available at https://ddd.uab.cat/record/248843 under the terms of the  $\bigcirc^{\mbox{\footnotesize IN}}$  license

# DC characterization and small signal modelling of organic thin film transistors with different geometries

A. Arnal<sup>1-3</sup>, A. Crespo-Yepes<sup>2</sup>, E. Ramon<sup>1\*</sup>, L. Terés<sup>1</sup>, R. Rodríguez<sup>2</sup> and M. Nafría<sup>2</sup>.

- 1. Institut de Microelectrònica de Barcelona, IMB-CNM (CSIC), 08193, Bellaterra, Catalonia, Spain.

- 2. Department of Electronic Engineering, Autonomous University of Barcelona (UAB), Edifici Q, 08193, Bellaterra, Spain.

- 3. PhD in Electrical and Telecommunication Engineering, Universitat Autònoma de Barcelona (UAB).

\* Corresponding author E. Ramon (Eloi.Ramon@imb-cnm.csic.es).

Abstract—Organic Devices offer low-cost manufacturing and better flexibility, sustainability and solution-processability than their Si-based MOS counterparts, which make them suitable for new applications where those characteristics are an advantage. However, organic device performance is still far from that provided by CMOS technology and many issues are still unclear. In this work, a performance comparison of Interdigitated and Corbino geometries of Organic Thin Film Transistors (OTFT), with different areas but fabricated with identical stack materials and techniques, is done. With this purpose, I-V characteristics and C-V curves of the OTFTs were measured and a Common-Source circuit was proposed and implemented for extracting relevant electrical parameters of the devices, through a standard small signal analysis. The parameter extraction methodology in the frequency domain proposed allows rapid testing of the device/circuit performance of this technology, which is for the first time applied to organic devices. Results show that organic transistors exhibit similar channel dimensions dependencies as MOS devices, despite the large voltages, and can be also described by the same small signal model.

Organic Thin Film Transistor (OTFT), Corbino Thin Film Transistor (CTFT), Organic Electronics, Capacitance-Voltage, DC characterization, small signal model.

## I. INTRODUCTION

Organic Electronics (OE) is one of the most promising technologies for the fabrication of new smart and flexible electronic systems [1]. Thanks to the diverse fabrication techniques that it comprises [2]–[5], this technology allows the use of flexible substrates and novel solution-based materials, in new smart systems in different fields such as Radio Frequency Identification (RFID) tags, disposable sensors, flexible displays or functional circuits [6]–[8]. These systems can be instant made, fully additive, low temperature processed, lightweight, bendable, scalable and sustainable, all of this combined with low-cost manufacturing. These new features enable wearable and disposable electronic systems, unfeasible for the moment with the traditional silicon technology. However, more investigations are still needed to analyze the performance of different architectures and to develop suitable models. To evaluate the properties of Organic Thin Film Transistors (OTFT) some works analyze and model their DC behavior through different parameters such as Threshold Voltage, Mobility or Driving Current, and also the Operating Voltages, which are much larger than for MOSFETs [9]. Other works analyze the frequency response of OTFTs through the measurement of S-parameters in isolated devices [10]. Moreover, some functional circuits could be used to study the OTFT performance and their response in the frequency domain, since the circuit frequency response (gain and cut-off frequency) mainly depends on the transistor parameters. Then, this work takes advantage of this dependence in a Common-Source (CS) amplifier to experimentally study the performance of Organic Thin Film Transistors (OTFT) with different architectures and areas fabricated with an already patented and commercial technology [11]. Device level measurements are also carried out, for comparison. Special emphasis is done on their frequency response related parameters, i.e., the role of the dielectric stack capacitance was analyzed in detail, for its inclusion in a small signal model. This novel methodology allows a fast extraction of device performance parameters, through the modelling of the frequency response of the test circuit. The method has been applied to the characterization of OTFTs, which operates far afield from CMOS devices.

# II. SAMPLES AND EXPERIMENTAL SETUP

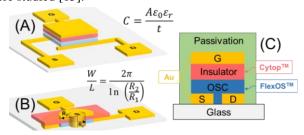

Two different architectures of Organic Thin Film Transistors have been studied: 1) Interdigitated fingers for the source and drain terminals (OTFT), and 2) Corbino [12] OTFT (CTFT) with a cylindrical shape (see Figure 1A and B, respectively). The devices are fabricated by NeuDrive Ltd. (UK) [13], using gold contacts, Cytop<sup>TM</sup> as a dielectric and proprietary organic p-type semiconductor FlexOS<sup>TM</sup> [14]. The fabrication process combines sputtering, spin coating and photolithographic steps. The cross section of the OTFT (Fig. 1A) and CTFT (Fig. 1B) are presented together with the stack of materials in Figure 1C.

The Interdigitated OTFTs processed by NeuDrive present the classical interdigitated geometry, where source and drain are interleaved behind the gate. This geometry allows easy scalability since different widths can be achieved by using multiple fingers. Two different interdigitated channel lengths were used,  $10\mu m$  and  $4\mu m$ . For the  $10\mu m$  length devices, two widths were studied:  $980\mu m$  and  $9800\mu m$ . For the  $4\mu m$  channel length devices, five widths were studied:  $160,\,320,\,640,\,1280$  and  $2560\mu m$  using two different finger widths. For the Corbino OTFT, four different channels lengths (5, 10, 20 and  $40\mu m$ ), combining three different external radius  $R_2$  (105, 100 and  $120\mu m$ ) with two internal radiuses  $R_1$  (100 and  $80\mu m$ ) were studied [15].

**Fig. 1.** Architecture of the (A) Interdigitated OTFT, and (B) Corbino OTFT. (C) OTFT Stack materials, common to both architectures.

I-V and C-V curves of the devices were measured with the Semiconductor Parameter Analyzer Keithley 4200, which allows large current and capacitance resolution measurements with high voltage biasing (±30V). The frequency response of the Common-Source amplifiers built with the studied OTFTs was determined by measuring the amplitude of the output voltage, when the frequency of the input signal was swept from 100Hz to 1MHz. General-purpose digital scope was used for the output signal measurement.

### III. DEVICE CHARACTERIZATION

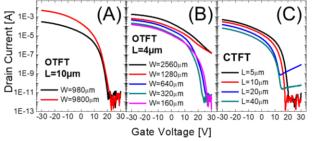

To evaluate the device performance, I-V characteristics and C-V curves were measured on the devices with different architectures and dimensions. Figure 2 shows typical Drain Current – Gate Voltage ( $I_D\text{-}V_G$ ) characteristics of all of them. As can be seen, subthreshold region is located at voltages above 0V, implying that these devices (p-type transistors) are operating in depletion mode [16]. Off currents are of the order of pA in most of the cases, meaning a low consumption when the device is off (Fig. 2). Note that, when device is on, currents in the  ${\sim}100\mu\text{A-}1\text{mA}$  range are achieved with mobilities between 1 to 1.75 cm²/V·s, under operating voltages around  ${\pm}30\text{V}$  [17]. These voltages are much larger than in CMOS technology ( ${\sim}0.8\text{V}$ ) [18], but usual in organic devices [19].

Fig. 2. Drain Current–Gate Voltage characteristics measured on Interdigitated OTFT with (A)  $L=10\mu m$ , (B)  $L=4\mu m$  and (C) Corbino OTFT.

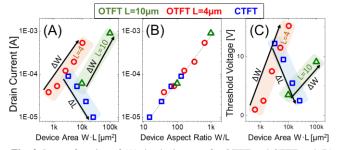

For the interdigitated OTFTs,  $I_D$  increases as expected, linearly with device width (Fig. 3A). Contrarily, for the Corbino architecture, an  $I_D$  reduction is observed (Fig. 3A), because device width and length, change with the radiuses as well (L=R<sub>1</sub>-R<sub>2</sub>). However, when representing  $I_D$  as a function of device aspect ratio, in both cases, Interdigitated and Corbino, it is proportional to W/L (Fig. 3B). To evaluate the dependence of  $V_{th}$  on the device area, as a criterium,  $V_{th}$  was defined as the gate voltage at which  $I_D$ =10 $\mu$ A. Figure 3C shows that  $V_{th}$  of Interdigitated devices grows linearly with the device width, while in the Corbino it decreases with the channel length. Note that  $I_D$  and  $V_{th}$  follow the same geometry scaling dependence that MOS technologies [20].

Fig. 3.  $I_D$  as a function of (A) the device area for OTFT and CTFT and (B) as a function of the aspect ratio W/L. (C)  $V_{th}$  as a function of device area.

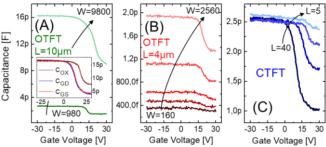

The parasitic capacitances associated to the stack were also measured (C-V curves) in the same devices. The gate capacitance (Cox) was measured when source and drain were grounded (similar values to those measured on MIM structures were obtained for the capacitances per unit area, 5,94·10<sup>-5</sup>F/m) C<sub>GD</sub> and C<sub>GS</sub> were also measured, with the drain or source terminals grounded, respectively, while the other terminal is kept floating. A strong dependence of the measured capacitance with the device area is observed (Fig. 4) for the two OTFTs architectures. The inset in Figure 4A shows that, for negative polarities, the three capacitances (C<sub>OX</sub>, C<sub>GS</sub> and C<sub>GD</sub>) are almost equal, indicating that the channel region acts as a bottom terminal of the stack when device is ON (accumulation of ptype carriers). In the case of CTFT devices, capacitance increases with device area (i.e. channel length decreases) when applying positive bias (subthreshold region). This dependence is observed because, in that regime, the area of the capacitance depends only on the overlapping between the gate and drainsource electrodes. However, at negative bias, CTFT capacitance exhibits similar values for different areas, because the effective area under the gate terminal is the same due to the effect of the channel (i.e. gate metal electrode does not scale with device area). Therefore, their cylindrical architecture implies a L-independent gate area when CTFT device is ON.

**Fig. 4.** C-V characteristic of the Gate stack for the interdigitated OTFT with (A) L=10 $\mu$ m, (B) with L=4 $\mu$ m, and for (C) Corbino OTFT. The inset in (A) shows the area dependence of the three measured capacitances.

# IV. FREQUENCY RESPONSE AND SMALL SIGNAL MODEL

In order to evaluate the performance of the studied OTFT and CTFT, a Common Source (CS) amplifier is used [21], which allows easy correlation of device and circuit performances, because the amplifier's gain and cut-off frequency strongly depend on the transistor parameters [22]. This configuration is represented in Figure 5A and the corresponding small signal equivalent circuit in Figure 5B, where a MOSFET-like smallsignal model is considered for the OTFT. Circuit analysis leads to a transfer function given by equation 1, which shows that the CS circuit gain depends on the transconductance (gm) and output resistance of the transistor (the last one included in R<sub>OUT</sub>. which is defined as  $R_{OUT} = r_0 / R_D / R_{OSC}$ ). In addition, the cut-off frequency is determined by the parasitic Gate-Drain capacitance ( $C_{GD}$ ), being independent of  $C_{GS}$ . These parameters can be extracted from |H(s)| measurements. In our experiments, the value of R<sub>SS</sub> (the output resistance of our input source), R<sub>G1</sub>, R<sub>G2</sub>, C<sub>S</sub>, R<sub>OSC</sub> and C<sub>OSC</sub> (being the last one the input impedance of our scope) and the DC voltage supply, V<sub>CC</sub>, were fixed. It must be emphasized that, in these experiments several parameters change from experiment to experiment (i.e. when a different device area or geometry are used, different voltages at device terminals are registered), thus direct comparisons are meaningless. Moreover, circuit values such as R<sub>D</sub> or V<sub>x</sub> were selected in order to maximize the gain. Then, to account for the differences in the OTFTs, RD valued could vary between  $340k\Omega$  and  $1M\Omega$ .  $V_{GS}$  and  $V_{DS}$  DC values were registered before extracting the frequency response, to assure the transistor operating point. A frequency sweep of the input signal was performed from 100Hz to 1MHz. Only the mid and high frequency regimes were analysed, since low frequency response is mainly given by the circuit parameters.

**Fig. 5.** (A) Common Source (CS) amplifier implemented to evaluate the OTFT performance in the frequency domain, and (B) small signal model for mid and high frequency regims.  $R_G = R_{G1}/R_{G2}$  and  $R_{OUT} = r_0//R_D//R_{OSC}$ .

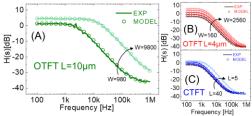

Figure 6 shows the magnitude of the frequency responses of the CS amplifiers built with the different Organic transistors, measured (lines) and their fitting to eq. 1 (circles). As observed, the gain increases with the device width and in the best case it is  $\sim$ 6dB. The cut-off frequency also increases with the device width. In addition, the effect of the transmission zero (given by  $C_{\rm GD}$ ) in eq. 1 is clearly observed in the 100kHz-1MHz interval.

Fig. 6. (A) Experimental (lines) and fitted (circles) frequency response for the Interdigitated OTFT with  $L=10~\mu m$ , ( B) Interdigitated OTFT with  $L=4~\mu m$  and (C) Corbino OTFT.

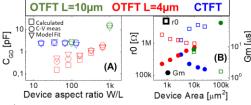

The device parameters obtained from the fitting of the experimental data in Figure 6 to eq. 1 are depicted in Figure 7. Figure 7A shows the parasitic capacitance between gate and drain terminals (C<sub>GD</sub>) as a function of the device aspect ratio obtained analytically (considering that for negative voltages C<sub>GD</sub>=C<sub>OX</sub>, as shown in the inset in Fig. 4A) (squares), from the experimental C-V curve (circles) and from the fitting of the amplifier frequency response to the eq. 1 (triangles). Similar values of C<sub>GD</sub> are obtained for the different topologies and areas for the three extraction methods. The  $r_0$  and  $g_m$  parameters are depicted in Figure 7B. A large dependence of these parameters with the channel dimensions is observed in both OTFT architectures, being less significant in the case of CTFT due to their complex device width and length radiuses-dependence. As observed, for the Interdigitated OTFT, g<sub>m</sub> increases and r<sub>0</sub> decreases linearly with device area. Inversely, for the CTFT, g<sub>m</sub> decreases and r<sub>0</sub> increases non-linearly with device area, what means larger separation between radiuses (i.e. L increase).

**Fig. 7.** (A) Analytically calculated Gate-Drain capacitance (squares), measured from the C-V curves (circles) and obtained from the data fitting (triangles). (B)  $r_0$  (empty squares) and  $g_m$  (circles) obtained from the fitting.

### V. CONCLUSIONS

Two different architectures of organic thin film transistors (Interdigitated and Corbino) with different dimensions have been studied. Their performance has been evaluated through the frequency response of an OTFT-based Common-Source (CS) amplifier, since it strongly depends on the device properties.

To extract the transistor parameters from the experimental data, a MOSFET-like small signal model of the OTFT has been assumed. The dependences observed for C<sub>GD</sub> in all the devices have been verified from the comparison of the CS-extracted values with those obtained from C-V data and analytical calculation. The results show that the extracted small signal model parameters (g<sub>m</sub>, r<sub>0</sub>, and C<sub>GD</sub>) depend on the device dimensions and materials properties. A linear dependence of r<sub>0</sub>, g<sub>m</sub> and C<sub>GD</sub> with device width is observed in the Interdigitated OTFT. In the case of the Corbino devices, C<sub>GD</sub> does not depend on the device widths or lengths (i.e. radiuses), since there is the same effective area under the gate electrode for negative biasing. g<sub>m</sub> and r<sub>0</sub> present a non-linear area dependence, due to the relation between width and length in the CTFT. Therefore, the circuit performance is strongly driven by device dimensions, as for MOS devices, despite the large voltages applied.

# Acknowledgments

This work was supported by the TEC2016-75151-C3-1-R, RTI2018-102070-B-C21, and 2017SGR-1159. Projects funded by the Spanish AEI, ERDF and Generalitat de Catalunya.

### REFERENCES

- [1] X. Guo *et al.*, "Current Status and Opportunities of Organic Thin-Film Transistor Technologies," *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 1906–1921, 2017, doi: 10.1109/TED.2017.2677086.

- [2] Y. Takeda *et al.*, "Organic Complementary Inverter Circuits Fabricated with Reverse Offset Printing," *Adv. Electron. Mater.*, vol. 4, no. 1, p. 1700313, Jan. 2018, doi: 10.1002/aelm.201700313.

- [3] S. H. Ko, H. Pan, C. P. Grigoropoulos, C. K. Luscombe, J. M. J. Fréchet, and D. Poulikakos, "All-inkjet-printed flexible electronics fabrication on a polymer substrate by low-temperature high-resolution selective laser sintering of metal nanoparticles," *Nanotechnology*, vol. 18, no. 34, p. 345202, Aug. 2007, doi: 10.1088/0957-4484/18/34/345202.

- [4] H. Jeong, S. Baek, S. Han, H. Jang, S. H. Kim, and H. S. Lee, "Novel Eco-Friendly Starch Paper for Use in Flexible, Transparent, and Disposable Organic Electronics," *Adv. Funct. Mater.*, vol. 28, no. 3, p. 1704433, Jan. 2018, doi: 10.1002/adfm.201704433.

- [5] N. A. Azarova *et al.*, "Fabrication of organic thin-film transistors by spray-deposition for low-cost, large-area electronics," *Org. Electron. physics, Mater. Appl.*, vol. 11, no. 12, pp. 1960–1965, Dec. 2010, doi: 10.1016/j.orgel.2010.09.008.

- [6] B. Kumar, B. K. Kaushik, and Y. S. Negi, "Organic thin film transistors: Structures, models, materials, fabrication, and applications: A review," *Polym. Rev.*, vol. 54, no. 1, pp. 33–111, 2014, doi: 10.1080/15583724.2013.848455.

- [7] E. R. i Garcia, "Inkjet Printed Microelectronic Devices and Circuits," no. September, 2014.

- [8] K. Myny, E. Van Veenendaal, G. H. Gelinck, J. Genoe, W. Dehaene, and P. Heremans, "An 8-bit, 40-instructions-per-second organic microprocessor on plastic foil," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 284–291, 2012, doi: 10.1109/JSSC.2011.2170635.

- [9] J. S. Chang, A. F. Facchetti, R. Reuss, S. Member, A. F. Facchetti, and R. Reuss, "A Circuits and Systems Perspective of Organic/Printed Electronics: Review, Challenges, and Contemporary and Emerging Design Approaches," *IEEE J. Emerg. Sel. Top. Circuits Syst.*, vol. 7, no. 1, pp. 7–26, 2017, doi: 10.1109/JETCAS.2017.2673863.

- [10] T. Zaki *et al.*, "AC characterization of organic thinfilm transistors with asymmetric gate-to-source and gate-to-drain overlaps," *Org. Electron.*, vol. 14, no. 5, pp. 1318–1322, 2013, doi: 10.1016/j.orgel.2013.02.014.

- [11] B. A. Brown, S. D. Ogier, M. Palumbo, and K. L. McCall, "Transistors and Methods for Making Them," 2012.

- [12] M. Mativenga *et al.*, "Infinite output resistance of corbino thin-film transistors with an amorphous-In ga znO active layer for large-area AMOLED displays," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3199–3205, 2014, doi: 10.1109/TED.2014.2338306.

- [13] "NeuDrive." [Online]. Available: http://www.neudrive.com/. [Accessed: 10-Sep-2019].

- [14] K. L. McCall *et al.*, "Low voltage high mobility organic semiconductors for flexible display applications," *Proc. Int. Disp. Work.*, vol. 3, pp. 1766–1769, 2012.

- [15] D. Munteanu, S. Cristoloveanu, and H. Hovel, "Circular Pseudo-Metal Oxide Semiconductor Field Effect Transistor in Silicon-on-Insulator Analytical Model, Simulation, and Measurements," *Electrochem. Solid-State Lett.*, vol. 2, no. 5, pp. 242–243, 1999, doi: 10.1149/1.1390798.

- [16] S. D. Ogier *et al.*, "Uniform, high performance, solution processed organic thin-film transistors integrated in 1 MHz frequency ring oscillators," *Org. Electron. physics, Mater. Appl.*, vol. 54, no. July 2017, pp. 40–47, 2018, doi: 10.1016/j.orgel.2017.12.005.

- [17] B. Kumar, B. K. Kaushik, and Y. S. Negi, "Organic thin film transistors: Structures, models, materials, fabrication, and applications: A review," *Polym. Rev.*, vol. 54, no. 1, pp. 33–111, Jan. 2014, doi: 10.1080/15583724.2013.848455.

- [18] C. Auth *et al.*, "A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects," in *Technical Digest International Electron Devices Meeting, IEDM*, 2018, pp. 29.1.1-29.1.4, doi: 10.1109/IEDM.2017.8268472.

- [19] A. Arnal, C. Martínez-Domingo, S. Ogier, L. Terés, and E. Ramon, "Monotype Organic Dual Threshold Voltage Using Different OTFT Geometries," *Crystals*, vol. 9, no. 7, p. 333, 2019, doi: 10.3390/cryst9070333.

- [20] T. Tsunomura, A. Nishida, and T. Hiramoto, "Analysis of NMOS and PMOS difference in VT variation with large-scale DMA-TEG," *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 2073–2080, 2009, doi: 10.1109/TED.2009.2026390.

- [21] X. Cheng, S. Lee, and A. Nathan, "TFT Small Signal Model and Analysis," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 890–893, 2016, doi: 10.1109/LED.2016.2575924.

- [22] D. Lovelace, J. Costa, and N. Camilleri, "Extracting small-signal model parameters of silicon MOSFET transistors," 1994 IEEE MTT-S Int. Microw. Symp. Dig. (Cat. No.94CH3389-4), pp. 865–868, 1994, doi: 10.1109/MWSYM.1994.335220.