This is the **accepted version** of the article:

Claramunt, Sergi; Ruiz, Ana; Wu, Q.; [et al.]. «A CAFM and device level study of MIS structures with graphene as interfacial layer for ReRAM applications». Solid-State Electronics, Vol. 186 (december 2021), p. 108080. DOI 10.1016/j.sse.2021.108080

This version is available at https://ddd.uab.cat/record/249448 under the terms of the GBY-NC-ND license

# A CAFM and device level study of MIS structures with graphene as interfacial layer for ReRAM applications

S. Claramunt<sup>1</sup>, A. Ruiz<sup>1,\*</sup>, Q. Wu<sup>2,\*</sup>, M. Porti<sup>1</sup>, M. Nafría<sup>1</sup>, X. Aymerich<sup>1</sup>

<sup>1</sup>Electronic Engineering Department, Universitat Autònoma de Barcelona, Barcelona 08193, Spain

<sup>2</sup>State Key Laboratory of Optoelectronic Materials and Technologies, School of Electronics and Information technology, Sun Yat-sen University, Guangzhou 510275, China

\*Corresponding authors: ana.ruiz@uab.cat, wuqian33@mail.sysu.edu.cn

Abstract— Capacitive Metal-Insulator-Semiconductor structures with graphene as interfacial layer between the HfO<sub>2</sub> dielectric and the top electrode have been fabricated and investigated at device level and at the nanoscale with Conductive Atomic Force Microscope. In particular, their electrical properties and variability have been compared to devices without graphene to evaluate their feasibility as ReRAM devices. At device level, we observe that, when graphene is present as an intercalated layer, several resistive switching cycles can be measured, meanwhile the standard structures without graphene do not show resistive switching behavior. Nanoscale analysis showed that the graphene layer prevents the microstructural irreversible damage of the oxide material during a forming process. Therefore, graphene somehow protects the structure during the CF formation. This protection would explain the observation of RS of the devices with intercalated graphene.

Keywords—ReRAM, graphene, non-volatile memory, CAFM.

#### I. INTRODUCTION

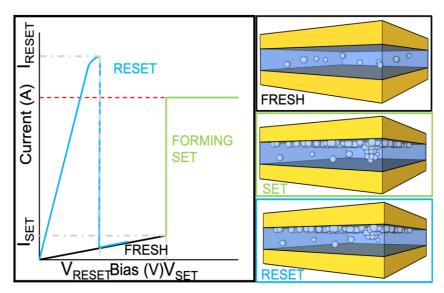

Resistive Random Access Memories (ReRAM) are a type of emerging non-volatile memory devices that offer an excellent scalability, non-volatility, high speed, high performance and compatibility with the current CMOS technology [1]. ReRAM are based in the Resistive Switching (RS) phenomenon, which consists in the change of the resistance that some insulators show under the application of an electric field. A typical ReRAM cell is fabricated by placing an insulator layer between two metal electrodes, the so-called metal-insulator-metal (MIM) structure, or between a metal electrode and a semiconductor (metal-insulator-semiconductor or MIS) structure. In some devices, the switching mechanism is believed to be based on a change in the resistivity of the insulator due to the formation of conductive filaments (CF) [2-9]. Initially, in the fresh state, the device is at the High Resistive State (HRS). If one applies low voltages to the structure, a small amount of current is detected, because of the random distribution of defects in the insulator layer (Fig. 1, black box). Usually the CFs (Fig. 1, green box) need to be initially created in a forming process (Fig.1, green curve) by means of the application of a forming voltage (Vf). After the forming process the device will be in the so called Low Resistive State (LRS). In order to switch again to the High Resistive State (HRS), a new voltage pulse must be applied, to trigger the RESET process (Fig.1, blue curve), being the voltage value at which the switching back to the HRS happens known as the reset voltage (V<sub>RESET</sub>). During this process, the CF is destroyed/closed (Fig.1, blue box), increasing the gate oxide resistance. Finally, once the reset process is done the device could return again to the LRS by applying another controlled voltage pulse, called set process. Now, the CF is re-opened, reducing the oxide resistivity and, consequently, reaching the LRS again. The voltage at which the device switches from the HRS to the LRS is called set voltage (V<sub>SET</sub>). Usually, V<sub>SET</sub> is lower than Vf, as the CF was already created during the forming, so during the set processes only a re-opening of the filament is necessary. In either the set or forming processes a compliance current is enforced through the ReRAM cell in order to avoid the complete destruction of the RRAM cell. Once the CF is created, subsequent reset and set processes can change the device between the HRS and LRS states. Depending on the polarities of V<sub>SET</sub> and V<sub>RESET</sub>, we can distinguish between two types of RS: unipolar and bipolar. In unipolar RS, V<sub>SET</sub> and V<sub>RESET</sub> have the same polarity (either positive or negative) meanwhile in the bipolar case, set and reset processes occur at opposite polarities. Usually the reset process in the unipolar switching is related to the joule heating effect on the CF formed during the forming/set process [10], meanwhile in the bipolar case it is associated mainly to the migration of charges and/or metallic ions [11].

Resistive switching is strongly dependent on the used materials. Regarding the insulator, different oxides have been reported to show RS, but binary metal oxides are the most promising candidates. Examples are titanium oxide (TiO<sub>2</sub>) [12], zinc oxide (ZnO) [10], aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) [13] or hafnium oxide (HfO<sub>2</sub>) [2, 4, 9]. The last one is very interesting as it has shown either unipolar or bipolar switching[14], high cycle endurance and retention times [15] and, in top of all, is already widely used in the CMOS fabrication technology [16], so it could be easily integrated, for example, in 3D cross-point arrays [17]. Regarding the electrodes, it has been reported that the formation/destruction of the CF and, in consequence, the behaviour of the ReRAM cell, strongly depends on the materials used in the electrodes and even in the fabrication processes [18]. Recently, novel materials like graphene [19] were proposed to improve the device performance. Graphene is a 1 atom thick carbon-based material isolated for the first time by Geim and Novoselov in 2004 [20] that presents incredible physical properties like high conductivity [21], high thermal transport [22], high flexibility and transparency [23], among others. Moreover, due to its planar nature, it could be compatible with the typical CMOS processes and could be easily intercalated in RRAM cells during its fabrication.

Fig. 1. Example of the IV curve of a unipolar RS process (left) and the model of each state (right). First the RRAM cell is at the Fresh state (black color), with the oxygen vacancies distributed randomly through the oxide. Then, after the Forming/Set process (green color), the oxygen vacancies will be concentrated to the most reactive electrode (in this case the top electrode) and a conductive filament is formed. In the Reset process (blue color) the CF is broken due to joule heating.

Graphene can be synthetized using different methods. For electronic applications the most common method is the Chemical Vapor Deposition (CVD) [24]. In this method, a copper sheet is used as a catalyst for the growth of the graphene layer using NH3 as a precursor gas. This method has the advantage that is self-limited (it stops at one carbon layer) and nowadays it is possible to fabricate square-meter sized graphene sheets [25]. On the other hand, the resulting graphene sheet is polycrystalline presenting grain boundaries, hindering its physical properties compared to single-crystal graphene [26]. Moreover, it is needed a transference process to place the graphene layer from the copper sheet to the target substrate [27]. Usually, this transference process results in the formation of wrinkles and holes [28], although newer transference techniques minimize these problems [29]. Different studies have been conducted to analyse the effect of an intercalated graphene layer between the top electrode and the insulator in a Metal-Insulator-Metal (MIM) or Metal-Insulator-Semiconductor (MIS) structure in HfO<sub>2</sub> ReRAM cells. In Mannequin et. al. they use graphene as a buffer layer between an Au electrode and the HfO2 insulator layer, resulting in a stabilization of the LRS, leading to a better control of the formation of the CF, as the graphene layer avoids interfacial interactions[30], preventing the migration of metal atoms into the insulator or acting as an oxygen barrier[31]. Note that, due to the localised nature of the CFs, the analysis of the mechanisms involved in the RS is not easy. Many works have studied RS at device level, that is, in devices in which the gate area is covered by a metal film. However, these studies do not allow a direct observation of the nanoscale features of the dielectric material, which is crucial to understand the physical phenomena underlying the CF formation. Therefore, high spatial resolution techniques are required to evaluate their properties. Several works have used nanoscale resolution techniques for the study of the CF characteristics, as the combination of Focused Ion Beam (FIB) and Transmission Electron Microscopy (TEM) [32]. Another alternative is the use of Conductive Atomic Force Microscopy (CAFM), which allows to measure, at the nanoscale, topographical and current maps of a given material. CAFM has been already used to study at the nanoscale high-k dielectrics [33-40], 2D materials as graphene [41-45], RS and the characteristics of the CF [4, 5].

In this work, the electrical properties and variability at device level and at the nanoscale (using CAFM) of MIS structures with and without graphene as interfacial layer between the top electrode and the dielectric are studied. The objective is to compare the electrical behaviour of these two type of structures and preliminary evaluate their feasibility for ReRAM applications.

## II. EXPERIMENTAL

In this work, MIS capacitors with ultra-thin HfO<sub>2</sub> dielectrics have been fabricated and analysed. In some of them, a graphene layer between the high-k dielectric and the top electrode was intercalated. These structures are called, from now on, Metal-Graphene-Insulator-Semiconductor (MGIS) devices.

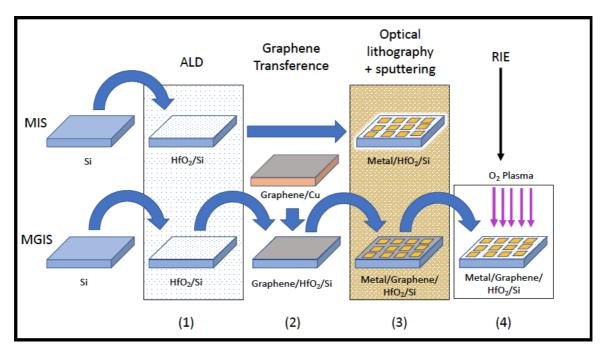

The fabrication of the MIS and MGIS devices is schematically depicted in Figure 2. First, a 6.6 nm thick HfO<sub>2</sub> layer was deposited by Atomic Layer Deposition (ALD) at 200°C on a p-Si substrate (Step 1). After that, for the MGIS devices, a graphene monolayer is deposited over the HfO<sub>2</sub> (Step 2). To do so, first a graphene monolayer is grown using the Chemical Vapor Deposition (CVD) method over a Cu foil [24]. The graphene monolayer is transferred over the HfO<sub>2</sub>/Si substrate using the following procedure [46]: first, a layer of PMMA is spin-coated over the graphene/Cu. This PMMA will be a scaffold for the graphene layer when it is detached from the Cu layer. Then, the PMMA/Graphene/Cu is placed in a container with FeCl<sub>3</sub> in order to etch the Cu layer away. After that, the PMMA/Graphene is placed consecutively in a HCl and deionized water

container in order to totally clean the Graphene monolayer from Cu residues. Finally, the PMMA/Graphene is "fished" from the water container using the HfO<sub>2</sub>/Si substrate. After the water is dried, the PMMA is removed using acetone. In order to clean the surface of the graphene layer of possible polymer residues, the graphene/HfO<sub>2</sub>/Si stack is heated at 400°C in a H<sub>2</sub>/N<sub>2</sub> atmosphere for 4 hours. The next step is to fabricate the metal electrodes by means of optical lithography (Step 3). First, a thin layer of photosensitive resin was spin-coated over the sample (the HfO<sub>2</sub>/Si stack for the MIS and the Graphene/HfO<sub>2</sub>/Si stack for the MGIS). Then, using a Microwriter from Durham-Magneto,  $80x80 \mu m^2$  square windows were patterned by laser and later removed by means of a developer. Following the optical lithography, a metal layer of Au (20nm)/Ti (40nm) was deposited by sputtering using an Evaporation System Auto 306 from Boc Edwards. After the lift-off of the photosensitive layer, this procedure results in a pattern of  $80x80 \mu m^2$  Au/Ti electrodes over the samples. For the case of the MGIS samples an additional step is necessary, consisting in an attack with an O<sub>2</sub> plasma using a Reactive Ion Etcher (RIE 2000 CE) from South Bay Technology Inc. in order to eliminate the exposed graphene between the metallic pads (Step 4).

Figure 2. Fabrication steps of the MIS and MGIS devices. In Step 1 a HfO<sub>2</sub> layer is deposited on a Si substrate. In Step 2 the graphene monolayer is transferred to the future MGIS sample. Then in Step 3 metal electrodes are defined by means of optical lithography and sputtering. Finally, for the MGIS devices, a fourth step is needed in order to eliminate the excess of graphene by means of RIE. Steps 1 and 3 are common for the MIS and MGIS devices while step 2 and 4 correspond only the MGIS devices.

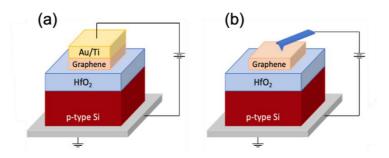

The fabricated devices have been analysed at device level (Fig. 3a) with a Semiconductor Parameter Analyzer (SPA) and at nanoscale with a CAFM (Fig. 3b). At device level, current limited (CL) Ramped Voltage Stresses (RVS) were applied (CL=0.1A or 0.1mA), in order to control the CF forming process and evaluate their feasibility as Resistive Switching (RS) based memory devices. At the nanoscale, the morphological and electrical properties of the devices were measured with an Agilent 5500 AFM, which was connected to a Resiscope Module (CSI Instruments [47]) in order to be able to measure currents in a higher dynamic range (from pA to mA) compared to standard CAFMs. With our CAFM setup, the role of the graphene layer on the CF formation was evaluated from the measurement of morphological and current images on areas where the CF was induced with the CAFM tip on devices without top electrode (Fig. 3b). With this configuration, the CAFM tip plays the role of the top electrode. The used tip was a bulk Pt tip from Rocky Mountain Nanotechnology and measurements were obtained in contact mode. For the measurement of the current images and I-V curves at the nanoscale, during the scans, a voltage was applied at the substrate while the tip was grounded.

Fig. 3. Scheme illustrating the experimental configuration of device level (a) and nanoscale (b) measurements of MGIS devices. In (b), the AFM tip plays the role of the top electrode.

#### III. RESULTS

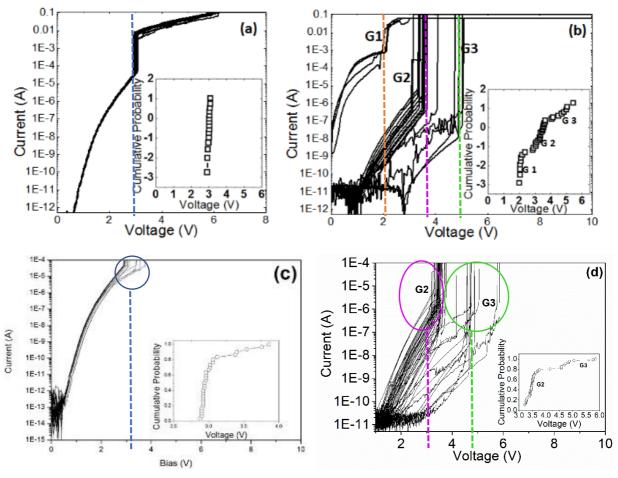

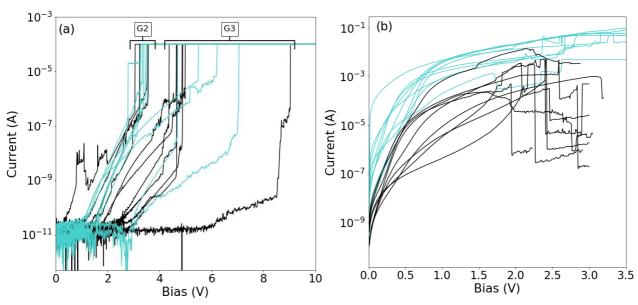

The electrical conduction and the subsequent forming process of the MIS and MGIS devices have been first investigated from the measurement of I-V curves when CL of 0.1A or 0.1mA were used. Fig. 4 shows a set of typical I-V characteristics measured on different MIS (a and c) and MGIS (b and d) devices, when CL=0.1 A (a and b) and CL=0.1mA (c and d) is applied. The inset corresponds to the Weibull plot of the forming voltage (V<sub>F</sub>). MIS structures (Fig. 4a and c) show a very small variability in the tunnelling conduction before the forming process. V<sub>F</sub> also shows very small variations. These results demonstrate that the gate dielectric properties are very homogeneous in the set of devices. However, in the MGIS devices (Fig. 4b and d), larger deviations are observed in both, the currents measured before the forming and in V<sub>F</sub> (Fig. 4b and d, inset). The I-V curves measured in MGIS devices (Fig. 4b and d) can be classified in 3 different groups depending on its morphology and (V<sub>F</sub>, I<sub>F</sub>) values. Few MGIS devices showed higher currents and smaller V<sub>F</sub> than MIS devices, classified as Group 1 (G1) in Fig. 4b. This group is not observed in the analysed set of devices when CL=0.1 mA. It can be seen that most of the devices behave like those in Group 2 (G2). These MGIS devices mostly show higher V<sub>F</sub> and smaller I<sub>F</sub> (although still with high variability) compared to MIS devices. Finally, Group 3 (G3) shows an erratic and much smaller conductivity and higher V<sub>F</sub> than MIS devices and even MGIS devices from G2. It is worth noting that the fresh current measured before the Forming event is completely different between the different groups. Taking into account that the only new element in the MGIS devices is the graphene layer (compared to MIS devices, without an important variability) we can conclude that the resulting quality of the graphene interlayer after fabrication of the MGIS could be the origin of the different behaviours observed in MGIS devices.

Fig. 4. I-V characteristics measured on (a and c) MIS and (b and d) MGIS devices for CL=0.1A (a and b) and CL=0.1mA (c and d). In (c) and (d) the forming voltage is highlighted in a cercle.

In order to obtain more insight of this phenomenon, the electrical properties of the MIS and MGIS devices after the forming process have been also analysed. After forming with CL=0.1A, the I-V curves measured on both the MIS and MGIS devices show the typical irreversible post-breakdown conduction behaviour, so that RS was not observed. For MIS devices, the CF formation was also irreversible in the case of the smaller CL=0.1 mA. This result is not unexpected, as the relatively big area of the device ( $6400 \, \mu m^2$ ) combined with the thin oxide layer ( $6.6 \, nm$ ) promotes a hard breakdown independently of the CL applied. However, the behaviour of the MGIS devices when CL=0.1mA is somehow different. The devices in Group 1 did not show RS, which could be related to holes in the graphene layer that may be generated during device fabrication. These holes promote the direct contact between the metal electrode and the oxide layer provoking an irreversible breakdown like in the MIS devices. The high conductivity compared to MIS devices and low VF We detected that some of the G2 and G3 devices

showed RS after the forming. Figure 5a shows some examples of the Forming IVs of G2 and G3 devices from Fig. 4d. The I-Vs in green correspond to MGIS devices that showed RS meanwhile those in red are those that suffered an irreversible breakdown. Although there is a mix of behaviours between groups, one can see that irreversible Forming processes are mainly associated to G2 devices, whereas the MGIS that showed RS cycles are mostly linked to G3. In general, G3 MGIS devices present lower conduction and higher V<sub>F</sub> than the samples from G2. These results could be explained recalling that during Forming/Set process the oxygen ions will bond to the defects in the MGIS graphene layer, i.e., [31], defects present at grain boundaries (GB), wrinkles, etc. The noticeable difference between the fresh I-V curves (before Forming) between G2 and G3, and the fact that for G2 devices usually RS is not observed (as in the MIS devices) suggest that in the G2 MGIS devices there could be cracks in the graphene layer (i.e., regions of the oxide not covered by the graphene layer that are formed during the transference process [28]) that could allow the direct contact between the Ti from the top electrode and the HfO<sub>2</sub>, becoming preferential sites to the oxygen ions to bond. So, this MGIS would behave similarly to the MIS devices, but, as the top electrode contact area would be smaller, the current would be smaller too, when compared to MIS devices. The few cases in which RS is observed in G2 devices could indicate that the crack in the graphene layer is very small so that a soft-breakdown occurs. In the case of G3, a more homogeneous graphene layer could be present (i.e., without cracks) and the oxygen ions would attach to the grain boundaries and other defects until a soft-breakdown occurred due the oxygen vacancies. Further works are necessary to demonstrate this hypothesis.

The corresponding first LRS curve after the forming process for each sample in Fig. 5a is plotted in Fig. 5b. Green colour correspond to the samples that showed RS while red colour to the samples that showed an irreversible CF. Note that the MGIS samples that show a Reset event present lower currents. This phenomenon could be explained by the formation of a thicker CF in the case of a hard breakdown [5] increasing the conductivity of the device in the LRS.

Fig. 5. (a) Forming I-V curves of MGIS with CL=0.1 mA and (b) their corresponding LRS curves after the forming process. Green colour corresponds to MGIS that show RS meanwhile red colour curves represents MGIS devices that show a hard breakdown.

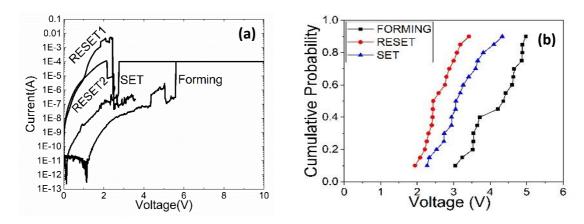

Although the geometry of the MGIS devices difficult subsequent switching cycles (in a similar way than the irreversible CF formation of the MIS devices), a preliminary study of the variability of the fabricated devices has been performed. Fig. 6a shows, as example, 2 RS cycles measured on the same MGIS device. Note that after the forming, the device was reset from the LRS to a HRS (RESET1, without any current limit) by applying an RVS with the same polarity (unipolar RS). SET and RESET2 correspond to the I-V curves of the second cycle. Therefore, since RS is only observed when graphene is intercalated between the  $HfO_2$  and the top electrode, the results confirm that graphene controls the formation of the CF, avoiding destructive microstructural damage and allowing the observation of RS.

The device-to-device variability of the first  $V_{SET}$ ,  $V_{RESET}$  and  $V_F$  was preliminary analyzed. Fig. 6b shows the cumulative probability function of  $V_F$  (squares), the first  $V_{RESET}$  (circles) and the first  $V_{SET}$  (triangles) of different MGIS devices that showed RS (CL=0.1mA). Note that the  $V_F$  variability is larger in MGIS devices (Fig. 4b and 4d) than in MIS capacitors, as observed previously in Fig. 4 (insets), which is also quite high compared to other technologies. The higher variability observed during the formation of the CF in graphene based devices could be related, as previously mentioned, to defects in the graphene layer and/or introduced during the fabrication process [48]. Moreover,  $V_F$  values are closer to  $V_{SET}$  (around 1V) in comparison with other similar technologies that do not use graphene as a interfacial layer (around 2-3V) [49], suggesting that graphene really might have a role in the formation of the CF. Graphene not only avoids irreversible damage (allowing the RS observation), but also makes the re-opening of the CF after the corresponding RESET more difficult (a higher voltage is required) than in other similar technologies [49, 50], further supporting the protective role of the graphene layer.

Fig. 6 (a) Example of two RS cycles measured on a MGIS device. (b) Cumulative probability of  $V_F$  (squares), the first  $V_{RESET}$  (circles) and the first  $V_{SET}$  (triangles) of different devices.

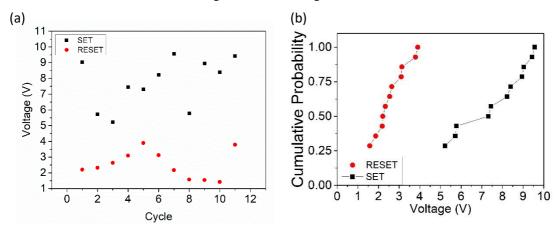

When  $V_{RESET}$  are analyzed (Fig. 6b), one can conclude that their variability is similar (although higher in the case of  $V_{SET}$ ) to that measured in other technologies. Therefore, in this case, it is not clear if such variability could be related to either the graphene or the oxide properties. Further analysis should be performed to clarify this point, which is out of the scope of this paper. Note also that, due to the  $V_{RESET}$  and  $V_{SET}$  variability, their statistical distributions are very close, not showing a clear voltage window between them. From a practical point of view, this could be a problem, since our devices show unipolar RS and a clear window between  $V_{RESET}$  and  $V_{SET}$  would be required. However, it must be taken into account that such distributions correspond to the first  $V_{RESET}$  and  $V_{SET}$  of different devices, showing the inter-device variability. When the intradevice variability is investigated, the preliminary results are different. As an example, Fig. 7a shows the cycle-to-cycle variability of  $V_{SET}$  (black squares) and  $V_{RESET}$  (red circles) of one device. The Weibull plots of  $V_{SET}$  and  $V_{RESET}$  of this device is also shown in Fig 7b. Note that now a voltage window separating both distributions can be observed. Note, moreover, that in the case of the analyzed device,  $V_{SET}$  variability is higher than that of  $V_{RESET}$ , being this result also compatible with the data shown in Fig. 6b. Further studies are necessary to investigate the origin of this behavior. However, these observations, together with the fact that only few devices showed several RS cycles, allowed us to conclude that when comparing forming, set and reset voltages,  $V_{SET}$  is the less stable and controllable parameter. So the most difficult issue for the observation of RS in the fabricated MGIS devices is to control the set voltage without inducing irreversible CFs.

Fig. 7. (a) Variability of  $V_{\text{SET}}$  (black squares) and  $V_{\text{RESET}}$  (red circles) during 14 cycles observed in the same device. Cumulative probability of  $V_{\text{SET}}$  (black squares) and  $V_{\text{RESET}}$  (red circles) is shown in (b).

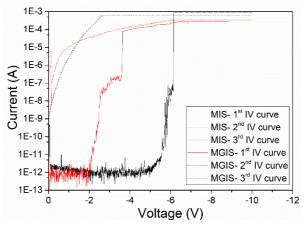

The role of the graphene layer on the formation of the CF in MGIS devices was also investigated at the nanoscale with CAFM. To perform this study, structures as those shown in Fig. 3b, that is, without top electrode, were used (Graphene-Insulator-Semiconductor structures). Identical structures without graphene were also considered as reference (Insulator-Semiconductor structures). Note that during the CAFM measurements, the Pt tip acts as a top (metallic) electrode, so that we will still talk about MIS and MGIS structures but now the top electrode is Pt, so that the obtained data is not directly comparable to those in fully developed structures. In both structures, RVS (without CL) were applied at different sites until the CF was formed. Examples of I-V curves measured with the CAFM in MIS (black) and MGIS (red) structures are shown in Fig. 8. On each sample, three I-V curves were measured at the same site. The first one shows the formation of the CF, while the second and third ones correspond to the post-forming conduction. Note that the currents measured with CAFM (Fig. 8) on the MIS structure before the CF formation are smaller (at a given voltage) compared to those registered at device level (Fig. 4a). This is because the area through which current is collected with the CAFM is smaller: while at device level the current is measured

Fig. 8. Forming and the next two I-V curves measured on MIS (black) and MGIS (red) structures measured with CAFM. No CL was used. The maximum current measurable by the setup is 1mA. In both kind of samples an irreversible BD was induced, so the RS could not be observed.

through the whole area of the device  $(80x80\mu m^2)$ , in CAFM experiments only the current through the contact area between the tip and the sample is registered. This contact area is much smaller ( $\sim 300 \text{nm}^2$  on oxides), leading to lower currents. The area through which current can flow would also explain the higher currents measured with CAFM in MGIS structures (compared to MIS structures) before de CF formation: although the physical contact area of the CAFM tip with the surface is similar in both cases, the conduction area in the MGIS devices is larger because graphene is not an insulator. In both structures (MIS and MGIS), the second and third I-V curves measured at the same site show a higher conductivity, demonstrating that the CF was actually formed. Note that in both samples, probably due to the fact that a different material was used as top electrode (now the Pt tip plays the role of the top electrode) or because no CL was applied during the forming, irreversible CF were formed and no RS was observed, which is compatible with the results in Fig. 4b.

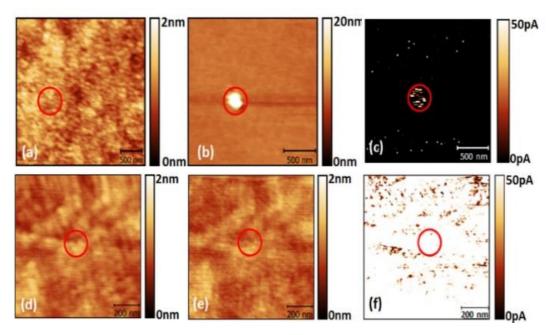

Despite that in any case RS was observed, the comparison of the CFs induced in the samples could provide information at the nanoscale when such CFs are scanned with the CAFM. After the formation of the CF with the CAFM, topographical and current maps of the areas where the CFs were created were measured with the CAFM. Fig. 9 shows topographic (b and e) and current (c and f) images obtained with the CAFM at a gate voltage of 0.1V on the gate area of a MIS (a, b and c) and MGIS (d, e, and f) structure (recall that in this case, the top electrode was the Pt tip), corresponding to the areas where I-V curves such as those shown in Fig. 8 were measured on the region inside the circles. For comparison, Fig. 9a and 9d correspond to topographical images obtained before the RVS were applied. Note that the background current in the MGIS structure (Fig. 9f) is larger than in the MIS device because of the larger conduction area under the tip associated to the non-insulating graphene layer.

Fig. 9. Topographical (a, b, d and e) and current (c and f) images obtained with the CAFM on the gate area of a MIS (a, b and c) and MGIS (d, e and f) structure, without top electrode before (a and d) and after (b, c, e and f) RVS were applied at different sites (inside the circles).

In the MIS structure, at the site where the CF was created, a hillock in the topography (Fig. 9b), not measured before the RVS (Fig. 9a), was observed (6 nm high), indicating that the oxide has been seriously damaged [51]. Moreover, higher currents (~120pA at 0.1V) than in the rest of the oxide are also registered at the same site, as expected, since a conductive path was created between the two electrodes. In this case, the CF formation has been irreversible and uncontrolled and has completely destroyed the oxide (as shown also in Fig. 8), leading to hillocks that could be related to Dielectric Breakdown Induced Epitaxy [52] (DBIE, damage induced in the oxide microstructure due to thermo-chemical effects) and/or to charge trapping at the conductive filaments [51]. On MGIS devices, however, despite the CF formation is also irreversible, no significant changes were observed in the topographical images measured before and after the CF formation (Fig. 9d and 9e). In addition, in Fig. 9f (MGIS structure), no spot with a remarkable larger current is measured because the CF is masked by the larger background current. Therefore, these results further demonstrate that graphene somehow protects the structure during the CF formation. Although irreversible CFs were also created with CAFM in the MGIS devices (remember that CAFM IV curves were applied without CL), the presence of graphene somehow protects the MGIS structure leading to a softer BD event. This protection observed at the nanoscale would explain the observation of RS at device level in the MGIS devices (Fig. 6a) when a CL is applied, compared to MIS devices where a catastrophic damage was measured (Fig. 4) even in the case of using a CL. This protection could be related to the screening effect of the electric field applied to the structure, already observed in [53] due to the presence of a graphene interface layer. Though the screening degrades the device electrostatics (worsening the performance of transistors [53]), in the case of ReRAM devices it could be a great advantage, avoiding the formation of irreversible CFs, and allowing the observation of RS, as our results suggest.

#### IV. CONCLUSIONS

The variability of the CF forming and the RS properties of capacitive structures with thin HfO<sub>2</sub> layers as dielectric and graphene as interfacial layer between the dielectric and the top electrode (MGIS devices) have been analysed (at device level and at the nanoscale, with CAFM) and compared to identical devices without graphene. The device-to-device variability of the MGIS structures, is larger than in MIS capacitors probably related to defects in the graphene layer and/or introduced during the transfer process. The intercalation of the graphene layer prevents the microstructural irreversible damage of the HfO<sub>2</sub> layer allowing the observation of unipolar RS phenomenon at device level, which was not detected in devices without graphene. These results suggests the potential use of the MGIS structures for ReRAM applications.

### V. ACKNOWLEDGEMENT

This work has been partially supported by the Spanish AEI and ERDF (TEC2016-75151-C3-1-R).

#### REFERENCES

- [1] J. Y. Seok *et al.*, "A Review of Three-Dimensional Resistive Switching Cross-Bar Array Memories from the Integration and Materials Property Points of View," *Adv. Funct. Mater.*, vol. 24, no. 34, pp. 5316–5339, Sep. 2014.

- [2] J. K. Schaeffer, L. R. C. Fonseca, S. B. Samavedam, Y. Liang, P. J. Tobin, and B. E. White, "Contributions to the effective work function of platinum on hafnium dioxide," *Appl. Phys. Lett.*, vol. 85, no. 10, pp. 1826–1828, 2004.

- [3] T.-H. Hou, K.-L. Lin, J. Shieh, J.-H. Lin, C.-T. Chou, and Y.-J. Lee, "Evolution of RESET current and filament morphology in low-power HfO<sub>2</sub> unipolar resistive switching memory," *Appl. Phys. Lett.*, vol. 98, no. 10, p. 103511, Mar. 2011.

- [4] M. Lanza, G. Bersuker, M. Porti, E. Miranda, M. Nafría, and X. Aymerich, "Resistive switching in hafnium dioxide layers: Local phenomenon at grain boundaries," *Appl. Phys. Lett.*, vol. 101, no. 19, p. 193502, Nov. 2012.

- [5] S. Claramunt *et al.*, "Non-homogeneous conduction of conductive filaments in Ni/HfO<sub>2</sub>/Si resistive switching structures observed with CAFM," *Microelectron. Eng.*, vol. 147, pp. 335–338, Nov. 2015.

- [6] Y. S. Kim *et al.*, "Resistive switching behaviors of NiO films with controlled number of conducting filaments," *Appl. Phys. Lett.*, vol. 98, no. 19, p. 192104, May 2011.

- [7] M. A. Villena *et al.*, "Simulation of thermal reset transitions in resistive switching memories including quantum effects," *J. Appl. Phys.*, vol. 115, no. 21, p. 214504, Jun. 2014.

- [8] N. Raghavan, "Failure of Weibull distribution to represent switching statistics in OxRAM," *Microelectron. Eng.*, vol. 178, pp. 230–234, Jun. 2017.

- [9] X. Wu *et al.*, "Evolution of Filament Formation in Ni/HfO 2 /SiO x /Si-Based RRAM Devices," *Adv. Electron. Mater.*, vol. 1, no. 11, p. 1500130, Nov. 2015.

- [10] W.-Y. Chang, Y.-C. Lai, T.-B. Wu, S.-F. Wang, F. Chen, M.-J. Tsai, "Unipolar resistive switching characteristics of ZnO thin films for non-volatile memory applications", *App. Phys. Lett.*, vol. 92, p. 022110, 2008.

- [11] Y.C. Yang, F. Pan, Q. Liu, M. Liu, F. Zeng, "Fully Room-Temperature-Fabricated Nonvolatile Resistive Memory for Ultrafast and High-Density Memory Application", *Nano Lett.*, vol. 9, no. 4, pp. 1636–1643, 2009.

- [12] D.-H Kwon *et al.*, " Atomic structure of conducting nanofilaments in TiO2 resistive switching memory", *Nat. Nanotechnol.*, vol. 5, pp. 148-153, 2010.

- [13] Y. Wu, S. Yu, B. Lee, P. Wong, "Low-power TiN/Al<sub>2</sub>O<sub>3</sub>/Pt resistive switching device with sub-20 μA switching current and gradual resistance modulation", *J. Appl. Phys.*, vol. 110, no. 9, p. 094104, 2011.

- [14] L. Goux, Y.-Y Chen, L. Pantisano, X.-P. Wang, G. Groeseneken, M. Jurczak, D. J. Wouters, "On the Gradual Unipolar and Bipolar Resistive Switching of TiN\ HfO<sub>2</sub>\Pt Memory Systems", *Electrochem. Solid ST.*, vol. 13, p. G54, 2010.

- [15] F. Yuan, et al., "Conduction Mechanism and Improved Endurance in HfO<sub>2</sub>-Based RRAM with Nitridation Treatment", Nanoscale Res Lett, vol. 12, p. 574, 2017.

- [16] L. Kang, K. Onishi, Y. Jeon, B.H. Lee, C. Kang, W.-J. Qi, R. Nieh, S. Gopalan, R. Choi, J.C. Lee, "MOSFET devices with polysilicon on single-layer HfO<sub>2</sub> high-K dielectrics", : International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), pp. 35-38, 2000.

- [17] K.-M. Persson, M.S. Ram, O.-P. Kilpim, M. Borg, L.-E. Wernersson, "Cross-Point Arrays with Low-Power ITO-HfO<sub>2</sub> Resistive Memory Cells Integrated on Vertical III-V Nanowires", *Adv. Electron. Mat.*, vol. 6, no. 6, p. 2000154, 2020

- [18] K.-L. Lin, T.-H. Hou, J. Shieh, J.-H. Lin, C.-T. Chou, and Y.-J. Lee, "Electrode dependence of filament formation in HfO 2 resistive-switching memory," *J. Appl. Phys.*, vol. 109, no. 8, p. 084104, Apr. 2011.

- [19] S. Sato, "Graphene for nanoelectronics", Jpn. J. Appl. Phys., vol. 54, p. 040102, 2015.

- [20] K. S. Novoselov *et al.*, "Electric Field Effect in Atomically Thin Carbon Films," *Science*, vol. 306, no. 5696, pp. 666–669, Oct. 2004.

- [21] D. V. Tuan, J. Kotakoski, T. Louvet, F. Ortmann, J. C. Meyer, S. Roche, "Scaling Properties of Charge Transport in Polycrystalline Graphene", *Nano Lett.*, vol. 13, pp. 1730-1735, 2013.

- [22] W. Cai, A. L. Moore, Y. Zhu, X. Li, S. Chen, L. Shi, R. S. Ruoff, "Thermal transport in suspended and supported monolayer graphene grown by chemical vapor deposition", *Nano Lett.*, vol.0, no. 10, pp. 1645-1651, 2010.

- [23] K. S. Kim, Y. Zhao, H. Jang, S. Y. Lee, J. M. Kim, K. S. Kim, J.-H. Ahn, P. Kim, J.-Y. Choi, B. H. Hong, "Large-scale pattern growth of graphene films for stretchable transparent electrodes", *Nature*, vol. 457, pp. 706-710, 2009.

- [24] X. Li *et. al.*, "Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils", *Science*, vol. 324, no. 5932, pp. 1312-1314, 2009.

- [25] E. S. Polsen, D. Q. McNerny, B. Viswanath, S. W. Pattinson, A. J. Hart, "High-speed roll-to-roll manufacturing of graphene using a concentric tube CVD reactor", *Sci. Rep.*, vol. 5, p. 10257, 2015.

- [26] X. Zhou, S.-H. Ji, , S.P. Chockalingam, J.B. Hannon, R.M. Tromp, T.F. Heinz, A. N. Pasupathy, F.M. Ross, "Electrical transport across grain boundaries in graphene monolayers on SiC(0 0 0 1)", 2D Mater., vol. 5, no. 3, p. 031004, 2018.

- [27] J. W. Suk, A. Kitt, C.W. Magnuson, Y. Hao, S. Ahmed, J. An, A.K. Swan, B.B. Goldberg, R.S. Ruoff, "Transfer of CVD-Grown Monolayer Graphene onto Arbitrary Substrates", ACS Nano, vol. 5, no. 9, pp. 6916-6924, 2011.

- [28] Y. Chen, X.-L. Gong J.-G. Gai, "Progress and Challenges in Transfer of Large-Area Graphene Films", *Adv. Sci.*, vol. vol. 3, no. 8, p. 1500343, 2016.

- [29] J. Qu, B.-W. Li, Y. Shen, S. Huo, Y. Xu, S. Liu, B. Song, H. Wang, C. Hu, W. Feng, "Evaporable Glass-State Molecule-Assisted Transfer of Clean and Intact Graphene onto Arbitrary Substrates", ACS Appl. Mater. Interfaces, vol. 11, no. 18, pp. 16272–16279.

- [30] A. Misra *et al.*, "Work function tuning and improved gate dielectric reliability with multilayer graphene as a gate electrode for metal oxide semiconductor field effect device applications," *Appl. Phys. Lett.*, vol. 100, no. 23, p. 233506, Jun. 2012.

- [31] H. Tian *et al.*, "Monitoring Oxygen Movement by Raman Spectroscopy of Resistive Random Access Memory with a Graphene-Inserted Electrode," *Nano Lett.*, vol. 13, no. 2, pp. 651–657, Feb. 2013.

- [32] G. Martín, M.B. González, F. Campabadal, F. Peiró, A. Cornet, S. Estradé, "Transmission electron microscopy assessment of conductive-filament formation in Ni–HfO<sub>2</sub>–Si resistive-switching operational devices", vol. 11, no. 1, p. 014101, 2018.

- [33] M. Lanza *et al.*, "Grain boundaries as preferential sites for resistive switching in the HfO 2 resistive random access memory structures," *Appl. Phys. Lett.*, vol. 100, no. 12, p. 123508, Mar. 2012.

- [34] F. Hui *et al.*, "Graphene and Related Materials for Resistive Random Access Memories," *Adv. Electron. Mater.*, vol. 3, no. 8, p. 1600195, Aug. 2017.

- [35] K. Shubhakar *et al.*, "Study of preferential localized degradation and breakdown of HfO<sub>2</sub>/SiOx dielectric stacks at grain boundary sites of polycrystalline HfO<sub>2</sub> dielectrics," *Microelectron. Eng.*, vol. 109, pp. 364–369, Sep. 2013.

- [36] M. Porti, M. Nafria, and X. Aymerich, "Current limited stresses of SiO/sub 2/ gate oxides with conductive atomic force microscope," *IEEE Trans. Electron Devices*, vol. 50, no. 4, pp. 933–940, Apr. 2003.

- [37] Y. L. Wu, J. J. Lin, B. T. Chen, and C. Y. Huang, "Position-dependent nanoscale breakdown characteristics of thin silicon dioxide film subjected to mechanical strain," *IEEE Trans. Device Mater. Reliab.*, vol. 12, no. 1, pp. 158–165, 2012.

- [38] V. Yanev *et al.*, "Tunneling atomic-force microscopy as a highly sensitive mapping tool for the characterization of film morphology in thin high-k dielectrics," *Appl. Phys. Lett.*, vol. 92, no. 25, p. 252910, Jun. 2008.

- [39] U. Celano, Y. Yin Chen, D. J. Wouters, G. Groeseneken, M. Jurczak, and W. Vandervorst, "Filament observation in metal-oxide resistive switching devices," *Appl. Phys. Lett.*, vol. 102, no. 12, p. 121602, Mar. 2013.

- [40] K. Murakami *et al.*, "Current Voltage Characteristics through Grains and Grain Boundaries of High-k Dielectric Thin Films Measured by Tunneling Atomic Force Microscopy," in *AIP Conference Proceedings*, 2011, vol. 1395, pp. 134–138.

- [41] R. Kumar, D. Varandani, B.R.Mehta, "Nanoscale interface formation and charge transfer in graphene/silicon Schottky junctions; KPFM and CAFM studies", *Carbon*, vol. 98, pp. 41-49, 2015.

- [42] J.A. Kellar, J.M.P. Alaboson, Q. H. Wang, M.C. Hersam, "Identifying and characterizing epitaxial graphene domains on partially graphitized SiC(0001) surfaces using scanning probe microscopy", *Appl. Phys. Lett.*, vol. 96, p. 143103, 2010.

- [43] J. Li, J. Wu, Z. Huang, X. Qi, J. Zhong, "Local conductivity of graphene oxide study by conductive atomic force microscope", *J. Appl. Phys*, vol. 126, p. 215701, 2019.

- [44] F. Giannazzo, G. Greco, E. Schilirò, S. Di Franco, I. Deretzis, G. Nicotra, A. La Magna, F. Roccaforte, "Nanoscale electrical mapping of twodimensional materials by conductive atomic force microscopy for transistors applications", *AIP Conference Proceedings*, vol. 1990, p. 020008, 2018.

- [45] S. Claramunt, Q. Wu, A. Ruiz, M. Porti, C. Couso, M. Nafría, X. Aymerich, B. Sempere, C. Colominas, "Nanoscale electrical characterization of a varistor-like device fabricated with oxidized CVD graphene", 2017 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), 2017.

- [46] A. Reina *et al.*, "Transferring and Identification of Single- and Few-Layer Graphene on Arbitrary Substrates," *J. Phys. Chem. C*, vol. 112, no. 46, pp. 17741–17744, Nov. 2008.

- [47] J. Alvarez *et al.*, "Conductive-probe atomic force microscopy characterization of silicon nanowire," *Nanoscale Res. Lett.*, vol. 6, no. 1, p. 110, Dec. 2011.

- [48] J. D. Buron et al., "Graphene mobility mapping," Sci. Rep., vol. 5, no. 1, p. 12305, Dec. 2015.

- [49] A. S. Sokolov, Y.-R. Jeon, S. Kim, B. Ku, D. Lim, H. Han, M.G. Chae, J. Lee, B.G. Ha, C. Choi, "Influence of oxygen vacancies

- in ALD HfO<sub>2</sub>-x thin films on non-volatile resistive switching phenomena with a Ti/HfO<sub>2</sub>-x/Pt structure", *Appl. Surf. Sci.*, vol. 434, pp. 822-830, 2018.

- [50] G. Gonzalez-Cordero, F. Jimenez-Molinos, J.B. Roldan, M.B. Gonzalez, F. Campabadal, "In-depth study of the physics behind resistive switching in TiN/Ti/HfO<sub>2</sub>/W" structures", vol. 35, *J. Vac. Sci. Technol. B*, p. 01A110, 2017.

- [51] M. Porti, M. Nafría, M. C. Blüm, X. Aymerich, and S. Sadewasser, "Atomic force microscope topographical artifacts after the dielectric breakdown of ultrathin SiO<sub>2</sub> films," *Surf. Sci.*, vol. 532–535, pp. 727–731, Jun. 2003.

- [52] K. L. Pey *et al.*, "Breakdowns in high-k gate stacks of nano-scale CMOS devices," *Microelectron. Eng.*, vol. 80, no. SUPPL., pp. 353–361, Jun. 2005.

- [53] G. Iannaccone, F. Bonaccorso, L. Colombo, and G. Fiori, "Quantum engineering of transistors based on 2D materials heterostructures," *Nat. Nanotechnol.*, vol. 13, no. 3, pp. 183–191, Mar. 2018.