RESEARCH ARTICLE | JUNE 15 2021

## A study on free-standing 3C-SiC bipolar power diodes

Fan Li ➡; Arne Benjamin Renz; Amador Pérez-Tomás; ... et. al

Check for updates

Appl. Phys. Lett. 118, 242101 (2021)

https://doi.org/10.1063/5.0054433

CrossMark

### Articles You May Be Interested In

Dual role of 3C-SiC interlayer on DC and RF isolation of GaN/Si-based devices

Appl. Phys. Lett. (September 2022)

Vacancy-induced enhancement of electron-phonon coupling in cubic silicon carbide and its relationship to the two-temperature model

Journal of Applied Physics (September 2021)

Prospects for the commodity lending use in the process of the machine-tractor fleet modernization

AIP Conference Proceedings (December 2022)

scitation.org/journal/apl

# A study on free-standing 3C-SiC bipolar power diodes

Cite as: Appl. Phys. Lett. **118**, 242101 (2021); doi: 10.1063/5.0054433 Submitted: 18 April 2021 · Accepted: 31 May 2021 · Published Online: 15 June 2021

Fan Li,<sup>1,a)</sup> D Arne Benjamin Renz,<sup>1</sup> Amador Pérez-Tomás,<sup>2</sup> Vishal Shah,<sup>1</sup> Peter Gammon,<sup>1</sup> Francesco La Via,<sup>3</sup> Mike Jennings,<sup>4</sup> and Phil Mawby<sup>1</sup>

#### AFFILIATIONS

<sup>1</sup>School of Engineering, University of Warwick, Coventry CV4 7AL, United Kingdom

- <sup>2</sup>Catalan Institute of Nanoscience and Nanotechnology (ICN2), CSIC and The Barcelona Institute of Science and Technology, 08193 Barcelona, Spain

- <sup>3</sup>Consiglio Nazionale delle Ricerche-Instituto per la Microelettronica e Microsistemi (CNR-IMM), Strada VIII, n.5 Zona Industriale, 95121 Catania, Italy

<sup>4</sup>College of Engineering, Swansea University, Swansea SA1 8EN, United Kingdom

<sup>a)</sup>Author to whom correspondence should be addressed: fanlisemicon@gmail.com

#### ABSTRACT

A low p-n built-in potential (1.75 V) makes 3C-SiC an attractive choice for medium voltage bipolar or charge balanced devices. Until recently, most 3C-SiC had been grown on Si, and power device fabrication had, therefore, been hindered by issues, such as high defect density and limited processing temperature, while devices were necessarily limited to lateral structures. In this work, we present the fabrication and characterization of a vertical PiN diode using bulk 3C-SiC material. A p-type ohmic contact was obtained on Al implanted regions with a specific contact resistance  $\sim 10^{-3} \Omega$  cm<sup>2</sup>. The fabricated PiN diode has a low forward voltage drop of 2.7 V at 1000 A/cm<sup>2</sup>, and the on-off ratio at  $\pm 3$  V is as high as 10<sup>9</sup>. An ideality factor of 1.83–1.99 was achieved, and a blocking voltage of  $\sim 110$  V was observed using a single-zone junction termination design.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0054433

Wide bandgap (WBG) semiconductors are considered substrates for the next generation electronics, targeting high power and harsh environments that conventional Si devices struggle to meet. 4H-SiC is currently the most mature wide bandgap technology, available with a range of commercial unipolar diodes and transistors up to 1700 V. On the other hand, not as much work has been carried out on bipolar devices in SiC, <sup>1,2</sup> Ga<sub>2</sub>O<sub>3</sub>, <sup>3</sup> and diamond.<sup>4,5</sup> WBG bipolar power devices are far less developed compared with their unipolar counterparts, mainly due to the issues related to deep level acceptor activation, high p-n junction potentials, and low minority carrier lifetime. Due to its narrower bandgap Eg\_3C-SiC of 2.3 eV (at 300 K),<sup>6</sup> 3C-SiC has a lower p-n junction built-in potential ( $\sim$ 1.75 V) than 4H-SiC ( $\sim$ 3 V). It is shown in Ref. 7 that 3C-SiC PiN diodes rated up to 4.5 kV have a forward voltage drop at 250 A/cm<sup>2</sup> lower than 4H-SiC. Until recently, however, the need to use 3C-SiC grown on Si substrates has made power device fabrication difficult. This is due to the high defect density within these 3C-SiC epilayers,<sup>8,9</sup> and also due to the need to employ lateral architectures, in order to avoid the 3C-SiC/Si heterojunction. Low voltage lateral p-n junction diodes were previously demonstrated by forming implanted regions in 3C-SiC epilayers grown on Si substrates.<sup>10,11</sup> Furthermore, while there were several reports achieving p-type conduction in Al doped 3C-SiC epilayers,<sup>12–14</sup> it remains an obstacle for implanted layers, which is often required in edge termination and Junction Barrier Schottky designs. This is mainly due to the post-implantation anneal temperature, which is limited to the 1414 °C (melting point of Si), thus not sufficient to activate the deep level Al dopants. In Ref. 15, p-type conduction was realized after Al was implanted (200 keV,  $8 \times 10^{14}$  cm<sup>-2</sup>, peak doping  $\sim 5 \times 10^{19}$  cm<sup>-3</sup>) into 3C-SiC at high temperature (850 °C) followed by a 1400 °C postimplant anneal, although the activation rate was estimated to be as low as 1%. With lower temperature Al implantation (500 °C; 180/110/60/  $30 \text{ keV}, 11.2/7/5/2.7 \times 10^{14} \text{ cm}^{-2}$ , peak doping  $\sim 1 \times 10^{20} \text{ cm}^{-3}$ ) and anneal (1300 °C), it was shown that in Al implanted 3C-SiC layers, p-type conduction could only be achieved after a very long anneal (>317 h).<sup>16</sup> Studies on 3C-SiC growth methods in recent years led to a continuous reduction of defect density, and free-standing 3C-SiC wafers were demonstrated.<sup>17-21</sup> By removing the Si substrates (polish, etch, melt, etc.), the leftover 3C-SiC wafer not only keeps the large area

desired for lowering device costs, but also a higher processing temperature can be achieved. In addition, without the heterojunction, a vertical structure becomes possible, making the most of 3C-SiC in power device applications. In this work, by fabricating edge terminated, vertical power PiN diodes on bulk 3C-SiC wafers, both p-type conduction and high voltage (>100 V) p-n junction blocking is demonstrated.

To obtain the bulk 3C-SiC material used in this work, first, 150  $\mu$ m intentionally nitrogen doped (1 × 10<sup>18</sup> cm<sup>-3</sup>) n-type 3C-SiC was grown on Si(100) substrates via Chemical Vapor Deposition (CVD). Next, the chamber temperature was increased to 1750 °C to melt and remove the Si(100) substrate. Another  $10 \,\mu m$  thick nonintentionally doped ( $\sim 2.5 \times 10^{16} \text{ cm}^{-3}$ ) n-type 3C-SiC epilayer was then grown on the highly doped 3C-SiC substrate. More detailed information about the bulk 3C-SiC growth can be found in Refs. 21 and 22. TEM analysis suggested that the resulting stacking fault density of these homoepitaxial grown 3C-SiC layers is below 10<sup>3</sup> cm<sup>-1</sup>,<sup>22</sup> which is among the lowest values obtained using various techniques, including standard Si substrate, inverted silicon pyramids substrate, and lower temperature (1400 °C) homoepitaxy growth.<sup>18</sup> Polishing of the as-grown 3C-SiC surface was challenging due to the stress and bowing within the wafer<sup>23,24</sup> and, thus, was not carried out. By performing a tapping mode AFM scan in several  $10 \times 10 \,\mu\text{m}^2$  areas, rms surface roughness around 10 nm was observed.

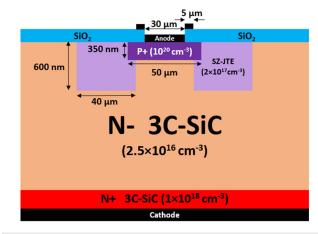

The PiN diode fabrication began with two box-profile Al implantations, both performed at 600 °C. First a 350 nm deep, highly doped  $(1 \times 10^{20} \text{ cm}^{-3}) \text{ p}^+$  anode region  $(180/100/40 \text{ keV}, 20/10/5 \times 10^{14} \text{ cm}^{-2})$ was formed. Second, a 600 nm deep, p-doped  $(2 \times 10^{17} \text{ cm}^{-3})$ Single-Zone Junction Termination Extension (SZ-JTE) region (500/ 350/250/150/80 keV,  $4.4/2.2/2.2/1.9/1.3 \times 10^{12}$  cm<sup>-2</sup>) was formed. Post-implantation anneals were performed at 1700 °C for 2 h in Ar, with the sample surface covered by a carbon cap, which was then removed by oxidation in dry O2 at 850 °C for 30 min. Following that, the samples went through standard RCA 1 and 2 cleaning procedures and were thermally oxidized in dry O2 at 1300 °C to form a thin SiO<sub>2</sub> layer ( $\approx$ 75 nm), which passivates the surface dangling bonds and isolates the devices. With the top surface protected by a layer of baked photoresist, the back side SiO<sub>2</sub> was removed by wet etch (HF), after which, a Ti/Ni (30/100 nm) bilayer was evaporated onto the n<sup>+</sup> substrate and annealed at 1000 °C for 1 min in Ar to form the cathode.<sup>25</sup> Via photolithography, the surface passivation SiO2 was selectively wet etched in diluted HF, and circular Ti/Al/Ni (30/100/50 nm) metal stacks with 40  $\mu$ m diameter were then evaporated and lifted-off as the anodes.<sup>12</sup> To form ohmic contact, the anodes went through a rapid thermal anneal at 1100 °C for 2 min in Ar. A cross-sectional view of the final device with a circular structure is shown in Fig. 1.

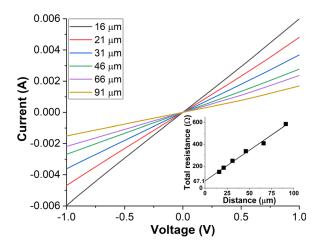

Transmission Line Method (TLM) structures were fabricated in the p<sup>+</sup> implanted regions, and their room temperature I–V characteristics are shown in Fig. 2. Ohmic behavior is observed, and the lowest specific contact resistance is ~9.7 × 10<sup>-4</sup>  $\Omega$  cm<sup>2</sup>. Not only is this among the lowest values recently reported for p-type 3C-SiC,<sup>12,16</sup> but also the post-implant anneal time is significantly reduced from >300 h to a more practical 2 h. However, the extracted specific contact resistance (10<sup>-4</sup>-10<sup>-2</sup>  $\Omega$  cm<sup>2</sup>) and sheet resistance (2500–15000  $\Omega$ /sq) values have a large distribution. This is most likely due to the rough surface previously mentioned and can be improved by optimizing the growing conditions and polishing methods.

FIG. 1. Schematic cross section view of the fabricated free-standing 3C-SiC PiN diode with Single Zone Junction Termination Extensions (SZ-JTEs).

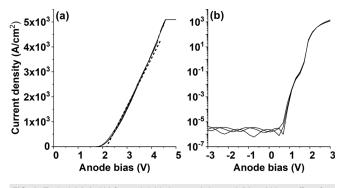

Typical room temperature forward J-V characteristics of the PiN diodes are shown in Fig. 3(a), and the built-in potential can be extracted from the intersection of forward current linear region fitting and the x-axis, which is just above 2 V, slightly higher than the theoretical value 1.75 V, but still 33% lower than the 3 V of typical 4H-SiC PiN diodes.<sup>1,2,26</sup> The current density goes above 1000 A/cm<sup>2</sup> at 2.7 V forward bias and hits the measurement compliance (5000 A/cm<sup>2</sup>) at  $\sim$ 4.5 V. Device self-heating is inevitable at such a high current density. At elevated temperatures, SiC carrier lifetime was found to increase exponentially, while the carrier mobility and diffusion coefficients decrease.<sup>27</sup> It was shown in Ref. 28 that significant degradation occurred to 4H-SiC PiN diodes above 1700 A/cm<sup>2</sup>, and a 9000 A/cm<sup>2</sup>, 8-ms pulse can heat the device to 2000-2300 K. Carrier transportation in SiC in extreme conditions, such as in this work, is not yet well understood and needs further investigations. The differential specific on-resistance is estimated to be  $\sim 0.5 \text{ m}\Omega \text{ cm}^2$ , and the on-off ratio at  $\pm 3$  V is greater than 10<sup>9</sup> as shown in Fig. 3(b).

FIG. 2. Room temperature I–V characterization of the p-type ohmic contact TLM and fitting of the total resistance.

FIG. 3. Typical (a) 0–5 V forward J–V characteristics and (b)  $\pm 3$  V on–off performance of PiN diodes at room temperature.

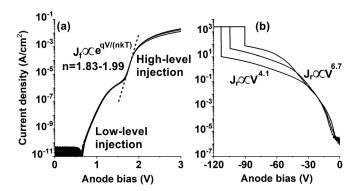

The built-in potential can be estimated from the second knee in the semi logarithmic graph [Fig. 4(a)], where the series resistance begins to dominate the forward conduction. A double-bump feature is consistently observed in the forward semi-log scale J–V curve [Fig. 4(a)]. This is usually due to an inhomogeneous interface,<sup>29,30</sup> which causes multiple current paths with different barrier heights, affecting the conduction mechanism. The diode ideality factor *n* can be extracted from the high-level injection region, and the typical values are 1.83–1.99, indicating the current transport is dominated by recombination. This latest result shows great improvements from literature, where either too large ( $n > 3^{31,32}$ ) or too small values ( $n \approx 1.5^{11}$ ) were observed. In the low-level injection region, ideality factors >2 were obtained this is most likely due to defect induced carrier recombination.<sup>33</sup>

At high reverse bias, the diodes suffer from a high leakage current density  $J_r$ , reaching 0.1 mA/cm<sup>2</sup> at -10 V as seen in Fig. 4(b).  $J_r$  does not follow a square root dependence (space-charge generation dominant) on the reverse bias. Instead,  $J_r \propto V^{\alpha}$ , where  $\alpha \approx 6.7$  from 0 to -50 V. The fast increasing leakage is most likely due to defect assisted tunneling. It is known that stacking faults are the main cause of the high leakage in 3C-SiC devices,<sup>34,35</sup> and in order to achieve a low  $J_r$  of  $\sim 0.1$  mA/cm<sup>2</sup> at -600 V, stacking fault density needs to be kept below 700 cm<sup>-1.9</sup> Also, the fact,  $J_r$  is above 0.1 mA/cm<sup>2</sup> at -10 V, means that self-heating cannot be neglected here, which can raise the leakage current level further.<sup>36</sup> Increasing the reverse bias further, the  $\alpha$  value drops to  $\sim 4.1$ . A maximum blocking voltage of  $\sim 110$  V was achieved

FIG. 4. Typical semi-log scale J–V characteristics of (a) forward and (b) reverse biased PiN diodes at room temperature.

[Fig. 4(b)]. Assuming a critical field for 3C-SiC of 1.4 MV/cm,<sup>37</sup> the theoretical 1D breakdown of the device is 210 V, occurring at a depletion region depth 3  $\mu$ m from the surface. These devices, therefore, achieve ~50% of the 1D theoretical value for this drift layer, further demonstrating the scope for improvement in the surface quality and termination.

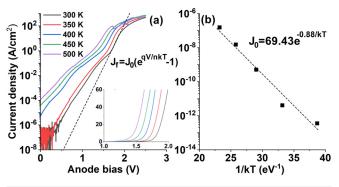

At elevated temperatures (300-500 K), the forward current density increases, and the built-in potential decreases as shown in Fig. 5(a), which is due to the increasing number of intrinsic carriers. As can be seen from the linear plot inset [Fig. 5(a)], at relatively low current density (<60 A/cm<sup>2</sup>), the forward J–V curves are parallel to each other, indicating a temperature independent differential resistance. Similar behavior was previously observed for 4H-SiC PiN diodes,<sup>36</sup> the result of compensation between an increase in carrier lifetime and a decrease in mobility and the diffusion coefficients. The low voltage (0 to -2 V) leakage current density increases significantly with increasing measurement temperature, from  $\sim 1 \times 10^{-7}$  A/cm<sup>2</sup> at 25 °C to  $\sim 1 \times 10^{-4}$  A/cm<sup>2</sup> at 225 °C. Despite the leakage being dominated by defect assisted tunneling, the thermally generated component, the saturation current density, J<sub>0</sub>, can be extracted from the high-level injection region [Fig. 5(a)], and the Arrhenius plot is shown in Fig. 5(b). The activation energy for the thermally generated leakage component is estimated to be ~0.88 eV, still lower than  $E_{g_{-3C-SiC}/2} \approx 1.15$  eV, in which case it is considered that carrier transportation is dominated by recombination. This is likely due to a tunneling contribution to the carrier transportation, which still cannot be neglected, even in the high-level injection ( $\sim 100 \text{ A/cm}^2$ ) regime, thus leading to a lower activation energy than expected.

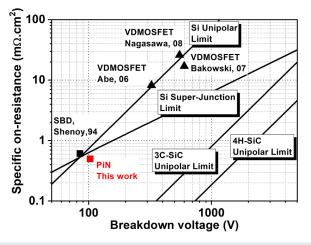

A figure of merit (FoM) graph of Si, 3C-SiC, and 4H-SiC for power device applications is shown in Fig. 6 with some literature data of 3C-SiC unipolar devices.<sup>14,38,40</sup> due to lack of bipolar device results. As can be seen, the PiN diode fabricated in this work currently betters both the Si unipolar and super-junction limits. Also, improvement over the 3C-SiC MOSFETs and Schottky Barrier Diode can be inferred, because as the voltage rating is scaled up, the rise in onresistance of these bipolar devices will be less than the unipolar devices. Furthermore, simple improvements can be made to these bulk 3C-SiC vertical PiN diodes to further improve this picture. Reducing the drift layer thickness to the maximum reverse depletion width (~3  $\mu$ m in this case) would have substantially lowered the onresistance. Furthermore, lowering the drift layer doping

FIG. 5. PiN diode (a) log scale forward J–V characteristics at 300–500 K and (b) the saturation current density  $J_0$  Arrhenius plot.

FIG. 6. Power device figure of merit graph for Si, 3C-SiC, and 4H-SiC, literature 3C-SiC devices parameters are provided.  $^{14,37-39}$

$(<1 \times 10^{16} \text{ cm}^{-3})$ , smoothing the surface, and improving upon the junction termination process (use of P-Ring, or trench terminations) would all result in an increased breakdown voltage. However, there remains an evident gap between current 3C-SiC power device performance and the 3C-SiC unipolar limit, which needs will be narrowed in the near future via follow-up studies on defect density reduction and device processing.

Vertical PiN diodes have been fabricated using Al implantation into bulk 3C-SiC material. Removal of the Si substrate made possible post-implantation annealing at 1700 °C, making the development of a p-type ohmic contact more practically realizable. The diodes showed good on-state performance, with a reasonable ideality factor of 1.83–1.99. Despite a very high on–off ratio ( $\sim$ 10<sup>9</sup>) at ±3 V, considerable defect assisted tunneling was observed at higher reverse bias. The thermally generated leakage component was found to be dominated by space charge generation, with an activation energy of  $\sim$ 0.88 eV. Limited by the defect density and surface roughness, the maximum blocking voltage reached in this work is  $\sim$ 110 V, but achieving 1000 A/cm<sup>2</sup> with a low forward voltage drop of 2.7 V demonstrates the potential of using 3C-SiC for PiN and Merged PiN Schottky power diodes applications.

This work was supported in part by the European Commission through the Challenge Project under Grant No. 720827.

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

- <sup>1</sup>C. A. Fisher, M. R. Jennings, Y. K. Sharma, D. P. Hamilton, P. M. Gammon, A. Pérez-Tomás, S. M. Thomas, S. E. Burrows, and P. A. Mawby, "Improved performance of 4H-SiC PiN diodes using a novel combined high temperature oxidation and annealing process," IEEE Trans. Semicond. Manuf. **27**(3), 443–451 (2014).

- <sup>2</sup>Y. Bu, H. Yoshimoto, N. Watanabe, and A. Shima, "Fabrication of 4H-SiC PiN diodes without bipolar degradation by improved device processes," J. Appl. Phys. **122**(24), 244504 (2017).

- <sup>3</sup>M. M. Islam, M. O. Liedke, D. Winarski, M. Butterling, A. Wagner, P. Hosemann, Y. Wang, B. Uberuaga, and F. A. Selim, "Chemical manipulation of hydrogen induced high p-type and n-type conductivity in Ga<sub>2</sub>O<sub>3</sub>," Sci. Rep. **10**(1), 6134 (2020).

- <sup>4</sup>M. Saremi, R. Hathwar, M. Dutta, F. A. Koeck, R. J. Nemanich, S. Chowdhury, and S. M. Goodnick, "Analysis of the reverse I-V characteristics of diamondbased PIN diodes," Appl. Phys. Lett. 111(4), 043507 (2017).

- <sup>5</sup>J. Holmes, M. Dutta, F. A. Koeck, M. Benipal, J. Brown, B. Fox, R. Hathwar, H. Johnson, M. Malakoutian, M. Saremi, A. Zaniewski, R. Alarcon, S. Chowdhury, S. M. Goodnick, and R. J. Nemanich, "A 4.5 μm PIN diamond diode for detecting slow neutrons," Nucl. Instrum. Methods Phys. Res. B 903, 297–301 (2018).

- <sup>6</sup>M. E. Levinshtein, S. L. Rumyantsev, and M. S. Shur, Properties of Advanced Semiconductor Materials: GaN, AIN, InN, BN, SiC, SiGe (John Wiley & Sons, 2001).

- <sup>7</sup>A. E. Arvanitopoulos, M. Antoniou, S. Perkins, M. Jennings, M. B. Guadas, K. N. Gyftakis, and N. Lophitis, "On the suitability of 3C-silicon carbide as an alternative to 4H-silicon carbide for power diodes," IEEE Trans. Ind. 55(4), 4080–4090 (2019).

- <sup>8</sup>F. Giannazzo, G. Greco, S. D. Franco, P. Fiorenza, I. Deretzis, A. La Magna, C. Bongiorno, M. Zimbone, F. L. Via, M. Zielinski, and F. Roccaforte, "Impact of stacking faults and domain boundaries on the electronic transport in cubic silicon carbide probed by conductive atomic force microscopy," Adv. Electron. Mater. 6(2), 1901171 (2020).

- <sup>9</sup>H. Nagasawa, T. Kawahara, K. Yagi, and N. Hatta, "Propagation of stacking faults in 3C-SiC," Mater. Sci. Forum **679–680**, 282–285 (2011).

- <sup>10</sup>K. Shibahara, T. Takeuchi, S. Nishino, and H. Matsunami, "Electrical properties of undoped and ion-implanted cubic SiC grown on Si(100) by chemical vapor deposition," Jpn. J. Appl. Phys., Part 1 28(8), 1341–1347 (1989).

- <sup>11</sup>R. Tyagi and T. P. Chow, "Self-enclosed vs. LOPOS-terminated lateral planar p<sup>+</sup>/n and n<sup>+</sup>/p junctions in 3C-SiC/Si," presented in 8th International Symposium on Power Semiconductor Devices and ICs (1996), pp. 115–118.

- <sup>12</sup>M. Spera, G. Greco, R. Lo Nigro, C. Bongiorno, F. Giannazzo, M. Zielinski, F. L. Via, and F. Roccaforte, "Ohmic contacts on n-type and p-type cubic silicon carbide (3C-SiC) grown on silicon," Mater. Sci. Semicond. Process. **93**, 295–298 (2019).

- <sup>13</sup>L. Wang, S. Dimitrijev, J. Han, P. Tanner, A. Iacopi, and L. Hold, "Demonstration of p-type 3C-SiC grown on 150 mm Si(100) substrates by atomic-layer epitaxy at 1000 °C," J. Cryst. Growth **329**(1), 67–70 (2011).

- <sup>14</sup>M. Abe, H. Nagasawa, P. Ericsson, H. Strömberg, M. Bakowski, and A. Schöner, "High current capability of 3C-SiC vertical DMOSFETs," Microelectron. Eng. 83(1), 24–26 (2006).

- <sup>15</sup>M. V. Rao and P. Griffths, "Al and B ion-implantations in 6H- and 3C-SiC," J. Appl. Phys. 77(6), 2479–2485 (1995).

- $^{16}$  R. Nipoti, M. Canino, M. Zielinski, F. Torregrosa, and A. Carnera, "1300 °C annealing of 1  $\times$  10<sup>20</sup> cm $^{-3}$  Al<sup>+</sup> ion implanted 3C-SiC/Si," ECS J. Solid State Sci. Technol. 8(9), P480–487 (2019).

- <sup>17</sup>N. Hatta, T. Kawahara, K. Yagi, H. Nagasawa, S. A. Reshanov, and A. Schöner, "Reliable method for eliminating stacking fault on 3C-SiC (001)," Mater. Sci. Forum **717–720**, 173–176 (2012).

- <sup>18</sup>F. L. Via, A. Severino, R. Anzalone, C. Bongiorno, G. Litrico, M. Mauceri, M. Schoeler, P. Schuh, and P. Wellmann, "From thin film to bulk 3C-SiC growth: Understanding the mechanism of defects reduction," Mater. Sci. Semicond. Process. **78**, 57–68 (2018).

- <sup>19</sup>G. Fisicaro, C. Bongiorno, I. Deretzis, F. Giannazzo, F. L. Via, F. Roccaforte, M. Zielinski, M. Zimbone, and A. L. Magna, "Genesis and evolution of extended defects: The role of evolving interface instabilities in cubic SiC," Appl. Phys. Rev. 7(2), 021402 (2020).

- <sup>20</sup>H. Nagasawa and K. Yagi, "3C-SiC single-crystal films grown on 6-inch Si substrates," Phys. Status Solidi B 202(1), 335–358 (1997).

- <sup>21</sup>F. L. Via, M. Mauceri, V. Scuderi, C. Calabretta, M. Zimbone, and R. Anzalone, "3C-SiC bulk growth: Effect of growth rate and doping on defects and stress," Mater. Sci. Forum **1004**, 120–125 (2020).

- <sup>22</sup>R. Anzalone, M. Zimbone, C. Calabretta, M. Mauceri, A. Alberti, R. Reitano, and F. L. Via, "Temperature investigation on 3C-SiC homo-epitaxy on fourinch wafers," <u>Materials</u> 12(20), 3293 (2019).

- <sup>23</sup>M. Zielinski, S. Ndiaye, T. Chassagne, S. Juillaguet, R. Lewandowska, M. Portail, A. Leycuras, and J. Camassel, "Strain and wafer curvature of 3C-SiC films on silicon: Influence of the growth conditions," Phys. Status Solidi A 204(4), 981–986 (2007).

- <sup>24</sup>B. E. Watts, G. Attolini, T. Besagni, M. Bosi, C. Ferrari, F. Rossi, F. Riesz, and L. D. Jiang, "Evaluation of curvature and stress in 3C-SiC grown on differently oriented Si substrates," Mater. Sci. Forum **679–680**, 137–140 (2011).

- <sup>25</sup>F. Li, Y. Sharma, V. Shah, M. Jennings, A. Pérez-Tomás, M. Myronov, C. Fisher, D. Leadley, and P. Mawby, "Electrical activation of nitrogen heavily implanted 3C-SiC(100)," Appl. Surf. Sci. 353, 958–963 (2015).

- <sup>26</sup>R. Singh, J. A. Cooper, M. R. Melloch, T. P. Chow, and J. W. Palmour, "SiC power Schottky and PiN diodes," IEEE Trans. Electron Devices **49**(4), 665–672 (2002).

- <sup>27</sup>P. Ivanov, M. Levinshtein, K. Irvine, O. Kordina, J. Palmour, S. Rumyantsev, and R. Singh, "High hole lifetime (3.8 μs) in 4H-SiC diodes with 5.5 kV block-ing voltage," Electron. Lett. **35**, 1382–1383 (1999).

- <sup>28</sup> M. E. Levinshtein, T. T. Mnatsakanov, P. A. Ivanov, J. W. Palmour, M. K. Das, and B. A. Hull, "Self-heating of 4H-SiC PiN diodes at high current densities," Mater. Sci. Forum **600–603**, 1007–1010 (2008).

- <sup>29</sup>G. Brezeanu, G. Pristavu, F. Draghici, M. Badila, and R. Pascu, "Characterization technique for inhomogeneous 4H-SiC Schottky contacts: A practical model for high temperature behavior," J. Appl. Phys. **122**(8), 084501 (2017).

- <sup>30</sup>P. M. Gammon, A. Perez-Tomas, V. A. Shah, O. Vavasour, E. Donchev, J. S. Pang, M. Myronov, C. A. Fisher, M. R. Jennings, D. R. Leadley, and P. A. Mawby, "Modelling the inhomogeneous SiC Schottky interface," J. Appl. Phys. 114(22), 223704 (2013).

- <sup>31</sup>K. Furukawa, A. Uemoto, M. Shigeta, A. Suzuki, and S. Nakajima, "3C-SiC p-n junction diodes," Appl. Phys. Lett. 48(22), 1536–1537 (1986).

- <sup>32</sup>P. G. Neudeck, D. J. Larkin, J. E. Starr, J. A. Powell, C. S. Salupo, and L. G. Matus, "Electrical properties of epitaxial 3C- and 6H-SiC p-n junction diodes produced side-by-side on 6H-SiC substrates," IEEE Trans. Electron Devices 41(5), 826–835 (1994).

- <sup>33</sup>N. A. Modine, A. M. Armstrong, M. H. Crawford, and W. W. Chow, "Highly nonlinear defect-induced carrier recombination rates in semiconductors," J. Appl. Phys. **114**(14), 144502 (2013).

- <sup>34</sup>A. Boulle, D. Chaussende, L. Latu-Romain, F. Conchon, O. Masson, and R. Guinebretière, "X-ray diffuse scattering from stacking faults in thick 3C-SiC single crystals," Appl. Phys. Lett. **89**(9), 091902 (2006).

- <sup>35</sup>K. Yagi, T. Kawahara, N. Hatta, and H. Nagasawa, "Switch-back epitaxy' as a novel technique for reducing stacking faults in 3C-SiC," Mater. Sci. Forum 527-529, 291–294 (2006).

- <sup>36</sup>M. E. Levinshtein, P. A. Ivanov, M. S. Boltovets, V. A. Krivutsa, J. W. Palmour, M. K. Das, and B. A. Hull, "High-temperature (up to 773K) operation of 6 kV 4H-SiC junction diodes," Solid State Electron. **49**(7), 1228–1232 (2005).

- <sup>37</sup>T. Kimoto and J. A. Cooper, "Appendix C: Major Physical Properties of Common SiC Polytypes," in *Fundamentals of Silicon Carbide Technology* (John Wiley & Sons Singapore Pte. Ltd, 2014), pp. 521–524.

- <sup>38</sup>H. Nagasawa, M. Abe, K. Yagi, T. Kawahara, and N. Hatta, "Fabrication of high performance 3C-SiC vertical MOSFETs by reducing planar defects," Phys. Status Solidi B 245(7), 1272–1280 (2008).

- <sup>39</sup>M. Bakowski, A. Schöner, P. Ericsson, H. Strömberg, H. Nagasawa, and M. Abe, "Development of 3C-SiC MOSFETs," J. Telecommun. Inf. Technol. 2, 49–56 (2007), available at http://yadda.icm.edu.pl/yadda/element/bwmeta1.element.baztech-article-BAT8-0008-0010.

- <sup>40</sup>P. Shenoy, A. Moki, B. J. Baliga, D. Alok, K. Wongchotigul, and M. Spencer, "Vertical Schottky barrier diodes on 3C-SiC grown on Si," in IEEE International Electron Devices Meeting (1994), Paper No. 4891443.