Contents lists available at ScienceDirect

# Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# On the role of power dissipation in the Post-BD behavior of FDSOI NanoWire FETs<sup>☆</sup>

R. Goyal \*0, A. Crespo-Yepes, M. Porti, R. Rodriguez, M. Nafria

Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona (UAB) 08193, Bellaterra, Barcelona, Spain

#### ARTICLE INFO

Handling Editor: Francisco F. Gamiz

Keywords:

Aging

FDSOI

Nanowire

High-k

Reliability

Dielectric breakdown

#### ABSTRACT

Dielectric Breakdown, which has been associated with the progressive wear-out of the gate dielectric, has been one of the most detrimental failure mechanisms in CMOS devices. With downscaling, new device architectures and/or materials have been introduced, so, it is necessary to evaluate the BD impact at device (and circuit) level in these new structures. In this work, the dielectric BD and the post-BD behavior in largely scaled FDSOI nanowire transistors with high-k gate dielectric have been characterized, using the energy and the power dissipated by the device under test as key parameters. The experimental results evidence the presence of new detrimental effects for the device's integrity beyond the traditional dielectric BD.

### 1. Introduction

In CMOS technologies, dielectric breakdown (BD) of the gate oxide has been one of the most important reliability concerns because of its impact on the gate stack conduction, which can lead to the final device failure [1-7] and damage the circuit functionality. [8-10]. During the last decades, BD (i.e., Soft, Progressive and Hard BD [11-13]) has been widely studied in planar bulk MOSFETs with SiO2 and Hf-based high-k gate dielectrics [4-6,13], also the post BD conduction and the observation of the BD reversibility under specific stress conditions [14-16]. Additionally, Ultimate Nanowire (NW) transistors on Fully Depleted Silicon-On-Insulator (FDSOI) also experience the dielectric BD, with negative consequences on the circuit functionality. However, the impact of the device architecture (i.e., Buried Oxide (BOX) under the active area, channel confinement...), if any, on the BD and post-BD performance of the device have not been comprehensively analysed yet. In this work, the BD and post-BD behaviour of NW FDSOI MOSFETs with high-k gate dielectric have been characterised, using as key parameters the energy and the power dissipated by the device.

## 2. Device and experimental procedure

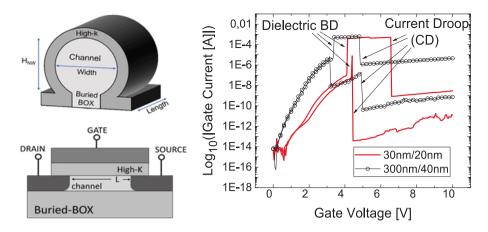

The studied devices were nMOS and pMOS FDSOI MOSFET transistors fabricated at CEA-LETI, with high-k  $\Omega$ -gate (HfSiON/TiN with EOT

=1.3 nm and  $H_{\rm NW}=11$  nm) and nanowire architecture (NW-FET) [17]. The buried oxide (BOX) thickness is 145 nm. Fig. 1 (left) shows the 3D sketch and the cross-section of a single device. Devices with two different widths were studied: (1) W = 30 nm (1-channel) with lengths ranging from 20 nm to 1000 nm, and (2)  $W_{\rm eff}=300$  nm (split in 10-channels of W = 30 nm) with two lengths, 20 and 40 nm. Ramped voltage stresses (RVS) were applied to the gate terminal (from 0 V to  $|10\ V|$ , with the rest of the terminals grounded) to induce the oxide wear out and to provoke the dielectric BD. Approximately, 300 transistors have been measured which allow the statistical analysis of the BD and CD events. But only those devices in which the BD and CD are triggered are used in this study. The applied voltage and the current through the gate were registered during the experiments, together with the sampling time used during the RVS, to calculate the dissipated power and energy before/after the BD.

## 3. Results and discussion

Fig. 1(right) shows different examples of  $I_G$ - $V_G$  curves measured during the RVS. In these devices, after the typical BD-related current increase, a new event can be triggered, observed as a large and sudden current drop (which from now on will be named as CD), always measured at larger voltages than BD. In many cases, the BD and CD events are clearly distinguishable. However, in some cases, CD is

E-mail address: rishab.goyal@autonoma.cat (R. Goyal).

https://doi.org/10.1016/j.sse.2025.109228

$<sup>^{\</sup>star}$  This article is part of a special issue entitled: 'EuroSOI-ULIS 2025' published in Solid State Electronics.

<sup>\*</sup> Corresponding author.

Fig. 1. (left-top) 3D sketch of the  $\Omega$ -Gate NW FD-SOI transistors (left-bottom) Transistor cross-section [17]. (right) Examples of typical  $I_G$ -V $_G$  curves measured during the RVS applied to the gate terminal to provoke the BD in nMOS FDSOI transistors with W/L = 30 nm/20 nm (lines) and W/L = 300 nm/40 nm (circles).

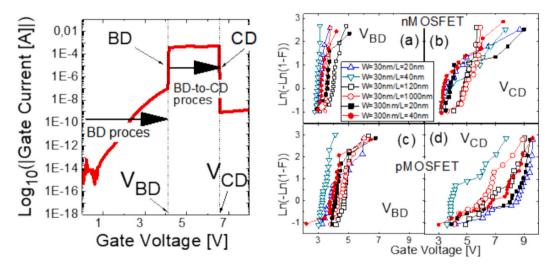

Fig. 2. (left) Definition of the parameters used in this work. (right) Weibull distributions of  $V_{BD}$  (a and c), and  $V_{CD}$  (b and d), for nMOS (top) and pMOS transistors (bottom) of different lengths and 1-channel (W = 30 nm, open symbols) and 10-channel (W = 300 nm, solid symbols) architectures.

immediately triggered after the BD, so that the equipment (Keithley 4200) is not able to register the BD, and only the CD is measured. Such behaviour was observed in all the studied devices, nMOS or pMOS, and single or 10-channel devices, though with a large dispersion in the associated voltages and currents. BD of the gate oxide has been extensively studied in bulk devices, and no relevant differences could be expected in these FDSOI transistors. However, CD events, since unique of these technologies, must be further investigated.

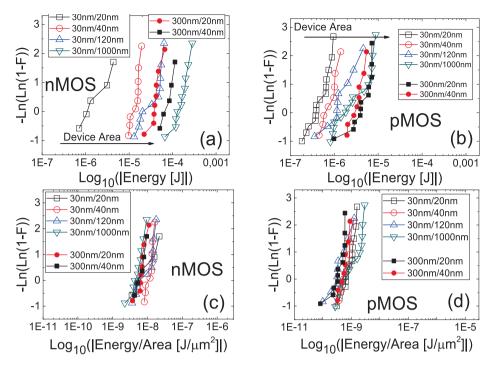

Fig. 2(left) shows the definition of the BD and CD related parameters, such as  $V_{BD}/V_{CD}$ , the BD process voltage region (i.e. from 0 V to  $V_{BD}$ ) and the BD-to-CD process region (from V<sub>BD</sub> to V<sub>CD</sub>). Fig. 2(right) shows the V<sub>BD</sub> and V<sub>CD</sub> statistical distributions, for nMOS and pMOS with different areas. As expected, the V<sub>BD</sub> distributions depend on the device area and device type (n-type or p-type transistor), while those of V<sub>CD</sub> do not, due to the local nature of the post-BD conduction, for all device types. In addition, V<sub>CD</sub> distributions are broader than those of V<sub>BD</sub> because of the random nature of the conductive filament after the BD that is controlling the device conductivity. Since energy dissipation plays a key role in the gate BD and self-heating is a critical issue in channel-confined technologies [18], the energy-to-BD (i.e., from 0 V-to-V<sub>BD</sub>), E<sub>BD</sub>, and the energyto-CD (from V<sub>BD</sub>-to-V<sub>CD</sub>), E<sub>CD</sub>, together with the power dissipated at the moment that BD and CD are triggered (i.e., at V<sub>BD</sub> and V<sub>CD</sub>), have been computed and statistically analyzed to get more insights on the origin of the CD and on the conditions that trigger this failure mode. Note that only devices on which both BD and CD are clearly measured (around 140 out of the 300) are included in the analysis (Figs. 3, 4 and 5). Fig. 3 shows the energy- to-BD (Fig. 3 a and b) and this energy normalized to the device area (Fig. 3 c and d). Note that, since the number of devices (20) per type and dimensions is the same, the number of points plotted in the distributions indicates the probability of the occurrence of the BD and CD events. As observed in Fig. 3,  $E_{\rm BD}$  is area dependent for both device types (Fig. 3 a and b) but larger for the nMOS. Interestingly, the normalized distributions have large slopes (i.e. low dispersion) and, independently of the device type or architecture, the energy values are concentrated in an energy decade (Fig. 3 c and d). Therefore, as for bulk devices, the dissipated energy also plays a key role in the BD of these FDSOI technologies.

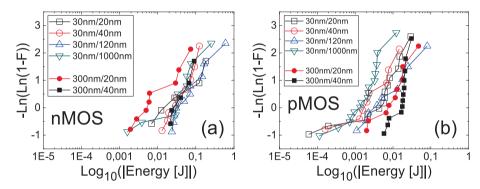

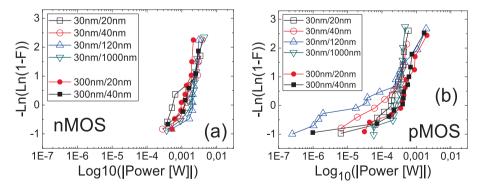

In contrast to the BD, the  $E_{CD}$  distributions of the BD-to-CD process (Fig. 4) are not area dependent, as reasonably expected, because of the extremely local nature of the BD phenomenon. The  $E_{CD}$  values are larger for the nMOS transistors as compared to the pMOS transistors because the energy values exhibit larger dispersion. The smaller slopes of  $E_{CD}$  suggest that this parameter is not as well-suited to characterize the CD event as it is for the BD. Therefore, power consumption at the CD event,  $P_{CD}$ , (Fig. 5) has been evaluated, for both nMOS and pMOS transistors (Fig. 5 a and b, respectively). As can be observed, for both device types, the distributions of  $P_{CD}$  are also independent of the device area. However, some differences have been observed in nMOS and pMOS devices.

Fig. 3.  $E_{BD}$  (top) and  $E_{BD}$  normalized to device area (bottom) in nMOS (a and c) and pMOS (b and d) transistors.

Fig. 4. Energy-to-CD (i.e. from  $V_{BD}$  to  $V_{CD}$ ) in nMOS (a) and pMOS (b) FDSOI transistors.

Fig. 5. Power dissipated at the CD event (i.e., at  $V_{\text{CD}}$ ) for nMOS (a) and pMOS (b) transistors.

For the nMOS transistors, the values of  $P_{CD}$  are larger (with a maximum of  $\sim 3$ mW, compared to  $\sim 1$ mW for the pMOS) and exhibit low dispersion with almost monomodal distributions (as observed for  $E_{BD}$  in Fig. 3). However, for the pMOS, bimodal distributions seem to be observed, suggesting that two mechanisms can lead to the CD event. Note, however, that the mode observed at larger  $P_{CD}$  appears to be like

that observed in the nMOS, suggesting the presence of an intrinsic CD mode (in nMOS and pMOS) and an extrinsic mode (mostly observed in pMOS). Therefore, opposite to the mechanism that controls the BD (i.e. wear out), which is an area dependent and cumulative process related to the dissipated energy in the device (Fig. 3), the CD is driven by a local and instantaneous process, probably linked to the power dissipation in

the device after the BD.

#### 4. Conclusions

The BD and CD phenomenology in high-K  $\Omega$ -shape NW FD-SOI transistors have been statistically analyzed, using the power consumption at BD and CD and the dissipated energy to BD and to CD as parameters. The results show that, as for bulk technologies, BD is a cumulative process that depends on the device area, associated with the oxide wear out consequence of the energy dissipation. However, the CD, solely observed in these FDSOI technologies, is driven by the local conduction of the BD path and triggered when a certain amount of power has been dissipated, probably related to the power dissipation capability of the Buried Oxide (BOX).

#### CRediT authorship contribution statement

R. Goyal: Writing – review & editing, Writing – original draft, Validation, Supervision, Methodology. A. Crespo-Yepes: Writing – review & editing, Writing – original draft, Validation, Supervision, Methodology. M. Porti: Writing – original draft. R. Rodriguez: Writing – review & editing, Writing – original draft, Validation, Supervision, Methodology. M. Nafria: Writing – original draft.

## Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Acknowledgments

This work was supported by Grant PID2022-136949OB-C22 funded by MCIN/AEI/10.13039/501100011033/ FEDER, UE, and 2021-SGR-00199. EU ASCENT project is acknowledged for sample provision.

## Data availability

No data was used for the research described in the article.

### References

[1] Degraeve R, Groeseneken G, Bellens R, Ogier JL, Depas M, Roussel PJ, et al. New insights in the relation between electron trap generation and the statistical

- properties of oxide breakdown. IEEE Trans Electron Devices Apr. 1998;45(4): 904–11. https://doi.org/10.1109/16.662800.

- [2] Linder BP, Lombardo S, Stathis JH, Vayshenker A, Frank DJ. Voltage dependence of hard breakdown growth and the reliability implication in thin dielectrics. IEEE Electron Device Lett Nov 2002;23:661–3. https://doi.org/10.1109/ LED.2002.805010.

- [3] Stathis JH. Impact of ultrathin oxide breakdown on circuits. Integrated Circuit Design and Technology Conference May 2005. https://doi.org/10.1109/ ICICDT.2005.1502607.

- [4] Choi JH, Mao Y, Chang JP. Development of hafnium based high-k materials-a review. Mater Sci Eng, R July 2011;72(6):97–136. https://doi.org/10.1016/j. mser 2010 12 001

- [5] Ribes G, Mitard J, Denais M, Bruyere S, Monsieur F, Parthasarathy C, et al. Review on High-k Dielectrics Reliability Issues. IEEE Trans Device Mater Reliab Mar. 2005; 5:5–19. https://doi.org/10.1109/TDMR.20 05. 8 45236.

- [6] Porti M, Nafría M, Aymerich X. New insights on the post-BD conduction of MOS devices at the nanoscale. IEEE Electron Device Lett Jan 2005;26:109–11. https:// doi.org/10.1109/LED.2004.841190.

- [7] Wu EY, Suñe J. "Recent advances in dielectric breakdown of modern gate dielectrics," in Integrated Reliability Workshop Final Report (IRW). 2013 IEEE International, Oct 2013:5–10. https://doi.org/10.1109/IIRW.2013.6804141.

- [8] Rodriguez R, Stathis JH, Linder BP, Kowalczyk S, Chuang CT, Joshi RV, et al. The impact of gate-oxide breakdown on SRAM stability. IEEE Electron Device Lett Sep. 2002;23(9):559–61. https://doi.org/10.1109/LED.2002.802600.

- [9] B. Kaczer, R. Degraeve, Ph. Roussel, and G. Groeseneken, Gate oxide breakdown in FET devices and circuits: From nanoscale physics to system-level reliability,' Microelectronics Reliability, vol. 47, pp. 559-566, Apr-May 2007. doi.org/ 10.1016/j.microrel.2007.01.063.

- [10] Fernandez R, Martin-Martinez J, Rodriguez R, Nafria M, Aymerich X. Gate Oxide Wear-out and Breakdown effects on the performance of analog and digital circuits,. IEEE Trans Electron Devices May 2008;55(4):997–1004. https://doi.org/10.1109/ TFD 2008 917334

- [11] Depas M, Nigam T, Heyns M. Soft breakdown of ultra-thin gate oxide layers. IEEE Trans Electron Devices Sep 1996;43(9):1499–504. https://doi.org/10.1109/ 16.538341

- [12] Tsujikawa S, Kanno M, Nagashima N. Reliable assessment of progressive breakdown in ultrathin MOS gate oxides towards accurate TDDB evaluation. IEEE Transaction on Electron Devices Mar 2011;58(5):1468–75. https://doi.org/ 10.1109/TED.2011.2114349.

- [13] Avella A, Krautschneider WH. Impact of Soft and Hard Breakdown on analog and digital circuits. IEEE Trans Device Mater Reliab Dec 2004;4(4):676–80. https:// doi.org/10.1109/TDMR.2004.836729.

- [14] Nafria M, Suñe J, Aymerich X. Exploratory observations of post-breakdown conduction in polycrystalline-silicon and metal-gate thin-oxide metal-oxidesemiconductor capacitors. Journal Applied Physics Jan 1993;73:205–15.

- [15] A. Crespo-Yepes, J. Martin-Martinez, R. Rodriguez, M. Nafria, X. Aymerich, 'Reversible dielectric breakdown in ultrathin Hf based high-k stacks under currentlimited stresses,' Microelectronics Reliability, vol. 49, issue 9-11, pp. 1024-1028, Sep-Nov 2009.

- [16] W. H. Liu, K. L. Pey, X. Li, M. Bosman, 'Observation of switching behaviors in post-breakdown conduction in NiSi-gated stacks,' IEEE International Electron Devices Meeting, pp. 135-138, Mar 2010, DOI 10.1109/IEDM.2009.5424402.

- [17] Almeida LM, Agopian PGD, Martino JA, Barraud S, Vinet M, Faynot O, et al. CEA-LETI. DOI Jan 2017. https://doi.org/10.1109/S3S.2016.7804394.

- [18] Zhao Y, Qu Y. Impact of self-heating effect on transistor characterization and reliability issues in sub-10nm technology nodes. IEEE J Electron Devices Soc 2019; 7:829–36. https://doi.org/10.1109/JEDS.2019.2911085.