This is the **accepted version** of the book part:

Saraza-Canflanca, Pablo; Camacho-Ruiz, Eros; Castro-Lopez, R.; [et al.]. «Simulating the impact of random telegraph noise on integrated circuits». A: SMACD/PRIME 2021. (2021), p. 1-4. 4 pàg. VDE Verlag GmbH.

This version is available at https://ddd.uab.cat/record/291204  $\,$

under the terms of the  $\textcircled{O}^{\texttt{N}}_{\texttt{COPYRIGHT}}$  license

# Simulating the impact of Random Telegraph Noise on integrated circuits

P. Saraza-Canflanca<sup>1</sup>, E. Camacho-Ruiz<sup>1</sup>, R. Castro-Lopez<sup>1</sup>, E. Roca<sup>1</sup> J. Martin-Martínez<sup>2</sup>, R. Rodriguez<sup>2</sup>, M. Nafria<sup>2</sup> and F.V. Fernandez<sup>1</sup>

<sup>1</sup>Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC/Universidad de Sevilla), Sevilla, Spain <sup>2</sup>Electronic Engineering Department (REDEC) group, Universitat Autònoma de Barcelona (UAB) Barcelona, Spain

*Abstract*— This paper addresses the statistical simulation of integrated circuits affected by Random Telegraph Noise (RTN). For that, the statistical distributions of the parameters of a defectcentric model for RTN are experimentally determined from a purposely designed integrated circuit with CMOS transistor arrays. Then, these distribution functions are used in a statistical simulation methodology that, taking into account transistor sizes, biasing conditions and time, can assess the impact of RTN in the performance of an integrated circuit. Simulation results of a simple circuit are shown together with experimental measurements of a circuit with the same characteristics implemented in the same CMOS technology.

#### Keywords—RTN, CMOS, Simulation, Transistor, Characterization

#### I. INTRODUCTION

Random Telegraph Noise (RTN) has become a subject of increasing concern in deeply-scaled CMOS technologies [1], due to its role as a source of device and circuit performance variability [2], [3]. At device level, RTN is observed as random and sudden discrete jumps of the drain current, which are caused by threshold voltage shifts associated to stochastic charge trapping/de-trapping events in/from device defects [4]. The impact of RTN has been reported for a wide variety of circuits, such as SRAMs or Ring Oscillators [3].

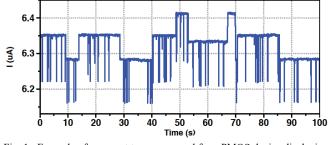

Fig. 1 shows an example of a current trace measured on a PMOS transistor with  $|V_{gs}| = 1.0V$  and  $|V_{ds}| = 0.1V$  clearly showing the RTN effect. The parameters that characterize the RTN phenomenon are the number of defects in the transistor, the amplitude of the current shifts (or, analogously, the amplitude of the threshold voltage shifts) associated to each of these defects, and their time constants, which may depend on the bias and temperature conditions. These time constants are the capture time ( $\tau_c$ ), i.e., the average time that an empty defect takes to capture a charge carrier, and the emission time ( $\tau_e$ ), i.e.,

Fig. 1. Example of a current trace measured for a PMOS device displaying RTN-induced current shifts.

This work was supported in part by the VIGILANT Project (PID2019-103869RB / AEI / 10.13039/501100011033). Pablo Sarazá Canflanca also acknowledges MICINN for supporting his research activity through the predoctoral grant BES-2017-080160.

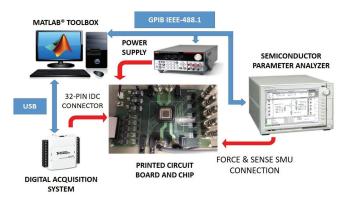

the average time that an occupied defect takes to emit the charge carrier. All of these are stochastic parameters that can be modeled by distribution functions; hence, the impact of RTN on circuit performances must be studied statistically. To obtain the characteristic parameters of such distribution functions, an integrated circuit containing thousands of devices was designed on a 65-nm CMOS technology [5] and characterized with the experimental setup [6] shown in Fig. 2.

This paper presents the complete methodology for statistical simulation of RTN effects. To that end, Section II presents the distribution functions used. Section III presents the simulation methodology and Section IV shows the experimental results on a practical circuit.

# II. RTN CHARACTERIZATION

The experimental setup allows to obtain thousands of current traces under different biasing and temperature conditions. From the current traces, the TiDeVa tool [7], [8], identifies the current levels by applying a maximum likelihood estimation (MLE)-based method. From the current levels, the number of defects, their associated current shifts, and the times at which captures and emissions take place can be identified [7].

These data must be modelled with a mathematical formulation that can be exploited for circuit simulation. The characteristic parameters of RTN are random variables, and, therefore, they are modeled with probability distribution functions.

# A. Distribution of the number of defects

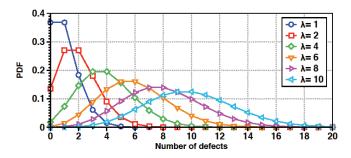

Frequently, the number of defects in a transistor has been modeled as a Poisson distribution [9], [10]. A discrete random

Fig. 2. Schematic representation of the experimental setup used in this work.

Fig. 3. Examples of Poisson distribution for several values of the mean number of defects  $\lambda$ .

variable *X* is said to have a Poisson distribution with parameter  $\lambda$  ( $\lambda \in \mathbb{R}$ ,  $\lambda \ge 0$ ) if the probability mass function of *X* follows:

$$f(k;\lambda) = \Pr(X=k) = \frac{\lambda^k e^{-\lambda}}{k!}$$

(1)

For the RTN problem, this probability mass function represents the probability that, for transistors having an average number of defects  $\lambda$ , a given transistor contains exactly k defects. The equation can be easily adapted if instead of the average number of defects in the device, the average density of defects in the technology is considered:

$$\Pr(k \text{ defects in device}) = \frac{(\lambda A)^k e^{-\lambda A}}{k!}$$

(2)

where A is the device area and  $\lambda$  is now the average number of defects per unit area (defect density). Fig. 3 shows some examples of a Poisson distribution for several values of  $\lambda$ .

#### B. Distribution of the capture and emission times

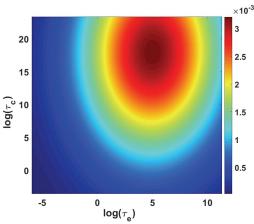

The joint probability density function of the emission and capture times is formulated as a bivariate log-normal function [4],[11]:

$$P_{def}(\tau_{e},\tau_{c}) = \frac{1}{\tau_{e}\tau_{c}2\pi\sigma_{\tau_{e}}\sigma_{\tau_{c}}\sqrt{1-\rho^{2}}}.$$

$$= \frac{1}{\tau_{e}\tau_{c}^{2}\pi\sigma_{\tau_{e}}\sigma_{\tau_{c}}\sqrt{1-\rho^{2}}} \frac{\left[\left(1\tau_{e}-\mu_{\tau_{e}}\right)^{2}+\left(1\tau_{c}-\mu_{\tau_{c}}\right)^{2}+2\rho\left(1\tau_{e}-\mu_{\tau_{e}}\right)\left(1\tau_{c}-\mu_{\tau_{c}}\right)\right]}{\sigma_{\tau_{e}}^{2}}$$

(3)

where  $l\tau_e = \log(\tau_e)$  and  $l\tau_c = \log(\tau_c)$ ,  $\mu_{\tau_e}$  and  $\mu_{\tau_c}$  are the mean value of the emission and capture times,  $\sigma_{\tau_e}$  and  $\sigma_{\tau_c}$  are their standard deviations and  $\rho$  is the correlation coefficient. Distribution parameters are fitted to match the capture and emission events observed experimentally, resulting in the plot of Fig. 4.

It must be remarked that emission and capture times in (3) are in fact mean values of random variables corresponding to the real time at which particular emission or capture events occur. The emission and capture events are commonly modeled by a Markov process, yielding the probability that a defect with emission/capture time  $\tau$  is emitted/captured at time instant t as:

Fig. 4. Bivariate log-normal distribution of capture and emission times.

$$P(t) = \frac{1}{\tau} e^{-t/\tau} \tag{4}$$

# C. Distribution of the threshold voltage and current shifts

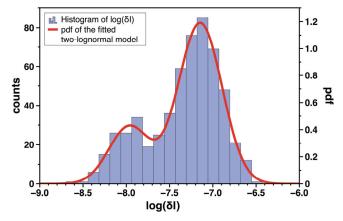

The current shifts are extracted from the RTN current traces. Fig. 5 shows the histogram of the current shifts for 400 PMOS devices with W/L = 80nm/60nm for  $|V_{gs}| = 1.0V$  and  $|V_{ds}| = 0.1V$ . It can be concluded that a two-lognormal seems a good approximation for the current shifts  $\delta I$ :

$$f(\delta I) = \frac{R}{\delta I \sqrt{2\pi}\sigma_l} e^{-\frac{(\log(\delta I) - \mu_l)^2}{\sigma_l^2}} + \frac{(1-R)}{\delta I \sqrt{2\pi}\sigma_u} e^{-\frac{(\log(\delta I) - \mu_u)^2}{\sigma_u^2}}$$

(5)

where  $\mu_l$ ,  $\mu_u$ ,  $\sigma_l$  and  $\sigma_u$ , represent the mean and standard deviation of the lower and upper lognormal distribution and *R* represents the relative amplitude of both distributions.

Fitting the two-lognormal distribution in (5) to the experimental results in Fig. 5 yields the associated distribution function, displayed in red. Equivalently, a similar fitting process can be performed for the threshold voltage shift distribution.

Fig. 5. Histogram of the experimentally extracted amplitudes for the RTNinduced current shifts (in blue), together with their associated pdf (in red).

# **III. SIMULATION METHODOLOGY**

Once the probability density functions that govern RTN defects are established, a methodology to simulate circuits can be developed. Charge capture and emission in/from defects induce changes in the threshold voltages of the transistors and, hence, shifts of their drain current along time. As circuit simulators can obtain the drain current from a given threshold voltage (and operating conditions) modeling the shifts of the latter ones will enable obtaining the changes of the former ones.

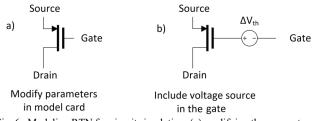

Basically there are two possible approaches to incorporate this threshold voltage variation into circuit simulation [12]. The first one is to incorporate such variations into the transistor model, and the second one is to modify the circuit netlist to add a controlled voltage source to each transistor gate to model the threshold voltage shift, as illustrated in Fig. 6. Both approaches have benefits and downsides but the RTN mathematical framework shown before can be used with either approach. In the examples shown below, however, the circuit netlist modification approach has been used.

Being RTN a stochastic effect, circuit simulations should be also statistical (e.g., Monte-Carlo simulations). For that, hundreds or thousands of instances like that in Fig. 6(b) must be generated. The generation of instances in the form of a transient voltage along a certain simulation time  $T_{sim}$  proceeds through the following steps for each device:

**Step 1:** Generate the number of defects  $N_{def}$  for this device according to Poisson distribution. A simple algorithm to generate samples of this distribution can be found in [13]. If  $N_{def} = 0$ , the process is completed for this device.

**Step 2:** Generate emission  $\tau_e$  and capture time  $\tau_c$  of each defect according to the bivariate lognormal distribution in (3).

**Step 3:** Generate a sample of the associated threshold voltage shift  $\Delta V_{th}$  for that defect. The governing probability density function, analogous to that for current shifts in eq. (5), can be efficiently sampled by: (1) deciding if the first or the second term in (5) becomes active by comparing the relative amplitude *R* with a sample of the commonly available uniform distribution; and (2) generating a sample of the selected lognormal distribution by applying the Box-Muller method using also two samples of uniform distributions [14].

Step 4: Generate the initial state (t = 0) of each defect

Fig. 6. Modeling RTN for circuit simulation: (a) modifying the parameters of the model card; (b) including a voltage source at the transistor gate.

according to the occupation probability:  $P_{occ} = \frac{\tau_e}{\tau_e + \tau_c}$

**Step 5:** If the defect is occupied (empty), generate a sample of the time instant  $t_{ec}$  in which the charge will be emitted/captured. The probability, as given in (4), uses the time in the decimal scale. As the defects have been sampled from a bivariate log-normal distribution, it is necessary to transform (4) to logarithmic scale:

$$P(t) = \frac{t}{\tau} e^{-t/\tau} \tag{6}$$

The probability density function in (6) can be efficiently sampled by generating its cumulative density function and selecting a sample from a uniform distribution.

**Step 6:** Increase t by  $t_{ec}$ . Increase (decrease) threshold voltage shift at time t by  $\Delta V_{th}$  if the defect has been captured (emitted).

**Step 7:** If  $t < T_{sim}$  go to Step 5.

**Step 8:** Increase defect counter *n*. If  $n \le N_{def}$  go to Step 2.

**Step 9:** Sort the times  $t_{ec}$  corresponding to emission and capture events of all defects, and calculate the time evolution of their combined threshold voltage shift.

### IV. SIMULATION AND EXPERIMENTAL RESULTS

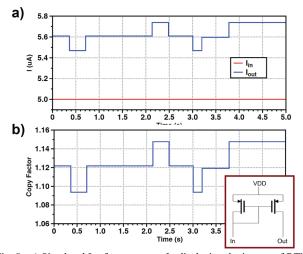

The methodology in Section III was applied to the generation of hundreds of traces of threshold voltage shifts vs. time. For illustration's sake, four of these traces are shown in Fig. 7. By comparing these traces with the current trace in Fig. 1, it can be noticed that they show the same kind of random behavior, but Fig. 1 is a noisy one. This is because: (a) the voltage source in Fig. 6(b) must not contain noise as the noise is already included in the transistor model, and (b) the experimental trace in Fig. 1 contains noise intrinsic to the measurement setup that must not be included in a circuit simulation. The generated traces were used to simulate the impact of RTN on a basic integrated circuit: the simple current mirror in the inset of Fig. 8. An example of such a simulated output current for a constant input current is shown in Fig. 8(a), together with the associated copy factor in (b).

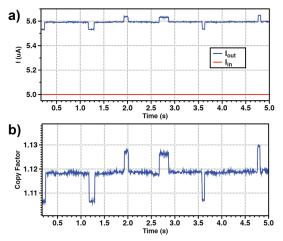

To experimentally validate the simulation methodology, the current mirror was integrated in the same 65-nm CMOS technology [15]. When biased in the same conditions, a typical behavior of the output current for a constant input current and the corresponding copy factor of the current mirror from one of the samples is shown in Fig. 9. It can be observed that the RTN directly impacts the copy factor of the current mirror, as expected from the simulation results displayed in Fig. 8.

#### V. CONCLUSIONS

In this paper, a complete methodology to simulate the impact of RTN on circuits has been presented. Since the parameters that characterize RTN are stochastic, a statistical

Fig. 7. Examples of  $\Delta V_{th}$  traces generated for four different devices by using the simulation methodology presented in this work.

characterization of the phenomenon has been performed to extract the corresponding parameter distributions. Then, by sampling these distributions, the statistical simulation of integrated circuits affected by RTN can be performed. To do this, the effect of RTN on the devices  $V_{\rm th}$  is included as a variation in the gate voltage of the device, which is incorporated through a voltage source on the transistor gate. Finally, this simulation methodology has been experimentally validated.

#### VI. REFERENCES

- N. Tega et al., "Increasing threshold voltage variation due to random telegraph noise in FETs as gate lengths scale to 20 nm", in Symp. on VLSI Technology, IEEE, pp. 50, 2009.

- [2] N. Tega et al., "Impact of threshold voltage fluctuation due to random telegraph noise on scaled-down SRAM", in Int. Rel. Phys. Symp. (IRPS), IEEE, pp. 541-546, 2008.

- [3] M. Luo, R. Wang, S. Guo, J. Wang, J. Zou, R. Huang, "Impacts of random telegraph noise (RTN) on digital circuits", IEEE Trans. Electron Devices, vol. 62, pp. 1725-1732, 2015.

- [4] T. Grasser et al., "Switching oxide traps as the missing link between negative bias temperature instability and random telegraph noise," in Int. Electron Devices Meet. (IEDM), IEEE, pp. 1-4, 2009.

- [5] J. Diaz-Fortuny et al., "A versatile CMOS transistor array IC for the statistical characterization of time-zero variability, RTN, BTI and HCI", IEEE J. Solid-State Circuits, vol. 54, no 2, pp. 476-488, 2018.

- [6] J. Diaz-Fortuny et al., "Flexible setup for the measurement of CMOS time-dependent variability with array-based integrated circuits", IEEE Trans. Instrum. Meas., vol. 69, no. 3, pp. 853-864, 2019.

- [7] P. Saraza-Canflanca et al., "TiDeVa: a toolbox for the automated and robust analysis of Time-Dependent Variability at transistor level", Proc. of Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), pp. 1-4, 2018.

- [8] P. Saraza-Canflanca et al., "A robust and automated methodology for the analsis of time-dependent variability at transistor level," in Integration, the VLSI Journal, Vol. 72, pp. 13-20, 2020.

Fig. 8. a) Simulated  $I_{out}$  for a constant  $I_{in}$  displaying the impact of RTN, and b) the corresponding copy factor, for the current mirror in the inset.

- [9] K. Takeuchi et al., "Direct observation of RTN-induced SRAM failure by accelerated testing and its application to product reliability assessment," Proc. Symp. VLSI Technology, pp. 189-190, 2010.

- [10] T. Nagumo et al., "New analysis method for comprehensive understanding of random telegraph noise," IEEE Int. Electron Devices Meet., (IEDM) 2009.

- [11] T. Grasser et al., "Analytical modeling of the bias temperature instability using capture/emission time maps," in Int. Electron Devices Meet. (IEDM), IEEE, pp. 27.4.1-27.4.4, 2011.

- [12] A. Lange, F. A. V. Gonzalez, I. Lahbib and S. Crocoll, "Comparison of modeling approaches for transistor degradation: model card adaptations vs subcircuits," 49th European Solid-State Device Research Conference (ESSDERC), Cracow, Poland, pp. 186-189, 2019.

- [13] D. Knuth, The Art of Computer Programming, Vol. 2: Seminumerical Algorithms, 3<sup>rd</sup> edition. Addison Wesley, 1997.

- [14] G. Box and M.E. Muller, "A Note on the generation of random normal deviates," in the Annals of Mathematical Statistics, Vol. 29, No. 2, pp. 610-611, 1958.

- [15] P. Martin-Lloret et al., "An IC array for the statistical characterization of time-dependent variability of basic circuit blocks", Proc. of Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), pp. 241-244, 2019.

Fig. 9. a) Measured  $I_{out}$  for a constant  $I_{in}$  displaying the impact of RTN on the current mirror in the inset of Fig. 8 fabricated in the same 65nm CMOS technology [15], and b) the corresponding copy factor.