CAFM Nanoscale electrical properties and reliability of HfO<sub>2</sub> based gate dielectrics in electron devices: Impact of the polycrystallization and Resistive Switching

CAFM Nanoscale electrical properties and reliability of HfO<sub>2</sub> based gate dielectrics in electron devices: Impact of the polycrystallization and Resistive Switching

A dissertation submitted by

Vanessa Iglesias Santiso

in fulfillment of the requirements for the degree of

Doctor of Philosophy in Electronic Engineering

Supervised by Dr. Marc Porti i Pujal Bellaterra, October 2012

Dr. Marc Porti, titular professor of the Electronic Engineering department of the Universidad Autónoma de Barcelona,

### Certifies

That the dissertation "CAFM Nanoscale electrical properties and reliability of HfO<sub>2</sub> based gate dielectrics in electron devices: Impact of the polycrystallization and resistive switching" submitted by Vanessa Iglesias Santiso to the School of Engineering in fulfillment of the requirements for the degree of Doctor of Philosophy in Electronic Engineering has been performed under his supervision.

Dr. Marc Porti

Bellaterra, October of 2012

Adicado a vós, ós que sempre estivestes ó meu carón e confiastes en min

### Acknowledgements

I would like to thank my director Prof. Marc Porti i Pujal for supervising my work and helping me to carry it out. Also to thank him the freedom I had to plan and report my investigations. All members of the Reliability of Electron Devices and Circuits group (REDEC) of the Universidad Autónoma de Barcelona also deserve my acknowledgement for working together during this time.

I am also very grateful for having the chance to work with different groups during my stays abroad. I thank to the directors of the research groups who welcomed me warmly, Dr. Thomas Schroeder from the IHP (Innovations for High Performance Microelectronics) (Frankfurt-Oder, Germany), Prof. Benstetter from the University of Applied Sciences of Deggendorf (Deggendorf, Germany) and specially to Mathias Rommel from the Fraunhofer Institute for Integrated Systems and Device Technology IISB (Erlangen, Germany) and his group for making me feel at home.

On the other hand, I also must thank to the Spanish government for the financial support that gave me the opportunity to carry out this work.

De forma más personal me gustaría agradecer a mis padres todo el esfuerzo realizado durante este largo camino porque sin ellos esto no hubiese sido posible. Gracias por enseñarme a levantarme después de caer y por vuestro apoyo incondicional. Si hoy soy lo que soy es, en gran parte, gracias a vosotros. A mis abuelos Constantino e Isaura, por estar siempre ahí, especialmente a mi abuela por no dejar de sorprenderme cada día con su fortaleza y sus ganas de aprender. A mi hermana Vero y a Julia, por ser como ese faro que, aún en la distancia, me ayuda en los momentos de tempestad. Gracias por estar ahí. A Óscar, por su infinita paciencia y confianza. Gracias por creer en mi. Finalmente agradecer a mis compañeros de fatiga los momentos compartidos durante esta travesía por el departamento, chic@s, sin vosotros esto no sería lo mismo. Gracias.

# Index

| Publications relat | ed to this thesis                                | i  |

|--------------------|--------------------------------------------------|----|

| Presentation       |                                                  | 1  |

| Chapter I: Introdu | ction                                            | 3  |

| 1.1 The MO         | SFET transistor                                  | 4  |

| 1.1.1              | Basic principles                                 | 4  |

| 1.1.2              | MOSFET scaling                                   | 8  |

| 1.2 High-k d       | ielectrics                                       | 10 |

| 1.3 Dielectri      | c Breakdown                                      | 13 |

| 1.3.1              | SILC and percolative model                       | 13 |

| 1.3.2              | Statistical distribution of Dielectric Breakdown | 16 |

| 1.3.3              | Dielectric Breakdown and Resistive Switching     | 18 |

| 1.4 Standard       | l charazterization techniques                    | 19 |

| 1.5 Tools wi       | th a nanometer resolution                        | 21 |

| Chapter II: Atomic | c Force Microscope and related techniques        | 27 |

| 2.1 Atomic I       | Force Microscope                                 | 28 |

| 2.2 Operation      | n modes                                          | 29 |

| 2.2.1              | Contact mode                                     | 29 |

| 2.2.2              | Non-contact mode                                 | 29 |

| 2.2.3              | Tapping mode                                     | 30 |

| 2.3 Conduct        | ive Atomic Force Microscope                      | 31 |

| 2.4 Kelvin P       | robe Force Microscope                            | 33 |

| 2.5 Atomic I       | Force Microscope probes                          | 35 |

| 2.6 Setups u       | sed                                              | 39 |

| Chapter III: Impact of the tip characteristics and environmental                                    |      |

|-----------------------------------------------------------------------------------------------------|------|

| conditions on the CAFM resolution                                                                   | 41   |

| 3.1 Sample description                                                                              | 42   |

| 3.2 Etching of the top layer                                                                        |      |

| 3.3 Optimization of the AFM resolution: Impact of the environment                                   | 40   |

| and tip characteristics                                                                             | 47   |

|                                                                                                     |      |

| Chapter IV: Polycristallization effects on the electrical properties                                |      |

| and reliability of HfO <sub>2</sub> /SiO <sub>2</sub> based high-k stacks                           | 51   |

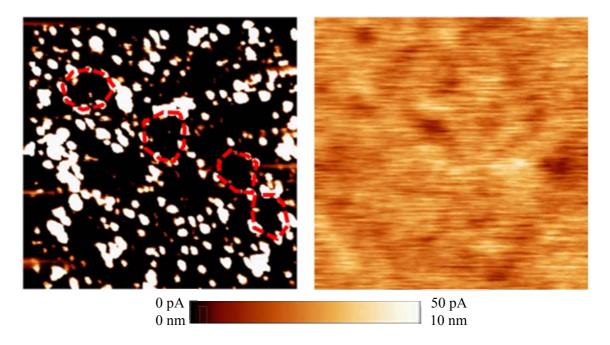

| 4.1 Topographical and electrical properties of as-grown polycrystallin HfO <sub>2</sub> gate stacks | ne   |

| 4.1.1 Topographical and electrical correlation                                                      | 52   |

| 4.1.2 Analysis of the BD spots                                                                      | 58   |

| 4.2 Electrical properties of stressed polycrystalline HfO2 gate stack                               | 60   |

| 4.3 BD distributions and the role of the interfacial layer in                                       |      |

| polycrystalline HfO <sub>2</sub> based gate stacks                                                  | . 63 |

| Chapter V: Nanoscale observation of Resistive Switching on HfO <sub>2</sub><br>based MIM structures | . 69 |

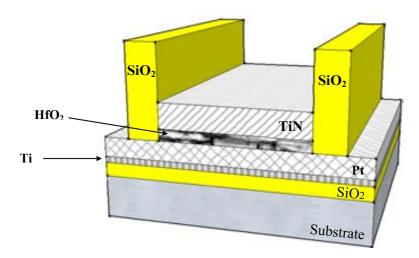

| 5.1 Samples and experimental set-up                                                                 | 70   |

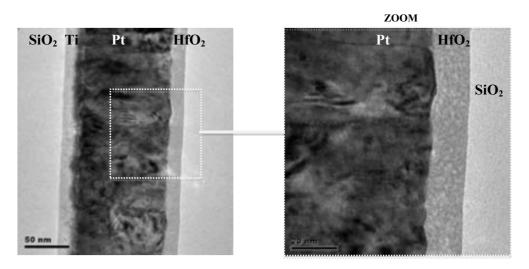

| 5.2 Morphological characterization                                                                  | 71   |

| 5.3 Resistive Switching on TiN/HfO2/Pt structures                                                   | 72   |

| 5.4 Resistive Switching on HfO <sub>2</sub> /Pt structures triggered with the CAFM tip              | 75   |

| Summary and Conclusions                                                                             | 79   |

| References                                                                                          | . 83 |

| Papers (A-D) and Annex                                                                              |      |

### Publications related to this thesis

### COMPENDIUM OF PUBLICATIONS INCLUDED IN THIS THESIS

- A) V. Iglesias, M. Porti, M. nafría, X. Aymerich, P. Dudek, G. Bersuker, "Dielectric BD in polycristalline HfO<sub>2</sub> gate dielectrics investigated by CAFM", Journal of Vacuum Science & Technology B Journal Vacuum Science Technology B 29, 01AB02 (2011)

- B) V. Iglesias, M. Porti, M. Nafría, X. Aymerich, P. Dudek, T. Schroeder, G. Bersuker, "Correlation between the nanoscale electrical and morphological properties of crystallized hafnium oxidebased metal oxide semiconductor structures", Applied Physics Letter 97, 262906 (2010)

- C) V. Iglesias, M. Lanza, K. Zhang, A. Bayerl, M. Porti, M. Nafría, X. Aymerich, G. Benstetter, Z. Y. Shen, and G. Bersuker "Degradation of polycrystalline HfO<sub>2</sub>-based gate dielectrics under nanoscale electrical stress" Applied Physics Letters 99, 103510 (2011)

- D) V. Iglesias, M. Lanza, A. Bayerl, M. Porti, M. Nafría, X. Aymerich, L. F. Liu, J. F. Kang, G. Bersuker, K. Zhang, and Z. Y. Shen, "Nanoscale observations of Resistive Switching High and Low conductivity states on TiN/HfO<sub>2</sub>/Pt structures" Microelectronics Reliability, vol. 52, Issues 9–10, pp. 2110-2114 (2012)

### OTHER PUBLICATIONS

- ➤ K. P. McKenna, A. Shluger, V. Iglesias, M. Porti, M. Nafria, M. Lanza, G. Bersuker, "Grain boundary mediated leakage current in polycrystalline HfO<sub>2</sub> films", Microelectronic Engineering 88, 1272 (2011)

- ➤ G. Bersuker, J. Yum, L. Vandelli, A. Padovani, L. Larcher, V. Iglesias, M. Porti, M. Nafria, K. P. McKenna, A. Shluger, P. Kirsch, R. Jammy, "Grain boundary-driven leakage path formation in HfO₂ dielectrics", Solid-State Electronics 65-66, 146-150 (2011)

- ➤ G. Bersuker, D. C. Gilmer, D. Veksler, P. Kirsch, L. Vandelli, A. Padovani, L. Larcher, K. P. McKenna, A. Shluger, V. Iglesias, M. Porti, M. Nafría, "Metal Oxide RRAM Switching Mechanism Based on Conductive Filament Properties", Journal of Applied Physics 110, 124518 (2011)

- ➤ M. Lanza, V. Iglesias, M. Porti, M. Nafria, X. Aymerich "Polycrystallization effects on the nanoescale electrical properties of high-k dielectrics", Nanoescale Research Letters, 6:108 (2011)

- Fontsere, A. Perez-Tomas, M. Placidi, J. Llobet, N. Baron, S. Chenot, Y. Cordier, J. C. Moreno, M. R. Jennings, P. M. Gammon, C. A. Fisher, V. Iglesias, M. Porti, A. Bayerl, M. Lanza, M. Nafria, "Nanoscale investigation of AlGaN/GaN-on-Si high electron mobility transistors", Nanotechnology 23 395204 (2012)

- ➤ Fontsere, A. Perez-Tomas, M. Placidi, J. Llobet, N. Baron, S. Chenot, Y. Cordier, J. C. Moreno, V. Iglesias, M. Porti, A. Bayerl, M. Lanza, M. Nafria," Gate current analysis of AlGaN/GaN on silicon heterojunction transistors at the nanoscale", Applied Physics Letters 101, 093505 (2012)

### CONTRIBUTIONS TO CONFERENCES

- ❖ G. Bersuker, J. Yum, V. Iglesias, M. Porti, M. Nafria, K. McKenna, A. Shluger, P. Kirsch, R. Jammy, "Grain Boundary-Driven Leakage Path Formation in HfO₂ Dielectric" Proceedings European Solid-State Device Research Conference, 333 (2010)

- ❖ V. Iglesias, M. Porti, M. nafría, X. Aymerich, P. Dudek, G. Bersuker, "Dielectric BD in polycristalline HfO₂ gate dielectrics investigated by CAFM", Workshop on Dielectrics in Microelectronics (WODIM), (oral presentation). Proceedings paper, pp. 56 (2010)

- M. Porti, M. Lanza, V. Iglesias, M. Nafría and X. Aymerich, "Crystallization effects on the variability of the electrical properties of high-k dielectrics at the nanoscale", European Materials Research Society, (Invited talk) (2010)

- ❖ G. Bersuker, D. C. Gilmer, D.Veksler, J. Yum, H. Park, S. Lian, L.Vandelli, A.Padovani, L.Larcher, K. McKenna, A. Shluger, V. Iglesias, M. Porti, M. Nafría, W. Taylor, P. D. Kirsch, R. Jammy, "Metal Oxide RRAM Switching Mechanism Based on Conductive Filament Microscopic Properties", IEEE *International Electron Device Meeting* (IEDM). Proceedings paper pp. 19.6.1-19.6.4 (2010)

- ❖ Bayerl, V. Iglesias, M. Lanza, M. Porti, M. Nafría, X. Aymerich, "High-k dielectric polycrystallization effects on the nanoscale electrical properties of MOS structures", Proceedings of the 8th Spanish Conference on Electron Devices (CDE) (Poster). Proceedings paper, pp. 1-4, (2011)

- ❖ V. Iglesias, A. Bayerl, M. Lanza, M.Porti, M.Nafria, X.Aymerich, "Impact of the polycrystallization of high-k dielectrics on the nanoscale and device level electrical properties of MOS capacitors", Nanospain (poster). Proceedings paper, pp. 1-4 (2011)

- ❖ V. Iglesias, T. Erlbacher, M. Rommel, K. Murakami, A. J. Bauer, L. Frey, M. Porti, J. Martín-Martínez, R. Rodríguez, M. Nafria, X.Aymerich, G. Bersuker "Effect of HfO₂ polycrystallinity on distribution of the CAFM-induced TDDB in high-k gate stacks" Workshop on Dielectrics in Microelectronics (WODIM), (POSTER) (2012)

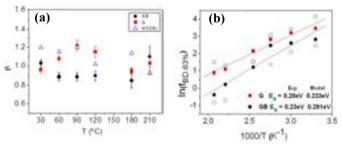

### CURRENT SUBMITTED ARTICLES

V. Iglesias, M. Martin-Martinez, M. Porti, R. Rodriguez, M. Nafria, X.Aymerich, T. Erlbacher, M. Rommel, K. Murakami, A. J. Bauer, L. Frey, G. Bersuker "Temperature dependence of CAFM TDDB distributions in polycrystalline HfO<sub>2</sub> gate stacks: The role of the interfacial layer and grain boundaires", submitted to Electron Device Letters.

# PRESENTATION

Nowadays it is difficult to imagine a life without electronic devices anywhere. They are so present in our routines that they seem to be there from always. However, electronics beginning is not so far away. In 1883, Thomas Alva Edison discovered that electrons flew from one metal conductor to another through vacuum when a voltage is applied between them. This effect, known as Edison effect, was applied in 1904 by John Fleming to invent the diode, opening the way to the current electronics. After this, the electronic field evolution was continuous. Different devices appeared (triode, tretode, etc.), but the bipolar transistor development in 1947 by John Bardeen, Walter Houser Brattain and William Bradford Shockley supposed a turning point in the electronics era. The introduction of the transistor allowed, among other things, to reduce the electronic device dimensions as well as to increase its speed. Shortly afterwards, a different type of transistor was developed, the FET (Fiel Effect Transistor), although the theory had been patented previously to the bipolar transistor development. For many years, transistors were made as individual electronic components and were connected to other electronic devices (resistors, capacitors, inductors, diodes, etc.) on boards to fabricate an electronic circuit. They were much smaller than vacuum tubes, faster and consumed much less power. However, circuits based on individual transistors became too large and too difficult to be assembled. To improve them it would be necessary to pack the transistors closer and closer together. To solve that, in 1959, Jack Kilby and Robert Noyce developed the integrated circuit. Silicon-based integrated circuits (ICs) have become the backbone of today's semiconductor world, being the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) his main, more common and important device.

For more than 45 years, since the 1960's, the number of transistors per unit area has been doubling every 1.5 years, leading to an important shrinking in the transistor size. However, this continuous miniaturization has found its physical limits. For example, the thickness reduction of  $SiO_2$  dielectric layer, with current sizes at nanometric scale, has become a crucial issue in the scientific comunity since it is being affected by quantum phenomena, as for example, tunneling current. Thickness scaling down leads to larger leakage currents (implying a higher power consumption) and, consequently, to an impoverishment of the reliability of the transistor. At this point, it seems inevitable the introduction of some variations in the present technology as well as the research of different alternatives. From the different proposed solutions, the  $SiO_2$  replacement by other materials, as high-k dielectrics, could be an alternative. However, although it sounds simple it is really a complicate issue. The introduction of new materials has associated new challenges and difficulties that must be solved as soon as possible to

achieve the semiconductor company's request. The main problems related to the use of high-k dielectrics based stacks are: i) high density of intrinsic defects, ii) no good interaction with the gate electrode, iii) unavoidable formation of a  $SiO_2$  layer at the interface with the Silicon substrate, iv) poor carrier's mobility at the conductive channel due to scattering phonons, and v) polycristallization of the high-k dielectric when it is subjected to high temperatures during the manufacturing process, which can alter the electrical properties of the device, among others.

Since many of the problems associated to these materials (like, for example, their polycrystallization) and the failure mechanisms that affect the gate oxide are phenomena that have been found to have a nanometric origin, it seems logical to study them at the same scale to obtain an accurate knowledge. Different tools as the Scanning Probe Microscopy based techniques have recently been used to perform such nanoscale analyses. Among them, especially when studying the electrical properties and reliability of gate dielectrics, the Conductive Atomic Force Microscope (CAFM) has been the most used until now. This technique is capable to obtain simultaneously and independently topographical and electrical information at the nanoscale, achieving lateral resolutions of the order of 10nm.

Following this line, this thesis is focused to evaluate, mainly with CAFM, the influence of the polycrystallization on the electrical properties and reliability of a high-k based gate stack. In chapter I, the MOSFET, basic component of present microelectronics, is introduced. Among other things, its evolution and different problems related to its scaling down are described. High-k dielectrics are also introduced in this chapter as well as different characterization techniques to achieve a nanoscale resolution.

Chapter II is devoted to describe in detail the main characterization tool used in this work, the Atomic Force Microscope (AFM), and two related techniques, which are important to study the electrical properties and reliability of gate dielectrics: CAFM and Kelvin Probe Microscope (KPFM).

Chapter III is focused on the description of the sample characteristics used in this work and the search of optimal experimental conditions to perform the CAFM measurements with the highest resolution.

Chapter IV presents the main aim of this work. It is known that some high-k materials, as for example HfO<sub>2</sub>, could change its morphology as a consequence of high temperature manufacturing processes. In this chapter, a deep study about the impact of the high-k layer polycristallization of HfO<sub>2</sub> based gate stacks, after an annealing process, on the gate stack electrical characteristics and reliability is shown. The study has been carried out at the nanoscale using, mainly, a CAFM.

Finally, chapter V introduces the analysis at the nanoscale of high-k materials in the field of non-volatile data memories (NVMs). Specifically, in the Resistive Random Access Memory (RRAM) technology, based on a reversible and repeatable change of the resistance (Resistive Switching, RS) of a metal-insulator-metal (MIM) memory cell. The RS phenomenon is analysed at device level and at the nanoscale with CAFM.

# CHAPTER I

### Introduction

Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is the main, more common and important device in the silicon-based integrated circuits. It is present in almost every electronic set, having, therefore, a relevant position in the microelectronics field. In this chapter, firstly, the basic concepts of a MOSFET transistor are introduced as well as the consequences of the continuous shrinking of MOS devices and the possible alternatives to avoid these consequences. High-*k* dielectrics and associated failure mechanism, as dielectric breakdown (BD), are also introduced. Resistive switching, which will be also treated in chapter V, based on the creation of reversible conductive filaments (probably related to reversible BD events) is presented too. In the second part, the attention will be centred in the different characterization techniques normally used to study the electrical properties and reliability of MOS devices: standard characterization techniques and tools with nanometric resolution, as Conductive Atomic Force Microscope (CAFM).

### 1.1 The MOSFET transistor

### 1.1.1 Basic principles

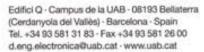

The MOSFET is based in the Metal Oxide Semiconductor (MOS) structure, illustrated by Figure 1.1. A traditional MOS structure consists of a semiconductor substrate, which can be p or n-type, with a thin silicon oxide layer and a polysilicon contact, referred to as the gate [Pierret 96]. Before 1970, the gate was typically made of metal. After 1970, heavily doped polycrystalline silicon was used as the standard gate material because of its ability to withstand high temperature without reacting with SiO<sub>2</sub>. After 2007, the trend has been to reintroduce metal gate and replace SiO<sub>2</sub> with more advanced dielectrics (see section 1.2). As the oxide is a dielectric material, its structure is equivalent to a planar capacitor with one of the electrodes replaced by a semiconductor.

Figure 1.1: Traditional MOS structure consisting of a semiconductor substrate, which can be p or n-type, a silicon oxide layer as dielectric and a polysilicon contact as gate

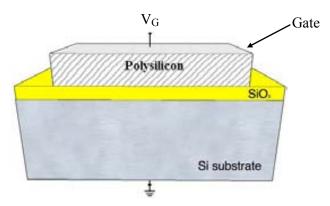

The energy band diagram of an ideal MOS structure is drawn in figure 1.2. The oxide is situated in the middle meanwhile the gate and the substrate are on the left- and right-hand sides. In an ideal situation there is no charge in the oxide or at  $SiO_2/Si$  interface and no band bending that usually occurs as a consequence of the different values of metal and semiconductor work functions ( $\Phi$ , defined as the energy needed to move an electron from the Fermi level into the vacuum).

Figure 1.2: Energy band diagram for an ideal MOS capacitor.  $\Phi_M$  and  $\Phi_S$  are the metal and semiconductor work functions respectively.  $\Phi_B$  is the electron energy barrier

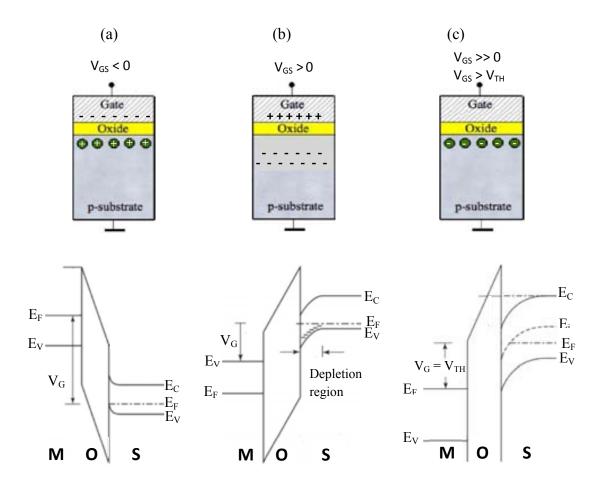

Assuming a p-type Si substrate three modes can be distinguished in a MOS capacitor depending on the applied bias between the gate  $(V_G)$  and the substrate  $(V_S)$ : accumulation, depletion and inversion.

If the applied voltage is  $V_{GS}$ <0V, a large number of holes are attracted to the surface (figure 1.3(a-top)). Looking at the band diagram (figure 1.3(a-bottom)), it can be observed that the band edge on the gate side shifts upwards. Consequently,  $E_v$  (valence energy) is closer to  $E_F$  (Fermi energy) at the oxide/semiconductor interface than in the bulk and therefore, the surface hole concentration, p, is larger than the bulk hole concentration, forming an accumulation layer at or near the interface. This regime is known as *accumulation*.

If a positive  $V_{GS}$  is applied, the positive charge in the oxide/semiconductor interface is pushed away into the substrate. Therefore, the semiconductor is depleted of mobile carriers at the interface and a negative charge, due to the ionized acceptor ions, remains in the space charge region figure 1.3(b-top). Looking at the band diagram it can be observed that the band edge on the gate side shifts downwards figure 1.3(b-bottom). In this case, a depletion region is formed since  $E_F$  is far from both  $E_c$  (conduction energy) and  $E_v$ . This regime is known as *depletion*

If  $V_{GS}$  is high enough, free electrons (minority carriers in a P-type substrate) are attracted to the insulator/semiconductor interface increasing the density of the negative charge (figure 1.3 c-top). From the band diagram is observed that the band edge on the gate side shifts downwards further (figure 1.3(b-bottom). At some values of  $V_G$ ,  $E_F$  will be close enough to  $E_c$  at the  $Si/SiO_2$  interface, becoming this, rich in electrons figure 1.5(b) (minority carriers) and, therefore inverting the interface from P type to N type. This regime is known as *inversion*. The minimum voltage required to generate this situation is known as threshold voltage,  $V_{TH}$ .

An analogue behaviour can be described for a MOS structure with a n-type silicon substrate. However, in this case, the different operation modes are reached by applying inverted polarities. It is important to remember that the behavior described until now corresponds to the ideal situation, which occurs when no charge is trapped in the oxide and the work function difference between metal and semiconductor metal ( $\Phi_{ms}$ ) is zero (the work function is defined as the energy needed to move an electron from the Fermi level into vacuum). However, this is not normally true and, moreover, the presence of charge in the oxide cannot be ruled out. Therefore, it is necessary to add a voltage to achieve the flat band conditions, defined as the situation in which there is no internal potential difference across a metal-oxide-semiconductor structure.

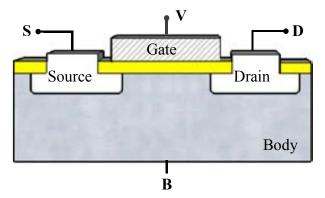

The MOS capacitor is not a widely used device in itself, but it is the basic part of the MOS transistor (MOSFET), by far the most used semiconductor device. The MOSFET is a four-terminal device with a source (S), gate (G), drain (D), and bulk (B) (or substrate) as electrodes (figure 1.4). Its working principle is based on the modulation of free carriers' concentration at the channel (oxide-semiconductor interface) by the polarization of the MOS capacitance. Depending on the type of carriers through the conduction channel (i.e. the inversion layer), the MOSFET can be classified as N-MOSFET (electron through the channel) or P-MOSFET (holes through the channel). Combination of both, P-MOSFET and N-MOSFET are used to construct integrated circuits (ICs). This technology is known as Complementary Metal Oxide

Semiconductor (CMOS).

Figure 1.3: Different modes of an ideal MOS capacitor: (a) accumulation (b) depletion (c) inversion. On top, the types of charges present on the insulator/semiconductor interface are represented. On bottom, the energy band diagrams are shown.

Figure 1.4: Cross-section of an Metal-Oxide-Semiconductor-Field-Effect-Transistor (MOSFET).

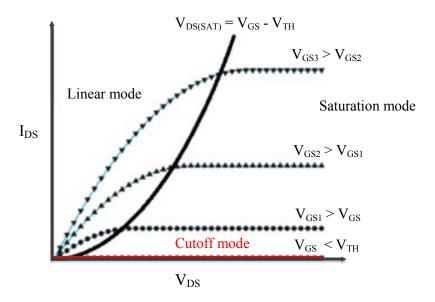

Depending on the applied voltage at the terminals, three different modes can be defined: a) cutoff or weak-inversion mode, b) ohmic mode or linear region, and c) saturation or active mode [Pierret 96 <sup>I</sup>].

If  $V_{GS} < V_{TH}$  the inversion channel is not created at the interface and the transistor is turned off, that is, there is not conduction between source and drain  $(I_{DS})$  even when a  $V_{DS}$  is applied. This is known as *cutoff* or *weak inversion mode*.

If  $V_{GS} > V_{TH}$  and  $V_{DS} < (V_{GS} - V_{TH})$ , the transistor is turned on and a channel, which allows current to flow between the drain and the source, is created. The current flowing through the channel is defined as (1.2):

$$I_{DS} \approx \frac{\mu_n C_{ox}}{2} \frac{W}{L} \left( 2 \left( V_{GS} - V_{TH} \right) V_{DS} - V_{DS}^2 \right)$$

(1.2)

were  $\mu_n$  is the carrier mobility,  $C_{ox}$  the oxide capacitance, W the channel width, L the channel length and  $V_{GS}$ ,  $V_{TH}$  and  $V_{DS}$  are the gate-source, threshold and drain-source voltage, respectively. In this region, the MOS transistor acts as a variable resistor controlled by the gate voltage relative to the source voltage. This is known as *ohmic* or *linear mode*.

If  $V_{GS} > V_{TH}$  and  $V_{DS} \ge (V_{GS} - V_{TH})$ , the channel is "pinched off" at the drain end, and  $I_{DS}$  saturates. That is,  $I_{DS}$  becomes, in first approximation, independent of the drain voltage. This is known as saturation mode. Figure 1.5 shows the typical I-V characteristics for the different modes for a N-MOSFET. Note that the behaviour above described corresponds to the ideal situation.

Figure 1.5:  $I_{DS}$ - $V_{DS}$  characteristics of an n-channel MOSFET for different  $V_{GS}$  voltages. Depending on the  $V_{GS}$  and  $V_{DS}$  values, different operation modes can be described.

### 1.1.2 MOSFET scaling

Over time, the reduction of the MOSFET dimensions has been continuous [Dennard 74, Baccarani 84, Critchlow 99, Frank 01]. Starting from a channel length of 10 mm in the 1960s, channel lengths of approximately the mean free path of charge carriers have been reached nowadays. This is known as scaling. There are several reasons for this continued size reduction. The main reason is to pack more and more devices in a given chip area. From an economical point of view, since fabrication costs for a semiconductor wafer are relatively fixed, the introduction of more chips per wafer reduces the price per chip. Moreover, smaller transistors switch faster and the power consumption decreases significantly with the down-scaling [Wilk 01]. In 1965, Gordon Moore, Intel co-founder, predicted that the number of transistors on a chip would double every year [Moore 65] although later, he actualized it to approximately every two years. Nowadays this prediction is known popularly as Moore's law.

During long time, the scaling rules were governed by two scaling methods: constant field scaling and constant voltage scaling [Dennard 74, Critchlow 99]. On one hand, constant voltage scaling proposed to maintain the applied voltage constant, while the dimensions of the MOSFET were scaled down. The associated disadvantage was the increase of the electric field as the minimum feature length was reduced, leading to: velocity saturation, mobility degradation, increasing leakage currents and lower breakdown voltages [Critchlow 99]. On the other hand, constant field scaling rules proposed to shrink MOSFET dimensions by a factor α to get a smaller FET with similar behaviour. To do that, all voltages and dimensions have to be reduced by the scaling factor α, meanwhile the doping and charge densities have to be increased by the same factor, maintaining constant the electric field inside the FET. This scaling methodology leads to an increase in the velocity of the circuit proportional to  $\alpha$ . In addition, circuit density increases proportionally to  $\alpha^2$ . However, residual current increases due to the threshold voltage reduction [Frank 01, Ghani 00]. Since the 'further scaling' of threshold voltage lead to large off state drain leakage currents, more generalized scaling rules were redefined during the 80's. The generalized scaling approach, were the voltage is not scaled as fast as the dimensions, allows to increase the electric field by a factor ε [Baccarani 84], being ε the scaling parameter, which usually describes the sizereduction. Although the scaling trend during the last decades of the past XX century was more aggressive than during the last 10 years, leading to a general believe that the end of Moore's law was close, on February of 2012, Intel announced a new device which assures that Moore's law will continue, at least for some more generations [Intel].

However, despite the advantages of the scaling, the MOSFET dimensions reduction has also some drawbacks that must be considered in detail. One of the consequences of such scaling process of the MOSFET is the reduction of the gate oxide thickness which leads to the appearance of what is known as tunnelling current through the gate oxide. Tunnelling current through the gate oxide is a quantum phenomenon by which the gate current (current between the gate and the substrate,  $I_{GS}$ ) is different of zero when a  $V_{GS}$  is applied (ideally it should be zero due to the presence of insulators). It was noticed as a significant source of leakage and greatly increased power dissipation in the 90s decade for the first time [Momose 94].

According to the tunnelling theory [Sanchez del Río 99], an important parameter that determines the magnitude of the tunnelling probability is the width of the potential

barrier. In MOSFETs, the element that plays the role of a potential barrier is the gate dielectric. Therefore, when the oxide thickness decreases, the width of the energy barrier is reduced, facilitating electrons tunneling through the insulator layer [Lee 01, Clerc 02, Gehring 04] as figure 1.6a shows.

Figure 1.6: Tunneling current in a MOSFET.

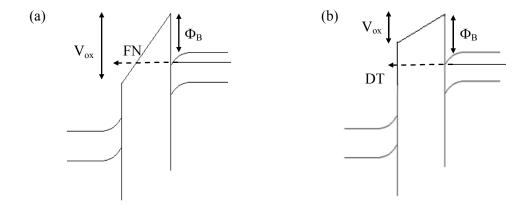

Different conduction modes can be described for the gate tunneling current, which are easily understood by analyzing the energy band diagram of the MOS structure [Lee 01]. Taking into account the shape of the energy barrier, Direct Tunneling (DT) and Fowler-Nordheim (FN) tunnelling are considered. If the oxide tunnel barrier is trapezoidal, DT occurs while FN takes place through a triangular barrier (figure 1.7). The transition from FN to DT occurs when the difference in potential energy over the oxide layer  $qV_{ox}$  becomes smaller than the tunnel barrier height  $\Phi_{B}$ , at the injecting interface [Depas 95]. In addition to the applied electrical field, the dominant conduction mechanism through the oxide (DT or FN) also depends on the oxide thickness. For small voltages and thin oxides the dominant tunneling mechanism is the DT, while for thick oxides and high electrical fields the dominant tunneling mechanism is the FN [Degraeve 99]. A more strict analysis of the conduction modes can be found in [Gehring 04, Yang 04].

Figure 1.7: Schematic energy band diagram in the case of (a) Fowler-Nordheim tunneling (FN) and (b) direct tunneling (DT) current

Due to the continuous SiO<sub>2</sub> layer thickness shrinking in a MOS transistor, tunnelling current increased more and more becoming the dominant source of device leakage. The main consequences of this leakage current enlargement are, on one hand, the consumption increase in standby power [Lo 97] and, on the other hand, the impoverishment of the reliability of the device. This impoverishment can be understood as an increment of the probability that the device failure happens for shorter times than usually.

At this point, the scientific community was forced to look for different alternatives since the perfect SiO<sub>2</sub> layer had reached his physical limit. In 2007, materials with higher dielectric constant were chosen as alternative to the SiO<sub>2</sub> layer to reduce the tunnelling current and also to avoid reliability issues [Yuan 97, Momose 94]. However, even with these materials, further scaling will be also required for future conventional CMOS generations. For example, the International Technology Roadmap for Semiconductors (ITRS) predicts an EOT of 0.55 nm for high-performance logic transistor on bulk Si in the year 2017 [ITRS], substantially lower than the currently 0,84-0,79 nm. The first idea that comes to mind is to reduce the physical thickness of the high-k layer, however, this is not a solution because this would increase gate leakage current again. The different options that are being taken into account are: (i) To introduce a new high-k material with k-value greater than the actual Hf-based oxides; (ii) To increase the k-value of IL; (iii) To reduce the physical thickness of IL [Frank 09, Frank 11, Ando 12]. Nowadays, devices with alternative architectures are also being investigated as possible replacements for the classical CMOS structure. Silicon on Insulator (SOI) MOS transistors and, especially multigate field-effect transistor (multigate FET) are acquiring an outstanding position to be the next generation of transistors [Colinge 04]. In fact, Intel has recently presented a new technology at 22nm based in 3D FinFET [sale en junio]. Anyway, high-k materials are also used in these new technologies so a better knowledge about them is mandatory. For this reason, high-k are the main topic of this thesis.

### 1.2 High-k dielectrics

The substitution of the  $SiO_2$  layer by high-k dielectrics allows to reduce the prohibitive leakage current through  $SiO_2$  based gate stacks as gate oxide thickness is scaled down. This replacement makes necessary the introduction of a new parameter to describe the electrical behavior of the transistor: the Equivalent Oxide Thickness (EOT). EOT, described in (1.3), is defined as the equivalent thickness of a  $SiO_2$  layer needed to obtain the same capacitance than the one obtained by the high-k dielectrics:

$$EOT = \frac{K_{SiO_2} \cdot t_{high-k}}{K_{high-k}} \tag{1.3}$$

where K and t are the dielectric constant and physical thickness, respectively, of the materials indicated in subscript (high-k and  $SiO_2$ ).

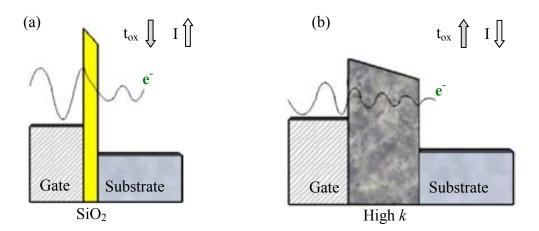

With the substitution of the SiO<sub>2</sub> by high-k dielectrics, equivalent performance can be obtained for the capacitance with a larger physical thickness (figure 1.8) and, therefore, reducing the leakage current. In addition, with the introduction of high-k gate insulators at the 45nm technology [Mistry 07], the poly-crystalline silicon gate electrode was replaced by metals [Chau 04, Gusev 06, Chudzick 07, Guha 09] in order to avoid the

channel mobility degradation because of poly-Si/high-k interface [Gusev 01, Lee 03].

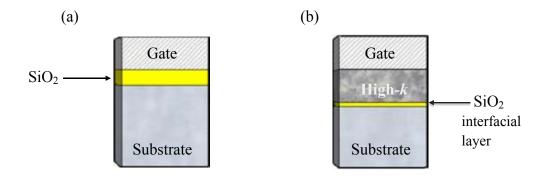

Figure 1.8: Schematics representation of the leakage current reduction (meanwhile the capacitance remains unalterable) in a MOS structure when a  $SiO_2$  dielectric (a) is replaced by a high-k dilectric (b)

However, the substitution of the SiO<sub>2</sub> by high-k dielectrics has not been an easy task. Mainly because the only inconvenient of SiO<sub>2</sub> is its lower dielectric constant while high-k dielectrics are materials with, in principle, only one advantage (a higher dielectric constant) and a lot of drawbacks. Despite the rapid increase in the understanding of high-k dielectrics, a lot of unresolved problems on their electrical performance and reliability still lie ahead. It was recognized that high-k materials knowledge is not enough mature to replace the traditional poly-Si/SiO<sub>2</sub> gate stack while simultaneously ensuring sufficiently low EOT, leakage current, appropriate threshold voltages and good reliability. It is unnecessary therefore, to say that a better knowledge about these materials is mandatory. Some of these problems are associated to the material itself as well as on the processing technology. For this reason, during the last years, the physical and electrical properties of several metal oxides as ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub> (among others) were studied as candidate materials [Wilk 01, Qi 99, Chin 00, Ragnarsson 01, Wu 00]. Among them, the semiconductor industry converged on Hf-based oxides, such as HfO<sub>2</sub> (k ~20-25) or HfSi<sub>x</sub>O<sub>y</sub>, for the first CMOS generation (45 nm technology) products featuring high-k gate dielectrics and metal gate electrodes (HKMG) [Mistry 07, Jan 09]. However, although two distinct integration schemes are being pursued currently for metal gate/high-k transistor fabrication, "gate-first" and "gate-last" integration [Kesapragada 10], the contact between HfO<sub>2</sub> and Si-substrate is not totally under control [Miyata 12]. The fabrication process of devices based on HfO<sub>2</sub> dielectrics can lead to an interfacial SiO<sub>2</sub> layer (IL) between both, high-k and Sisubstrate, which can increase the EOT of the structure (figure 1.9). The IL layer, in addition to the high-k layer, results in a system that is equivalent to two capacitors connected in series. For that reason, the total EOT of the HKMG stack can be expressed as it is indicated in (1.4).

$$EOT = EOT_{IL} + EOT_{HK}$$

(1.4)

Where EOT<sub>IL</sub> and EOT<sub>HK</sub> are contributions from the IL and high-k layer, respectively.

In figure 1.9, a typical HKMG stack structure is compared with a stack based in SiO<sub>2</sub> gate.

Figure 1.9:  $SiO_2$  gate stack (a) compared with typical high-k metal gate stack (b). In (b), a  $SiO_2$  interfacial layer appears increasing the EOT of the stack.

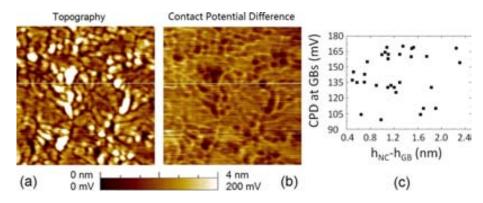

The morphology of the high-k material and its impact on the electrical properties of the stack is another important factor to be considered. High-k dielectrics can show polycrystalline, epitaxial crystalline or amorphous structure. The epitaxial crystalline layers show a good interfacial behavior with Si. However, this option requires great efforts since its manufacturing process is more difficult and expensive, increasing the cost of the device. For this reason, amorphous layers are generally the preferential option for several reasons such as low cost because of high compatibility with the existing fabrication process, lower density of interfacial defects and isotropic behavior which minimizes the carrier's dispersion and degradation of the mobility [ Robertson 04]. However, most of the amorphous high-k dielectrics tend to polycrystallize either during deposition or after heat treatment in a traditional CMOS process. This involves drawbacks, such as, inhomogeneity in their electrical behaviour and fluctuations of the dielectric constant along the stack due to the different orientations of the poly-crystals and the presence of grain boundaries (GB) [Chowdhury 10]. The impact of polycrystallization is an interesting issue to be analysed since its influence in the electrical behaviour is not well understood. Some works state that GBs act as conductive paths [Yanev 08, Bayerl 11] while others suggest that GBs do not have influence in the conduction through the dielectric [Kim 04]. The GBs influence in the electrical behaviour of a polycrystalline high-k layer, specifically HfO<sub>2</sub>, is treated in more detail in chapter IV as one of the main topics of this thesis.

It must also be considered that the introduction of new materials is generally associated with new reliability challenges that must be deeply studied. High-k materials introduce novel reliability phenomena, related to the asymmetric gate band structure and the presence of fixed charge, as well as degradation mechanisms already known for SiO<sub>2</sub> based technologies [Oates 03, Degraeve 08, Stathis 10, Ribes 05]. Although on the whole, most of the models and concepts that had been developed for SiO<sub>2</sub> reliability could be maintained on high-k stacks [Degraeve 08], the transfer of knowledge about SiO<sub>2</sub> properties and degradation mechanisms to the high-k dielectrics should be done very carefully due to the significant physical differences between both. For that, a better understanding is required for both, new and already known mechanism, since the behavior of well-known failure mechanisms could change [ITRS].

The most important high-k dielectric degradation and failure mechanisms are:

- Charge Trapping. High-k dielectrics have been known to be "trap-rich" materials. Significant amount of charge trapping centers that affect to device parameters, such as threshold voltage stability and drive current, are enclosed at high-k dielectrics films [Ribes 05, Shajan 04, Kerber 02, Minseok 07]. Nevertheless, the existence of these traps is not always a disadvantage. Since charge trapping could be a reversible phenomenon, some companies as Samsung, have developed flash memories based in charge trapping effects [Lee 05].

- Negative/Positive Bias Temperature Instability (NBTI/PBTI) is defined as the shift of the threshold voltage in a PMOS/NMOS transistor when a negative/positive voltage is applied to the gate at elevated temperature. NBTI is associated with positive charge trapping [Degraeve 08, Neugroschel 08]. PBTI is associated with negative charge trapping. Meanwhile PBTI was insignificant in NMOS transistors with SiO<sub>2</sub>, in SiO<sub>2</sub>/high-k it becomes an important reliability issue [Degraeve 08, Shimokawa 09].

- Channel Hot Carriers (CHC). Charge carries are accelerated by the large electric field across the channel of a MOSFET acquiring kinetic energy. Those carries that gain a very high kinetic energy are called hot carriers (HC). Hot carriers can generate electron-hole pairs near the drain due to impact ionization from atomic-level collisions. Moreover, HC can be injected into the gate channel interface, damaging the dielectric and causing threshold-voltage shift. [Amat 09, Amat 11, Amat 10]

- Stress Induced Leakage Current (SILC) is defined as an increase in the gate leakage current of a MOSFET, due to defects created in the gate oxide during electrical stressing.

- *Dielectric breakdown* (BD) is related to the loss of the dielectric properties of the gate oxide when the stack is subjected to an elevated electrical field. The changes of the electrical properties of the oxide after breakdown, can lead to the device or even circuit failure [Martin-Martinez 12].

Since, among the different failure mechanisms described above, the analysis of the BD of HfO<sub>2</sub>/SiO<sub>2</sub> based gate stacks will be part of this thesis, next section will be devoted to briefly introduce the main concepts and models related to this failure mechanism.

#### 1.3 Dielectric Breakdown

### 1.3.1 SILC and percolative model

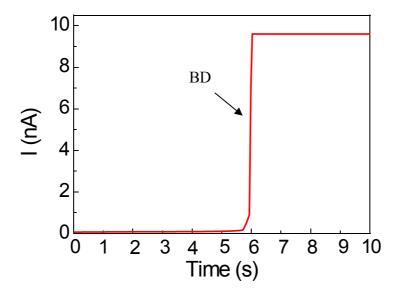

As noted above, BD is related to the loss of the dielectric properties of the gate oxide. As consequence of the changes on its dielectric properties, the failure of the device or even of the circuit [Martin-Martinez 12, Degraeve 01] could occur. For this reason, gate-oxide breakdown is one of the key reliability issues in MOSFETs. BD is characterized by a strong increase of the current through the oxide, which can be several

orders of magnitude greater than the current measured on a fresh (before BD) structure. Although BD has been intensively studied for more than two decades, there is not general consensus about its physical origin. Nevertheless, the percolation model, which describes the BD process, is widely accepted [Degraeve 98, Stathis 99, Nigam 09, Suñe 10, Raghavan 12]. According to this model, BD is the consequence of a degradation stage of the oxide microstructure [Lombardo 05], which has been related to the generation of defects during an electrical stress. The oxide degradation induced during an electrical stress can be understood as a continuous creation of traps, which lead to local energy levels in the bandgap of the oxide, facilitating trapping of charges in these defects tunnelling carriers from cathode to anode depending on the oxide thickness. In the last case, it is important to note that the measurement of the progressive increase of the gate leakage current during the degradation stage (SILC) could also give information about the degradation mechanism.

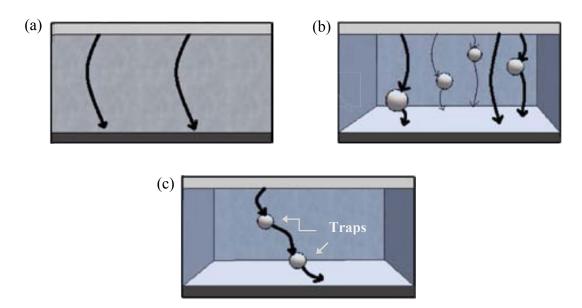

SILC is principally observed in oxides from 3 to 7nm thick [Jahan 99]. In thicker oxides, trapping charge at the generated defects becomes dominant while in thinner oxides, SILC is masked by Direct Tunnelling current. Even in 3-7nm thick oxides, SILC is basically measured at low fields, since at high fields is masked by Fowler-Nordheim tunnelling current [DiMaria 95]. SILC is caused by trap-assisted tunnelling through single traps. However, in some cases, a localized configuration of two traps can appear making easy the carriers tunnelling from cathode to anode. If it happens, a larger current density, compared to normal SILC, is observed. This phenomenon is known as "anomalous" SILC and it is, among others, a critical reliability issue in flash memories [Kumagai 08]. Actually, in thin oxides layers, breakdown can be understood as an extreme case of anomalous SILC [Degraeve 02]. Figure 1.10 illustrates a scheme where it is possible to compare: a) direct tunnelling from cathode to anode without traps in the oxide; b) trap-assisted tunnelling through single traps created during an electrical stress, responsible for SILC; and finally c) two-trap percolation path, responsible for "anomalous" leakage current.

Figure 1.10: Schematic showing (a) direct tunneling from cathode to anode without traps in the oxide, (b) trap assisted tunneling through single traps created during an electrical stress, responsible for SILC, (c) two-trap percolation path, responsible for "anomalous" leakage current.

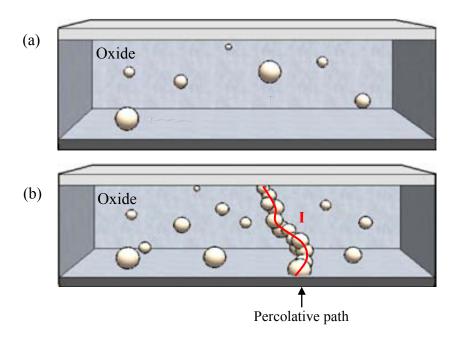

According to the percolative model, when the density of created defects reaches a critical value, a conductive path is formed between anode and cathode leading to a sudden increase of the gate current and, consequently, to BD [Suñe 90, Degraeve 96, Degraeve 98]. Furthermore, this model takes into account the extremely local nature (10-100nm²) of dielectric breakdown since the post-BD current mainly flows through the percolative path instead of the whole dielectric. In figure 1.11, a schematic that shows the formation of the percolation path associated to dielectric BD is illustrated to facilitate its understanding. Figure 1.11(a) represents the random generation of traps during an electrical stress while figure 1.11(b) shows the formation of the percolative path, leading to BD.

Figure 1.11: Formation of the percolative path, described from the percolation model, associated to dielectric BD. (a) Random generation of traps during an electrical stress. (b) Formation of the percolative path leading to a sudden and large increase of the gate current. When that happens, stack BD has been triggered.

Traditionally, for thick SiO<sub>2</sub> oxides (>10 nm), BD was observed as a sudden increase of the tunnelling current and it was associated to a complete loss of the dielectric properties (hard breakdown, HBD). However, with the oxide thickness reduction (< 5nm), besides HBD, two new breakdown modes less severe than HBD were identified: soft breakdown (SBD) [Miranda 00] and progressive breakdown (PBD) [Monsieur 02]. The analysis of these new failure modes and its impact on the device and circuit performance is specially important since it has been demonstrated that, depending on the breakdown hardness and the circuit functionality, the failure of a given device can or cannot lead to the failure of the corresponding circuit, especially on digital circuits [Avellan 04, Kaczer 00, Rodriguez 03, Kerber 06, A4 Ribes 08]. The main difference between the different modes is the time scale of the BD triggering and the post-BD current level. Post-breakdown current is the main difference between SBD and HBD. For the first case, the post-breakdown current is some orders of magnitude smaller than

for HBD. In the same way, the damage area observed is lower for the SBD than for the HBD as it was reported in [Alam 00, Miranda 01]. PBD is generally observed in oxides with a thickness lower than 2,5 nm. In this case, a progressive increase of current is observed before the BD is achieved [Monsieur 01]. PBD corresponds to the same phenomenon than SBD and HBD, in fact is considered their precursor, but at different time scales.

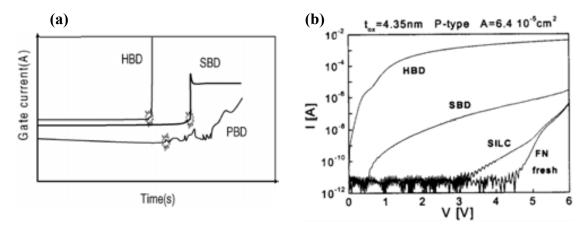

Figure 1.12a illustrates typical I-t curves measured when the different BD modes are observed during the application of a constant voltage stress. On the other hand, figure 1.12b illustrates typical post-BD I-V curves of the different failure modes (SILC, SBD and HBD) observed after applying ramped voltage stresses in a 2,5nm thick SiO<sub>2</sub> based stack. The I-V curve measured before any stress (labelled as FN, fresh) is also included as reference.

Figure 1.12: a) Different modes of breakdown: HBD, a sudden increase of the current is observed; SBD, an increase of the current, lower than HBD mode, is observed; PBD, a progressive increase of current is observed [Ribes 05]; b) Typical stages in the I-V characteristic of an ultrathin gate oxide as the degradation proceeds. FN refers to Fowler-Nordheim behavior of a fresh oxide; SILC to Stress Induced Leakage Current, SBD to Soft Breakdown and HBD to Hard Breakdown [Miranda 01]

With the advent of high-k dielectric films as a replacement of the SiO<sub>2</sub>/SiON dielectric, new questions come up due to the presence of a dual dielectric layer that includes an high-k and interfacial SiO<sub>2</sub> layer. Among them, at which layer breakdown is initially triggered, if any?, has still not found an unified answer. Some authors claim that BD is initially triggered at the interfacial layer [Aguilera 06, Bersuker 08, Suñe 10, Ribes 10, Raghavan 12]. However, others authors point to the high-k layer [Okada 08, Nigam 09]. This concern is one of the topics analyzed in this thesis and will be studied in more detail in chapter IV.

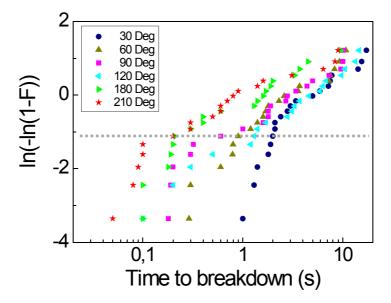

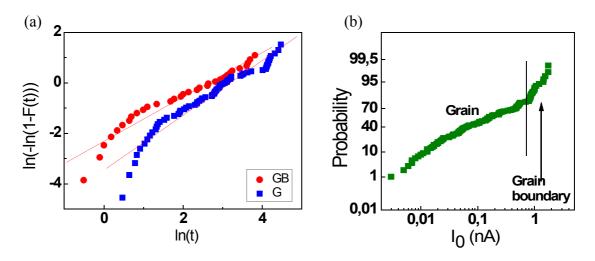

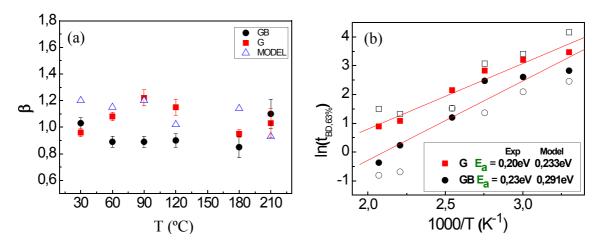

#### 1.3.2 Statistical distribution of BD

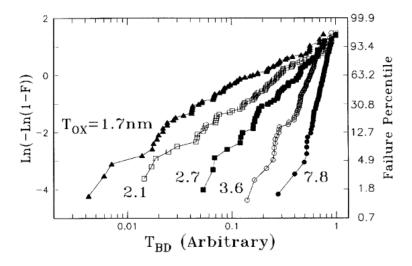

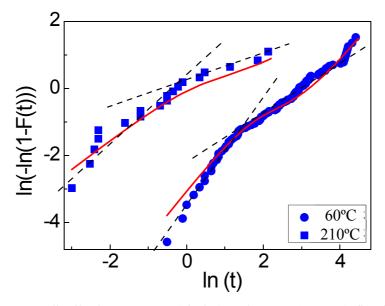

It is also important to remark that BD is a random event. Therefore, it should be described from a statistical point of view. In this sense, gate oxide breakdown is recognized as a statistical process which is normally characterized by Weibull distribution (1.5).

$$F(t) = 1 - \exp\left[-\left(\frac{t}{\eta}\right)^{\beta}\right] \tag{1.5}$$

Where F(t) is the cumulative failure function, t is the random variable,  $\beta$  is the shape parameter (usually called Weibull slope) that indicates the data dispersion, and  $\eta$  is the scale factor (time for a 63% probability of BD occurrence). Equation (1.6), known as Gumbel plot, is easily deduced from equation (1.5):

$$\ln\left[-\ln(1-F(t))\right] = \beta \ln(t) - \beta \ln(\eta) \tag{1.6}$$

Equation (6) is usually used to represent the  $t_{BD}$  cumulative distribution for the dielectric breakdown analysis. Plotting  $\ln[-\ln(1-F(t))]$  vs.  $\ln(t)$ , a linear behavior is observed and  $\beta$  and  $\eta$  can be easily extracted since  $\beta$  is the slope of the plot and  $t = \eta$  when the line is crossing through origin. In figure 1.13, an example of Gumbel plot, where typical  $t_{BD}$  distributions of  $SiO_2$  layers are represented for several oxide thicknesses, is shown [Wu 05].

Figure 1.13: Typical normalized t<sub>BD</sub> distributions for different oxide thicknesses [A75 Wu 05]

Trap generation rates (which clearly determine the formation of the percolative path, and therefore, the time to BD,  $t_{BD}$ ) have been shown to be strongly dependent on the temperature [Moazzami 89, Chen 99], affecting consequently, to the Weibull parameters ( $\beta$  and  $\eta$ ). Therefore, temperature dependence is also an important factor to be considered when  $t_{BD}$  reliability predictions have to be made. However, the temperature dependence of TDDB (Time Dependence Dielectric Breakdown) distributions remains an open issue. Although it is commonly assumed that temperature dependence follows the Arrhenius law (1.7) due to its simplicity, there is some evidence that non-Arrhenius behaviour may occur in ultra-thin oxides [Wu 05]. In this thesis, an Arrhenius relationship is assumed to analyze the temperature dependence of TDDB (see chapter IV).

$$t_{BD}(T) = A \cdot e^{\left(\frac{E_a}{RT}\right)}$$

(1.7)

Where A is a constant, E<sub>a</sub> is the activation energy for the deffects to be generated, k<sub>B</sub> is the Boltzmann constant, T is the temperature (in kelvin) and R is the gas constant.

### 1.3.3 Dielectric Breakdown and Resistive Switching

In section 1.3.1, dielectric breakdown was treated as an important reliability problem in microelectronics. However, it is worthy to mention that it may even be useful for some applications. Traditionally, this phenomenon was considered to be irreversible. Nevertheless, some authors have demonstrated that BD could be occasionally reversible in SiO<sub>2</sub> [Nafria 93, Suñe 93, Porti 02] if the current through the oxide is limited. Recent works have shown that, under current limited conditions, dielectric BD in ultrathin Hf based high-k gate dielectrics can also be a reversible phenomenon exhibiting two interchangeable conductivity states when the correct stress scheme is applied [Crespo-Yepes 09, Crespo-Yepes 10, Rodriguez 12]. On one hand, from the reliability point of view, the existence of two conductivity states indicates that the insulator properties of the dielectric can be at least partially recovered. On the other hand, this effect reveals similar characteristics with the resistive switching (RS) phenomenon observed in Metal-Insulator-Metal/Semiconductor (MIM/MIS) structures [Crespo-Yepes 09, Crespo-Yepes 11].

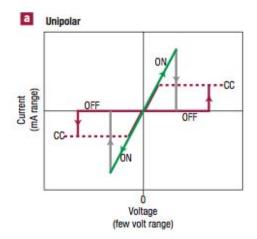

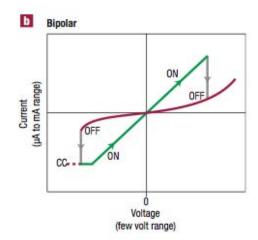

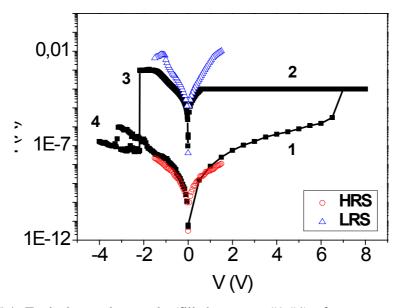

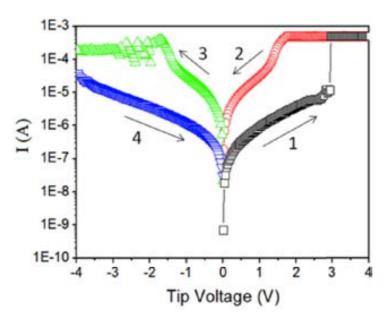

RS is known as the capability of some materials to switch between two conductivity states, denominated Low Resistive State (LRS) and High Resistive State (HRS). Although this phenomenon is known since a long time ago, in the early 1960s [Gibbons 64, Simmons 67], lately, it is becoming a prominent issue and it is being widely investigated since it is one of the best solutions to overcome the several technical limits of memory technology [Valov 11]. Among next generation of non-volatile memory (NVM), which uses RS as operating principle, random access memory (ReRAM) technology is standing out. This technology is one of the most promising emerging nonvolatile memories because of its simple structure, high switching speed, high scalability, low power and good compatibility with the standard CMOS process [Waser 07]. ReRAM is featured with reversible switching between two resistance states in metal oxide based materials normally implemented in MIM/MIS structures. [Waser 07, Sawa 08]. Normally, an initial "forming process" as a current-limited electric breakdown is needed to get the switch between both states. RS can be classified in terms of current-voltage (I-V) characteristics into two types: unipolar (nonpolar) and bipolar. It is called unipolar, or nonpolar, when the switching procedure does not depend on the polarity of the voltage and current signal. Otherwise, it is called bipolar when SET and RESET processes are operated using opposite voltage polarities. In order to show bipolar switching behavior, the structure of the system must have some asymmetry, such as different electrode materials or the voltage polarity during the initial electroforming step [Waser 07]. Figure 1.14 illustrates the I-V curves characteristics for unipolar and bipolar switching.

Figure 1.14: I-V characteristics for (a) unipolar and (b) bipolar switching. CC denotes the compliance current often needed to limit the ON current [94]

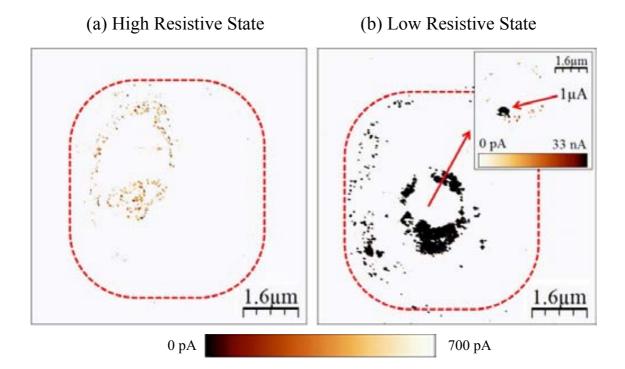

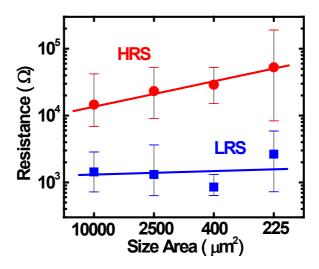

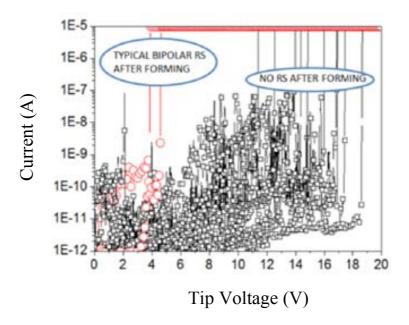

In addition, the physical mechanisms leading to the creation of the conductive path are also used to categorize the RS [Sawa 08, Waser 09]. Taking into account that the resistive state will be mainly determined by the electrical properties of the dielectric, the election of the convenient material is a challenge for the new generation of NVM based in MIM/MIS structures. HK materials also are being hardly investigated to be used into the ReRAM technology. However, there are still many open questions about the physics related to its working principle and many efforts are focused on the understanding about the switching mechanism. Recent studies have shown that the switching mechanism observed in some high-k dielectrics is based on a conductive filament (CF) through the insulator stack that can be created/destroyed depending on the applied voltage [Rozenberg 04]. However, other works suggest that the HRS should be related to the conduction of multiple filaments since I<sub>HRS</sub> has been observed to scale with the device area [Xu 08]. Besides these reports about filamentary-type resistive switching, a so called homogeneous interface-type switching, which is observed at the interface between different complex oxides and the metal electrode, has been reported [Asanuma 09]. With the aim of clarifying the origin of the conductance, in chapter V, different CAFM analysis of the RS phenomenon in HfO<sub>2</sub> films are presented.

### 1.4 Standard characterization techniques

In order to study the degradation process and to evaluate the electrical properties and failure mechanisms of micro- and nanoelectronic devices, electrical tests are applied to test structures. This section is devoted to introduce the characterization techniques used to perform this analysis.

The expected lifetime of MOS devices under normal operating conditions could be of several years, therefore, the time required to deteriorate the gate oxide under these conditions is too large to be investigated in reasonable time scales. For this reason, it is necessary to have a methodology that allows to extrapolate the expected lifetime.

According to this, accelerated electrical test are commonly used to degrade the electrical properties of test structures and to study the reliability of gate oxides. The electrical tests normally used consist of the application of voltages or the injection of currents (called electrical stresses) through test structures (generally MOS capacitors or transistors [Pierret 90]) and the measurement of the evolution of their electrical properties. Next lines will briefly describe the most common tests used in dielectric yield and reliability assessment. A more exhaustive description can be found at [Martin 98].

Constant Voltage Stress (CVS) is one of the most common electrical tests. It consists of the application of a constant voltage to the stack and the measurement of the gate current evolution over time until the dielectric breakdown is triggered. In this test, BD is detected as an increase of the leakage current through the gate. This type of stress is used to analyze the TDDB by measuring  $t_{\rm BD}$ , that is, the time-to-breakdown.

Constant Current Stress (CCS). In this case a constant current is injected until breakdown. The voltage evolution over time is monitored through a voltage versus time curve. Breakdown is detected when a sudden drop of voltage ocurs. This stress is used to measure the injected charge to BD and, in some cases, t<sub>BD</sub>, as well.

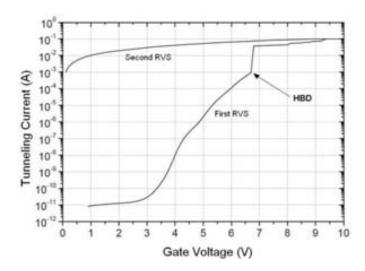

Ramped Voltage Stress (RVS). A continuous increasing voltage is applied to the structure until BD. During this test, gate current is measured and plotted in current-voltage (I-V) characteristics. BD is detected as a sudden increase at the gate current. Figure 1.15 illustrates two typical I-V curves measured during two consecutive RVS to a capacitor with a 3.5nm thick SiO<sub>2</sub> layer [Lanza 10]. During the first voltage ramp, a sudden increase of current is observed at 0.5V, which is related to a HBD phenomenon. Afterwards, the gate dielectric loses its isolator properties showing very high post-BD currents, as it can be checked in the second I-Vcurve.

Figure 1.15: I-V curves obtained during the application of two consecutive RVS on 3.5 nm thick SiO<sub>2</sub> based capacitor [68].

The accelerated electrical tests mentioned above are usually applied to gate devices, that is, to MOS capacitors or transistors with a gate electrode, and are usually referred as

standard characterization techniques. These tests allow to measure the global electrical properties through the gate. Therefore, they provide spatially average information of the oxide electrical properties. However, information at the nanometric scale is not available. To get a nanoscale analysis and to achieve a better understanding of the electrical properties, alternative techniques with a nanoscale resolution are required. Next section is devoted to describe those techniques.

#### 1.5 Tools with a nanometer resolution

In the case of ultra-reduced dimension transistors, inhomogeneities and microstructural defects must be taken into account because intrinsic parameter fluctuations associated to the discrete nature of matter and charge could have a strong impact on the global behaviour of the device. Local variations of electrical properties could have an important influence on the leakage current characteristics leading to a significant device-to-device variability. The main sources of variability are related to atomic level phenomena, the operating environment and the manufacturing process. Foremost among them are: Random Dopant Distribution (doping introduces a random distribution of discrete ions which create potential fluctuations affecting to the threshold voltage); Line Edge Roughness (roughness in the surface of gate transistor, due to intrinsic imperfections of the photolithographic process, can affect to the effective channel length); and, surface roughness (atomic-scale thickness variations which leads to fluctuations in the gate current and device threshold) [Asenov 08, Zhang 00, Aikaterini 12]. Furthermore, the homogeneity of the morphological and electrical properties of the high-k layer can also affect the variability of electrical properties of scaled devices [Bayerl 11]. Considering that these phenomena occur at the sub-micron scale, macroscopic analyses (standard characterization techniques) are not suitable, because local variations of the electrical properties and failure mechanism (which also happen at the nanoscale), as for example dielectric breakdown, cannot be measured. For this reason, measurement techniques with high lateral resolution (at the same scale as the material inhomogeneities) become indispensable for a better understanding.

On this matter, different microscopy techniques have been used to investigate the properties of different materials at a nanometer scale. The choice of the technique depends on the objectives pursued and the sample that wants to be analysed. *Scanning Electron Microscopy* (SEM), for example, is a very useful tool to analyse surfaces and to obtain information about the composition of the sample. [Goodhew 88]. *Transmission Electron Microscopy* (TEM) allows to obtain internal structural information (arrangement of atoms, defects, etc.) and compositional features of a sample using different imaging and diffraction techniques. Moreover, over the past few years, transmission electron microscopy has been revolutionized by the development of new techniques, among which *electron holography* allows to obtain magnetic and electrical information [Midgley 09, Midgley 01].

However, although both techniques are very powerful tools which have allowed to obtain useful information about different properties of the sample, SEM and TEM experiments need to be operated in vacuum chambers and require a laborious and complicated preparation of the surface under analysis. In this direction, since 1990s, a

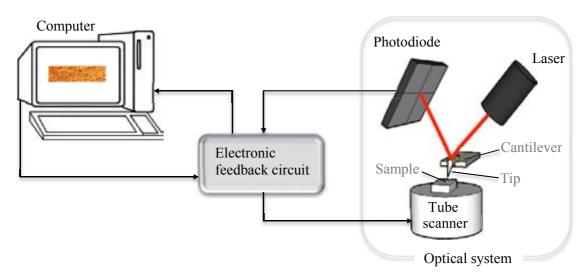

new family of microscopes, called Scanning Probe Microscope (SPM), have been started to be used to investigate topographical and electrical properties of surfaces. SPM, are a family of microscopes that basically collect topographical images using an extremely sharp tip that scans the sample. SPMs allow to obtain a sub-nanometric lateral and vertical resolution as well as 3D quantitative information of the investigated surface. Scanning Tunneling Microscope (STM) [Binnig 86] and Atomic Force Microscope (AFM) are two outstanding scanning probe microscopes.

STM was developed in 1981 and their inventors, Gerd Binnig and Heinrich Rohrer (at IBM Zürich), received the Nobel Prize in Physics in 1986. The invention of the Scanning Tunnelling Microscope was a landmark in the birth of nanotechnology. It was the first instrument that generated atomic images of surfaces [Binnig 83]. STM is based on the concept of quantum tunnelling, being able to detect the tunnelling current that flows between a metallic tip and a conductive sample, separated just few nanometers, when a bias is applied between both. This current, which depends on the tip-sample distance, is used to evaluate the topographical properties of the surface. The exponential dependence of the current on the tip-sample distance implies that small changes in topography lead to large changes in current. Its high resolution (~ 1 Å) permits to image atoms within materials. In spite of this high resolution, STM shows some drawbacks. It is necessary to keep in mind that the measured topography (obtained form the measurement of the tunnelling current) does not only depend on the sample morphology but also on the electronic properties of different atoms of the surface, which can also lead to changes in the tunnelling current. Therefore, any change measured in the topography could be caused by changes in the electrical or morphological properties, being not possible to know exactly its origin. Moreover, STM can only measure conductive surfaces and requires ultrahigh vacuum environments. In order to overcome some of these limitations, the AFM was developed in 1986. AFM resolution is not as high as with a STM, but sample preparation is not required and a wide range of materials can be analyzed (not just conductive samples as for STM). The ability to operate on insulating surfaces is essential for the development and testing of nanoscale devices. Although specific environments are not required to work with AFM, they can be useful to improve some kind of measurement resolution [Lanza 10'].

There are several AFM based techniques especially focused on the simultaneously topographical and electrical characterization of materials used in semiconductor industry [Oliver 08, De Wolf 01, Kalinin 07]. Some of the most relevant are the Conductive Atomic Force Microscope (CAFM) [Murrell 93], Spreading Resistance Microscope Scanning (SSRM) [De Wolf 99, De Wolf 98], Kelvin Probe Force Microscope (KPFM) [Nonnenmacher 91] and Scanning Capacitance Microscope (SCM) [Martin 88, Dreyer 95)]. Conceptually, CAFM and SSRM are quite similar. In both cases a bias is applied to a conductive tip and the resulting tip-sample current is measured simultaneously to the topography. However, CAFM is usually used to measure the properties of the sample collecting the tunneling current through an oxide layer, whilst SSRM measures the spreading resistance, derived from the measured

electrical current, to determine primarily the distribution of dopant concentrations within semiconductors. Although all of them have been shown to be powerful tools for characterizing the electrical properties of dielectrics and semiconductors at the nanoscale, since the topic of this thesis is mainly focused in the CAFM, our attention will be aimed to this technique.

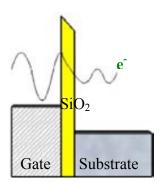

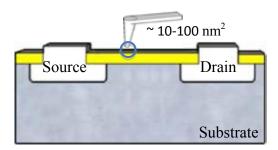

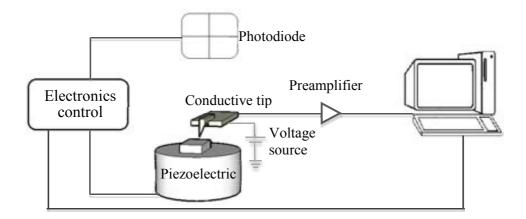

CAFM, also known under the term tunneling atomic-force microscopy (TUNA), has been developed in the mid 1990s in order to measure currents through thin silicon oxide gate dielectrics at the nanometer scale [O'Shea 95, Murrell 93, Welland 93, Ruskell 96, Olbrich 98, Kremmer 02]. Simultaneously to the topography, the current between tip and sample is also recorded when a bias is applied to the sample. The CAFM is usually used to simulate a MOS structure, which is the most common test structure in these fields. The tip (which is conductive) of the CAFM plays the role of the gate electrode (Figure 1.16). It means that a MOS capacitor with an area that corresponds to the contact area between the tip and the sample is defined. Taking into account that this area is of the order of 10-100nm<sup>2</sup>, the properties of the oxide can be investigated at the nanoscale range.

Figure 1.16: Illustration of an experimental configuration to characterize MOS structures at the nanoscale with CAFM. (~10-100 nm<sup>2</sup>). When the tip of the CAFM contacts with the surface, a MOS structure of nanometric dimensions is simulated.

In contrast to the STM, the CAFM can measure electrical properties on insulating surfaces and, moreover, the measured current is not influenced by the surface morphology of the dielectric. This shows the CAFM as a superior tool to study the quality of dielectric thin films [Olbrich 98', Olbrich 99, Frammelsberger 06]. Since its inception, CAFM has demonstrated to be useful to characterize electrical properties of ultrathin SiO<sub>2</sub> films before, during and after degradation at a nanometer scale [Porti 01, Degraeve 01', Pakes 04, Wu 06, Fiorenza 06, Polspoel 07]. It has been used to measure the dielectric strength of SiO<sub>2</sub> gate oxides [Olbrich 98, Ruskell 96], local variations of the gate oxide thickness [Olbrich 98] and the electrical degradation and breakdown of ultra thin SiO<sub>2</sub> gate oxide layers subjected to electrical stress [X. Blasco 05] and irradiation [Wu 07]. The local character (~100 nm²) of the BD event was experimentally demonstrated [Porti 02] for the first time with the CAFM. In the same way, this tool has been useful to observe that, in spite of the local character of the BD phenomenon, it can be propagated (depending on the BD hardness) laterally affecting neighbor areas

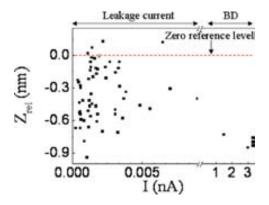

[Blasco 05', Wu 08]. This propagation, as well as the post-BD conduction, was observed to increase with the level of current injected during the stress [Porti 04]. That is, with the hardness of the BD event. On the other hand, statistical analyses performed at the nanoscale also confirms that  $t_{\rm BD}$  follows a Weibull distribution [Sire 07, Fiorenza 07, Erlbacher 11], as it is observed at device level.

In the early 2000, the CAFM was used to investigate high-k materials [Landau 00]. However, it was not until a few years ago that its use was widespread to study high-k based gate stacks. The first works were published in 2004. There, the electrical homogeneity of HfO<sub>2</sub> and HfAlO<sub>x</sub> films on silicon was studied [Blasco 04, Petry 04]. Afterwards, a variety of single high-k dielectrics or high-k based stacks (based, for example, on Al<sub>2</sub>O<sub>3</sub> [Lanza 09], Pr<sub>2</sub>O<sub>3</sub> [Lo Nigro 03], ZrO<sub>2</sub> [Engel-Herbert 09], Ta<sub>2</sub>O<sub>5</sub> [Atanassova 09], SrTiO<sub>3</sub> [Kraya 12]) were successfully analyzed confirming the CAFM technique as a powerful tool to study their electrical properties at nanoscale [Yanev 08]. For example, CAFM has been extensively used to study the electrical properties of asgrown (before an electrical stress) high-k dielectrics. Conduction by trap assisted tunneling (TAT) due to the higher density of native defects in high-k materials [McKenna 11, Aguilera 06, Lanza 11] or morphological and electrical changes due to its polycrystallization (as a consequence of an annealing treatment at temperature T<sub>A</sub> during the fabrication process) are some examples of its applications. At this respect, this technique has been helpful to show the contribution of dominant TAT and FN current transport mechanism to the oxide leakage [Uppal 09, Lanza 11] as well as the impact of the T<sub>A</sub> [Lanza 07, Lanza 11]. It has been shown that the electrical inhomogeneity of Hf-based high-k layers increase for annealing temperatures above the crystallization temperature [Blasco" 05] as a consequence of the high-k layer polycrystallization [Bayerl 11', Lanza 07, Pawlak 10]. Other issues, as the conductions mechanisms through high-k stacks with SiO<sub>2</sub> as interfacial layer [Aguilera 07] or the effect of gate dopant diffusion on the leakage current of Poly-Si/HfO<sub>2</sub> stacks [Yu 07], also have been studied through CAFM. Moreover, this technique has allowed identifying different conduction regimes in as-grown HfO<sub>2</sub>/SiO<sub>2</sub> stack, at different voltage ranges, which cannot be detected by standard electrical characterization techniques [Blasco 05].

Studies performed with CAFM about the degradation of the gate stack can be also found in the literature. Some of these works suggest that this degradation is due to the pre-existing electron traps in polycrystalline high-k gate stacks, which are the precursors of stress-induced defects [Paskaleva 08]. Recently, nanoscale electrical characterization has been performed to determine the cumulative failure distribution of TDDB [Wu 08, Erlbacher 11], which shows a bimodal shape for bilayer stacks [Delcroix 11].

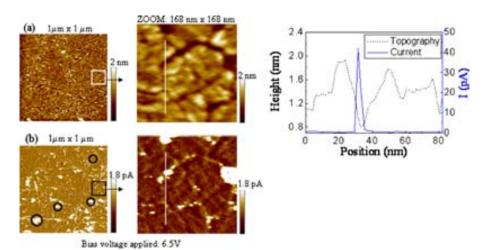

Nowadays, the microscopic study of Resistive Random Access Memory (ReRAM) devices is being also a current issue [Polspoel 12, Muenstermann 10, Son 08, Jeong 12, Bersuker 11, Lanza 12]. A resistive switching phenomenon has become especially significant as an option for future memory devices. The study of the transport

characteristics of reduced oxide metal nanoparticle interfaces, as well as the influence of the contact size at the interface can be used to understand resistive switching mechanisms and the effects of ohmic and tunnel contacts to switching phenomena [Kraya 12]. The nanoscale current distribution and switching properties of thin film heterostructures, as well as the investigation of the scaling capabilities of MIM structures, which exhibit whether filamentary or interface-type switching, can also be addressed by using CAFM technique [Muenstermann 10].

In addition to the study of gate oxides, CAFM is used for other topics in microelectronics fields. An important application of CAFM, although this is not the topic of this thesis, is its use to modify surfaces and create structures on the nanometer scale by local oxidation [Kim 11, Xie 06, Kremmer 03] allowing even to fabricate nanoscale devices [Campbell 95, Held 97, Tachiki 02]. Also new emerging materials as graphene or carbon nanotubes are being studied using this technique [Ahmad 11, Noël 10]

Summarizing, AFM techniques and specially CAFM, have been shown to be powerful tools for researching the electrical properties and reliability of gate dielectrics (SiO<sub>2</sub> and high-k). In this thesis, the CAFM technique has been used to analyse the influence of the polycrystallization on the morphology, electrical properties and reliability of a HfO<sub>2</sub> based gate stack. The impact of an electrical stress is also evaluated. Finally, RS in MIM structures based on HfO<sub>2</sub> was also investigated.

# CHAPTER II

# Atomic Force Microscope and related techniques

This chapter is devoted to the Atomic Force Microscope (AFM) and related techniques, concretely the Conductive Atomic Force Microscope (CAFM) and the Kelvin Probe Force Microscope (KPFM), both used in this thesis. The work principles of AFM and its related techniques are introduced, as well as the modifications that must be applied to the conventional AFM to measure the electrical properties of surfaces. In addition, since the tips are a critical point to perform AFM measurements, a section is dedicated to discuss them in detail. Finally, a presentation of the different set-up used in this thesis is presented.

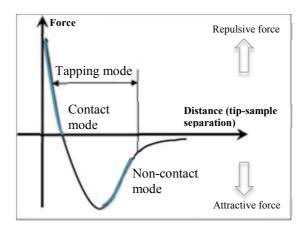

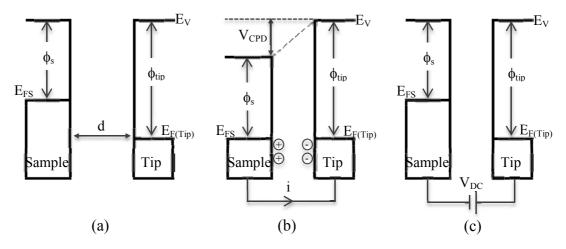

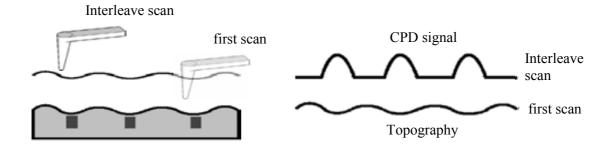

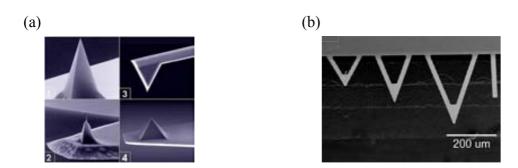

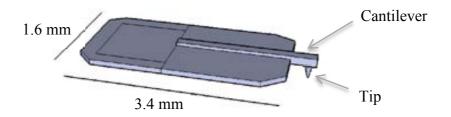

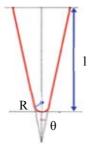

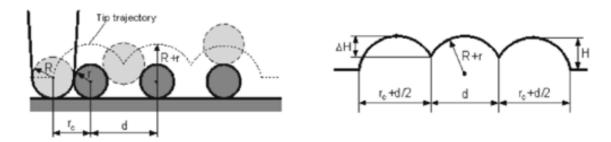

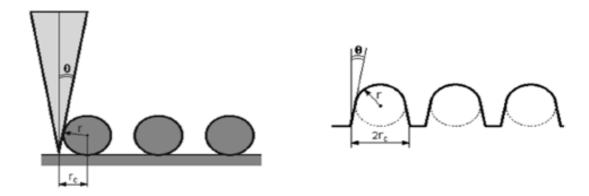

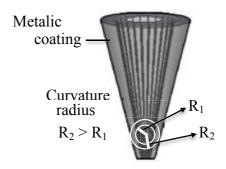

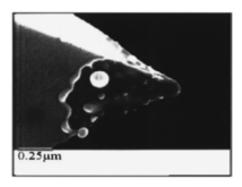

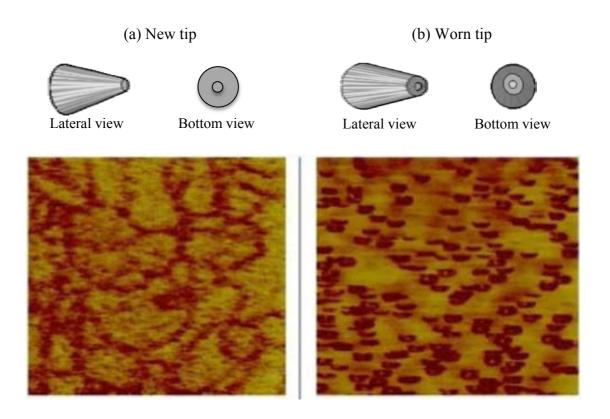

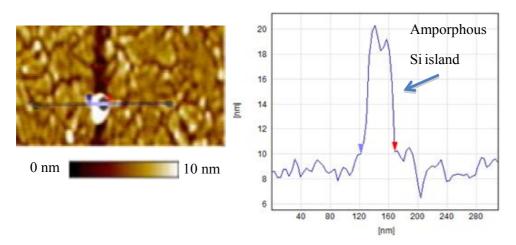

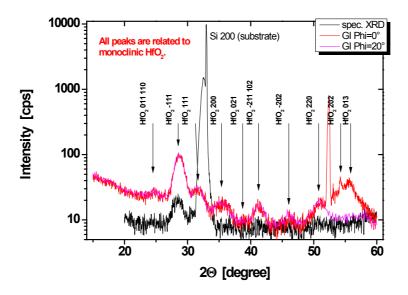

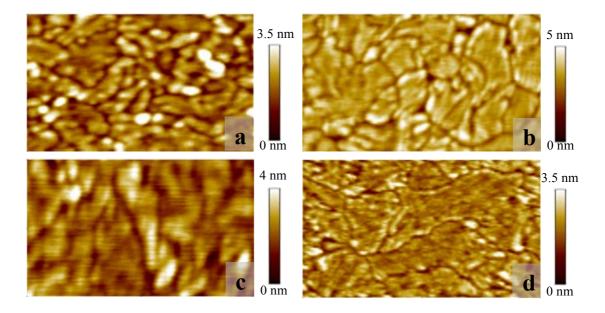

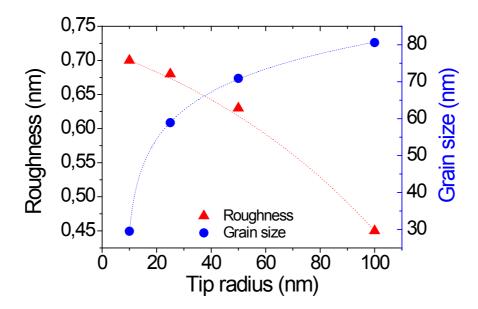

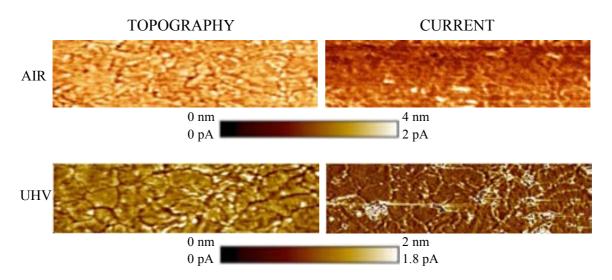

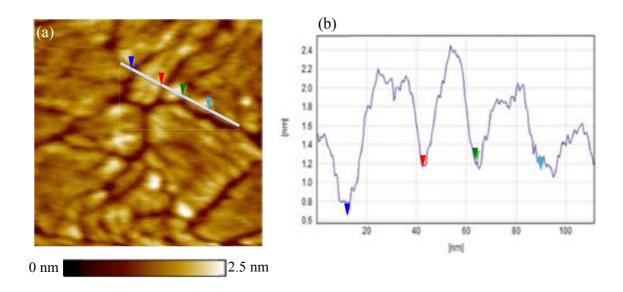

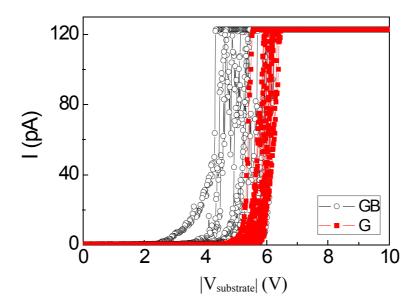

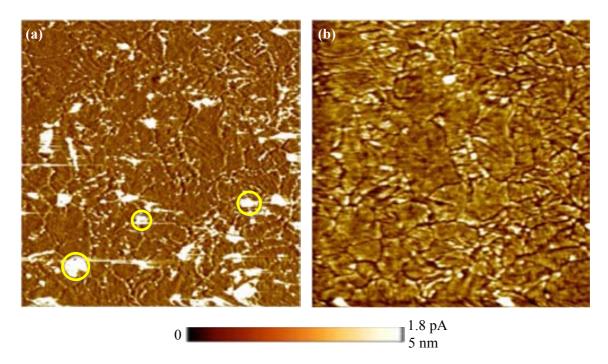

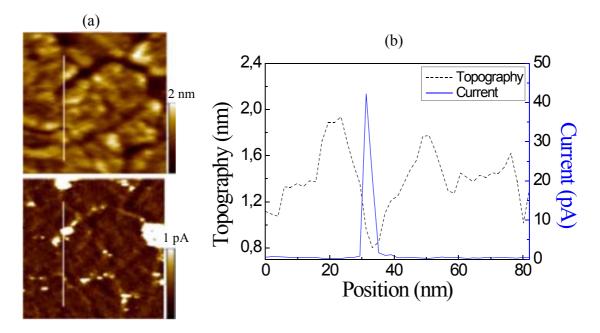

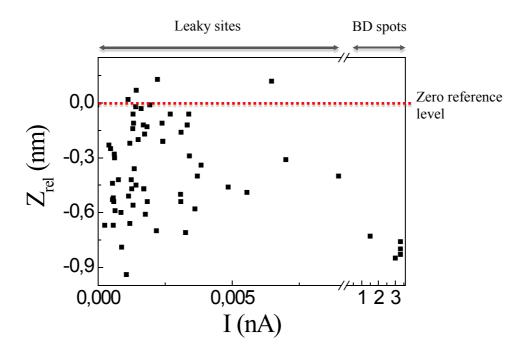

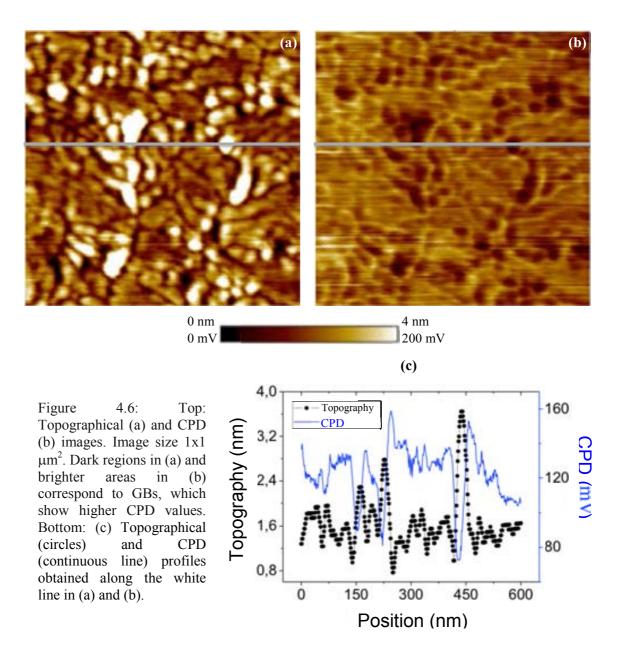

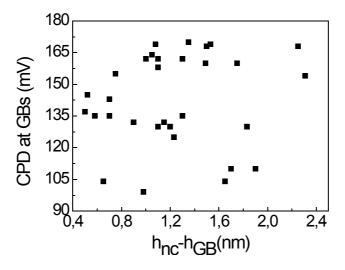

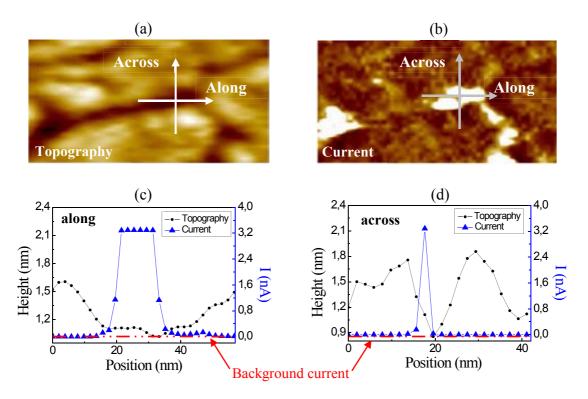

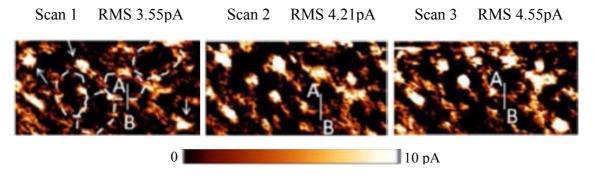

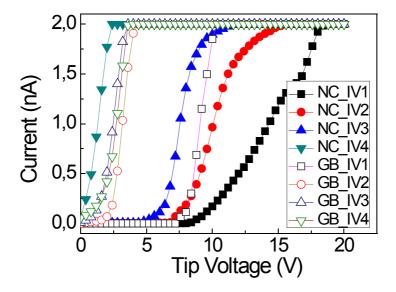

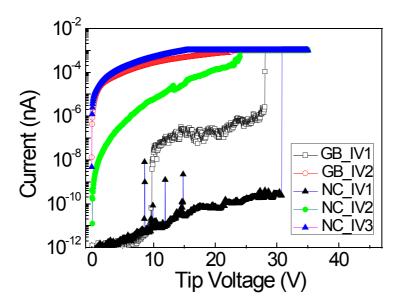

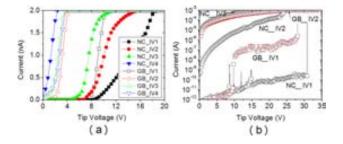

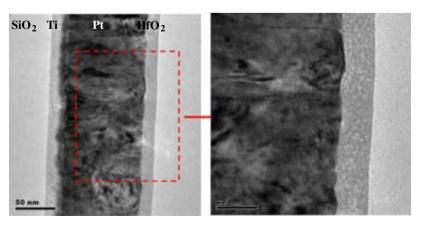

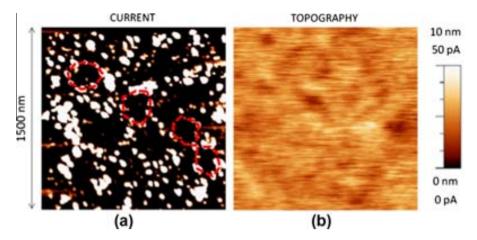

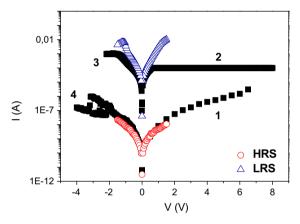

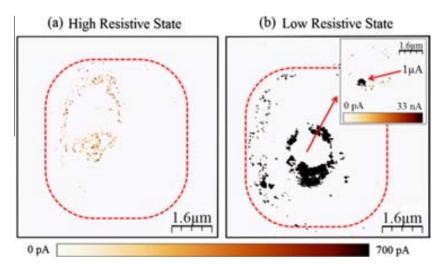

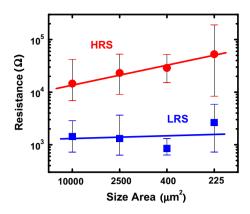

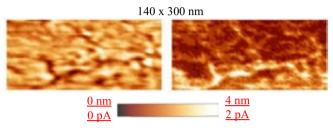

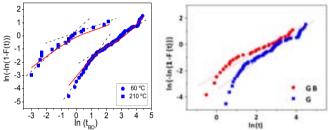

### 2.1 Atomic Force Microscope