ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

# **Analysis of Bidirectional Switch Power Modules for Matrix Converter Application**

Thesis dissertation presented to obtain the qualification of

Doctor of Philosophy in Electronic and Telecommunication

Engineering from the Electronic Engineering

Department of Universitat Autònoma de Barcelona (UAB)

by:

## José-Luis Gálvez Sánchez

Supervised by: Xavier Jordà Sanuy

Assigned Tutor: Gabriel Abadal Berini

Cerdanyola del Vallès, July 2017

# Acknowledgement

I would like to thank the Power Devices and Systems group of the Barcelona Microelectronics Institute of the National Microelectronics Centre (IMB - CNM) - CSIC headed by Prof. José Millán for given me the opportunity to join to this excellent team always at the forefront of technology and research in the power electronics field.

I would specially like to thank my supervisor Dr. Xavier Jordà for his support and excellence in pursuing an objective.

I would like also to thank the colleagues of the Power Devices and Systems group for their time for discussion and suggestions on the work of this thesis and their friendship and fellowship, in particular Mr. David Sánchez, Dr. Miquel Vellvehí, Prof. Philippe Godignon, Dr. Nacho Cortés, Dr. Xavier Perpinyà, Dr. Francesc Madrid, Dr. Pablo Fernández, Dr. Marcel Placidi, Dr. Pierre Brosselard.

I would like also to thank Dr. Miguel Ángel José Prieto and colleagues from the Universidad de Oviedo (Gijón) for their collaboration in the project.

I have only gratitude and warm words towards my friends and my family, parents and sisters, and, especially to Maica, Clara, Joana i Damià for their patience and effort in supporting me during all this time.

I am happy to share with all you this work.

# **Content**

| 1.  | Introdu | ection                                                  | 1         |

|-----|---------|---------------------------------------------------------|-----------|

| 1.  | 1. Ba   | ckground of the Thesis                                  | 1         |

| 1.2 | 2. Th   | e Matrix Converter and its Implementation               | 2         |

| 1.3 | 3. Aiı  | ms and Structure of the Thesis                          | 13        |

| 2.  | Analys  | is of the BDS's Commutation Phenomena                   | 17        |

| 2.  | 1. BD   | OS Topology                                             | 17        |

|     | 2.1.1.  | Diode Bridge BDS                                        | 18        |

|     | 2.1.2.  | Common Emitter BDS                                      | 18        |

|     | 2.1.3.  | Common Collector BDS                                    | 19        |

|     | 2.1.4.  | BDS with RB-IGBTs                                       | 19        |

|     | 2.1.5.  | BDS with SiC Power Devices                              | 22        |

|     | 2.1.6.  | Bidirectional Bi-Polar Junction Transistor (B-TRAN)     | 23        |

|     | 2.1.7.  | Dual-gate Normally-ON GaN HEMT                          | 24        |

| 2.2 | 2. Cu   | rrent Commutation                                       | 24        |

|     | 2.2.1.  | Basic Current Commutation                               | 25        |

|     | 2.2.2.  | Current Direction Based Commutation                     | 25        |

|     | 2.2.2   | 2.1. Four-step Current Commutation                      | 25        |

|     | 2.2.2   | 2.2. Other-step Current Commutation                     | 27        |

|     | 2.2.2   | 2.3. Current Sign Detection                             | 28        |

| 2.3 | 3. BD   | OS Commutation Process Analysis                         | 29        |

|     | 2.3.1.  | Introduction                                            | 29        |

|     | 2.3.1   | .1. Diode and IGBT Static Characteristics               | 30        |

|     | 2.3.1   | .2. Diode and IGBT Dynamic Characteristics              | 32        |

|     | 2.3.2.  | Study of Commutation Processes Based on a Four-step Com | nmutation |

|     | Strateg | y                                                       | 34        |

|     | 2.3.2   | 2.1. Type I Commutation (BDS-Aa to BDS-Ba)              | 35        |

|     | 2.3.2   | 2.2. Type II commutation (BDS-Aa to BDS-Ba)             | 39        |

|     | 2.3.2   | 2.3. Type III Commutation (BDS-Ba to BDS-Aa)            | 43        |

|     | 2.3.2   | 2.4. Type IV Commutation (BDS-Ba to BDS-Aa)             | 44        |

| 2.4 | 4 Su    | mmary                                                   | 47        |

| 3. | Charac   | terisation of BDS Devices                                       | 49  |

|----|----------|-----------------------------------------------------------------|-----|

|    | 3.1. BD  | S Static Characterisation                                       | 49  |

|    | 3.1.1.   | Static Device Measurement                                       | 49  |

|    | 3.1.2.   | Static Device Modelling                                         | 53  |

|    | 3.2. BD  | S Switching Test Circuit                                        | 54  |

|    | 3.2.1.   | Power Circuit                                                   | 55  |

|    | 3.2.2.   | Control Circuit                                                 | 56  |

|    | 3.2.3.   | Design and Measuring Considerations                             | 59  |

|    | 3.2.3    | .1. Power Circuit Considerations                                | 59  |

|    | 3.2.3    | .2. Control circuit considerations                              | 60  |

|    | 3.2.3    | .3. Current and Voltage Probes                                  | 61  |

|    | 3.3. Dy  | namic BDS Characterisation                                      | 66  |

|    | 3.3.1.   | Dynamic Device Modelling                                        | 72  |

|    | 3.4. Sui | nmary                                                           | 76  |

| 4. | Power    | Losses Computation Method                                       | 79  |

|    | 4.1 Int  | roduction                                                       | 79  |

|    | 4.2 De   | scription of the Semiconductor Power Losses Calculation Method  | 80  |

|    | 4.3 Po   | wer Losses Evaluation Method for a VSI                          | 83  |

|    | 4.3.1    | IGBT Conduction Losses                                          | 85  |

|    | 4.3.2    | IGBT Switching Losses                                           | 86  |

|    | 4.3.3    | Total IGBT Power Losses                                         | 87  |

|    | 4.3.4    | Diode Conduction Losses                                         | 87  |

|    | 4.3.5    | Diode Switching Losses                                          | 90  |

|    | 4.3.6    | Total Diode Power Losses                                        | 90  |

|    | 4.4 Im   | plementation of the VSI Power Losses Calculation                | 91  |

|    | 4.4.1    | Validation of the Power Losses Calculation Method               | 93  |

|    | 4.5 Su   | nmary                                                           | 95  |

| 5. | Evalua   | tion of the Semiconductor Power Losses within Matrix Converters | 97  |

|    | 5.1 Ma   | trix Converter Power Losses                                     | 97  |

|    | 5.1.1    | Identification of the commutation types                         | 99  |

|    | 5.1.2    | IGBT Conduction Losses                                          | 101 |

|    | 5.1.3    | IGBT Switching Losses                                           | 101 |

|    | 5.1.4    | Total IGBT Power Losses                                         | 104 |

|    | 5.1.5    | Diode Conduction Power Losses                                   | 105 |

| ;     | 5.1.6       | Diode Switching Losses                                              | . 107  |

|-------|-------------|---------------------------------------------------------------------|--------|

| ;     | 5.1.7       | Total Diode Power Losses                                            | . 110  |

| 5.2   | 2 1         | mplementation of the MC Power Losses Calculation                    | . 110  |

| ;     | 5.2.1       | Description of the Power Losses Functions                           | . 112  |

|       | 5.2         | 2.1.1 Conduction Losses Function                                    | . 112  |

|       | 5.2         | 2.1.2 Switching Losses Function                                     | . 113  |

| 5.3   | 3 ]         | Losses Calculation and Analysis                                     | . 115  |

| :     | 5.3.1       | Losses Comparison between Venturini and DS SVM Modulation           | . 116  |

| ;     | 5.3.2       | Losses Analysis for the Relevant Application Parameters of the MC   | . 117  |

| ;     | 5.3.3       | Losses Analysis for Different Power Devices Technologies            | . 120  |

| 5.4   |             | Summary                                                             | . 125  |

| 6.    | Bidiı       | rectional Switch Intelligent Power Module (BDS-IPM) for Matrix Conv | erter  |

| Appli | icatio      | ons                                                                 | . 129  |

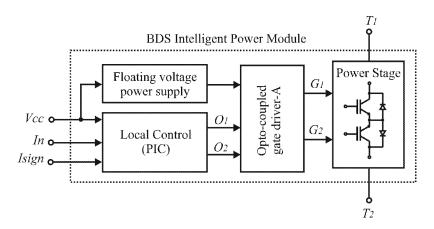

| 6.1   | . 1         | ntroduction to the BDS-IPM                                          | . 129  |

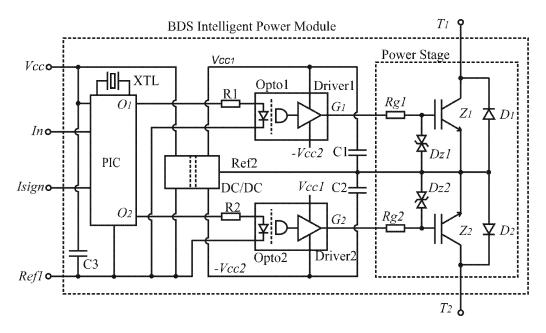

| 6.2   | 2. \$       | Structure the BDS-IPM                                               | . 131  |

| (     | 6.2.1       | . BDS-IPM Block Diagram                                             | . 131  |

| (     | 6.2.2       | Detailed BDS-IPM Schematic                                          | . 132  |

| 6.3   | s. 1        | BDS-IPM Electrical Characteristics                                  | . 135  |

| (     | 6.3.1       | . BDS-IPM Static Characteristics                                    | . 135  |

| (     | 6.3.2       | BDS-IPM Dynamic Characteristics                                     | . 136  |

| 6.4   | ļ. <i>1</i> | Application Example of the BDS-IPM: Three-Phase to One-Phase M      | latrix |

|       | (           | Converter                                                           | . 140  |

| (     | 6.4.1       | . Test Converter Power Circuit                                      | . 140  |

| (     | 6.4.2       | . Measurement Circuit and Techniques                                | . 144  |

| (     | 6.4.3       | . Current Direction Detection Circuit                               | . 146  |

| (     | 6.4.4       | Protection Circuit                                                  | . 147  |

| (     | 6.4.5       | . High Level Control Circuit                                        | . 147  |

| (     | 6.4.6       | Experimental Behaviour of the BDS-IPMs in a Test MC                 | . 151  |

| 6.5   | 5.          | Summary                                                             | . 152  |

| 7.    | Sum         | mary and Conclusion                                                 | . 155  |

| Refer | ence        | S                                                                   | . 159  |

| A. ]  | Lists       | of Acronyms and Symbols                                             | . 169  |

| A.    | 1 l         | List of Acronyms                                                    | . 169  |

| A.2   | 2 1         | List of Symbols                                                     | . 170  |

| B. Sv | witching Energy Losses Calculation  | . 172 |

|-------|-------------------------------------|-------|

| B.1   | IGBT                                | . 173 |

| B.2   | Diode                               | . 178 |

| C. M  | latrix Converter Modulation Methods | . 181 |

| C1.   | Venturini Algorithm                 | . 181 |

| C2.   | DS SVM Algorithm                    | . 182 |

# **List of Figures**

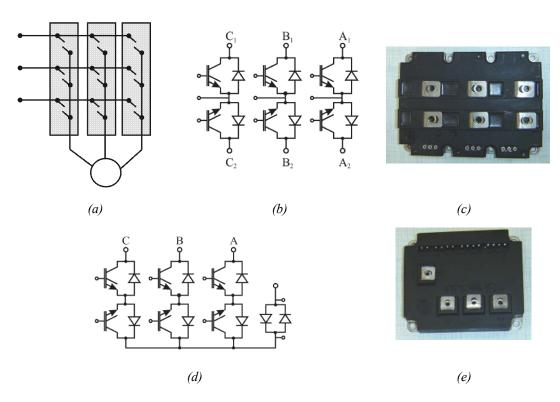

| Figure 1-1   | Matrix Converter topology                                                    |

|--------------|------------------------------------------------------------------------------|

| Figure 1-2   | Possible BDS discrete implementations                                        |

| Figure 1-3   | a) Scheme of a complete MC in one package. b) An EUPEC & SIEMENS             |

|              | 7.5 kW Matrix Converter module. c) Schematic of the Power stage              |

|              | module, R, S, T are the input phases; W, U, V, are the output phases and     |

|              | G <sub>R1</sub> till G <sub>W3</sub> are the eighteen IGBT gate terminals    |

| Figure 1-4   | a) 22kW prototype MC module. b) Schematic of the power stage module .        |

|              |                                                                              |

| Figure 1-5   | a) Scheme of a MC output leg in a single package. b) Schematic diagram       |

|              | of the internal circuit of DIM600EZM17-E000. c) Dynex module                 |

|              | DIM600EZM17- E000, 1700V, 600A. d) Schematic diagram of the                  |

|              | internal layout of SML300MAT06. e) Semelab module, SML300MAT06               |

|              | 600V, 300A11                                                                 |

| Figure 1-6a) | BDS of the MC in a single package. b) Dynex module, DIM400PBM17              |

|              | 1700V, 400A                                                                  |

| Figure 2-1   | A three-phase to three-phase MC circuit                                      |

| Figure 2-2   | Diode bridge BDS                                                             |

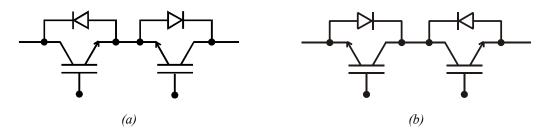

| Figure 2-3   | BDS realisation: a) Common Emitter, b) Common Collector                      |

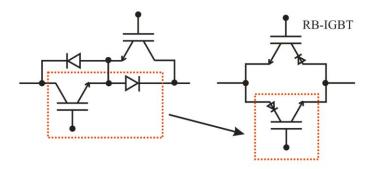

| Figure 2-4   | BDS is built with two anti-parallel RB-IGBTs                                 |

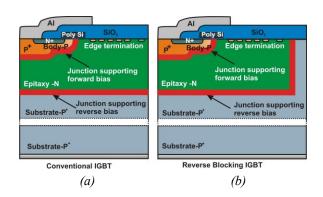

| Figure 2-5   | Basic cell and termination of a conventional a) IGBT; b) RB-IGBT 20          |

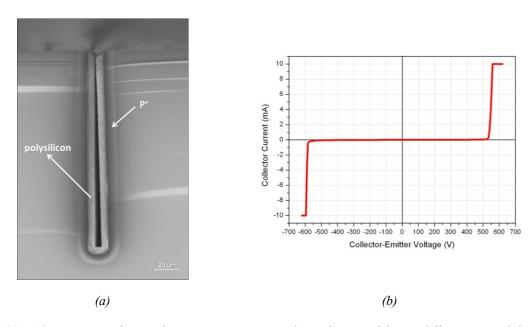

| Figure 2-6   | a) SEM picture of a trench region cross section. The uniformity of the P+    |

|              | diffusion around the walls with a depth of around 10 $\mu m$ can be          |

|              | appreciated; b) Bidirectional blocking characteristics of the fabricated RB- |

|              | IGBT                                                                         |

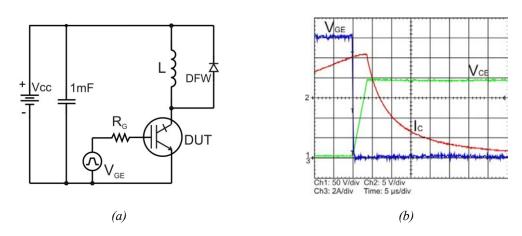

| Figure 2-7   | Turn-off of a non-irradiated RB-IGBT a) Test circuit; b) Waveforms 22        |

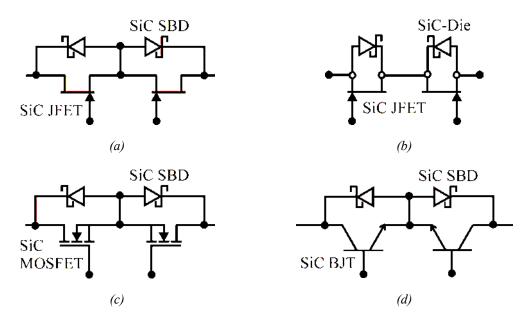

| Figure 2-8   | Full SiC BDS realisations based on. a) Normally-Off SiC JFETs in             |

|              | common source with anti-parallel SiC Schottky diodes; b) Normally-Or         |

|              | SiC JFETs in common drain with built-in diodes; c) SiC MOSFETs in            |

|              | common source with anti-parallel SiC SBDs; d) SiC BJTs in common             |

|              | emitter with anti-parallel SiC SBDs                                          |

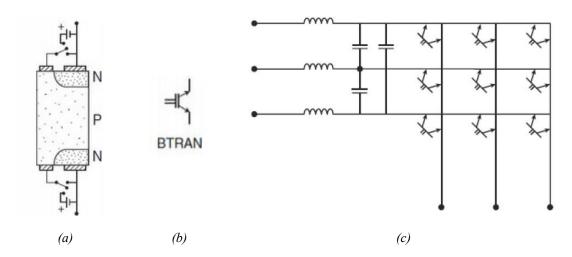

| Figure 2-9  | a) B-TRAN topology; b) B-TRAN circuit symbol; c) Matrix Converter                                              |

|-------------|----------------------------------------------------------------------------------------------------------------|

|             | application [56]                                                                                               |

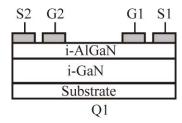

| Figure 2-10 | Concept of a dual-gate normally-ON GaN HEMT device [57] 24                                                     |

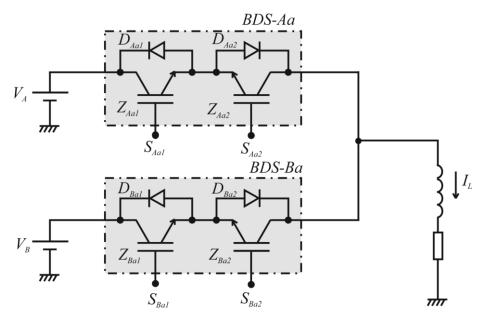

| Figure 2-11 | Schematic of a two-phase to single-phase MC                                                                    |

| Figure 2-12 | Four-step current commutation between two BDSs. a) Timing diagram                                              |

|             | when the direction of I <sub>L</sub> is positive; b) State representation. (SAa and                            |

|             | SBa are the switch control signals provided by microcontroller or DSP                                          |

|             | and SAa1, SAa2, SBa1, SBa2 are the gate control signals of each IGBT                                           |

|             | within the BDS, the direction of I <sub>L</sub> is positive (solid lines) when the                             |

|             | current flows towards the load and negative (dashed lines) when it flows                                       |

|             | towards the input voltage source.)                                                                             |

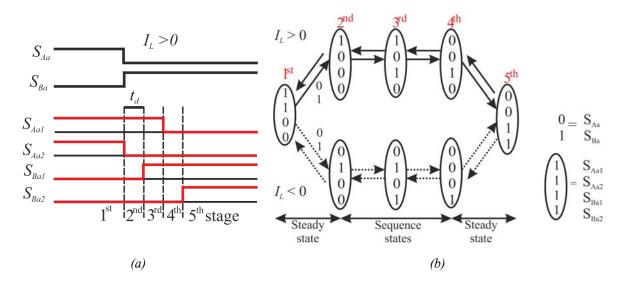

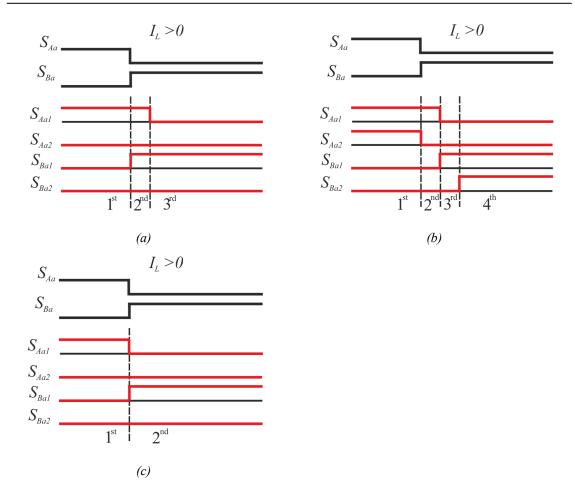

| Figure 2-13 | Timing diagram of several current commutation methods when the                                                 |

|             | direction of load current is positive. a) Two-step; b) Three-step and c)                                       |

|             | Single-step                                                                                                    |

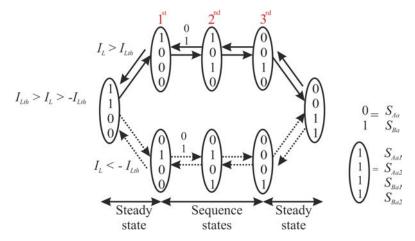

| Figure 2-14 | Two-step commutation using current threshold detection. I <sub>Lth</sub> is the                                |

|             | current threshold level                                                                                        |

| Figure 2-15 | Current sense detection based on the voltage drop across the BDS emitter                                       |

|             | point                                                                                                          |

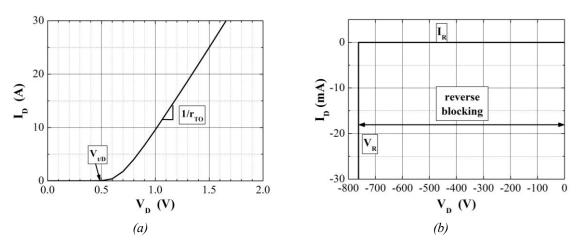

| Figure 2-16 | Diode I-V characteristics: a) forward biased, b) reverse biased 30                                             |

| Figure 2-17 | IGBT I-V characteristic: a) output characteristic, b) transfer characteristic                                  |

|             | 31                                                                                                             |

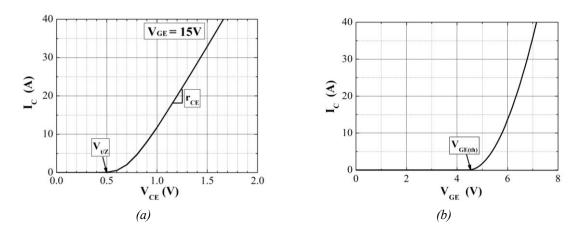

| Figure 2-18 | BDS I-V characteristics: a) forward and reverse conducting, b) forward                                         |

|             | and reverse blocking                                                                                           |

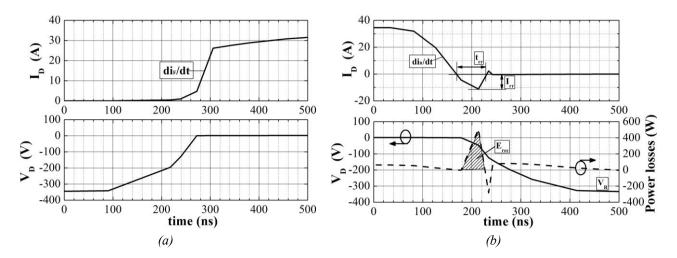

| Figure 2-19 | Switching voltage, current and power losses waveforms of diode. a) Turn-                                       |

|             | on, b) Turn-off and reverse recovery losses                                                                    |

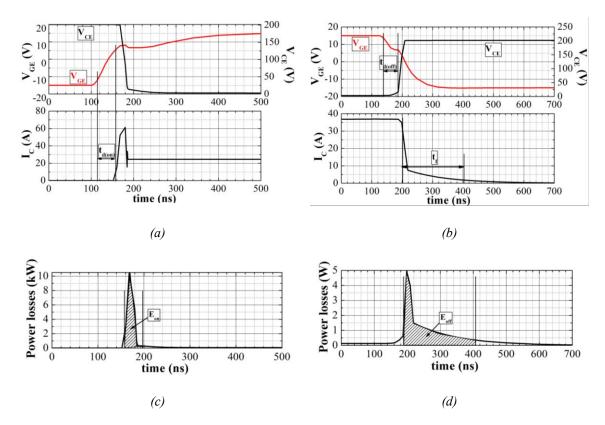

| Figure 2-20 | Switching IGBT waveforms: a) Turn-on, b) Turn-off, Energy losses c)                                            |

|             | Turn-on, d) Turn-off                                                                                           |

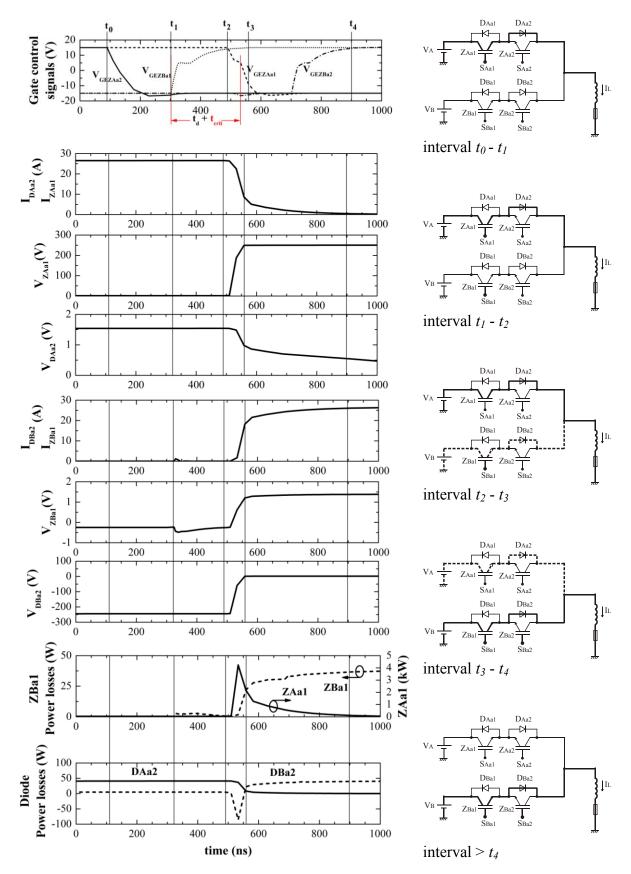

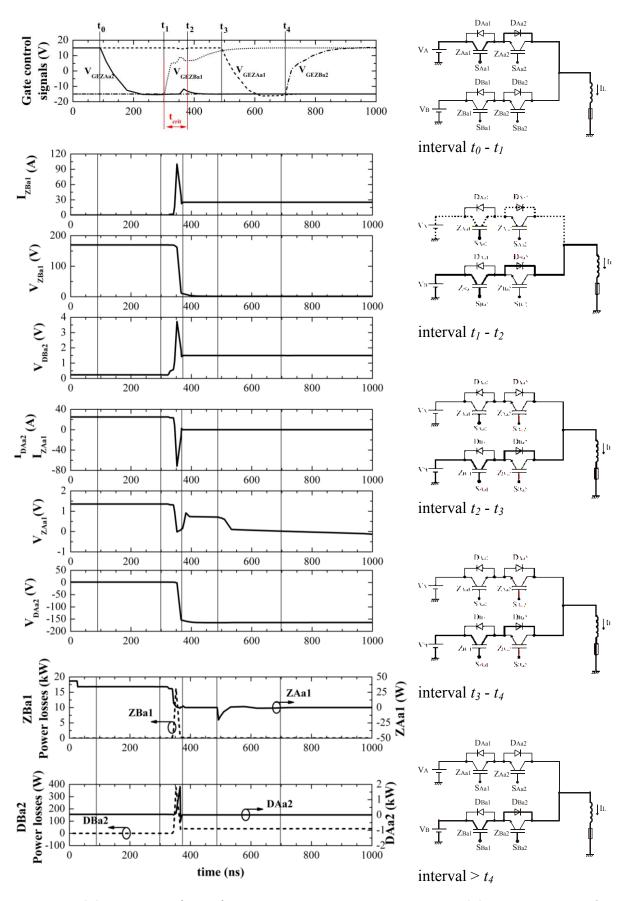

| Figure 2-21 | Device waveforms of type I commutation process                                                                 |

| Figure 2-22 | Type I current path                                                                                            |

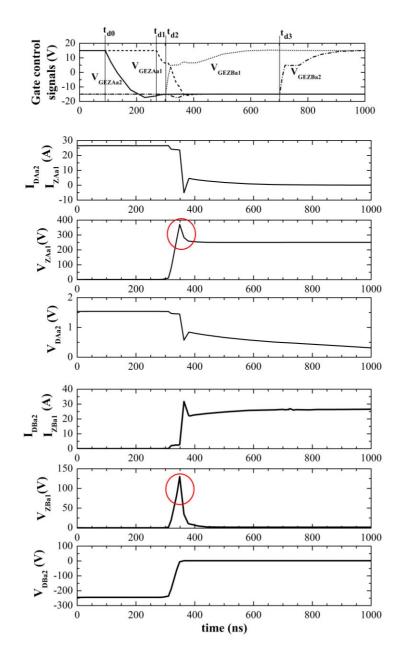

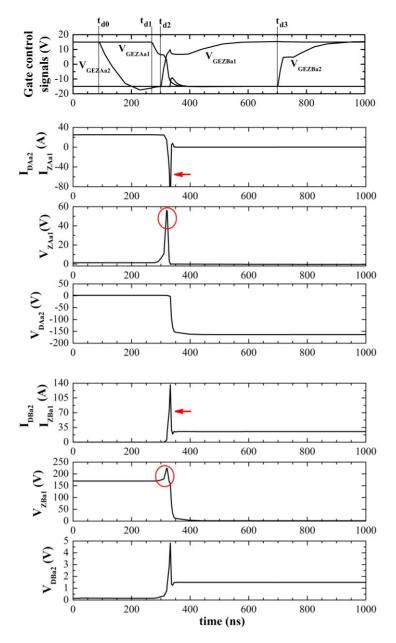

| Figure 2-23 | Device waveforms under a failure in the Type I commutation. Time                                               |

|             | instants $t_{d0}$ , $t_{d1}$ , $t_{d2}$ ; $t_{d3}$ and $t_{d4}$ correspond to the activation of the respective |

|             | control gate signals                                                                                           |

| Figure 2-24 | Device waveforms of type II commutation process                                                                |

| Figure 2-25 | Type II current path 42                                                                                        |

| Figure 2-26 | Device waveforms under a failure in the Type II commutation. Time                                              |

|-------------|----------------------------------------------------------------------------------------------------------------|

|             | instants $t_{d0}$ , $t_{d1}$ , $t_{d2}$ ; $t_{d3}$ and $t_{d4}$ correspond to the activation of the respective |

|             | control gate signals                                                                                           |

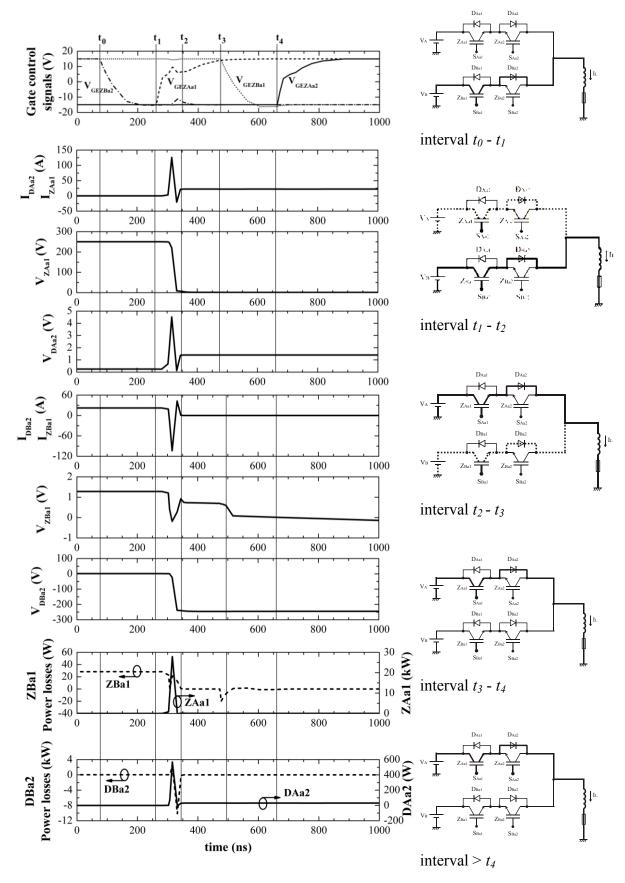

| Figure 2-27 | Device waveforms of type III commutation process                                                               |

| Figure 2-28 | Type III current path                                                                                          |

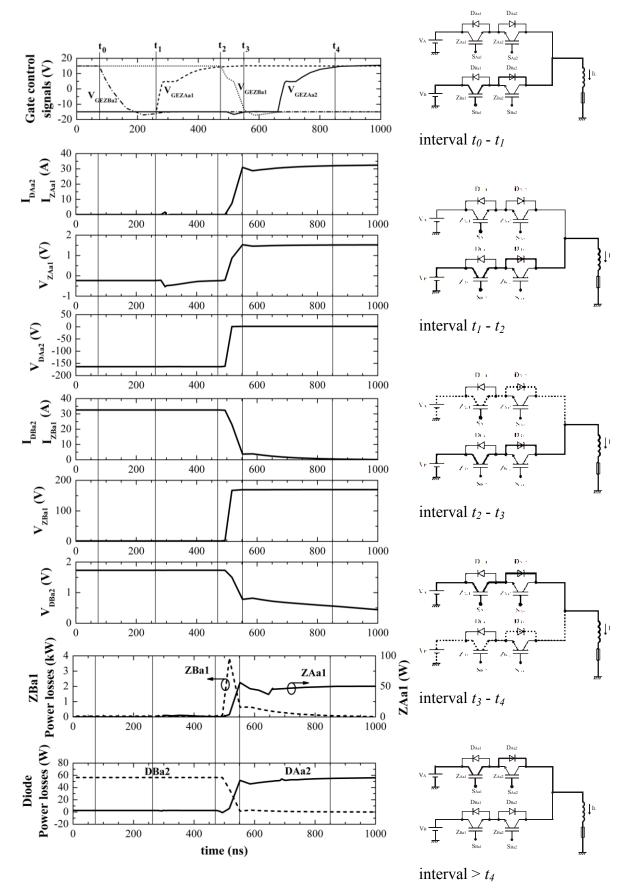

| Figure 2-29 | Device waveforms of type IV commutation process                                                                |

| Figure 2-30 | Type IV current path                                                                                           |

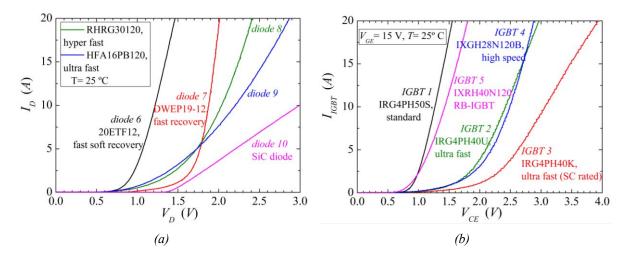

| Figure 3-1  | Static characteristics of the discrete devices a) diodes; b) IGBTs and RB-                                     |

|             | IGBTs                                                                                                          |

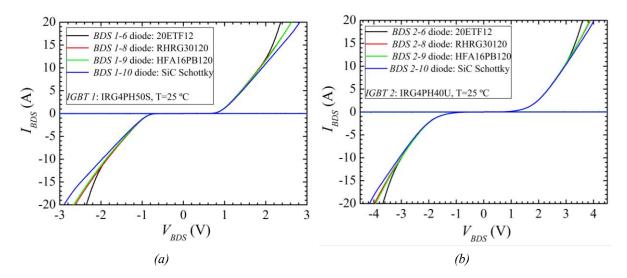

| Figure 3-2  | Comparative of the static characteristics of discrete common emitter BDSs                                      |

|             | a) standard IGBT + different diodes; b) ultra fast IGBT + different diodes                                     |

|             |                                                                                                                |

| Figure 3-3  | Comparative of the static characteristics of discrete common emitter BDSs                                      |

|             | a) ultra fast (SC) IGBT + different diodes; b) different IGBTs + soft                                          |

|             | recovery diode; c) different IGBTs + hyper fast diode, d) different IGBTs                                      |

|             | + ultra fast diode, e) different IGBTs + SiC diode; f) RB BDS 52                                               |

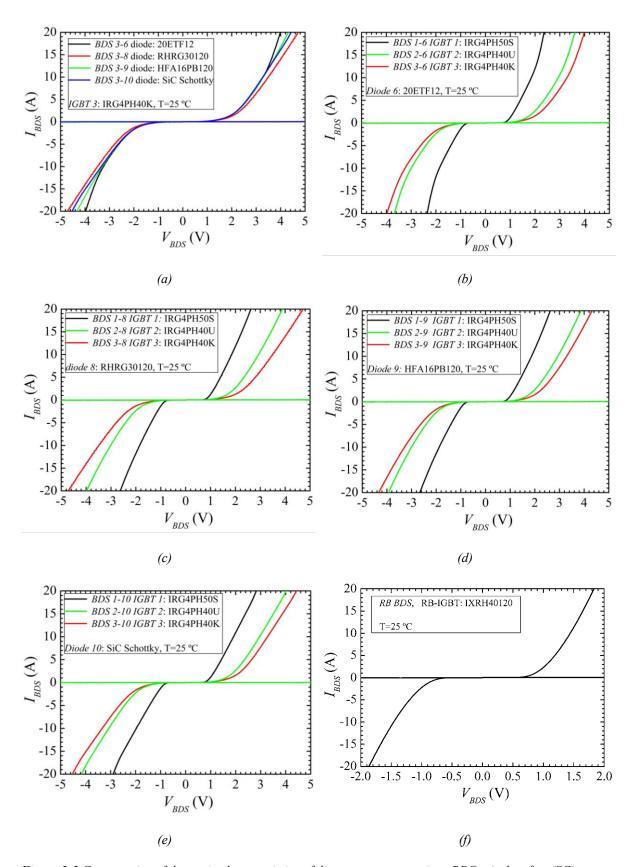

| Figure 3-4  | Comparison among the voltage drop of the built BDSs at 20 A 53                                                 |

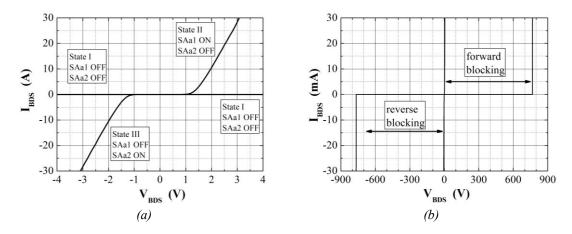

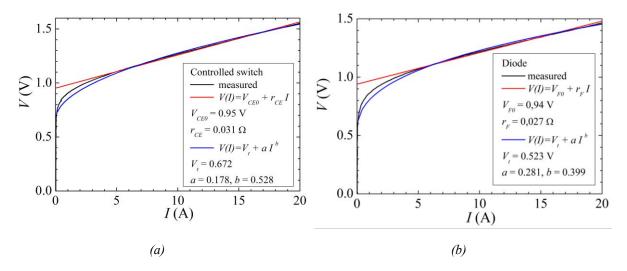

| Figure 3-5  | Static characterisation and modelling a) controlled switch, IGBT 1                                             |

|             | (IRG4PH50S), b) diode 6 (20ETF12) fast recovery diode                                                          |

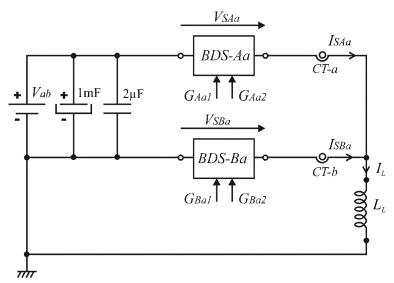

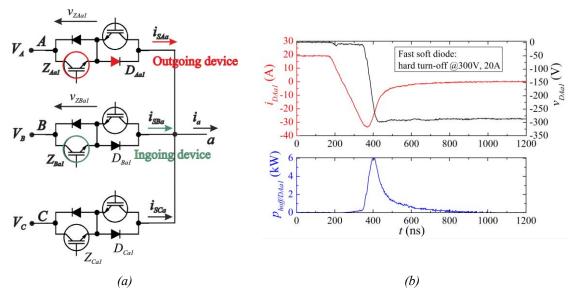

| Figure 3-6  | Schematic of the power stage of the experimental rig                                                           |

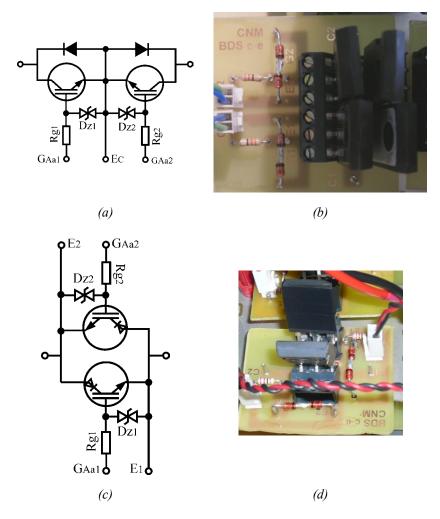

| Figure 3-7  | CE BDS commutation cell a) schematic; b) discrete implementation. RB                                           |

|             | BDS commutation cell c) schematic; d) discrete implementation 56                                               |

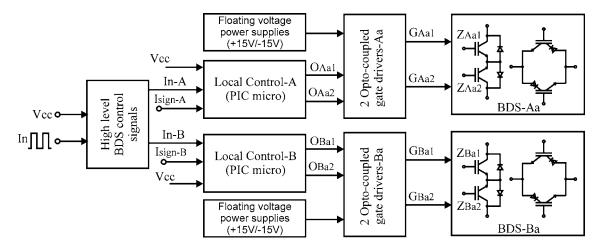

| Figure 3-8  | Block diagram of the universal BDS control board for a two-phase to one-                                       |

|             | phase MC                                                                                                       |

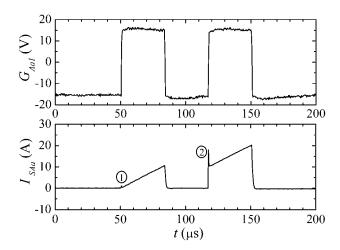

| Figure 3-9  | GAa1 gate driver signal and BDS-Aa current are set by an In signal with                                        |

|             | frequency of 15 kHz and duty cycle of 50 %                                                                     |

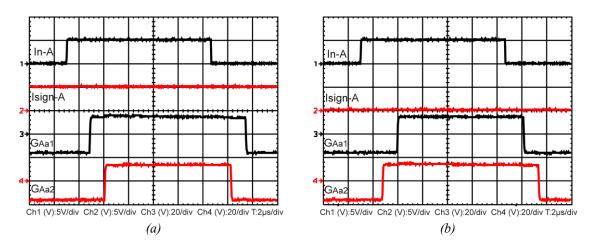

| Figure 3-10 | Universal BDS control board operation. Gate control signals for a signal                                       |

|             | demand on BDS-Aa, a) Ising-A $> 0$ . b) Ising $< 0$                                                            |

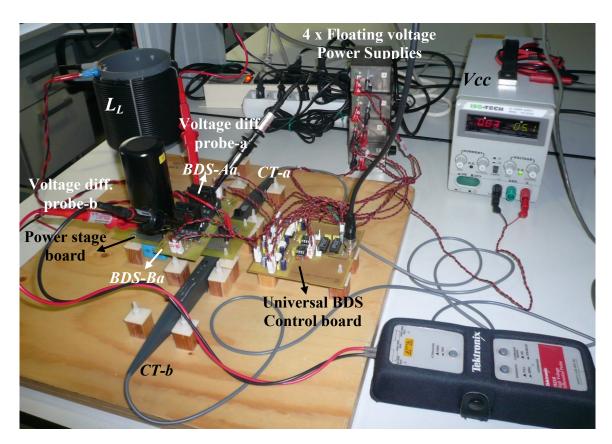

| Figure 3-11 | Experimental BDS switching test circuit                                                                        |

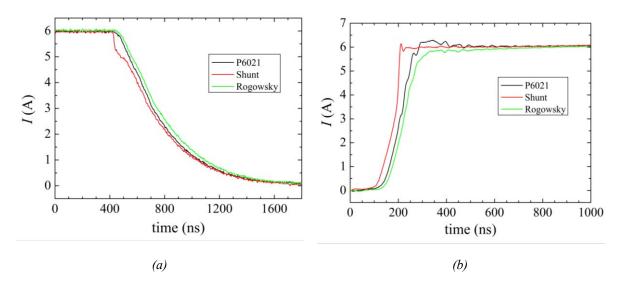

| Figure 3-12 | Current measurement with different current probes during IGBT a) turn-                                         |

|             | off, b) turn-on. 62                                                                                            |

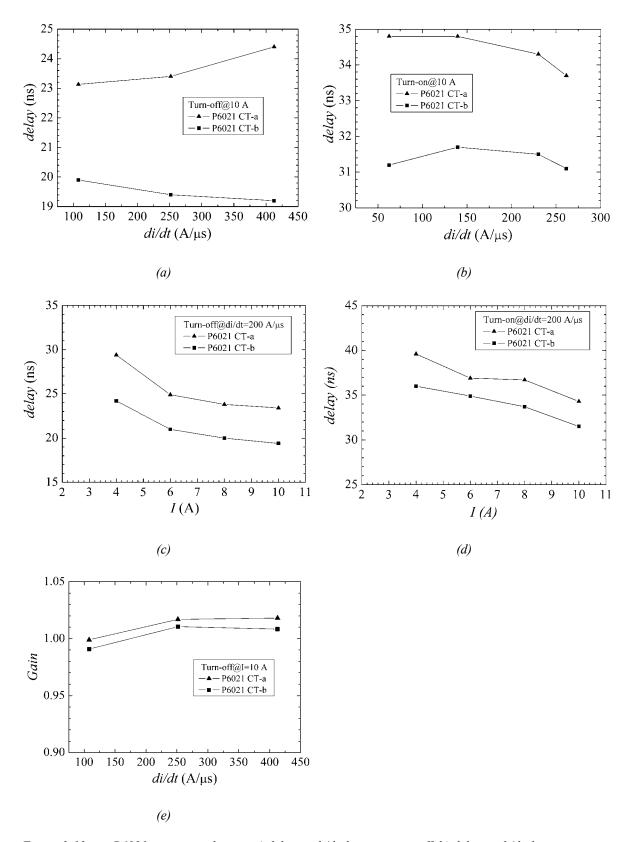

| Figure 3-13 | P6021 current probe test. a) delay vs di/dt during a turn-off. b) delay vs                                     |

|             | di/dt during a turn-on. c) delay vs current during a turn-off. d) delay vs                                     |

|             | current during a turn-on. e) gain vs di/dt during a turn-off                                                   |

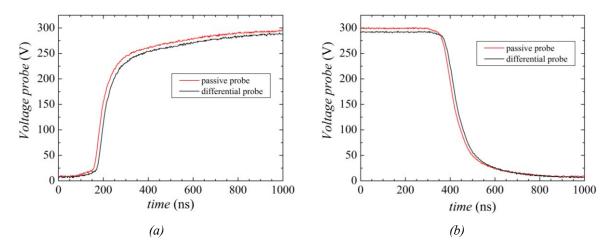

| Figure 3-14 |                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------|

|             | off. b) IGBT turn-on.                                                                                 |

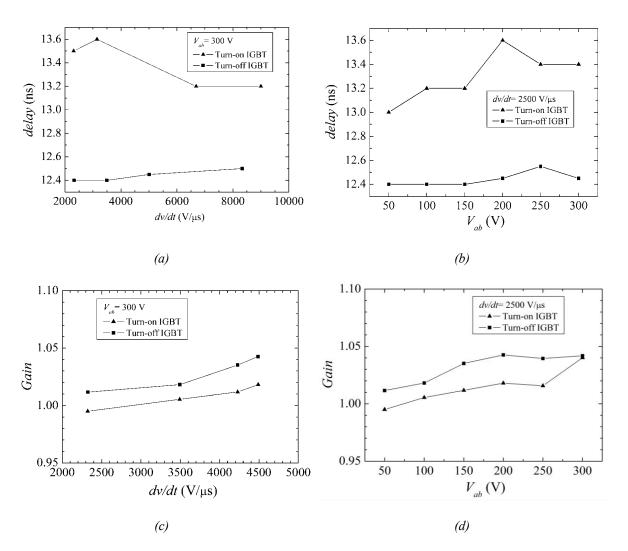

| Figure 3-15 | Differential voltage probe tests. a) delay vs dv/dt during a turn off and                             |

|             | turn-on. b) delay vs $V_{ab}$ during a turn-off and turn-on. c) Gain vs $dv/d$                        |

|             | during a turn-off and turn-on. d) Gain vs $V_{ab}$ during a turn-off and turn-or                      |

|             |                                                                                                       |

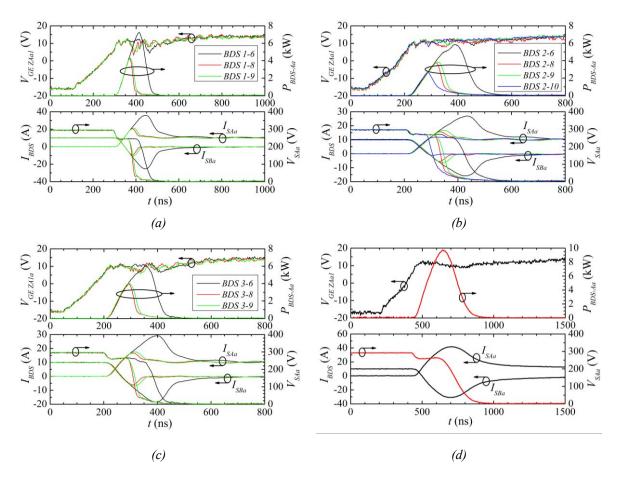

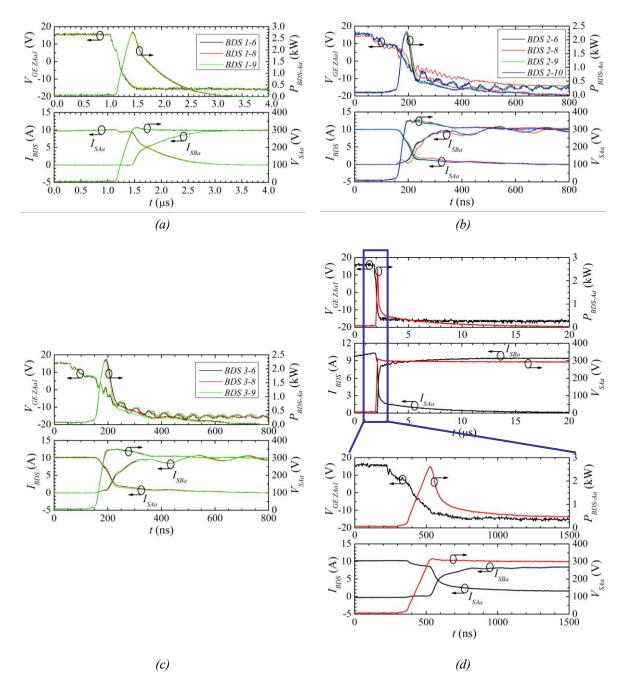

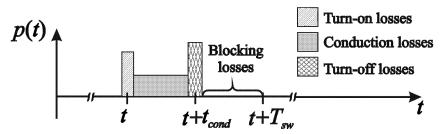

| Figure 3-16 | Experimental waveforms during the BDS-Aa turn-on at $V_{ab} = 300 \text{ V}$ , $I_L = 100 \text{ V}$  |

|             | 10 A: a) BDS 1-6, 8, 9. b) BDS 2-6, 8, 9, 10. c) BDS 3-6, 8, 9. d) RE                                 |

|             | BDS67                                                                                                 |

| Figure 3-17 | Experimental waveforms during the BDS-Aa turn-off at $V_{ab} = 300 \text{ V}$ , $I_L = 100 \text{ V}$ |

|             | 10 A: a) BDS 1-6, 8, 9. b) BDS 2-6, 8, 9, 10. c) BDS 3-6, 8, 9. d) RE                                 |

|             | BDS                                                                                                   |

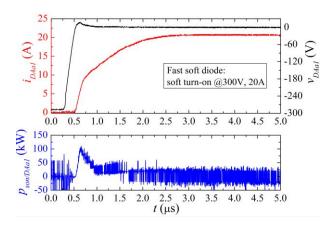

| Figure 3-18 | Experimental waveforms during a soft commutation process at $V_{ab} = 300$                            |

|             | V, $I_L = 10$ A: a) BDS 1-6, 9 turn-on. b) BDS 1-6, 9 turn-off. c) RB BDS                             |

|             | turn-on. d) RB BDS turn-off                                                                           |

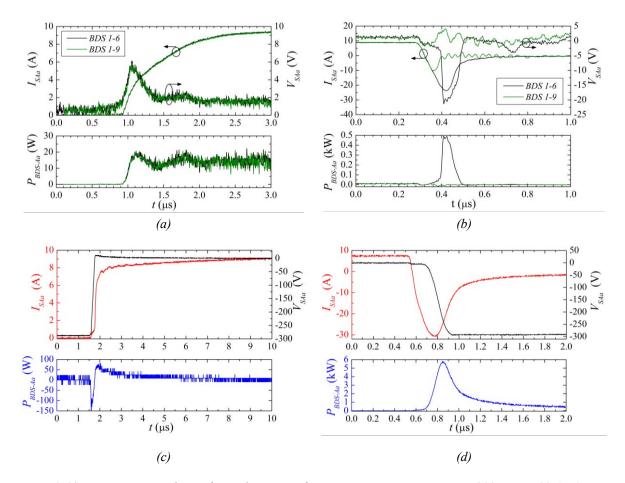

| Figure 3-19 | Energy losses associated to the BDS 1-6 at $V_{ab} = 100$ , 200, 250 and 300 V                        |

|             | and different $I_L = 5$ , 10, 15 and 20 A. Experimental points, linea                                 |

|             | approximation (3.4) and polynomial fitting (3.5). a) IGBT hard turn-off                               |

|             | b) IGBT hard turn-on. c) Diode recovery. d) Diode hard turn-on. e) IGBT                               |

|             | soft turn-on. f) IGBT soft turn-off                                                                   |

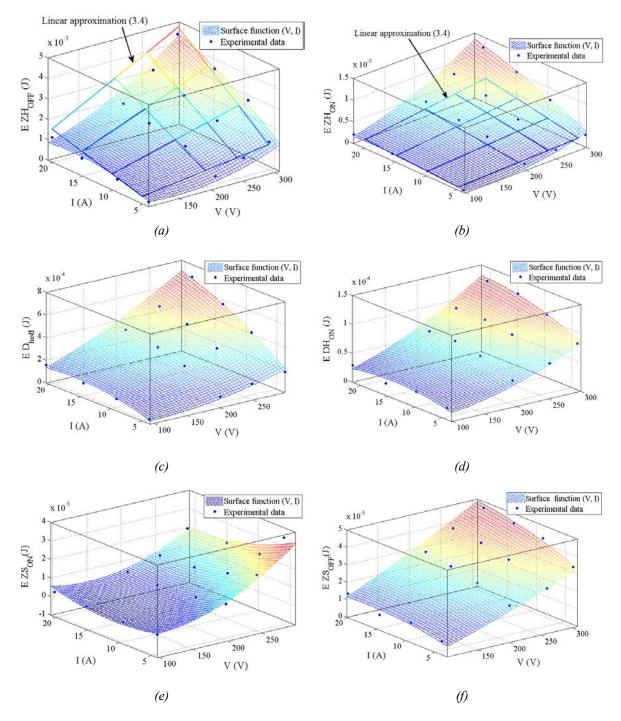

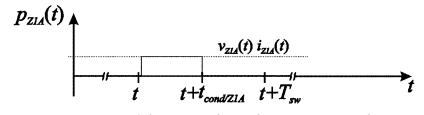

| Figure 4-1  | Schematic instantaneous power losses in a T <sub>sw</sub> interval                                    |

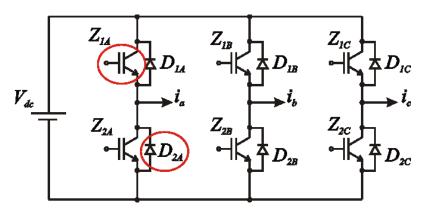

| Figure 4-2  | Three-phase VSI circuit schematic                                                                     |

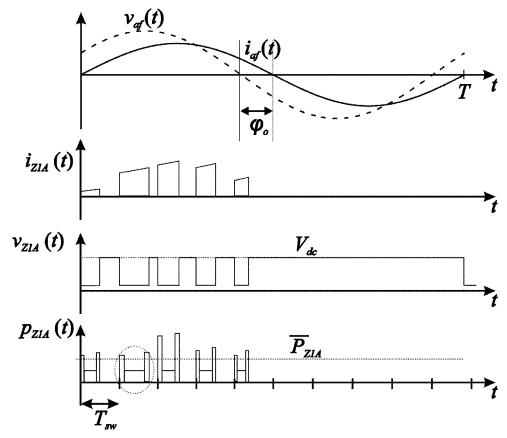

| Figure 4-3  | Schematic waveforms of Z1A IGBT within the converter a-phase 84                                       |

| Figure 4-4  | Schematic conduction losses in a T <sub>sw</sub> period                                               |

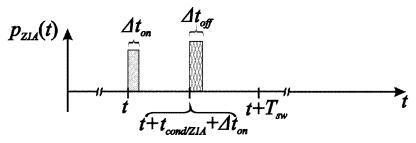

| Figure 4-5  | Schematic switching losses in a T <sub>sw</sub> cycle                                                 |

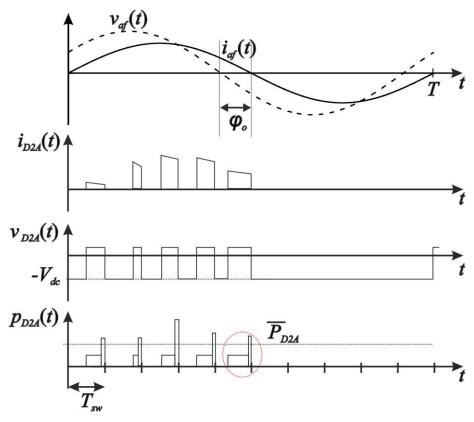

| Figure 4-6  | Schematic waveforms of D <sub>2A</sub> diode within the converter a-phase 88                          |

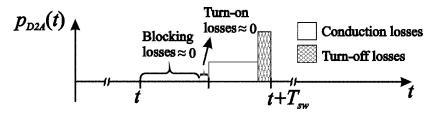

| Figure 4-7  | Schematic instantaneous power losses in a t+T <sub>sw</sub> interval                                  |

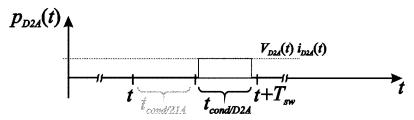

| Figure 4-8  | Schematic conduction losses in a T <sub>sw</sub> period                                               |

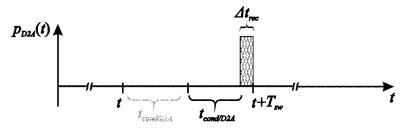

| Figure 4-9  | Schematic diode turn-off losses in the t+T <sub>sw</sub> interval                                     |

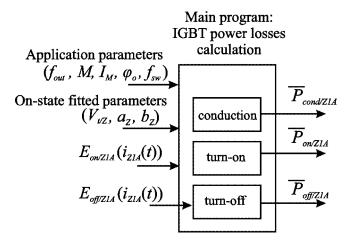

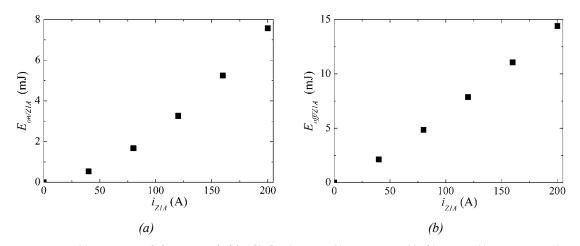

| Figure 4-10 | Block diagram of the power losses calculation script for a single IGBT                                |

|             | within the VSI                                                                                        |

| Figure 4-11 | Measured data provided by [87]: a) $E_{on/Z1A}(t)$ versus $i_{Z1A}(t)$ , b) $E_{off/Z1A}(t)$          |

|             | versus $i_{71A}(t)$ 92                                                                                |

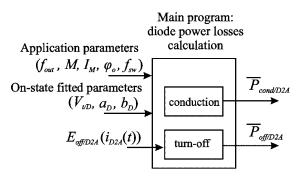

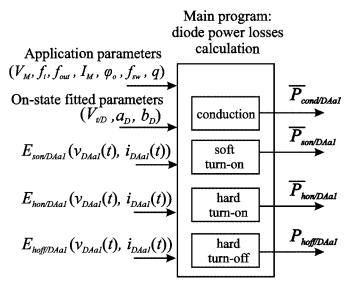

| Figure 4-12   | Block diagram of the power losses calculation script for a single diode                            |

|---------------|----------------------------------------------------------------------------------------------------|

|               | within the VSI 93                                                                                  |

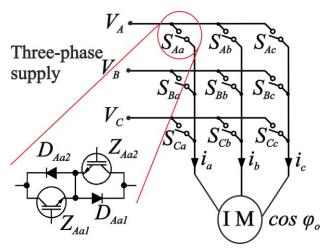

| Figure 5-1    | Typical three-phase to three-phase MC circuit topology implemented by                              |

|               | nine BDSs (two IGBTs and two diodes in common emitter configuration)                               |

|               | driving an AC machine of $\cos \phi_o$ power factor                                                |

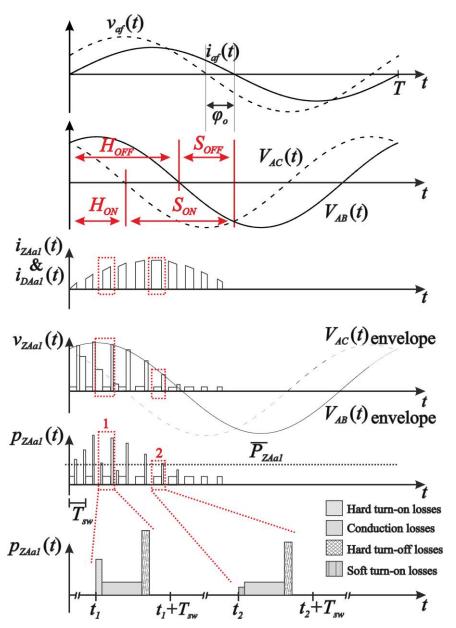

| Figure 5-2    | Schematic waveforms of the $Z_{Aa1}$ commutation processes within T period                         |

|               |                                                                                                    |

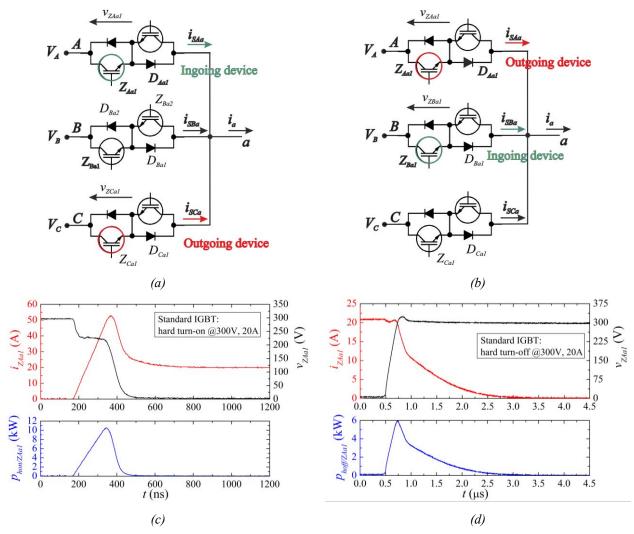

| Figure 5-3 a) | $S_{Ca}$ to $S_{Aa}$ commutation, b) $S_{Aa}$ to $S_{Ba}$ commutation, c) measured IGBT            |

|               | hard turn-on and d) hard turn-off switching waveforms and associated                               |

|               | losses of BDS 1-6                                                                                  |

| Figure 5-4    | Measured IGBT switching waveforms and associated losses of BDS 1-6                                 |

|               | a) Soft turn-on, b) soft turn-off                                                                  |

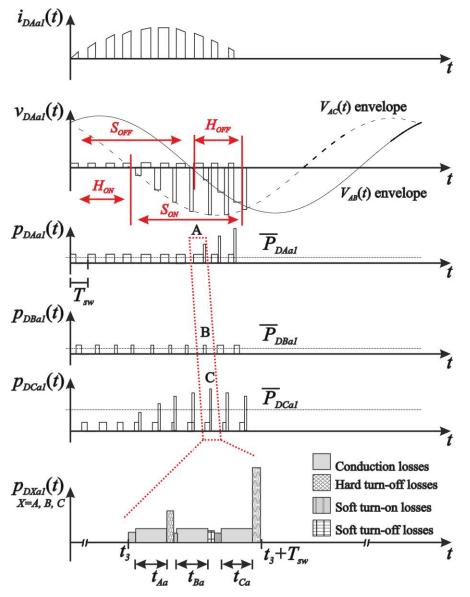

| Figure 5-5    | Schematic waveforms of the commutation processes within T period of                                |

|               | the diodes connected to output a-phase                                                             |

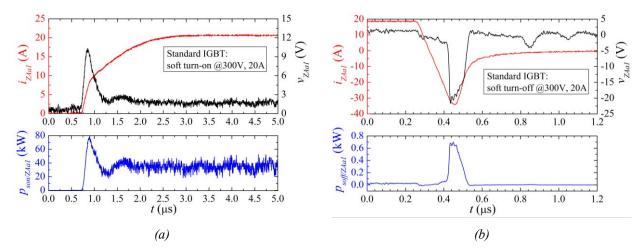

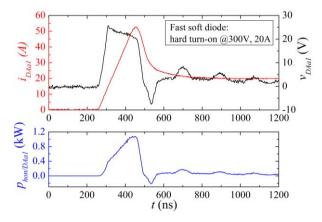

| Figure 5-6    | Measured diode soft turn-on switching waveforms and associated power                               |

|               | losses of BDS 1-6                                                                                  |

| Figure 5-7    | a) Diode turn-off in the $S_{Aa}$ to $S_{Ba}$ commutation process, b) measured hard                |

|               | turn-off switching waveforms and associated power losses of BDS 1-6                                |

|               |                                                                                                    |

| Figure 5-8    | Measured diode hard turn-on switching waveforms and associated power                               |

|               | losses of BDS 1-6                                                                                  |

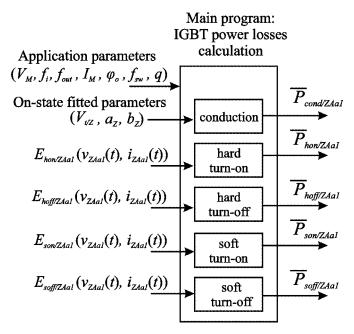

| Figure 5-9    | Block diagram of the power losses calculation script for a single IGBT                             |

|               | within the MC                                                                                      |

| Figure 5-10   | Block diagram of the power losses calculation script for a single diode                            |

|               | within the MC111                                                                                   |

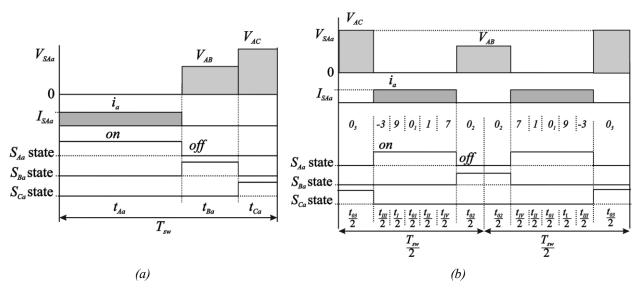

| Figure 5-11   | Schematic representation of the switching pattern for BDS S <sub>Aa</sub> for a)                   |

|               | Venturini modulation. b) double-side space vector modulation 112                                   |

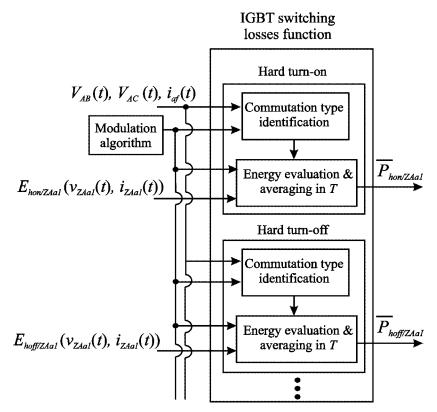

| Figure 5-12   | Block diagram of IGBT switching losses function                                                    |

| Figure 5-13   | Detail of the modulation algorithm block for the DS SVM case 115                                   |

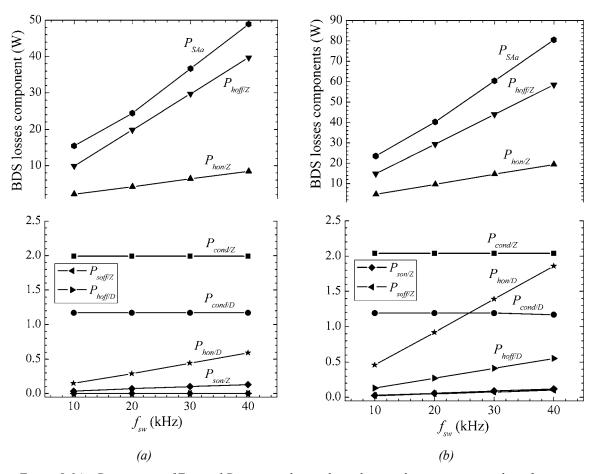

| Figure 5-14   | Comparison of Z <sub>Aa1</sub> and D <sub>Aa1</sub> power losses depending on the converter        |

|               | switching frequency. Operating conditions: f <sub>i</sub> and f <sub>out</sub> are 50 Hz, q is 0.5 |

|               | and $\cos \phi_0$ is 0.84. a) Venturini modulation. b) DS SVM modulation 117                       |

| Figure 5-15   | Comparison of $Z_{Aa1}$ and $D_{Aa1}$ power losses depending on $\cos \phi_o$ .                    |

|               | Operating conditions: $f_i$ and $f_{out}$ are 50 Hz, q is 0.5 and $f_{sw}$ is 20 kHz 118           |

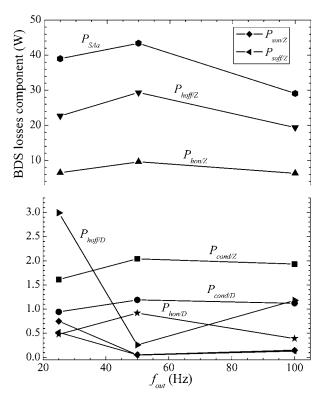

| Figure 5-16 | Comparison of $Z_{Aa1}$ and $D_{Aa1}$ power losses depending on $f_{out}$ . Operating                           |

|-------------|-----------------------------------------------------------------------------------------------------------------|

|             | conditions: $f_i$ is 50Hz, $q$ is 0.5 cos $\phi_o$ is 0.84 and $f_{sw}$ is 20 kHz                               |

| Figure 5-17 | Comparison of $Z_{Aa1}$ and $D_{Aa1}$ power losses depending on q. Operating                                    |

|             | conditions: $f_i$ and $f_{out.}are~50~Hz,cos~\phi_o$ is 0.84 and $f_{sw}$ is 20 kHz 120                         |

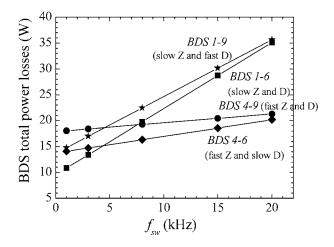

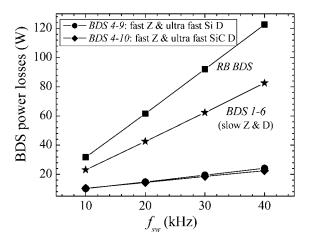

| Figure 5-18 | Comparison of BDS total power losses for different BDS combinations                                             |

|             | depending on $f_{\text{sw}}.$ Operating conditions: $f_{i}$ and $f_{\text{out}}.are\ 50$ Hz, $cos\ \phi_{o}$ is |

|             | 0.84                                                                                                            |

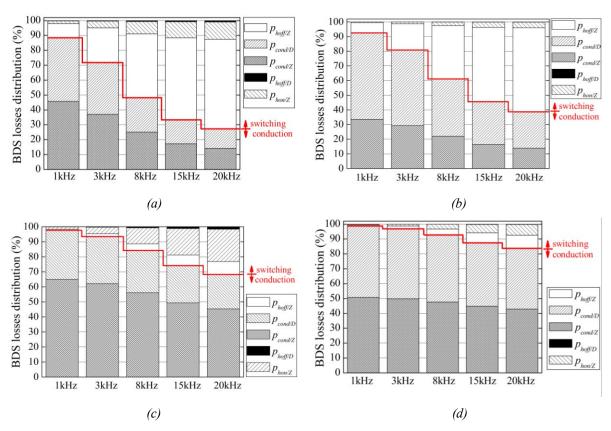

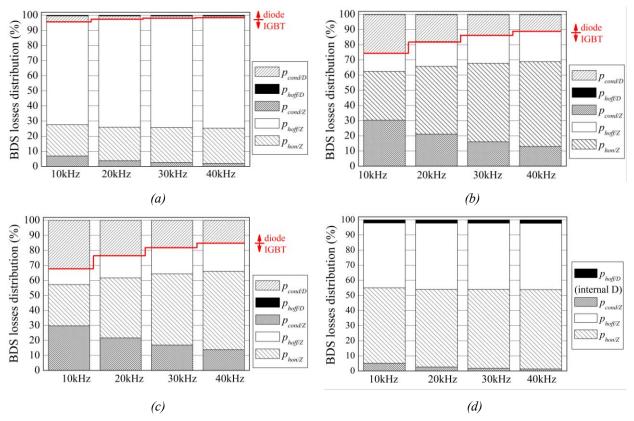

| Figure 5-19 | BDS power losses distribution depending on the operation mode. a) BDS                                           |

|             | 1-6. b) BDS 1-9. c) BDS 4-6. d) BDS 4-9                                                                         |

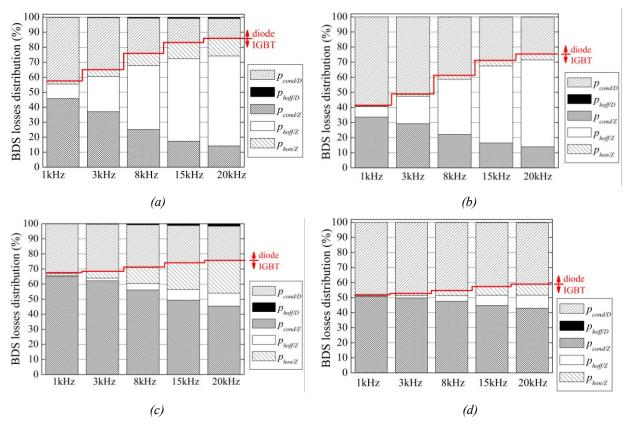

| Figure 5-20 | BDS power losses distribution depending on the power device. a) BDS 1-                                          |

|             | 6. b) BDS 1-9. c) BDS 4-6. d) BDS 4-9                                                                           |

| Figure 5-21 | Comparison between total BDS power losses based on different devices                                            |

|             | in a MC working at different switching frequencies                                                              |

| Figure 5-22 | BDS power losses distribution depending on the power device. a) BDS 1-                                          |

|             | 6. b) BDS 4-9. c) BDS 4-10. d) RB BDS                                                                           |

| Figure 6-1  | Block diagram of the proposed intelligent power module integrating a                                            |

|             | bidirectional switch                                                                                            |

| Figure 6-2  | Schematic circuit of the bidirectional switch power module                                                      |

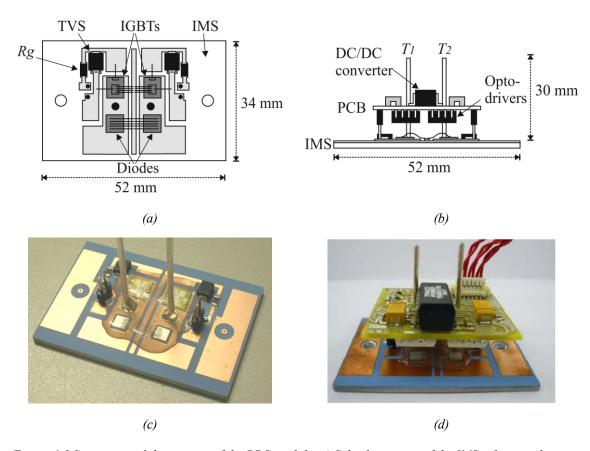

| Figure 6-3  | Structure and dimensions of the BDS module. a) Scheck top view of the                                           |

|             | IMS substrate showing the two pairs of IGBT and diode chips, gate                                               |

|             | resistors and TVS protection devices. b) Scheck lateral view showing the                                        |

|             | IMS substrate on the bottom with the power stage and the PCB with the                                           |

|             | control circuitry on top. c) Realisation of the power stage of a BDS                                            |

|             | module. d) Picture of a whole assembly of BDS module prototype                                                  |

|             | including the power and control stage                                                                           |

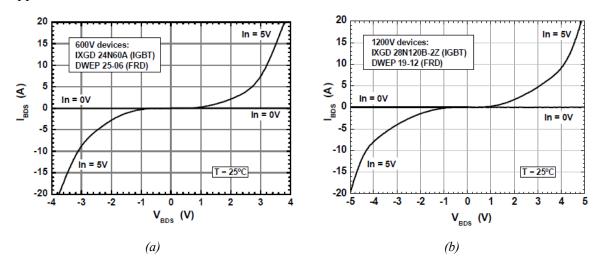

| Figure 6-4  | Static I-V characteristics of the BDS showing its voltage and current                                           |

|             | bidirectional capability. a) I-V curves using 600V devices. b) I-V curves                                       |

|             | using 1200V devices                                                                                             |

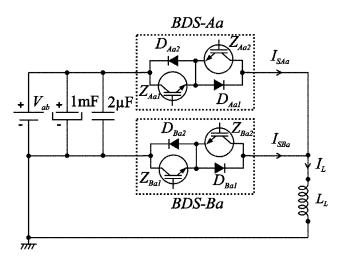

| Figure 6-5  | Schematic of the switching test circuit used to validate the commutation                                        |

|             | processes between BDS modules                                                                                   |

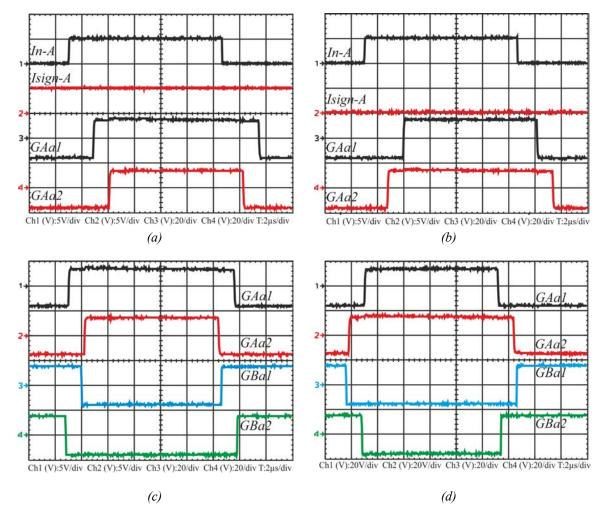

| Figure 6-6  | Control signals showing the generation of the commutation sequence of                                           |

|             | the IGBTs depending on the sign of the phase current. a) Gate voltages of                                       |

|             | BDS-Aa for $I_L > 0$ . b) Gate voltages of BDS-Aa for $I_L < 0$ . c) Gate                                       |

|             | voltages of BDS-Aa and BDS-Ba, $I_L > 0$ . d) Gate voltages for BDS-Aa           |

|-------------|----------------------------------------------------------------------------------|

|             | and BDS-Ba, $I_L < 0$                                                            |

| Figure 6-7  | Characteristic current and voltage switching waveforms of a BDS module           |

|             | (1200 V rated devices) at $V_{ab}$ = 300 V, $I_L$ = 25 A. a) Hard turn-on        |

|             | commutation type. b) Hard turn-off commutation type                              |

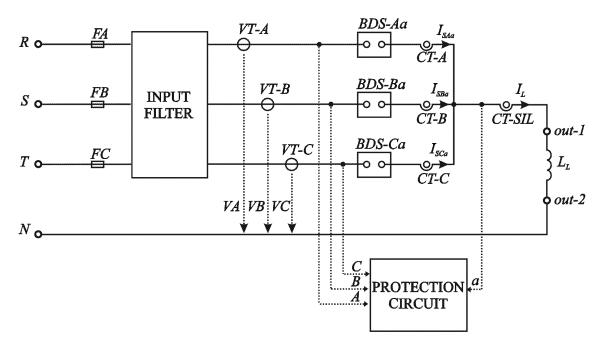

| Figure 6-8  | Diagram of the power circuit of the three-phase to one-phase test MC. 141        |

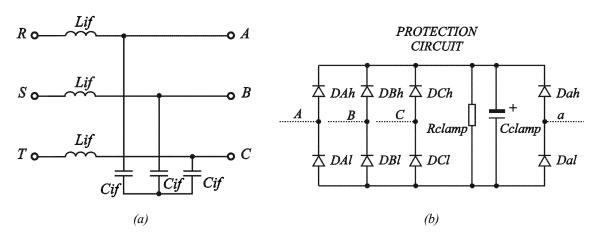

| Figure 6-9  | Schematic circuit of a) input L-C filter in star connection with                 |

|             | inductances: 200 $\mu H$ and capacitances: 100 nF. b) protection circuit 141     |

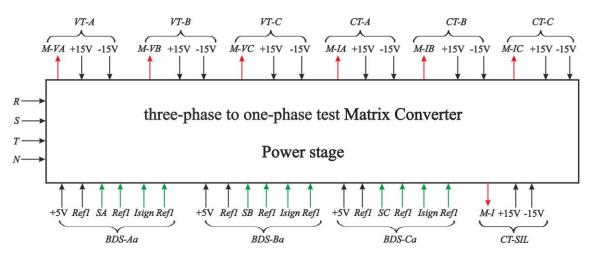

| Figure 6-10 | Signal diagram of the power stage                                                |

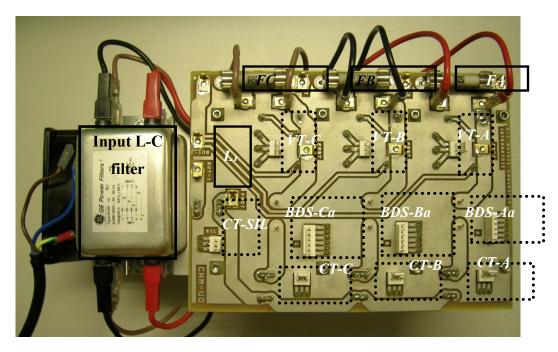

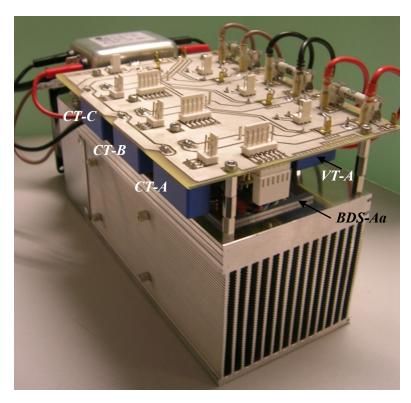

| Figure 6-11 | Top view of the power circuit of the three-phase to one-phase test MC            |

|             |                                                                                  |

| Figure 6-12 | View of the heat-sink and the BDS modules                                        |

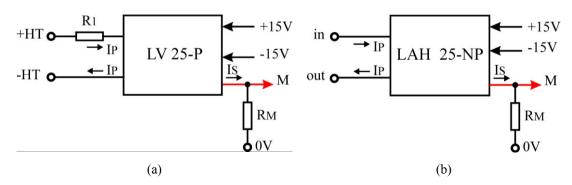

| Figure 6-13 | Schematic circuit of a) voltage transducer. b) current transducer 144            |

| Figure 6-14 | Schematic of the voltage transducer conditioning circuit                         |

| Figure 6-15 | Schematic of the current transducer conditioning circuit                         |

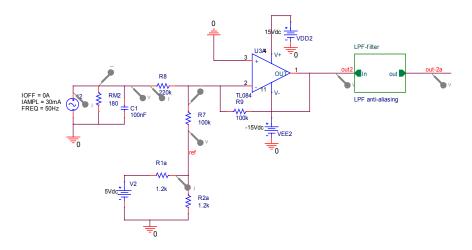

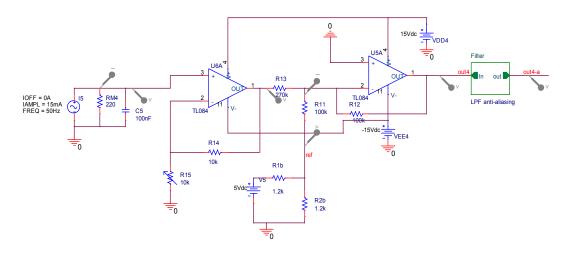

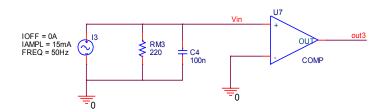

| Figure 6-16 | Schematic of the current direction detection circuit                             |

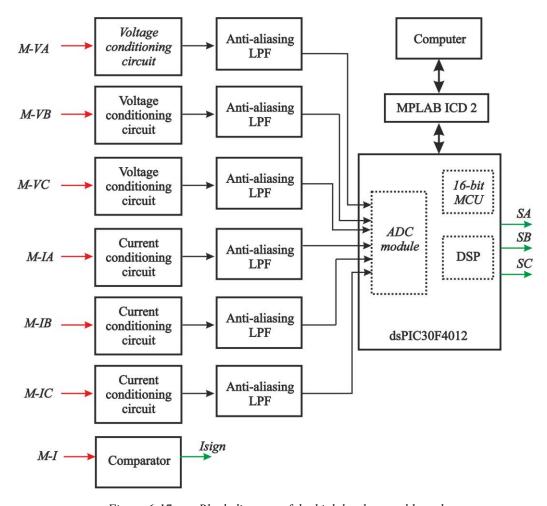

| Figure 6-17 | Block diagram of the high level control board                                    |

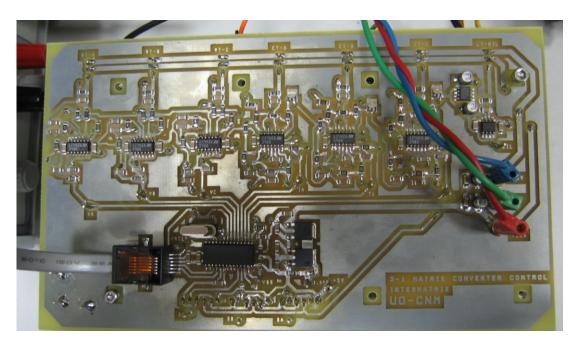

| Figure 6-18 | Fabricated control board of the three-phase to one-phase test MC 150             |

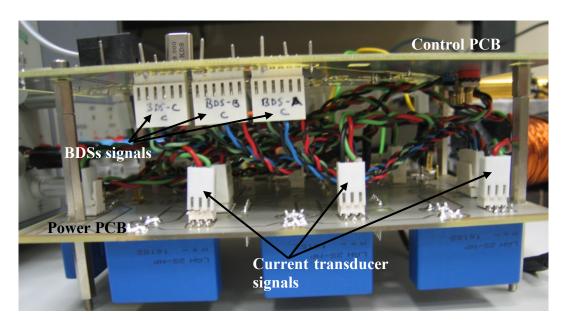

| Figure 6-19 | Mechanical and electrical assembly between the control and the power             |

|             | boards                                                                           |

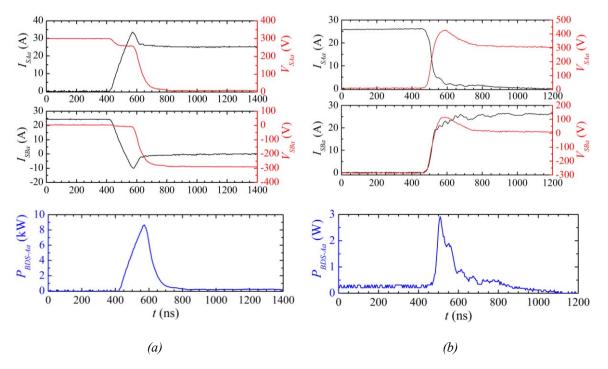

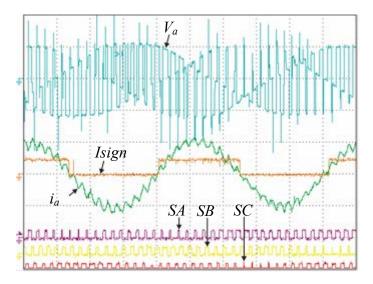

| Figure 6-20 | Characteristic waveforms of the test MC. Switching frequency 2 kHz.              |

|             | Input voltages $200\ V-50\ Hz,i_a$ output current $5\ A$ peak-peak $-100\ Hz.$   |

|             | i <sub>a</sub> : 2.3 A/div. V <sub>a</sub> : 200 V/div. Time: 2 ms/div           |

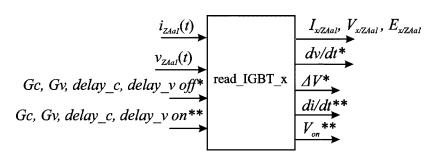

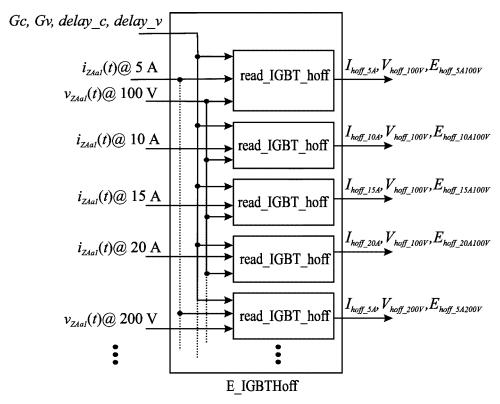

| Figure B-1  | Block diagram of the read_IGBT_x script                                          |

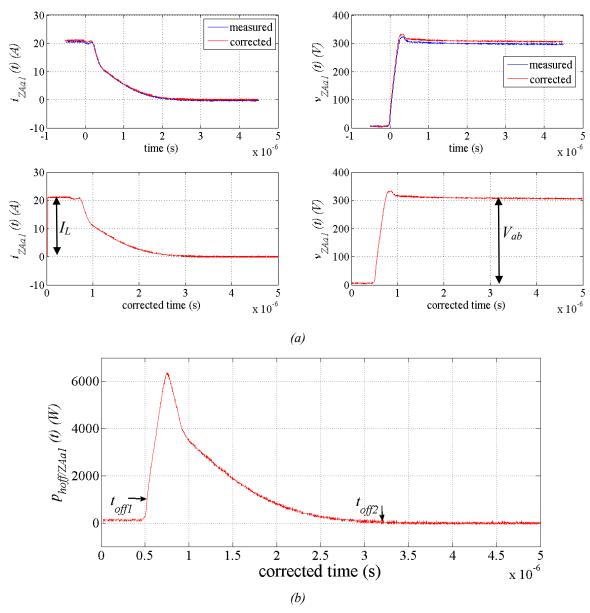

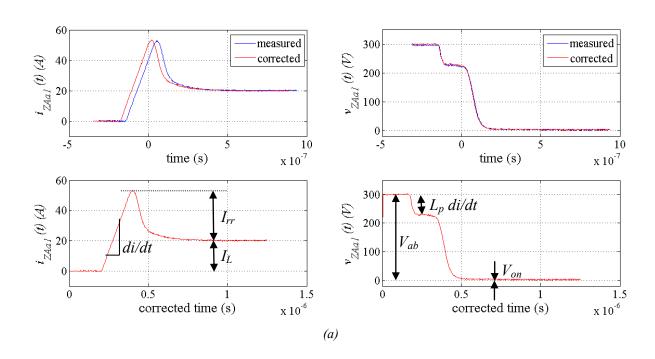

| Figure B-2  | a) Hard turn-off measured and corrected switching current and voltage            |

|             | signals at $V_{ab} = 300\ V$ and $I_L = 20\ A$ within BDS 1-6 . b) Hard turn-off |

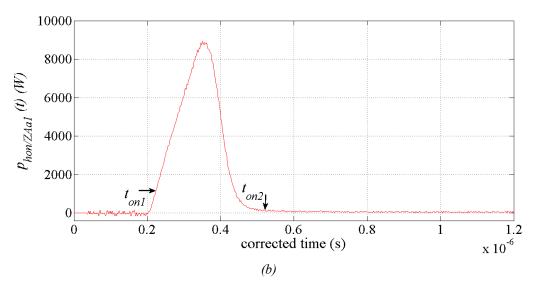

|             | instantaneous power dissipation                                                  |

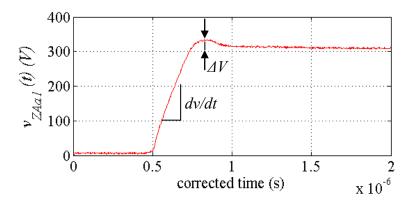

| Figure B-3  | Turn-off switching voltage zooming                                               |

| Figure B-4  | a) Hard turn-on measured and corrected switching current and voltage             |

|             | signals at $V_{ab}$ = 300 V and $I_L$ = 20 A within BDS 1-6. b) Hard turn-on     |

|             | instantaneous power dissipation                                                  |

| Figure B-5  | Block diagram of the IGBT hard turn-off energy losses calculation 177            |

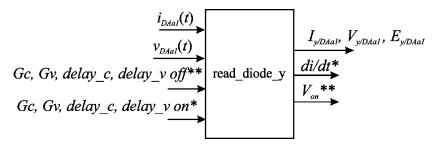

| Figure B-6  | Block diagram of the read_diode_y script                                         |

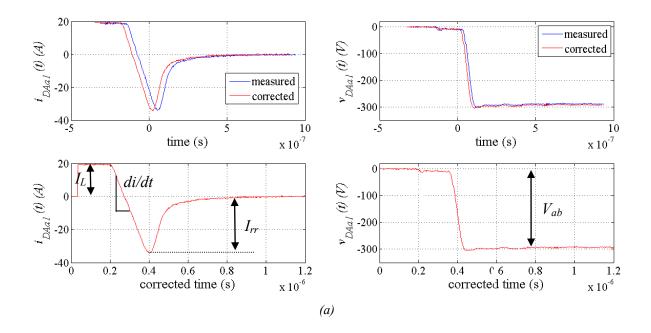

| Figure B-7 | a) Hard turn-off measured and corrected switching current and voltage         |  |

|------------|-------------------------------------------------------------------------------|--|

|            | signals at $V_{ab}$ = 300 V and $I_L$ = 20 A within BDS 1-6. b) Hard turn-off |  |

|            | instantaneous power dissipation                                               |  |

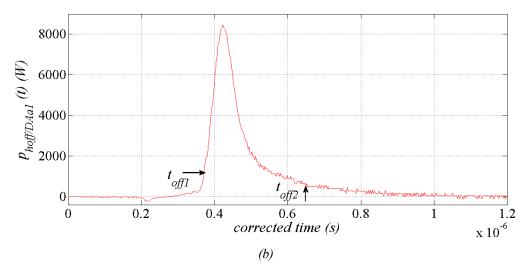

| Figure C-2 | Active configurations to build the a) Output reference voltage vector. b)     |  |

|            | input reference current vector                                                |  |

# **List of Tables**

| Table 1-1 | Pros, cons and solutions of MC as an induction motor drive                                                                   |

|-----------|------------------------------------------------------------------------------------------------------------------------------|

| Table 1-2 | Power devices useful for developing BDSs                                                                                     |

| Table 1-3 | Switch configurations and chip count of AC-AC converters. *Inductors on                                                      |

|           | the input side of the back-to-back converter [37]                                                                            |

| Table 1-4 | Main features of power modules commercially available to build a MC 12                                                       |

| Table 2-1 | Description of the BDS states                                                                                                |

| Table 2-2 | Types of commutation processes: S <sub>OFF</sub> : soft turn-off, S <sub>ON</sub> : soft turn-on,                            |

|           | H <sub>OFF</sub> : hard turn-off, H <sub>ON</sub> : hard turn-on, H <sub>OFF</sub> : diode turn-off reverse                  |

|           | recovery                                                                                                                     |

| Table 3-1 | Typical characteristics of the power devices employed to build the BDSs                                                      |

|           | under test                                                                                                                   |

| Table 3-2 | Switching characteristics of the discrete BDSs. Test conditions: Gate                                                        |

|           | controls $(G_{Aa1}, G_{Aa2}, G_{Ba1}, G_{Ba2}) = \pm 15 \text{ V}, R_{G1} = R_{G2} = 33 \Omega, V_{ab} = 300 \text{ V}, I_L$ |

|           | = 10 A                                                                                                                       |

| Table 3-3 | Static and dynamic characteristics of different BDS realisations                                                             |

| Table 4-1 | Test operating conditions and fitted parameters                                                                              |

| Table 4-2 | Power losses comparison between the analytical method and the                                                                |

|           | numerical implemented method                                                                                                 |

| Table 5-1 | Z <sub>Aa1</sub> commutation processes                                                                                       |

| Table 6-1 | Switching characteristics of the BDS module prototype at $V_{ab} = 300 \text{ V}$ , $I_L$                                    |

|           | = 25 A                                                                                                                       |

| Table 6-2 | Main features of dsPIC30F4012 148                                                                                            |

| Table C-1 | Switching configurations derived from the SVM for three-phase to three-                                                      |

|           | phase MC [18]. The ones involving S <sub>Aa</sub> BDS are red coloured                                                       |

| Table C-3 | Selection of the switching configurations depending on K <sub>v</sub> and K <sub>i</sub> sectors                             |

|           | of the MC references [18]. The ones involving SAA BDS are red coloured                                                       |

|           |                                                                                                                              |

| Table C-4 | Vector DS SVM sequence depending on K <sub>v</sub> and K <sub>i</sub> sectors of the MC for                                  |

|           | S <sub>Aa</sub> device                                                                                                       |

### 1. Introduction

This chapter introduces the reader to the challenges of the Matrix Converter (MC) practical implementation. One fundamental problem with the MC topology is that it requires a matrix of switches called bidirectional switches (BDS) to connect each input phase to each output phase. Other commonly used names for these bidirectional switches are Alternating Current (AC) switches or four-quadrant switches. The focus of this thesis is upon the study and development of bidirectional switches with high level of integration allowing friendly and reliable MC realisation. An updated state of the art of MC as well as some aspects about the BDS implementation is introduced. The aims and the main structure of the thesis are also presented.

## 1.1. Background of the Thesis

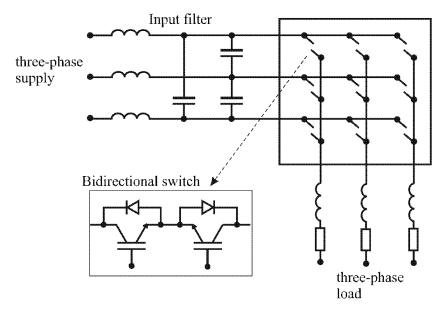

The MC is a single-stage converter which carries out a direct AC-AC conversion by means of a matrix of switches [1]. A typical configuration of this topology is a threephase voltage source with a three-phase load (generally a motor) as shown in Figure 1-1. This matrix of switches constitutes the power stage of the converter. As the industrial interest toward MCs has increased, different power stages specifically designed for MC applications are now available in industry standard packages. For instance, a full MC power stage in a single package is developed by Eupec [2] and a single AC switch is packaged separately in a module by Dinex [3]. All these different MC power stage implementations can be a solution to build more efficient MC prototypes. But, from the industrial applications point of view, a versatile, compact, high power density, high performance and efficient four-quadrant switch element is demanded. This is the basic idea behind the development of a new controlled bidirectional switch which integrates the power stage functionality with the intelligence in one device. That is, the controlled switching element should manage to switch-on or switch-off by itself depending on a simple control signal, to generate suitable control patterns to carry out a safe and efficient commutation processes and to implement local and global protection strategies to prevent the damage of the switch and the converter. Those can be some benefits of using this new switch which can make easy the MC implementation. The main disadvantages can be the complexity of integrating the control stage with the power one, the increase of the cost due to the different

components required to implement the control functionalities such as the gate drives, the isolated power supplies, the microcontroller or Field Programmable Gate Array (FPGA).

Figure 1-1 Matrix Converter topology

### 1.2. The Matrix Converter and its Implementation

Since one of the first attempts to establish the MC technology in 1976 by [1] till the first commercial Matrix Converter product in 2004 by Yaskawa Company [4] a great research effort in the fields of control algorithms, current commutation strategies and practical implementation has been carried out for thirty years [5]. The potential of this topology to perform direct AC-AC conversion as well as the growing number of industrial applications which require bidirectional transfer of power between the AC mains and a load has worth all this research work. The MC does not require large, bulky and expensive energy storage components so that it can be presented such as an almost all silicon compact solution for AC-AC power conversion. An array of controlled bidirectional switches (BDSs) are needed to connect directly an n-phase source to an m-phase load so that a variable output voltage of a desired amplitude and frequency can be generated [6].

As there are no DC-link capacitors, the MC can be also a proper solution for Aerospace applications [7] where temperature and size are a handicap. Another application which can be fulfilled by the MC topology is in electric vehicles since weight and size as well as bidirectional power flow are the main constraints [8].

In the MC application as a motor drive [9] for rolling mills, elevators, centrifuges and escalators significant energy and cost savings can be achieved by returning the wasted energy to the main power supply, in addition, a space saving is obtained since no additional equipment for breaking is necessary. Another important application related to renewable energies that often require bidirectional power flow is processing energy from alternative sources such as wind [10, 11], photo voltaic [12] and fuel cells [13]. Smart-grids is also a potential application for MCs [14] due to its capability to control the bidirectional power flow, i.e. between the utility and smart-grids. Besides, the BDS itself has a potential role within the smart-grid acting as a power router. Power routers, distributed throughout the smart-grid according to the load-demand, can perform switching to connect particular loads with the desired input sources. Table 1-1 resumes the advantages, disadvantages of MC as an induction motor drive and the proposed solutions to overcome the main problems of this topology, too.

#### Advantages

- No DC-link capacitors

- No large, bulky and expensive internal energy storage components

- Sinusoidal input/output currents with unity input power factor

- High output voltage quality

- Less harmonic distortion

- Natural bidirectional power flow capability

- High efficiency

- Compact converter design

- Suitable for applications under high temperature and pressure conditions

| Disadvantages                                | Proposed solutions                                         |  |  |  |

|----------------------------------------------|------------------------------------------------------------|--|--|--|

| Poor voltage transfer ratio                  | Optimise modulation [15]                                   |  |  |  |

|                                              | Using RB-IGBTs [16] reduce the number of the power         |  |  |  |

| Large number of                              | devices; a complete MC in a single package using devices   |  |  |  |

| semiconductors and gate                      | connected in common collector configuration which requires |  |  |  |

| drives                                       | only six gate drivers [2]. Use of specific modules         |  |  |  |

|                                              | implementing intelligent bidirectional switches [40].      |  |  |  |

| Complexity of the control                    | M. J J 44                                                  |  |  |  |

| Modern direct theories [17], [18] algorithms |                                                            |  |  |  |

| Protection circuit                           | Alternative protection circuits [19],[20]                  |  |  |  |

| Sensitive to input voltage                   | New modulation strategies [21], [22]                       |  |  |  |

| disturbances                                 | New modulation strategies [21], [22]                       |  |  |  |

| Problems in the current                      | Multistan commutation stratogics [22] [24] [25]            |  |  |  |

| commutation between BDSs                     | Multistep commutation strategies [23], [24], [25]          |  |  |  |

| Not yet a mature technology                  | increase the reliability of MC hardware [26], [27]         |  |  |  |

Table 1-1 Pros, cons and solutions of MC as an induction motor drive

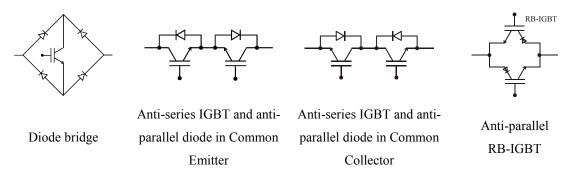

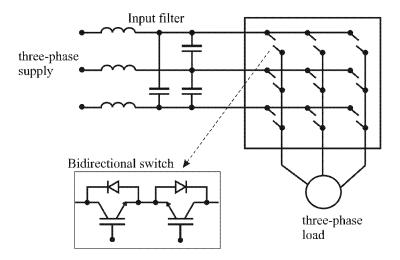

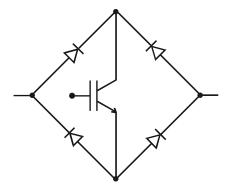

The MC implementation is the key point of the success of this alternative topology. A review of today solutions to build a MC and a power device status to construct a bidirectional switch is presented. As already explained MCs require bidirectional switches capable of blocking voltage in both polarities as well as conducting current in both directions. Nowadays, there are no such devices commercially available that accomplish these needs, so discrete devices need to be used to construct suitable BDSs as shown in Figure 1-2.

Figure 1-2 Possible BDS discrete implementations

The diode bridge (DB) arrangement uses only one active switching device so that current direction cannot be controlled. The common emitter (CE) and common collector (CC) arrangements allow the current direction to be controlled. Besides, the development of Silicon based devices as alternative to conventional Insulated Gate Bipolar Transistors (IGBTs) like the RB-IGBT (Reverse Blocking IGBT) [28] lead to simple BDS assemblies since such devices are able to block voltage in both polarities. The development of RC-IGBTs (Reverse Conducting IGBTs) [29] led also to the fabrication of compact BDSs with less chip count, as the anti-parallel diode usually connected with standard IGBTs is integrated in the same Silicon die in RC-IGBTs. In the framework of this thesis, a RB-IGBT was designed and fabricated in the clean room facility of the Institut de Microelectrònica de Barcelona - Centre Nacional de Microelectrònica (IMB-CNM, CSIC). This work led to apply for a patent [30]. Other emerging devices realised by the potential use of new semiconductor materials, such as Silicon Carbide (SiC) [31] or Gallium Nitride (GaN) [32] are also considered to build a BDS having fast switching and low loss characteristics because of their superior material properties. Other transition power devices in the form of a cascodes comprising SiC JFETs and low voltage Si power MOSFETs from Infineon [33], SiCED [34] and IXYS [35] have also been reported. Nowadays, commercial SiC JFET devices are already available [33]. Table 1-2 summarises the main features of the current and new device solutions in order to implement efficient BDSs. The BDS trend makes the MC topology less dependent on the device count so that its power stage cost can be minimised and a compact design achieved.

| Controlled device                       | Pros                                                                                                                         | Cons                                                                 | Accessible                                                                                                                                                                                                |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conventional IGBT (Si)                  | Maturity technology, spread used in industrial drive applications.                                                           | Limited reverse blocking capability. Requires external diode         | Great range in current and Breakdown voltage (BV)                                                                                                                                                         |

| RC-IGBT (Si)                            | Less silicon, simple module assembly                                                                                         | Need to add in series<br>another RC-IGBT to<br>block reverse voltage | <ul> <li>Infineon, Semikron and Fuji         Electric [36]: Great range in         current and BV</li> <li>IXYS: IXGA30N60C3C1,         600V, 30A, IGBT (Si) + SiC         Anti-Parallel Diode</li> </ul> |

| RB-IGBT (Si)                            | Forward and reverse voltage can be blocked                                                                                   | Slow turn-off<br>switching                                           | <ul> <li>IXYS: IXRH50N120, 1200V, 60A</li> <li>Fuji Electric: FGW85N60RB, 1200V, 85A</li> </ul>                                                                                                           |

| MOS Turn-off<br>Thyristor<br>(MTO) (Si) | reverse voltage blocking capability                                                                                          | Two devices in antiparallel are needed                               | Range in high current and high BV                                                                                                                                                                         |

| SiC JFET                                | Reduced switching losses with respect to the available IGBT (Si), low conduction losses, high temperature operation, high BV | High cost, few commercial devices                                    | Infineon: IJW120R100T1, 1200V                                                                                                                                                                             |

| SIC MOSFET                              | High switching frequen-<br>cy, low switching losses,<br>high temperature opera-<br>tion,                                     | High cost, high conduction losses                                    | Cree: CMF10120D, 1200V, 24A                                                                                                                                                                               |

| GaN HEMT                                | High speed switching frequency, high efficiency operation, low on-state resistance                                           | High cost, lack of commercial specific gate drivers                  |                                                                                                                                                                                                           |

| Blocked device                         | Pros                                                            | Cons                                                                                         | Accessible  Great range in current and BV |  |

|----------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|--|

| Conventional<br>Diode (Si)             | Technology maturity                                             | Limited in temperature, significant switching losses due to their reverse recovery behaviour |                                           |  |

| SiC-SBD<br>(Schottky<br>Barrier Diode) | High temperature operation, low losses characteristics, high BV | High cost                                                                                    | CNM, Infineon, IXYS, Fuji<br>Electric     |  |

Table 1-2 Power devices useful for developing BDSs

In terms of device count a comparison can be made between the MC and a conventional AC-AC converter with intermediate DC-link taking into account the switch configuration. This comparison is summarised in Table 1-3.

| Topology                               | ,                                | Switch<br>Configura-<br>tion | Fully controlled devices | Fast<br>diodes | Recti-<br>fier<br>diodes | Electrolytic<br>capacitors<br>bank | Large<br>induc<br>tors | Total<br>devices<br>count |

|----------------------------------------|----------------------------------|------------------------------|--------------------------|----------------|--------------------------|------------------------------------|------------------------|---------------------------|

| Conventional Matrix Converter AC-DC-AC | Inverter<br>with diode<br>bridge | <b>-</b>                     | 6                        | 6              | 6                        | 1                                  | 0 or 1                 | 18                        |

|                                        | Back-to-<br>Back<br>inverter     |                              | 12                       | 12             | 0                        | 1                                  | 3*                     | 24                        |

|                                        | 1                                |                              | 9                        | 36             | 0                        | 0                                  | 0                      | 45                        |

|                                        | 2                                | <b>+</b>                     | 18                       | 18             | 0                        | 0                                  | 0                      | 36                        |

|                                        | 3                                | ¥ ¥                          | 18                       | 18             | 0                        | 0                                  | 0                      | 36                        |

|                                        | 4                                | RB-IGBT                      | 18                       | 0              | 0                        | 0                                  | 0                      | 18                        |

Table 1-3 Switch configurations and chip count of AC-AC converters. \*Inductors on the input side of the back-to-back converter [37]

As it is described in Table 1-3, a back-to-back inverter requires twenty-four semiconductors (twelve IGBTs, twelve diodes), in the same way the MC needs thirty-six semiconductors (eighteen IGBTs, eighteen diodes) if conventional IGBTs in a common emitter or in a common collector configuration are applied. However, the use of RB-IGBTs reduces the number of semiconductors in the MC by 50% bringing the converter in a real competitive position to the well-known DC-link topology.

Some semiconductors manufacturers have produced power modules specially designed to build MCs and thus, enhance its realisation.

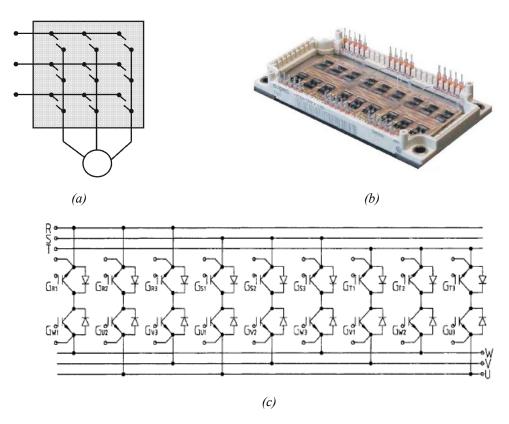

A complete MC in a single package (Figure 1-3a, Figure 1-3b) for lower power levels is possible to be built using power devices connected in the common collector

configuration [2]. To implement a power stage of a MC in a module all eighteen diodes and eighteen IGBTs must be connected in such a way that they build nine BDSs in a common collector configuration. The matrix structure should be realised internally, so that the twenty-four necessary external connections can be grouped in to six emitter potentials as deduced from Figure 1-3c. For instance, one emitter group could be  $G_{RI}$ ,  $G_{R2}$ ,  $G_{R3}$  and  $E_R$  and so on. While emitters and gates of the input are already sorted, emitters and gates of the output are still spread over the whole module. To get a symmetric module, the gate and emitter connections of the output would need to be sorted. With a bus bar structure running along the middle of the module a symmetric module can be realised. Thus, three gates belong to each of six emitter potentials as shown in Figure 1-3c. Every gate needs its own gate unit, but isolated power supplies are only needed for each emitter potential. Therefore, only six isolated power supplies are required for the whole converter.

Figure 1-3 a) Scheme of a complete MC in one package. b) An EUPEC & SIEMENS 7.5 kW Matrix Converter module. c) Schematic of the Power stage module, R, S, T are the input phases; W, U, V, are the output phases and  $G_{RI}$  till  $G_{W3}$  are the eighteen IGBT gate terminals

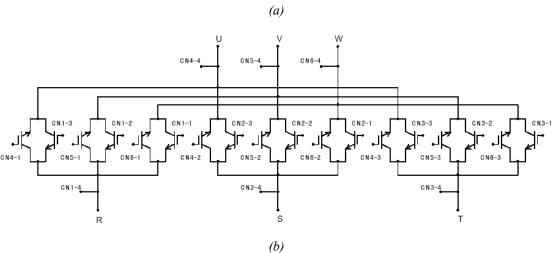

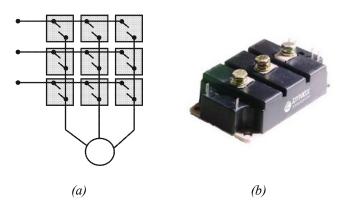

A prototype module configured for the MC application using RB-IGBTs in [16] follows the same module concept as mentioned before, a MC in a single module. Figure 1-4a shows the internal layout with the eighteen RB-IGBTs chips building a complete MC power stage. As it can be appreciated in the connection diagram of Figure 1-4b the number of discrete devices is half of the Eupec module. The need for series connected diodes is eliminated due to the RB-IGBT behaviour.

Figure 1-4 a) 22kW prototype MC module. b) Schematic of the power stage module

It is also possible to build a complete MC with three output legs in a single package (see Figure 1-5). One of the first approximations was possible by rearranging the interconnection of the devices in a standard six-pack IGBT module, giving the converter a greater power density and lower stray inductance as found in a six-pack IGBT module of Semikron [38] for MC applications. It operates with currents up to 450 A and voltages up to 1700 V. This module includes an integrated NTC temperature sensor for measuring the heat sink temperature in the vicinity of the chips. There are also available commercially modules from Dynex and Semelab [39] as depicted in Figure 1-5c and in

Figure 1-5e, respectively. They implement one output leg of a MC in common emitter configuration. A schematic diagram of the internal circuit arrangement of Dynex and Semelab modules is shown in Figure 1-5b and Figure 1-5d, respectively. These modules allow the designer to build high power converters.

Figure 1-5 a) Scheme of a MC output leg in a single package. b) Schematic diagram of the internal circuit of DIM600EZM17-E000. c) Dynex module, DIM600EZM17-E000, 1700V, 600A. d) Schematic diagram of the internal layout of SML300MAT06. e) Semelab module, SML300MAT06, 600V, 300A

Finally, a whole MC can be also implemented by assembling in the right way nine BDS packaged separately in a module as shown in Figure 1-6a. The first attempt to build a BDS is the diode bridge FIO50-12BD from IXYS (schematic diagram shown in Figure 1-2), but it presents high conduction losses since three devices are always conducting. In addition, the direction of the current cannot be controlled. On the other hand, a BDS in a common emitter configuration allows the current direction to be controlled. This device is accessible commercially by Dynex [3]. It is suitable for higher power applications, which allow operating with currents up to 400 A and voltages up to 1700 V. The main advantage of this module is the modularity that introduces in the MC design as well as the easy replacement of a damaged component without throwing away the entire module as it could be the case in the power modules of Figure 1-3, Figure 1-4

and Figure 1-5. Nevertheless, the main drawbacks of this solution compared with the previous module solutions are the achievement of a worse compactness, the increase of the converter size and the addition of stray inductances in the power circuit. Therefore, there is a trade-off between modularity and compactness in MC design. One of the objectives of this thesis will be the development of BDS modules including part of the control circuitry in order to achieve additional levels of integration.

Figure 1-6a) BDS of the MC in a single package. b) Dynex module, DIM400PBM17, 1700V, 400A

Table 1-4 summarises the main aspects to be taken into account when selecting one of the power modules to construct a MC.

| Characteristics | Part reference       | Configuration, No. of BDSs | Isolated gate drive power supplies | Manufacturer |

|-----------------|----------------------|----------------------------|------------------------------------|--------------|

| 1200V, 50A      | FIO50-12BD           | DB, 1                      | 9                                  | Ixys         |

| 1200V, 60A      | SK60GM123            | CE, 1                      | 9                                  | Semikron     |

| 1700V, 400A     | DIM400PBM17          | CE, 1                      | 9                                  | Dynex        |

| 600V, 300A      | SML300MAT06          | CE, 3                      | 9                                  | Semelab      |

| 1700V, 600A     | DIM600EZM17-<br>E000 | CE, 3                      | 9                                  | Dynex        |

| 1200V, 35A      | FM35R12KE3           | CC, 9                      | 6                                  | Eupec        |

| 1200V, 50A      | 18MBI150W-<br>120A   | RB-IGBT, 9                 | 6                                  | Fuji         |

Table 1-4 Main features of power modules commercially available to build a MC

# 1.3. Aims and Structure of the Thesis

A list of power modules based on the bidirectional switch concept for implementing MCs has been presented in this chapter. All these possible solutions implement only the power stage of the converter, an external control stage is needed to carry out the power conversion, and most of them become useless if one power device of the module is destroyed. One of the aims of this work is to improve the feasibility of the MC topology by using an intelligent bidirectional switch power module capable of full controlling itself. In this way, a local control circuitry is included in the module providing for instance the smart switching sequences for the current commutation strategy. In addition, the modular design allows easy replacement of damaged BDSs in an entire MC and makes the power and signals interconnections easier. Moreover, more efficient BDS modules can be implemented taking advantage of the new emergent power semiconductor devices.

The realisation of specific power modules implementing the BDS function for MC applications needs an in depth understanding of the commutation processes involved in this kind of power converter. In addition, the MC can be best suited to several applications with different specifications (voltage and current levels, volume, temperature, frequency operation) to be satisfied by the power components as the heart of the circuit. Hence, the selection of the optimum power semiconductors to implement MC applications determining the associated power losses is another aim of this research work. Cooling requirements can also be deduced from this analysis.

This PhD thesis report will try to develop the different issues mentioned above. It consists of seven chapters including the present one (introductory chapter 1). Conclusions are drawn in each chapter and a final conclusion will sum-up the main results. A list of references supporting the work is also included. In the appendix A, acronyms and symbols used in the thesis are enumerated. Appendix B describes how the switching losses are calculated. Appendix C explains in detail the implementation of the Venturini and double-sided space vector modulation algorithms.

Chapter 2 deals with the analysis of aspects related to the BDS concept such as the BDS configuration and realisation from discrete power devices. A SPICE simulation of a simplified MC, i.e. two-phase to single-phase MC, is performed in order to analyse the commutation processes involved between BDSs. Identification of a critical time interval during the commutation procedure is also discussed.

Chapter 3 introduces the test of BDS devices. A specific test circuit based on a simplified two-phase to one-phase MC structure is designed and fabricated in order to study the switching behaviour of BDSs formed by discrete devices or by a power module. The voltage and current of the devices involved in the commutation are measured so that the associated power losses can be directly determined. BDSs of different technologies are implemented and tested under the reduced MC switching test circuit. From the acquired data, static and dynamic power losses models are presented and discussed for each power device involved in BDS implementations.

Chapter 4 describes a method for the estimation of the semiconductor power losses in MC based on the static and dynamic characterisation of the BDSs devices performed in chapter 3. The conduction and switching power dissipation modelling are derived from the power device physical behaviour. The numerical calculation power losses method is presented, applied and validated for a standard VSI converter. It is important to have an accurate power losses model to acquire a better understanding of effects of the device technology on the power dissipation of AC/AC converters as analysed in chapter 5.

Chapter 5 extends the numerical power losses computation method validated for a VSI in chapter 4 to a MC. Higher complexity is added in the MC since the energy losses depend on the voltage and current throughout the output period of the converter. The implementation of the dissipation computation method is performed by means of MATLAB scripts allowing a fast evaluation and a modular design. The semiconductor power losses within a BDS are calculated according to the converter operating parameters such as: the modulation control, input and output frequency, input and output voltage rate, output current, switching frequency, power factor of the load, etc. A

prediction of the losses is crucial to help the designer to, for instance, select the suitable power devices according to the converter application.

Chapter 6 presents the implementation of an integrated bidirectional switch intelligent power module (BDS-IPM). Its structure, fabrication and electrical characterisation are detailed. In addition, an application example of the BDS module which consists of building a prototype three-phase to one-phase MC is described and discussed. This work has derived in the request of a patent [40].

Chapter 7 summarises and highlights the main achievements of the work done.

## 2. Analysis of the BDS's Commutation Phenomena

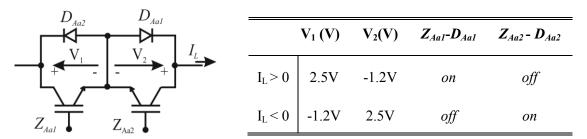

This chapter describes different BDS implementations which enable the MC construction (Figure 2-1). The static and dynamic characteristics of the power semiconductors devices forming a BDS are described. Current commutation strategies based on the output phase current direction are discussed in this chapter. We will focus on the study of BDS's commutation process.

Figure 2-1 A three-phase to three-phase MC circuit

#### **BDS** Topology 2.1.

The key element for implementing MCs is the controlled BDS, which can be realized by power semiconductor devices allowing high frequency operation. These BDSs will be opened and closed in a controllable way so that the desired output voltage and input current can be achieved. It must be kept in mind that input terminals of the MC should not be short circuited because it is usually fed by a voltage source, and that the output phases must be never opened because the load has an inductive nature. So a suitable control must be provided to avoid overcurrents and overvoltages in the MC. With these constraints, the three-phase to three-phase MC has twenty-seven possible switching states [41].

BDSs must capable of blocking voltage of both polarities as well as conducting current in both directions. Nowadays, discrete devices need to be used to construct suitable BDSs. These are diodes and controlled switching devices. Nevertheless, a monolithic bidirectional device concept has recently appeared and is under

development. It will provide bidirectional behaviour in one single die as referred in subsection 2.1.6. In the following BDS realisations, it has been assumed that the Silicon (Si) controlled switching device would be an IGBT, but other power devices such as MOSFETs, MCTs and Integrated Gate-Commutated Thyristors (IGCTs) can be used in the same way. Likewise, controlled gate devices based on wide band-gap (WBG) semiconductor materials such as Silicon Carbide (SiC) are also a very promising option to build a BDS. Different BDS realisation with discrete semiconductors are now presented.

#### 2.1.1. **Diode Bridge BDS**