2

**ADVERTIMENT**. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA**. El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. The access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# Design Automation methods and tools for building Digital<sup>2</sup> Printed Microelectronics Circuits

Ph.D. dissertation Electronic and Telecommunication Engineering

Author:

Manuel José Llamas Rodríguez

Supervisors:

Jordi Carrabina Bordoll (also tutor) Lluís Terés Terés

Universitat Autònoma de Barcelona (UAB) Department of Microelectronics and Electronic Systems (MiSE)

2017, Barcelona, Spain

The undersigned Prof. Dr. Jordi Carrabina Bordoll, professor of the Department of Microelectronics and Electronic Systems, of the Universitat Autònoma de Barcelona (UAB), and Dr. Lluís Terés Terés, scientific researcher at IMB-CNM (CSIC) and associated professor at UAB,

#### **CERTIFY**

That the dissertation entitled "Design Automation methods and tools for building Digital<sup>2</sup> Printed Microelectronics Circuits" has been written by **Manuel José Llamas Rodríguez** under their supervision, in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

And hereby to acknowledge the above, sign the present

Signature Jordi Carrabina Bordoll Signature Lluís Terés Terés

Barcelona, Spain, 18th July 2017.

## **Abstract**

Organic/Printed Electronics are, day by day, increasing on interest, as new applications are being proposed and developed. This kind of technologies do not intend to compete directly with the Silicon-based well-established industry, but rather to complement it with new devices that are advantageous for certain situations, whether in terms of cost or others.

However, in the digital processing domain there is still much work to be done to, slowly but steadily, follow the steps of the conventional fabless model that rules today's semiconductor market. I am referring not only to progresses at fabrication level, but also on the field of Electronic Design Automation.

Our research group conceived a novel strategy to efficiently produce Printed Electronics digital circuit designs based on what we called Inkjet-configurable Gate Arrays, which takes advantage of digital printing techniques. The Inkjet Gate Arrays consist in matrices of transistors over flexible substrates that, after being connected by digital printing techniques, they describe logic gates, and thus circuits.

The work presented in this dissertation targets a specific stage of any common Integrated Circuit design flow, referred to as physical synthesis. Specifically, my contribution provides a new approach to the Placement and Routing problem, where circuits are mapped onto the Inkjet Gate Arrays in a technology independent yield-aware manner. I tackle the issue of dealing with different Printed Electronics technologies that might present distinct yield properties, usually due to the intrinsic high variability of current fabrication processes. In such cases, being able to effectively process the IGA's fault distribution information is key to ensure that the mapped circuits will be capable of working correctly, from a functional perspective. In addition to the yield awareness concept, the circuit personalization capabilities of the novel P&R heuristic proposed herein allow more mapping flexibility, depending on different possible reasons/purposes (e.g. congestion).

This approach is not only convenient for today's first steps of digital circuit prototyping over Organic Electronics, but also scalable to future technological improvements at yield level, and on sizes and integration density.

## Resumen

La electrónica orgánica/impresa está continuamente creciendo en interés, con la aparición de nuevas propuestas y aplicaciones. Este tipo de tecnologías no pretenden competir directamente con las que provienen de la industria tradicional basada en Silicio, sino que tienen como propósito complementarla con nuevos dispositivos que proporcionen ciertas ventajas en determinadas situaciones, ya sea en términos de coste u otras.

Sin embargo, en lo que se refiere al campo del procesado digital queda mucho trabajo por hacer para, paulatinamente, ir siguiendo los pasos del modelo 'fabless' que rige el mercado de semiconductores actual. Este modelo consiste en la deslocalización entre los equipos de diseño y los fabricantes. Respecto a dicho progreso me refiero no solo a las mejoras que acontecen a nivel de procesos de fabricación, sino también en el campo de la automatización de los procesos de diseño.

Nuestro grupo de investigación concibió una novedosa estrategia para producir, de manera eficiente, diseños de circuitos digitales para electrónica impresa, basados en lo que denominamos Inkjet-configurable Gate Arrays, aprovechando las ventajas de la impresión digital. Estos Inkjet Gate Arrays consisten en matrices de transistores sobre sustratos flexibles que, una vez conectados mediante impresión digital, conforman puertas lógicas; las cuales, en su conjunto, materializan circuitos.

El trabajo presentado en esta tesis se centra en una etapa específica de cualquier flujo de diseño común de circuitos integrados, llamada síntesis física. En concreto, este trabajo proporciona una novedosa metodología para resolver el problema de ubicar y conectar, 'Placement and Routing', los circuitos sobre las mencionadas matrices de transistores, teniendo en cuenta su rendimiento, y con independencia de la tecnología de fabricación. Se aborda la manera de cómo tratar con tecnologías impresas diferentes, que puedan presentar distintos niveles de rendimiento, normalmente debidos a la alta variabilidad intrínseca a los procesos de fabricación actuales. En tales casos, un factor clave para asegurar que la colocación de los circuitos sea funcionalmente correcta es poder procesar de manera efectiva la información sobre la distribución de fallos de las matrices. Además del concepto de mapeo según el rendimiento, la novedosa heurística aquí propuesta proporciona la capacidad de personalizar los circuitos, lo que permite mayor flexibilidad en su construcción, dependiendo de distintas razones u objetivos posibles (p. ej. congestión).

Esta metodología no solo es conveniente para los primeros pasos que, en la actualidad, se están llevando a cabo en el desarrollo de prototipos de circuitos digitales para la electrónica orgánica, sino que también es escalable hacia nuevas mejoras en el rendimiento de las tecnologías de fabricación, así como en tamaños y densidad de integración.

# Acknowledgements

I would like to express my gratitude to Jordi Carrabina and Lluís Terés, for giving me the opportunity to work under their supervision. Their passion on tech, from the very basics to the most complex systems, and their interest on applied and industrial research trends is inspiring. I came to Barcelona years ago with the objective of learning more cool stuff. I didn't plan on making a Ph.D. However, by staying, I was able to keep on learning from their vast knowledge and experience in many different areas, as from the many other talented researchers who I have worked with. Overall, I'm very pleased about my progress and achievements over this period.

I would like to give my thanks, for their help and insights at any given moment, to Mohammad Mashayekhi, Francesc Vila, Jofre Pallarès, Keith Sabine, Matthias Köfferlein, Shinya Takamaeda-Yamazaki, Eloi Ramon and Carme Martínez-Domingo.

Special thanks to André Reis and Jody Matos for their priceless feedback and help. Thanks to them coming from UFRGS we were able to discuss and clarify many of the topics covered herein and elsewhere.

Many thanks to the people at CEA-Liten for the warm welcome (and for handling all the bureaucratic nightmare of my stage). Especially to Micaël Charbonneau and Adrica Kyndiah. My time at CEA was short but awesome thanks to them.

Thanks also to Lluís Ribas-Xirgo, Josep Velasco and Borja Martínez for sharing their knowledge and experience in teaching/academic (and even life) matters.

Additional thanks go to Marc Codina and Jordi Guerrero for their support with a great many things.

Special gratitude for the sake of humanity's knowledge must go to Alexandra Elbakyan (Sci-Hub) and Aaron Swartz. I will gladly interact and discuss with anyone about any of these topics. Especially with those who lack interest in moving forward to the XXI century, improving current processes/practices. It's about time.

# **Publication list**

#### 2016:

- M. Llamas, L. Terés and J. Carrabina. "Technology Independent Yield-Aware Place & Route Strategy for Printed Electronics Gate Array Circuits". 7<sup>th</sup> International Conference on Computer Aided Design for Thin-Film Transistors -CAD-TFT 2016 Conference Paper (Beijing, China).

- J. Carrabina, J. Pallarès, F. Vila, M. Llamas, M. Mashayekhi, J. Matos, A. Reis and L. Terés. "Process Design Kit and EDA Tools for Organic/Printed Electronics". 7<sup>th</sup> International Conference on Computer Aided Design for Thin-Film Transistors CAD-TFT 2016 Conference Paper (Beijing, China).

- J. Carrabina, M. Mashayekhi, M. Llamas, J. Pallarès, J. Matos, A. Reis and L. Terés. "Ink-Jet Configurable Gate Arrays". International Workshop on Flexible Electronics WFE 2016 Conference Paper (Tarragona, Spain).

- M. Llamas, L. Terés and J. Carrabina. "Novel EDA techniques for Printed Electronics Circuits". Design, Automation and Test in Europe DATE 2016, PhD Forum, Conference Paper (Dresden, Germany).

#### 2015:

- J. Carrabina, M. Mashayekhi, M. Llamas, S. Ogier, T. Pease, M. Matti, L. Mika-Matti and L. Terés. "Customization Technology and Tools for Building Printed Circuits". 6<sup>th</sup> International Conference on Flexible and Printed Electronics ICFPE 2015 Conference Paper (Taipei, Taiwan).

- M. Llamas, M. Mashayekhi, A. Alcalde, J. Pallarès, F. Vila, A. Conde, L. Terés and J. Carrabina. "Development of Digital Application Specific Printed Electronics Circuits: From Specification to Final Prototypes". IEEE/OSA Journal of Display Technology, vol. 11, no. 8, pp. 652-657. Article.

- J. Carrabina, M. Llamas, J. Matos, M. Mashayekhi and A. Reis. "Technology Mapping Tools for Building Optimal Circuits". 7<sup>th</sup> International Exhibition and Conference for the Printed Electronics Industry - LOPEC 2015 Conference Paper (Munich, Germany).

#### 2014:

M. Mashayekhi, M. Llamas, J. Pallarès, F. Vila, L. Terés and J. Carrabina.

"Development of a Standard Cell Library and ASPEC design flow for organic Thin Film Transistor Technology". XXIX Conference on Design of Circuits and Integrated Systems - DCIS 2014 Conference Paper (Madrid, Spain).

- M. Llamas, M. Mashayekhi, J. Pallarès, F. Vila, L. Terés and J. Carrabina. "Top-down Design Flow for Application Specific Printed Electronics Circuits (ASPECs)". XXIX Conference on Design of Circuits and Integrated Systems DCIS 2014 Conference Paper (Madrid, Spain).

- J. Matos, M. Llamas, M. Mashayekhi, J. Carrabina and A. Reis. "Optimization on Cell-library Design for Digital Application Specific Printed Electronics Circuits".

24<sup>th</sup> International Workshop on Power and Timing Modeling, Optimization and Simulation - PATMOS 2014 Conference Paper (Palma de Mallorca, Spain).

- M. Mashayekhi, M. Llamas, J. Pallarès, F. Vila, L. Terés and J. Carrabina. "Fault-Tolerant Inkjet Gate Array for Application Specific Printed Electronics Circuits".

6<sup>th</sup> International Conference on Computer Aided Design for Thin-Film Transistors CAD-TFT 2014 Conference Paper (Nanjing, China).

- M. Llamas, M. Mashayekhi, J. Pallarès, F. Vila, L. Terés and J. Carrabina. "A novel Application Specific Printed Electronics Circuits (ASPEC) design flow".

6<sup>th</sup> International Conference on Computer Aided Design for Thin-Film Transistors CAD-TFT 2014 Conference Paper (Nanjing, China).

- J. Carrabina, M. Mashayekhi, M. Llamas, C. Martínez-Domingo, E. Ramon, A. Alcalde, J. Pallarès, F. Vila, A. Conde and L. Terés. "Inkjet Gate Array: Novel concept to implement electronic systems". 6<sup>th</sup> International Exhibition and Conference for the Printed Electronics Industry LOPEC 2014 Conference Paper (Munich, Germany).

- M. Mashayekhi, M. Llamas, C. Martínez-Domingo, E. Ramon, J. Pallarès, F. Vila,

A. Conde, L. Terés and J. Carrabina. "Formalization of Design Rules and

generation of related structures using PCells". 6<sup>th</sup> International Exhibition and

Conference for the Printed Electronics Industry LOPEC 2014 Conference

Paper (Munich, Germany).

# **Table of Contents**

| 1 | . Intr | oduc  | tion                                                   | l |

|---|--------|-------|--------------------------------------------------------|---|

|   | 1.1.   | Prin  | nted/Organic/Flexible Electronics                      | 1 |

|   | 1.2.   | Mo    | tivations for this work                                | 2 |

|   | 1.3.   | Dig   | ital Circuit Design styles6                            | 5 |

|   | 1.4.   | Des   | ign Flows & Process Design Kits                        | 7 |

|   | 1.4.   | 1.    | ASIC overview                                          | 7 |

|   | 1.4.   | 2.    | ASPEC overview                                         | ) |

|   | 1.5.   | Dig   | ital printing for personalized digital circuits        | 2 |

|   | 1.6.   | Plac  | cement and Routing problem/strategy                    | 3 |

|   | 1.7.   | Goa   | als of this work14                                     | 4 |

| 2 | . Stat | e of  | the art for PE & EDA                                   | 7 |

|   | 2.1.   | Dig   | ital printing techniques for building digital circuits | 7 |

|   | 2.2.   | Driv  | ving applications for PE circuits                      | 3 |

|   | 2.3.   | Rel   | evant EDA tools                                        | 1 |

|   | 2.4.   | Plac  | cement and Routing                                     | 3 |

|   | 2.4.   | 1.    | Preliminary concepts                                   | 3 |

|   | 2.4.   | 2.    | Current SoA algorithms                                 | 7 |

|   | 2.4.   | 3.    | P&R SoA related to our IGA case                        | 4 |

|   | 2.4.   | 4.    | Selected P&R strategies                                | 5 |

|   | 2.5.   | Sun   | nmary of the chapter                                   | 5 |

| 3 | . Tar  | getin | g PE Technologies                                      | 7 |

|   | 3.1.   | Elei  | mentary technology information                         | 7 |

|   | 3.1.   | 1.    | Full-inkjet technology by TUC/UAB                      | 3 |

|   | 3.1.   | 2.    | Photolithographic technology by CPI/Neudrive           | ) |

|   | 3.1.   | 3.    | Printed Electronics technology by CEA-Liten            | ) |

|   | 3.2.   | PM    | OS & CMOS Cell Design styles                           | 2 |

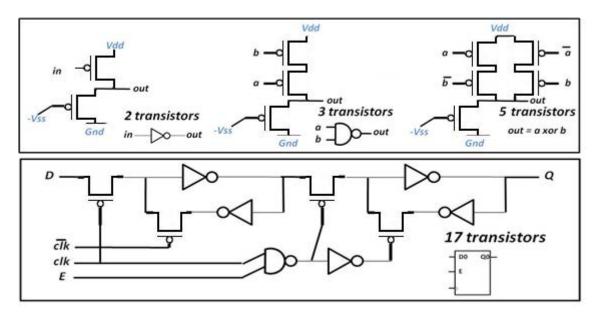

|   | 3.3.   | PM    | OS & CMOS Cell Libraries44                             | 4 |

|   | 3.3.   | 1.    | TUC/UAB44                                              | 4 |

|   | 3.3.   | 2.    | CPI/Neudrive                                           | 5 |

|   | 3.3.   | 3.    | CEA-Liten                                              | 5 |

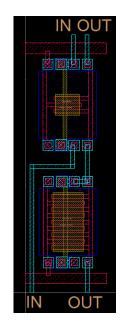

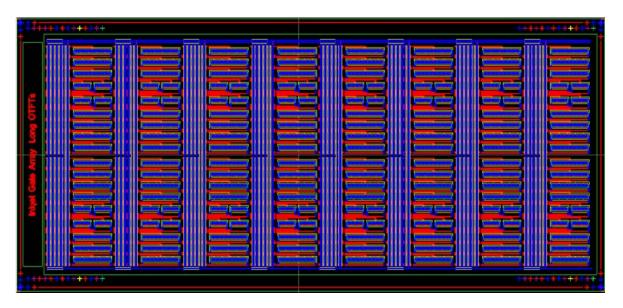

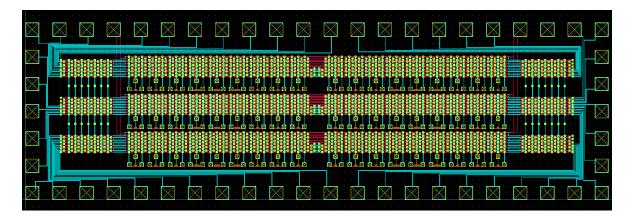

| 3.4.      | PMOS Inkjet-configurable Gate Array                   | 47  |

|-----------|-------------------------------------------------------|-----|

| 3.4.      | .1. 2-step Fabrication process                        | 47  |

| 3.4.2     | .2. TUC/UAB                                           | 48  |

| 3.4.3     | .3. CPI/Neudrive                                      | 48  |

| 3.4.4     | .4. CEA-Liten                                         | 49  |

| 3.5.      | Summary of the chapter                                | 50  |

| 4. P&F    | R Algorithms for Digital <sup>2</sup> PE Circuits     | 51  |

| 4.1.      | Managing circuit personalization files                | 51  |

| 4.2.      | Logic synthesis and technology mapping                | 52  |

| 4.3.      | Placement and Routing strategy and algorithms for IGA | 56  |

| 4.3.      | .1. Preliminary considerations and terminology        | 56  |

| 4.3.2     | .2. Proposed Algorithm                                | 64  |

| 4.4.      | Results                                               | 73  |

| 4.4.      | .1. Proposed circuit benchmarks and IGA templates     | 73  |

| 4.4.2     | .2. Implementation framework                          | 73  |

| 4.4.3     | .3. Complexity analysis of current implementation     | 75  |

| 4.4.4     | .4. Experimental results                              | 76  |

| 4.4.      | .5. P&R for circuit personalization                   | 78  |

| 4.4.0     | .6. IGA vs Standard Cell comparison                   | 79  |

| 4.5.      | Summary of the chapter                                | 80  |

| 5. Con    | nclusions and future work                             | 81  |

| 5.1.      | Overview and conclusions                              | 81  |

| 5.2.      | Future work                                           | 82  |

| Bibliogra | raphy                                                 | 87  |

| Annex A   | A: Digital printing examples                          | 111 |

| Annex B   | B: Dissertation's Copyright                           | 115 |

| Annex C   | C: Implementation's Copyright & Disclaimer            | 115 |

# **List of figures**

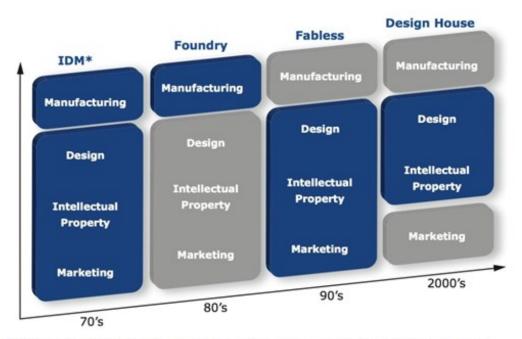

| Figure 1. Business model's historical evolution for electronics                         | 2  |

|-----------------------------------------------------------------------------------------|----|

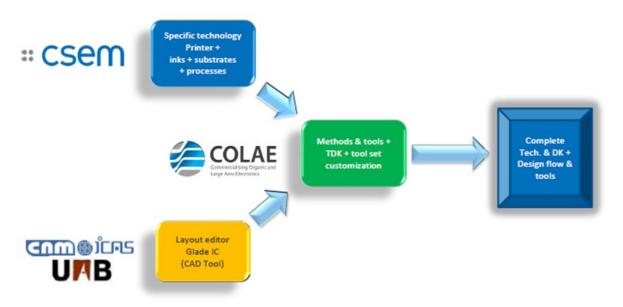

| Figure 2. Example of business model for UAB/IMB-CNM-CSIC R&D interests                  | 4  |

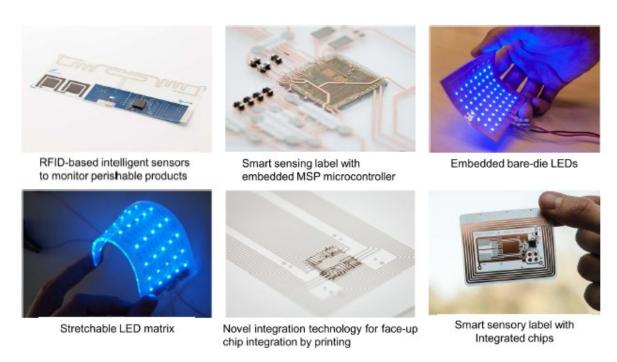

| Figure 3. Examples of hybrid electronics prototypes.                                    | 5  |

| Figure 4. Simplified complete manufacturing flow.                                       | 7  |

| Figure 5. VLSI typical flow.                                                            | 9  |

| Figure 6. Complete ASPEC flow                                                           | 0  |

| Figure 7. Resolution and throughput for highest quality levels of common deposition an  | ıd |

| patterning technologies for organic electronics                                         | 8  |

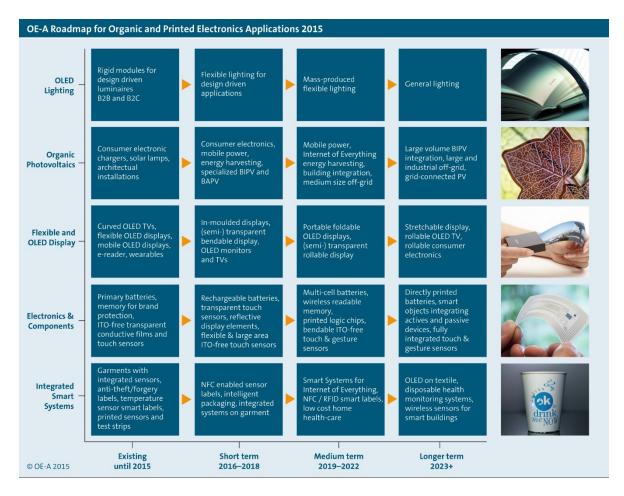

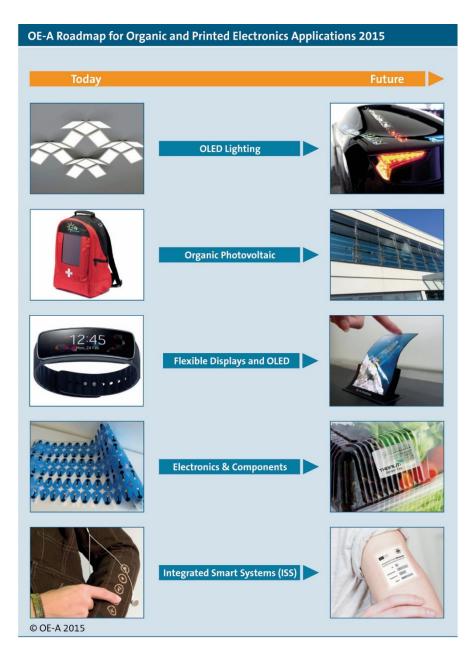

| Figure 8. OE-A Roadmap for Organic and Printed Electronics Applications 2015 (1). 1     | 9  |

| Figure 9. OE-A Roadmap for Organic and Printed Electronics Applications 2015 (2). 2     | 0. |

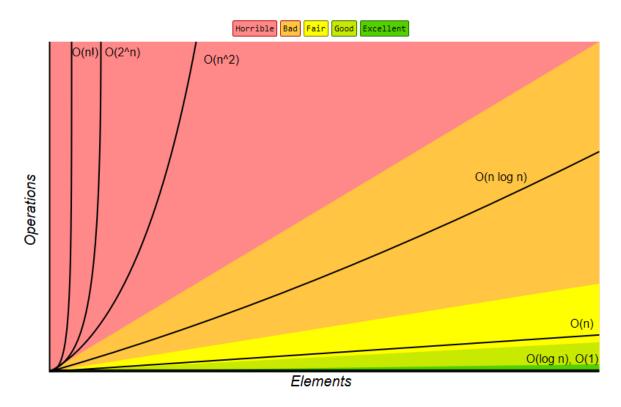

| Figure 10. Time complexity convenience                                                  | 25 |

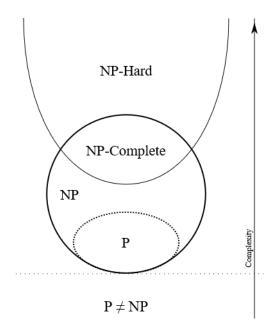

| Figure 11. Euler diagram for P, NP, NP-complete and NP-hard set of problems 2           | 6  |

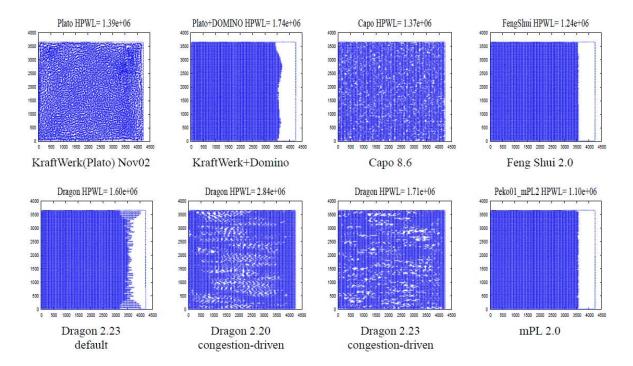

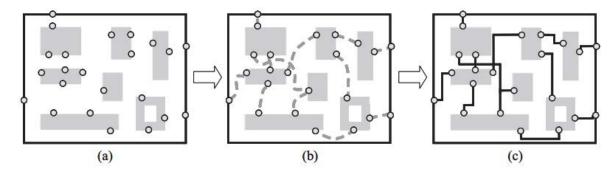

| Figure 12. Comparison of whitespace management                                          | 0  |

| Figure 13. Global and detailed routing                                                  | 1  |

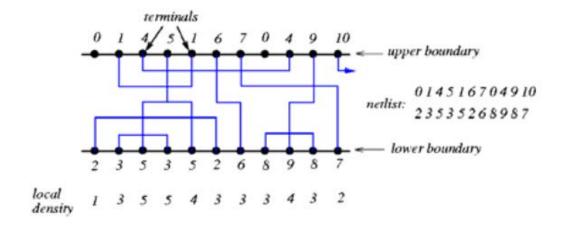

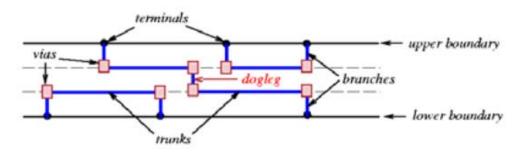

| Figure 14. Channel routing terminology                                                  |    |

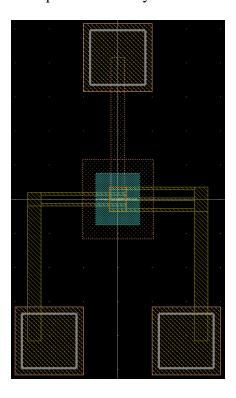

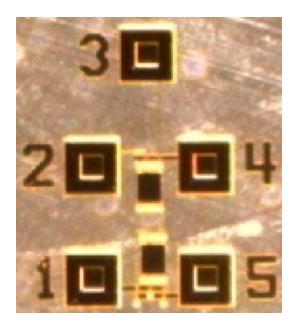

| Figure 15. OTFT layout (TUC/UAB)                                                        | 8  |

| Figure 16. OTFT (TUC/UAB).                                                              | 9  |

| Figure 17. OTFT layout (CPI/Neudrive)                                                   | 0  |

| Figure 18. OTFT (CPI/Neudrive)                                                          | 0  |

| Figure 19. OTFT layout (CEA-Liten)                                                      | -1 |

| Figure 20. OTFT (CEA-Liten).                                                            | -2 |

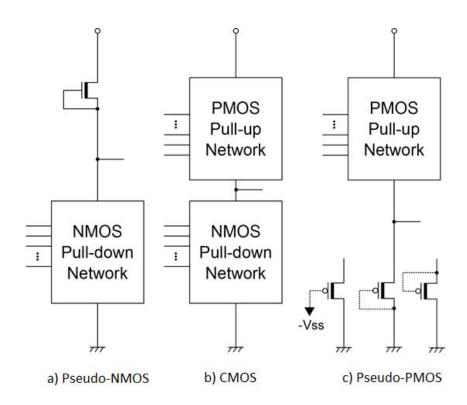

| Figure 21. Logic design styles                                                          | -3 |

| Figure 22. Examples of PMOS-only cells                                                  | 4  |

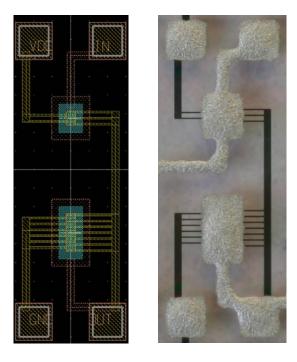

| Figure 23. Inverter (CPI/Neudrive)                                                      | 6  |

| Figure 24. Inverter (CEA-Liten)                                                         | -7 |

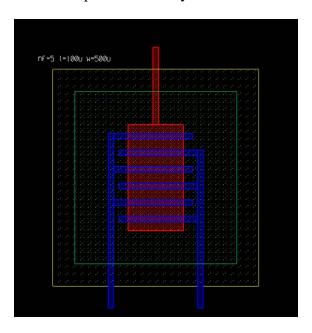

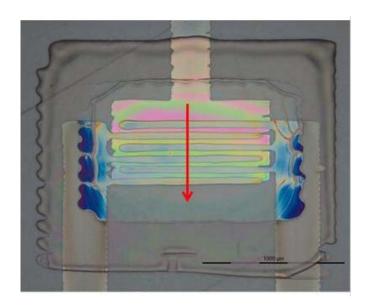

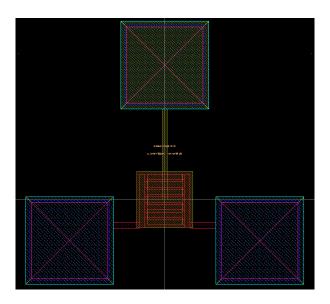

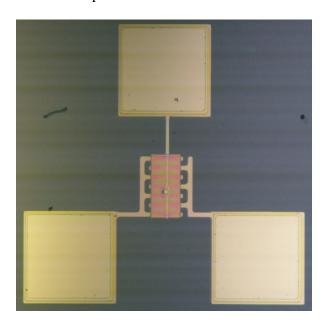

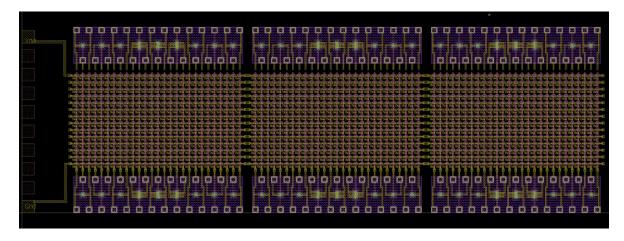

| Figure 25. IGA (TUC/UAB)4                                                               | 8  |

| Figure 26. IGA (CPI/Neudrive)                                                           | 9  |

| Figure 27. IGA (CEA-Liten)                                                              |    |

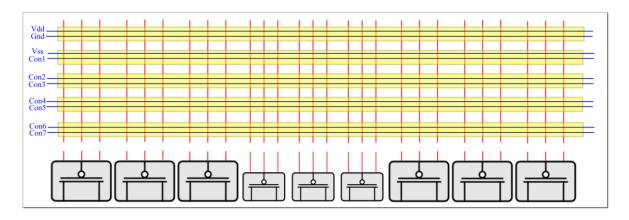

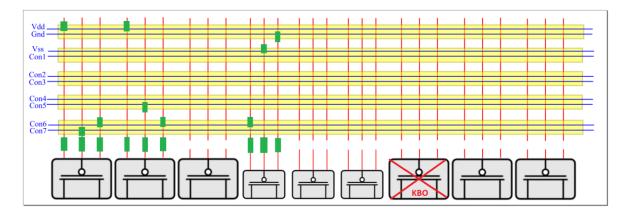

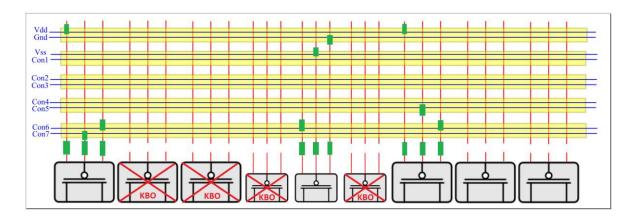

| Figure 28. BBC & wire cell schema (example 1)                                           | 6  |

| Figure 29. Nand2 mapping over BBC.                                                      |    |

| Figure 30. Nand2 mapping over BBC with another KGO map                                  | 8  |

| Figure 31. Mapping example in detail                                                    |    |

| Figure 32. P&R implementation flow                                                      | 4  |

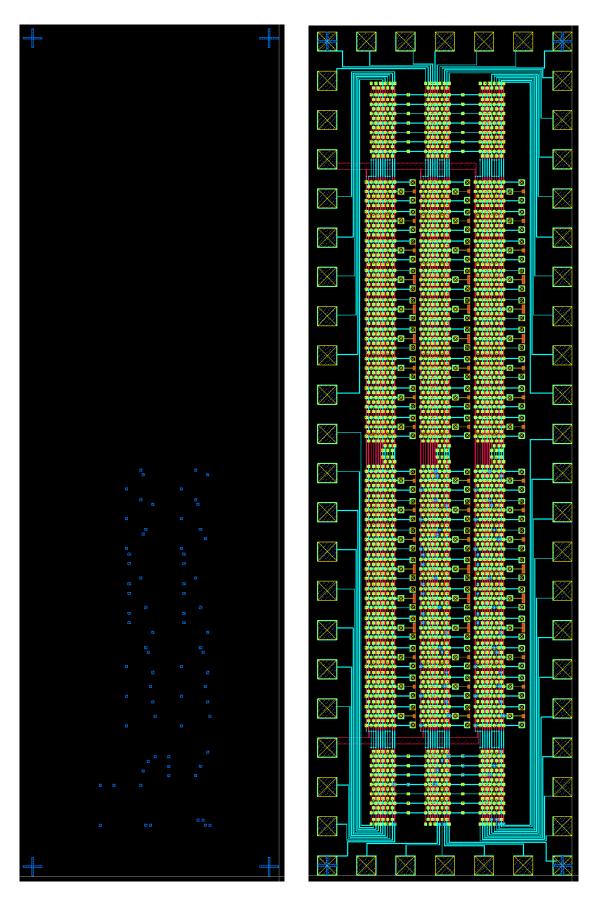

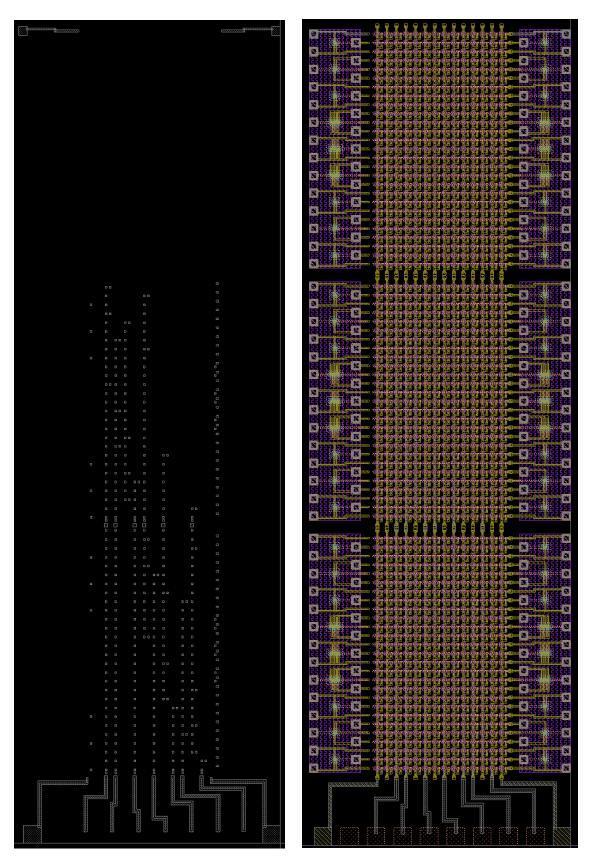

| Figure 33. C17 over CPI/Neudrive IGA (case 1). Only personalization metal (left). Final | al |

| IGA (right)11                                                                           |    |

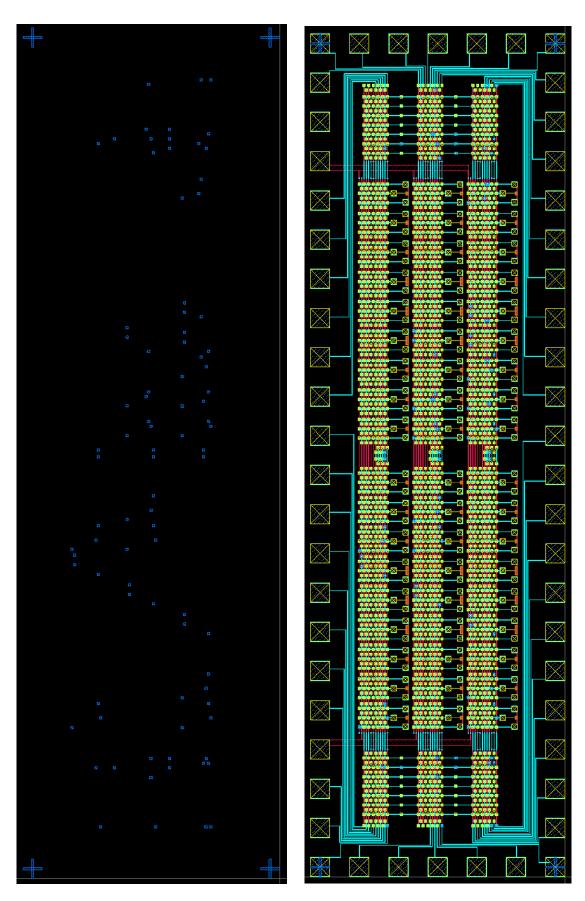

| Figure 34. C17 over CPI/Neudrive IGA (case 2). Only personalization metal (left). Final | al |

| IGA (right)                                                                             |    |

| Figure 35, C17 over CEA IGA, Only personalization metal (left), Final IGA (right), 11   | 4  |

# List of tables

| Table 1. Integrated Circuit Process Improvement with Time                        | 3    |

|----------------------------------------------------------------------------------|------|

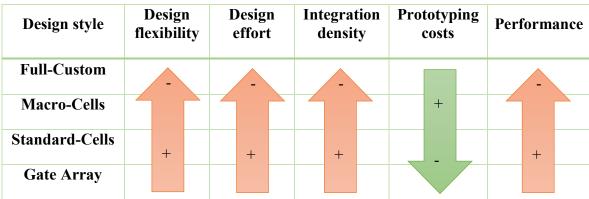

| Table 2. Design style comparison.                                                | 6    |

| Table 3. Most common time complexities.                                          | 24   |

| Table 4. Comparison of Placement techniques.                                     | 29   |

| Table 5. Cell library (TUC/UAB).                                                 | 45   |

| Table 6. Cell library (CPI/Neudrive).                                            | 45   |

| Table 7. Cell library (CEA-Liten).                                               | 46   |

| Table 8. Example of simple KGO map.                                              | 51   |

| Table 9. Logic synthesis and technology mapping example (before ABC)             | 53   |

| Table 10. Logic synthesis and technology mapping example (after ABC)             | 53   |

| Table 11. Benchmark examples over our fixed PMOS-only cell library (before ABC). | . 54 |

| Table 12. Benchmark examples over our fixed PMOS-only cell library (after ABC)   | 54   |

| Table 13. Benchmark examples over our fixed CMOS cell library (after ABC)        | 55   |

| Table 14. Mapping examples over different BBC configurations                     | 59   |

| Table 15. Outline of the P&R strategy.                                           | 64   |

| Table 16. Algorithm's specific notation.                                         | 64   |

| Table 17. Return codes.                                                          |      |

| Table 18. Main algorithm's pseudocode.                                           |      |

| Table 19. Subroutine 'Select_Gate'                                               | 68   |

| Table 20. Subroutine 'Place&Route'.                                              | 72   |

| Table 21. Benchmarks for P&R demonstrations.                                     | 73   |

| Table 22. P&R results                                                            |      |

| Table 23. Benchmark area based on Standard Cell design                           | 79   |

# List of acronyms

**ADC** Analog to Digital Converter

**API** Application Programming Interface

**ASIC** Application Specific Integrated Circuits

**ASPEC** Application Specific Printed Electronics Circuits

**AST** Abstract Syntax Tree

**BBC** Basic Bulk Cell

**CAD** Computer-Aided Design

**CLB** Configurable Logic Block

**CMOS** Complementary Metal-Oxide-Semiconductor

**CSV** Comma-Separated Values

**DEF** Design Exchange Format

**DFF** D Flip Flop

**DRC** Design Rule Check

**EDA** Electronic Design Automation

**E**<sup>2</sup>**PROM** Electrically Erasable Programmable Read-Only Memory (EEPROM)

**ERC** Electrical Rule Check

**FET** Field-Effect Transistor

**FOSS** Free and Open Source-Software

**FPGA** Field-Programmable Gate Array

**GA** Gate Array

GDS/GDSII Graphic Database System

**HCG** Horizontal Constraint Graph

**HDL** Hardware Description Language

**IDM** Integrated Devices Manufacturers

I/O Input/Output

IC Integrated Circuit

**IoT** Internet of Things

**IP** Intellectual Property

**IRDS** International Roadmap for Devices and Systems

ITRS International Technology Roadmap for Semiconductors

**KGO** Known Good OTFTs

**LEA** Left-Edge Algorithm

LEF Library Exchange Format

LSI Large Scale Integration

LVS Layout Versus Schematic

**MOSFET** Metal-Oxide-Semiconductor Field-Effect Transistor

NMOS N-type Metal-Oxide-Semiconductor

**NVRAM** Non-Volatile Random-Access Memory

**OE** Organic Electronics

**OE-A** Organic Electronics Association

**OLED** Organic Light-Emitting Diode

OOP Object Oriented Programing

**OPV** Organic photovoltaics

**OTFT** Organic Thin Film Transistor

**OTP** One-Time Programmable

**P&R** Place and Route

PAL Programmable Array Logic

**PCell** Parameterizable Cell

PDK Process/Physical Design Kit

**PE** Printed Electronics

PLD Programmable Logic Device

PMOS P-type Metal-Oxide-Semiconductor

**R&D** Research and Development

**RF** Radio Frequency

**RFID** Radio Frequency Identification

**RTL** Register-Transfer Level

SaaS Software as a Service

**SoA** State of the Art

**SoG** Sea-of-Gates

SC Standard Cell

**STA** Static Timing Analysis

**TVD** Test Vehicle Description

VCG Vertical Constraint Graph

VLSI Very Large Scale Integration

## 1. Introduction

## 1.1. Printed/Organic/Flexible Electronics

Printed Electronics (PE), also referred to as Organic, Flexible or Large Area electronics, depending on which characteristic is emphasized, is an interesting approach to develop low cost non-critical electronic devices in a complementary "More-than-Moore" pathway.

The intention of this approach is not to compete or substitute traditional Siliconbased chips, which follow a "More-Moore" course of action, but to complement those devices with alternative electronic elements that might be more suitable/cost-effective for certain applications. "Moore" refers to the well-known Moore's Law [1] from 1965 which states that the number of transistors per Silicon-based substrate would double every 2 years approximately, thus increasing integration density, performance and reducing chip costs per transistor, mostly associated to area and energy, since the speed is almost limited due to technology. Differences between "More-Moore" and "More-than-Moore" approaches can be explored in [2]. Basically, digital logic, microprocessors and mass memories are associated with "More-Moore" Complementary Metal-Oxide-Semiconductor (CMOS) scaling, whereas non-digital, different sensors, radio frequency (RF) devices, batteries, displays, etc. do not scale as fast as in Moore's Law and therefore fall into the "More-than-Moore" category. Recent convergences between "More-Moore", "More-than-Moore" and "Beyond CMOS" classifications make these divisions blurry and less relevant.

Periodically the semiconductor industry associations, formed by many institutions and firms, publish the set of documents, state-of-the-art reviews and market trends forecasts known as the International Technology Roadmap for Semiconductors (ITRS) [3]. These reports are good start points to explore recent events and tendencies in the vast knowledge areas covered by the semiconductor industry, for both "More-Moore" and "More-than-Moore" paths. A new roadmap has arisen recently, called International Roadmap for Devices and Systems (IRDS) [4], which is also worth checking.

In a similar manner the Organic Electronics Association (OE-A) [5] makes their own reviews, forecasts and roadmap, but focusing only in the Organic Electronics (OE) market. They periodically organize conferences, courses, projects and gatherings; and they are a reliable source of state-of-the-art progress information as well as enablers for the common advancement of the printed technologies and their applications.

In Chapter 2, dedicated to the state of the art (SoA), the reader will find the latest PE R&D trends and achievements, with special emphasis at circuit and systems level.

### 1.2. Motivations for this work

While traditional silicon-based chips have achieved a massive penetration into today's market, due to their impressive reduction in sizes and prizes, variety of purposes, and even flexibility in the sense of reprogrammability; Printed Electronics advantages are not to be underestimated, although they are not yet in mass market except for some few niches such as Organic Light-Emitting Diode (OLED) displays and lighting, organic photovoltaics (OPVs) and touch panels.

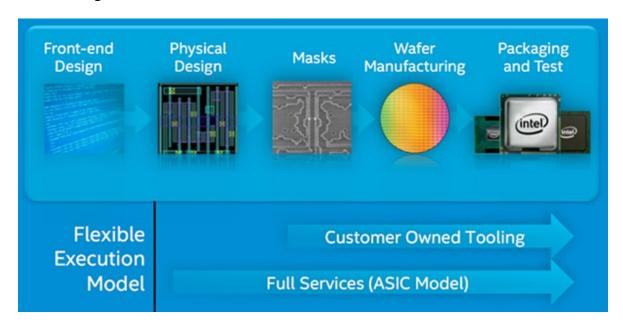

As Figure 1 depicts in the traditional electronic industry the business model evolved from Integrated Devices Manufacturers (IDM), where they designed and fabricated everything in one same place, to Foundries/Fabless/IP/EDA/Design houses where distributed teams designed circuits according to each Foundry's technologies [6].

## Semiconductor value chain deintegration: Business model's historical evolution

- IDM\*s are vertically integrated; In the 70's, most companies were IDM.

- · Foundries, focused on manufacturing, emerged in the 80's.

- · Fabless companies that outsourced manufacturing eventually became Foundries.

- . Design house have emerged in the last decade; Their focus is on IP.

Figure 1. Business model's historical evolution for electronics. <sup>1</sup>

2

<sup>&</sup>lt;sup>1</sup> Image source: Successful Semiconductor Fabless conference, Yole Développement, Mar. 2013.

Printed Electronics, as a non-mature technology, seem to walk again a very similar pathway, not only at technological scaling level (although at slower pace than Moore's Law) but at business model as well, now still quite vertical but expected to move to horizontal. With the advantage that tech foundries are much more affordable than silicon-based massive clean room facilities. Thanks to this, design teams should be able to fabricate prototypes with the technology they have. Table 1, from [7], summarizes the evolution of Integrated Circuits (IC) over silicon-based technologies; and from it we can recognize and place what would be the current state of PE technology and make comparisons. Current ICs over PE technologies, only considering digital processing capabilities, would be situated somewhere around the equivalent to year 1970's approximately, in terms of feature sizes while they usually implement large area circuits.

| Year | Process      | Chip<br>Size (mm) | Features (microns) | Wafer (mm) | Sample IC        | Clock    | Metal Layers |

|------|--------------|-------------------|--------------------|------------|------------------|----------|--------------|

| 1958 | Planar       | _                 | 100                | _          | First IC         | _        | _            |

| 1961 |              | $1.5 \times 1.5$  | 25                 | 25         | First silicon IC | _        |              |

| 1966 | _            | $1.5 \times 1.5$  | 12                 | 25         | SSI              | _        | _            |

| 1971 | pMOS         | $2.5 \times 2.5$  | 10                 | 50         | i4004            | 0.74 MHz | 1            |

| 1975 | pMOS         | $5 \times 5$      | 8                  | 75         | i8080            | 2 MHz    | 1            |

| 1978 | nMOS         | $5 \times 5$      | 5                  | 75         | Z-80             | 4 MHz    | 1            |

| 1982 | HMOS         | $9 \times 9$      | 3                  | 100        | i8088            | 8 MHz    | 1            |

| 1985 | HMOS         | $12 \times 12$    | 1.50               | 125        | i286             | 10 MHz   | 2            |

| 1990 | <b>HCMOS</b> | $12 \times 12$    | 0.80               | 150        | MC68040          | 25 MHz   | 3            |

| 1995 | CMOS         | $12 \times 12$    | 0.50               | 150        | Pentium          | 100 MHz  | 4            |

| 2000 | CMOS         | $15 \times 15$    | 0.25               | 200        | Pentium-III      | 1 GHz    | 6            |

| 2001 | CMOS         | $15 \times 15$    | 0.18               | 300        | Pentium-4        | 1.5 GHz  | 7            |

| 2005 | CMOS         | $22 \times 22$    | 0.10               | 300        |                  | 4 GHz    | 8            |

| 2010 | CMOS         | $25 \times 25$    | 0.06               | 300        | _                | 10 GHz   | 9            |

| 2015 | CMOS         | $28 \times 28$    | 0.03               | 450        | _                | 25 GHz   | 10           |

Table 1. Integrated Circuit Process Improvement with Time. <sup>2</sup>

Like in the Fabless model, designs should be sent, after adequate Intellectual Property (IP) protection [8, 9], to Foundries to be fabricated.

From our point of view, it is especially relevant the Technology & Knowledge Transfer paradigm considerations and best practices, for collaborating with other R&D agents to set up the whole business environment. Some examples were commented in [10, 11].

In the case of UAB/IMB-CNM-CSIC a new set of industrial Research and Development (R&D) opportunities were explored and launched for these increasingly interesting organic/printed technologies. Several ambitious projects (TDK4PE [12], ASPEC-TDK [13], MEF3-IRX [14], PEC4 [15]) obtained public funding and were successfully carried out over the years by the research groups I have been involved with. The preferred modus-operandi of the partnerships to develop Printed Electronics

\_

<sup>&</sup>lt;sup>2</sup> Table source: V. G. Oklobdzija. [7]

prototypes is shown in Figure 2. The UAB/CNM fabless role would target a specific technology provided by a partner foundry, besides developing their own inkjet printed process. Then we would produce Design Kits, based on our preferred Top-Down Design Flows and open/free-tools environments, so that anyone (ourselves, or designers from the foundry itself, or any other third party fabless design team) could produce prototypes for tape-out in such technologies.

Figure 2. Example of business model for UAB/IMB-CNM-CSIC R&D interests. <sup>3</sup>

We have worked along with different partners, academic, industrial and fostering organizations, like CPI [16], NeuDrive [17], CEA [18], CSEM [19], ENEA [20], COLAE [21], CETEMMSA [22], Flexink [23], Infiniscale [24], Sensing Tex [25], 3D Micromac [26], PhoeniX Software [27], URV [28], UFRGS [29], TUC [30], UAlg [31]... Each one of them provided their contributions in their respective areas of expertise, from modelling and simulations, to design kits, fabrication technologies, prototypes, characterization and testing processes. The idea is to obtain circuits that work, first with very simple functionalities, and then capable of scaling according to the technologies available.

It has been demonstrated that it is possible to achieve interesting applications using organic/printed technologies. But even so, a typical question arises on standard silicon-based environments. Why would it be necessary to perform any kind of digital processing using these technologies, instead of using the more mature, small, reliable and efficient silicon-based devices? The answer is clear: heterogeneous integration. Having everything integrated, for example, sensing + processing + energy in the same saleable substrate, can profit from the benefits of printed technologies for certain applications, especially when flexibility is required (e.g. wearables, automotive, etc.). To establish the

\_

<sup>&</sup>lt;sup>3</sup> Image source: TDK4PE documentation. [12]

desired functionalities is key to set the choice among technologies. So far, hybrid approaches have been the most market-ready options, and they are a perfectly valid middle-point segment. In Figure 3 we can observe some examples of hybrid prototypes, including RFID-based sensors, labels, LEDs, and so on. These few samples can also perform computing works thanks to their Silicon-based associated chips (hence the terms intelligent/smart).

Figure 3. Examples of hybrid electronics prototypes. <sup>4</sup>

But to obtain the desired integration in Printed Electronics it is necessary to be able to make stand-alone functional circuits. The typical structures for achieving circuits are basic logic gate libraries (inverters, AND, NAND, NOR...) that allow digital circuitry, analog cells for signal conditioning, Analog-to-Digital Converters (ADC), memories and I/O structures.

The main goal of the EDA field [32-34] has always been to automate design tasks and processes so that is easier, faster and, ideally, more reliable to obtain final electrical products. For this purpose there are many strategies, algorithms and tools from different vendors, all along the full design and fabrication flows, developed through many years for conventional Large Scale Integration (LSI) and Very Large Scale Integration (VLSI) target circuits. In this EDA context we can see that there is much R&D to be done and improved for helping Printed Electronics designers and, by extension, its industry. Sometimes it is possible to benefit from research and achievements done in Silicon-based environments, but in other cases it is necessary to define new ideas and strategies to deal

-

<sup>&</sup>lt;sup>4</sup> Image source: Holst Centre. [292]

with issues and particularities that are not contemplated in those areas, such as the reliability of the materials, fluidic properties, degradation, high variability, yield and fault distribution differences; even within the same technological process.

## 1.3. Digital Circuit Design styles

As briefly described in [35, 36] we can classify circuit design styles according to different criteria; most importantly regarding flexibility versus design effort. In this scenario flexibility corresponds to whether the physical design (layout), to be later fabricated, is going to be designed in a completely handcraft manner (full-custom); by using different libraries (semi-custom); or by using IP components (processors, buses, NoCs, peripherals, memories, ADC...) to build complex systems (SoC, MPSoC). This work is centered in the semi-custom design methodology, according to the current state of the art of the technology. Its basic choices as predesigned and pre-characterized libraries (Standard-Cells) or predefined templates with prefabricated transistors or gates that will be custom connected (routed), according to the desired functionality (Gate-Array). We can find comparisons between design styles at low level of design abstraction (full- and semi-custom), including most notable benefits and drawbacks of each methodology [37-39].

Table 2 depicts a brief comparison of the main differences between circuit design styles. The colors of the arrows illustrate whenever a Gate Array (GA) style choice is advantageous or not, since it is more similar to the Inkjet Gate Array (IGA) design style that we will propose to use.

Table 2. Design style comparison.

## 1.4. Design Flows & Process Design Kits

#### 1.4.1. ASIC overview

A very simplified traditional (Silicon-based) complete manufacturing flow is shown in Figure 4.

Figure 4. Simplified complete manufacturing flow. 5

This complete flow typically starts with a Register-Transfer Level (RTL) specification that describes the functionality of the system to be produced [40]. The most common Hardware Description Languages (HDL) for RTL coding are the VHDL and Verilog standards [41]. References for better understanding VHDL and Verilog languages and usage can be found in [42-51], and also some concise comparisons in [52, 53]. There are many software tools capable of creating (as an Integrated Development Environment IDE), parsing, compiling, elaborating, synthesizing, simulating and verifying HDLs into different hardware platforms (depending on the vendors). Typically, although not necessarily, VHDL is more used to build small synchronous designs or virtual components (IPs) in Field Programmable Gate Arrays (FPGA), from firms such as Xilinx, Lattice, Altera (now part of Intel), and many others who provide their own IDEs; while Verilog is more used for other design flows such as for Cadence, Mentor Graphics or Synopsys tools (commonly known as "the big 3" in the EDA business). It is also possible to start with a schematic circuit description, instead of using an RTL abstraction. In both cases components can be created or reused from other libraries, included the ones supplied by the vendors for their devices.

-

<sup>&</sup>lt;sup>5</sup> Image source: Intel. [291]

A physical design, also called layout, represents the different shapes that will generate the so-called masks that will be used for fabricating the circuits. Circuit layouts need to be created in compliance with the design rules of the targeted technology, that report of the feature sizes set to obtain a required yield and quality. These are verified via Design Rule Checks (DRC). Furthermore, circuit electrical rules are verified via Electrical Rule Checks (ERC). Automatic physical verification procedures, such as DRCs and ERCs, are also referred to as signoff checks. Typically they are included into PDKs to check the correctness of designs before sending them to the foundries. They usually have visual debugging capabilities.

Another kind of signoff procedure is a Static Timing Analysis (STA). Such analysis needs to be done for ensuring that timing requirements are satisfied [34, 54, 55]. The STA is a process that checks exhaustively that a circuit has the proper timing. It does so by calculating all the possible delays: intra-cell delays, paths, cycles, etc. An STA is not intended to check for functional correctness (i.e. functional verification).

As a final corroboration step an LVS is performed. For that, the layout has to be extracted into a netlist which includes Input/Output (I/O) pins, transistors and nets. This netlist is then compared to the schematic netlist, which should contain the same information. If both netlists match perfectly structurally then they are both representing the same circuit functionality and, only then, the layout is ready for fabrication (tape-out).

Fabrication processes start with producing the masks to be used on the wafers as photolithographic (e-beam or others) methods require, whether they are for addictive or subtractive techniques.

After fabrication, there will be a packaging step to encapsulate and protect the chips. Their I/O pins will make them connectable to other devices. Lastly, the chips will have to pass functionality tests and endure reliability tests, depending on the maximum stress and expected lifetime given by the manufacturer's warranty, to be ready for the market.

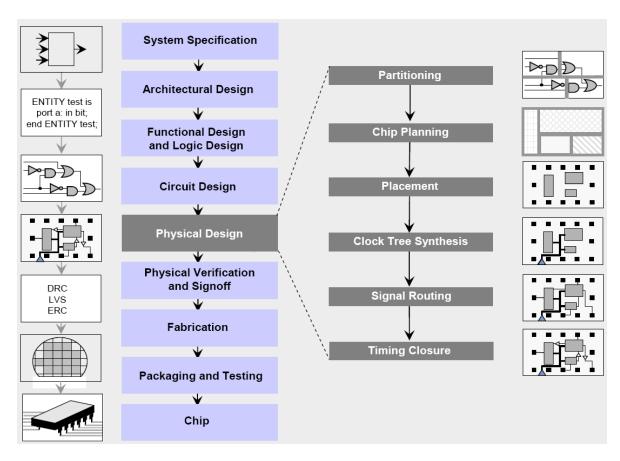

Evidently, each one of the steps in this flow can be further decomposed into smaller steps, as shown in Figure 5. Special attention is given to the physical design part, which is essential for the scope and goals of this dissertation.

Figure 5. VLSI typical flow. 6

Usually, physical design, where this research is focusing, comprises several stages that might include Partitioning (dividing the design into blocks according to the preferred strategy), Floorplanning (dividing the available substrate area into regions), Placement (of all cells assigned to each region), Clock Tree synthesis (for providing proper synchronized clock signals to every sequential component of the circuit), Routing (connecting locally and globally, elements, components and regions), and Timing Closure (which verifies that the entire design meets the timing constraints specified, such as the critical path, which determines the maximum clock frequency). An interesting reading comprising several relevant areas is the selection given in [56].

#### **1.4.2. ASPEC overview**

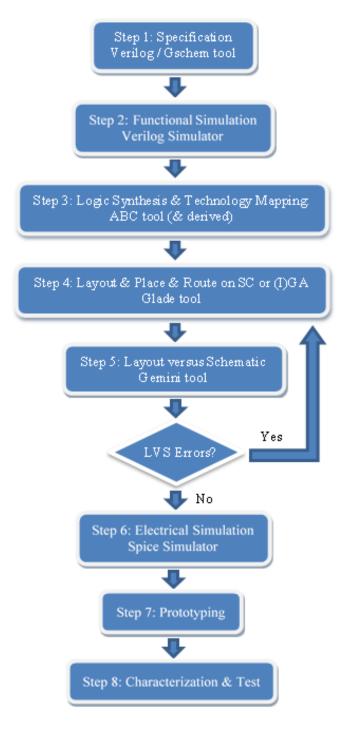

The design flows needed to be adapted to PE/OE technologies conforming to their inherent particularities. An initial idea was proposed in [57] trying to develop a semi-custom design methodology targeting Standard-Cell [58, 59] and Inkjet-configurable Gate Array methodologies [60-62] tailored to the particularities of the technologies. The

\_

<sup>&</sup>lt;sup>6</sup> Image source: A. B. Kahng. [182]

complete flow set-up for this research together with the related EDA tools is shown in Figure 6, as given in [62].

Figure 6. Complete ASPEC flow.

We can observe that this flow covers the entire chip production, from specification to final prototypes. The selection and usage of Free and Open-Source Software (FOSS) tools aligns perfectly with the current low complexity of PE prototyping technologies

available to designers<sup>7</sup>. This way, small design teams do not require spending on costly infrastructures and expensive licenses. In this research work my goal is to prove that this flow is effective and can be reapplied for any ASPEC as long as the corresponding technology files are available.

As commented for VLSI environments, a design can start either with a specification in HDL (in our case Verilog) or with a schematic drawing. For schematics we selected Gschem; part of the gEDA tool distribution [63]. For the HDL circuits expressed in Verilog I selected Icarus Verilog [64] for synthesis, and GTKWave [65] for waveform screening of functional simulations.

Logic synthesis and technology mapping are key steps for any technology, including PE. In this area, there are EDA tools for circuit optimization such as minimizing the number of gates (and consequently transistors) by applying Boolean algebra and producing combinational logic reductions. The selected tool for this purpose is ABC [66]. Area is a significant factor due to the fact that PE technologies are still showing low integration density (in terms of transistor per mm²). It is obvious that if we manage to reduce the gate count we can integrate the same chip functionalities while saving substrate area. The technology mapping process, placed between logic and physical synthesis, takes into account technology dependence after a technology independent synthesis step. In a semi-custom design methodology, circuit implementing requires an associated library of digital cells.

For instance, in some technologies such as unipolar (i.e. PMOS or NMOS only) some particular gates might not be available, due to the low performance or functional inabilities of series transistors. Hence it is necessary to specify a differentiated cell library for every technology. In the particular case of the PE technologies that I got access to, most of them are based in PMOS-only design style. This is due to the fact that in many OE technologies, the NMOS transistors don't reach a good enough mobility and conductivity as the P-type ones [67, 68]. Therefore, for most foundries8, the CMOS design style [69] is not yet enabled for digital circuits. However, CMOS is vastly preferred in silicon-based VLSI systems mainly because of its low static energy consumption and high noise immunity, which makes it more robust. A detailed explanation of interconnection noise can be found in [70].

Once we have minimized and mapped the circuit to a particular library, we continue with the physical design, either following a Standard Cell or Gate Array approach, using layout tools such as Glade [71] or KLayout [72]. The placement and routing will be done according to the circuit netlist.

As mentioned in the VLSI case, after physical synthesis it is necessary to perform physical verification checks, including DRC, ERC and LVS, to check wether the layout

\_

<sup>&</sup>lt;sup>7</sup> More advanced technologies (e.g. Thinfilm Technologies or PragmatIC) are oriented to application markets, thus not available for third parties.

<sup>&</sup>lt;sup>8</sup> Except those mixing organic (for PMOS) and oxide (for NMOS) transistors.

is well drawn and matches the circuit netlist. For this, we use both Glade and Gemini LVS tools [73].

Electrical simulations are needed in order to check performances including parasitic capacitances and resistances. In this case we use customized models for Spice simulators [74] such as Ngspice [75] or AIM-Spice [76].

As a last design step, Glade is used to generate the GDSII files that are sent to the foundry to be fabricated in the targeted process. The obtained circuits go through a series of characterization and test procedures. These will determine, for instance, the overall yield achieved (and the fault distribution of the OTFTs, for technologies with mid-yield in OTFTs). This characteristic is key for the proposal of our EDA tool strategy, as it will be explained in detail later on, concretely for technologies that do not achieve a high yield (close to 100%). Their results are required to obtain circuits out of mid-yield OTFT fabrication processes and will help to fine tune the models and design rules for future improvements on the targeted technologies.

## 1.5. Digital printing for personalized digital circuits

The Inkjet-configurable Gate Array (IGA) design style concept, introduced in [60] and developed through [77-82], relies on a crucial PE characteristic: the ability to use digital printing for metallization on top of different PE/OE substrates. As described in detail in [83] digital printing is a fabrication process that allows reproducing text, images and patterns in different coordinates of the substrate with control and precision. Since the design to be printed is described digitally (e.g. in our case a layout represented in the standard Graphic Database System GDSII format [84-86]), mapping circuits onto PE/OE substrates with prefabricated transistors in a GA disposition should be cheaper and more reliable than having to fabricate different masks for every circuit. Furthermore, it allows circuit-by-circuit personalization as a key aspect.

Traditionally in silicon-based environments designs are imprinted onto wafers by using a unique set of masks for a particular chip design. This allows for mass production (high volume) of that design over a big amount of wafers. Such masks are very expensive and are fixed. They only permit the production of one particular design repeatedly for a targeted process technology. Whenever design changes, masks (equivalent to plates in the conventional printing industry) also have to be changed (analog printing).

The classical silicon Gate Array (GA) or Sea-of-Gates (SoG) approach allowed circuit personalization for specific circuits by changing only metallization (and via) masks at the last stages (layers) of the fabrication process. Cost reduction was achieved by sharing the substrates among different circuits but they still need to fabricate those individual masks.

The IGA concept starts from that GA or SoG concept and moves masks (for equivalent analog printing) into files (for digital printing).

In this scenario the circuits are fabricated in two separated steps:

- 1) Fabricating the elementary devices on the substrate (e.g. 50 micron thickness of PolyEthylene Naphthalate PEN). The IGA substrate consists in an array of unconnected OTFTs (or cells), deep-metal wire cells and I/O pads.

- 2) Personalizing the circuit on top of that IGA substrate; which consists in mapping a circuit over the IGA template by Placing and Routing gates and cells using the OTFTs available.

The circuit layout obtained after the Placement and Routing is digitally printed over the IGA substrate, by using any of the suitable customization technologies available. Some of these techniques have been explained in [80]. In this work this is done at transistor-level, which allows more flexibility. While the IGAs could be designed at digital cell-level and even higher cell-level hierarchies (e.g. logic blocks in FPGAs). These options increase the current integration density at the cost of limiting circuit flexibility.

With this IGA design methodology, digital printing is highly beneficial, from the point of view of manufacturing costs, as opposed to the use of masks which would only allow to map circuits in a fixed pattern. However, it is slower since it is not as highly parallelized fabrication process as when using masks.

Moreover digital printing also provides the ability to change the function of the design imprinted over the different substrates, by changing the Placement and Routing design depending on the restrictions that we want to impose.

# 1.6. Placement and Routing problem/strategy

Placement and Routing (P&R), also referred to as physical synthesis, is one of the most important and challenging process in any circuit design flow. It is one of the key steps due to the time and efforts required by any design team, especially when scaling to VLSI chips and beyond. Thus, P&R design automation has been an historical focus point of the scientific and industrial community, in order to introduce into the market more reliable, compact and higher performance electronic products in less time (time to market).

In our case, the Inkjet-configurable Gate Array design style, together with the digital printing capabilities and the two-step fabrication process, provides us with the chance of performing P&R in a yield-aware manner trying to overcome, one of the main bottlenecks for many PE technologies.

The yield awareness is a critical constraint in our methodology. It is evident that, the lower the yield, the lower it is the probability of obtaining a circuit working correctly. This relation is not directly proportional; i.e. having a yield of 70% in terms of transistors, with a random failure distribution, will dramatically reduce the chances of obtaining a working circuit to almost none. This is especially relevant for mid-yield/high variability PE technologies, where several OTFTs could potentially fail at completely random locations in the substrate.

Whenever the expected yield of a technology is lower than the desirable 99.99% our strategy introduces a new step in between the other two fabrication processes (fabrication of the IGA substrate and circuit personalization). This middle step consists in a testing and characterization process of all OTFT devices present in the IGA substrate, resulting in a Known Good OTFTs map (KGO) that list the location of the working transistors in the array. This KGO map is very likely to change from foil to foil. Some reasons causing failing OTFTs can be found in [87]. The Placement and Routing will produce circuits that take this KGO map into account. Thus, the P&R will adapt to the fault distribution to produce working circuits out of mid-yield OTFTs foils since we eliminate the possibility of using faulty OTFTs. Since we rely on real test data, we do not need to use probabilistic models over virtual layouts for yield prediction, as in [88].

This middle characterization stage has also currently some associated drawbacks: (1) equipment, labor and time required for individual OTFT testing (i.e. using probe stations); and (2) pads required in the layout design for the probes to contact and test each OTFT. Moving to cell-based IGA these pad area requirements are lowered so it is possible to increase the integration density.

A detailed review of the P&R state of the art is provided in chapter 2, while our specific proposal is developed in chapter 4.

#### 1.7. Goals of this work

In summary, the main goal of this research work is to develop the EDA algorithms that provide full physical synthesis capabilities for Inkjet-configurable Gate Array Printed Electronics circuits.

We will be able to obtain functional circuits by the means of automatically generated layouts, according to our IGA designs style focusing on digital printing customization.

Since the fault distribution at transistor level might vary from foil to foil, even in the same technology and fabrication run, the powerfulness of our approach is that we can run the algorithm as many times as required for every specific PE circuit after its characterization to know each foil specific KGO map (whenever necessary, according to the expected yield of each technology), thus allowing its individual wiring, what maximizes yield at circuit level.

The intention is to provide a good P&R solution, according to the given constraints. For that purpose, this dissertation will detail how a conjoint constructive greedy P&R heuristic was devised, demonstrating its convenience for PE-based circuits.

This research work is intended to increase PE circuit design automation, hence reducing the time and efforts needed to successfully implement PE circuits, depending on the technology addressed and its corresponding yield. To clarify, the title of this dissertation includes the term Digital<sup>2</sup>, which is just a reference to both digital circuits and digital printing.

This methodology can also be used for other purposes than circuit yield increase. Functionalities such as circuit personalization, for which we can print individual circuit identification codes (such as a MAC internet address), can avoid the use of complex E<sup>2</sup>PROM or NVRAM devices.

In the following chapters of this dissertation the concepts will be explained to the reader, as well as the current state of the art, our approach to the problem at hand, the strategy and means to solve it in the most efficient way as currently possible, results obtained and final observations.

# 2. State of the art for PE & EDA

# 2.1. Digital printing techniques for building digital circuits

Analog printing techniques refer to the traditional methods of printing. In the conventional industry this would mean relying on a set of predefined plates that will imprint the same patterns (e.g. letters) into a targeted substrate (e.g. paper) over and over again. This allows for mass production (high volume) of a unique design. Analog printing methods are, for instance, flexography, gravure, offset, and screen printing. In the semiconductor industry the plate concept is the same, yet it has a different nomenclature. In this case chip fabrication relies on a set of predefined masks which will allow to imprint the designs onto and within the substrates (i.e. wafers) by combining a series of advanced fabrication processes such as photolithography, deposition, oxidation, etching, etc...

On the other hand digital printing techniques do not require masks for fixed designs. They allow to change the pattern to be imprinted over the substrate on demand. This provides more flexibility to produce different designs and lower fabrication costs, whenever such designs are intended to vary, regardless of the amount to be produced. These techniques consist in depositing the inks over the substrates without applying any kind of contact ever (and thus no pressure) on them. Some current digital printing methods are Inkjet (and other higher resolution variants such as Electrohydrodynamic Inkjet printing or Superfine Inkjet printing), and Aerosol jet printing.

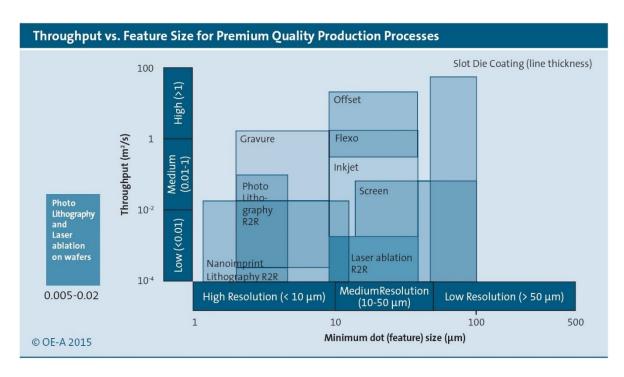

The following Figure 7, from the OE-A, as it appears in their original 6<sup>th</sup> Edition report, gives a brief idea of what kind of printing techniques can be used to produce PE/OE applications, comparing their current usual resolutions and throughputs.

Figure 7. Resolution and throughput for highest quality levels of common deposition and patterning technologies for organic electronics. 9

As it could be expected, techniques based on photolithography, have a very high resolution and accuracy, but also lower throughput levels; while other processes that require less precision, such as offset, flexography, inkjet or screen-printing, have a much better production rate. In-depth comparisons, advantages and drawbacks between printing techniques, whether analog or digital, can be found in [77, 89, 90].

# 2.2. Driving applications for PE circuits

In Figure 8 and Figure 9 it is possible to see the latest roadmap and examples of current and potential applications summarized by the OE-A.

-

<sup>&</sup>lt;sup>9</sup> Image source: OE-A. [5]

Figure 8. OE-A Roadmap for Organic and Printed Electronics Applications 2015 (1). 10

<sup>&</sup>lt;sup>10</sup> Image source: OE-A. [5]

Figure 9. OE-A Roadmap for Organic and Printed Electronics Applications 2015 (2). 11

As shown in these figures, market driven applications that are already available are, for instance, OLED lightings, photovoltaic chargers, OLED displays for multiple consumer electronics devices, batteries, conductive films, sensors and labels of various types. All of these examples can be introduced in the industries of Internet of Things (IoT), automotive, health care, wearables, packaging, leisure... With the continuous improvement of the technologies at every step of the manufacturing chain the applications are expected to become more flexible, efficient, reliable and complex; allowing more possible functionalities while benefiting from the low costs associated to Printed

<sup>&</sup>lt;sup>11</sup> Image source: OE-A. [5]

Electronics. Some examples in the scientific literature can be found, for instance, about organic photovoltaics [91, 92], flexible batteries [93, 94], electro-optic devices [95-97], OLED displays [98-100], logic and memory components, including Field Effect Transistors (FETs) and Organic Thin Film Transistors (OTFTs) [101-106], sensor arrays [107-113] and Radio Frequency Identification (RFID) tags [114-118]. Even a microprocessor was shown in [119, 120].

More examples of recent accomplishments on PE circuits and systems can be found in [59, 121-126], even with Programmable Array Logic (PAL) [127]. Additional progresses and findings with different focuses and objectives are excellently explained in the dissertations written by my colleagues [82, 90, 128]. Another recent interesting dissertation, related to OTFT modelling and simulation, is [129]. In relation to Design Automation for PE applicability I thoroughly encourage the reader to review [130, 131] as well, since they are closer to the scope of this work.

In the case of our research group we explored different circuit design styles, from a full-custom approach to Standard-Cells (SC) and Gate Array (GA) (also called masterslice) based configurations. The first ones apply a similar vision of the Application Specific Integrated Circuits (ASIC) model [132, 133], and therefore were adapted to what we called Application Specific Printed Electronics Circuits (ASPEC). The latter was a novel concept introduced in [60], and extended through [77-82], that provides more flexibility and deals better with Printed Electronics intrinsic characteristics and issues. Over the years, our research group proposed methodologies, design flows and Electronic Design Automation (EDA) / Computer-Aided Design (CAD) tools for minimizing all kinds of costs (free licensed, portable, customizable, standardized and powerful, yet user friendly) [58, 62, 128, 134-140]. A recent review of our own group's inkjet fabrication process can be found in [141].

For further knowledge about PE/OE and possible applications I suggest the books [142-144].

### 2.3. Relevant EDA tools

The EDA tool landscape is quite vast, addressing a wide range of missions at any step of any chip design flow. Besides each tool's purposes, there is also another major distinction to be done among such software products: usage fees.

In the commercial domain we can clearly highlight the so called 'big 3' companies: Cadence, Synopsys and Mentor Graphics (recently acquired by Siemens). All of them provide tools and licenses for any of the ASIC designs steps. Their business models cover many aspects of R&D, including monitoring the protected/FOSS/academic breakthroughs for incorporating novel ideas (the ones that have profit potential, of course) into their design flows and tools [56]. We can remark the pertinent solutions that each one of them provide:

- 1) Cadence: Within the Cadence tool portfolio the most interesting ones for the topics covered by this dissertation are Cadence Encounter RTL Compiler, and now successor Genus Synthesis. They are both complex tools for RTL (usually Verilog) and physical synthesis (P&R) of VLSI systems. They work together with the Innovus placement tool and Virtuoso suite for schematics and layouts. Most of their features can be checked at their website [145]. They accept standard format files for different steps of the design flow such as Verilog, LEF/DEF files, GDSII, Liberty, map, etc.

- 2) Synopsys: In the case of Synopsys we have the Design Compiler for RTL synthesis, and IC Compiler II for P&R. These tools require the Verilog netlist plus an additional design constraint file .sdc. As with any other tool, many variables/commands can be passed/executed via scripts; commonly Tcl [146]. They work with their Custom Compiler suite for schematics and layouts. There is more information available at their website [147]. From Synopsys (Ciranova) it was also interesting the PyCell Studio tool [148] for universal OpenAccess PyCell development in Python, with their own layout Application Programming Interface (API). The idea was quite convenient since OpenAccess-based PCells can be imported on Cadence, Mentor and, of course, Synopsys tools; rather than using SKILL or other languages for PCell creation/operations. This way PCells were intended to be portable to the major vendors. The OpenAccess [149, 150] philosophy and technology together with the OpenPDK project are some of the proposals fostered by the Silicon Integration Initiative Si2 [151].

- 3) Mentor Graphics: The digital design alternatives provided by Mentor Graphics that grab our attention are Oasys-RTL for physical RTL synthesis, Olympus-SoC for P&R and Calibre InRoute for signoff. Also the Tanner Place and Route tool. More details can be seen at their website [152].

On the other hand, for FOSS EDA tools we can highlight the following contributions:

- 1) Qflow: The Qflow suite [153] is an open-source digital synthesis flow. Typically a set of tools like this one manages a subset of FOSS target-specific tools for each step of the design flow. This framework also handles/converts the I/O files of each tool so that the flow is consistent and can work without needing further conversions. Qflow is firstly composed by Yosis [154] for HDL-Verilog synthesis, logic synthesis and technology mapping using ABC [66]. It also integrates Graywolf [155] for placement, Qrouter [156] for routing, and Magic [157] as layout editor.

- 2) UMpack: The UMpack suite [158] is also an open-source set of tools for physical design. It includes Parquet for floorplanning, MLPart for partitioning, and Capo for placement. As a suite it also contains support libraries and additional files for interoperability.

- 3) Alliance: The Alliance suite [159] is a set of free tools that includes all major steps of a complete design flow. It performs HDL-VHDL synthesis, logic synthesis,

- and placement and routing. It was the set of tools utilized in [130], which is a very interesting work for us, according to our scope.

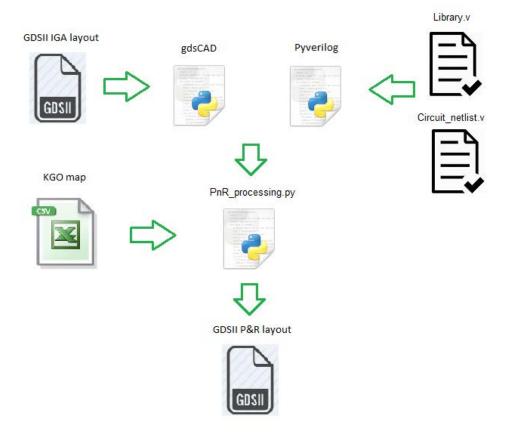

- 4) Python-based: Python [160] is a highly versatile and powerful interpreted language. There are many libraries, packages, and applications available online. It is utilized by several EDA tools (e.g. Glade [71], KLayout [72]...) mainly for PCell developments, scripting, and layout/database APIs. But there are more Python-based EDA tools, not only for layout editors. Some of them are particularly interesting for us. For instance, for processing GDSII layouts I have used gdsCAD [161], fixing some of its non-solved issues, since it is no longer being maintained. For HDL-Verilog processing I have used Pyverilog [162], which also utilizes Icarus Verilog [64]. Pyverilog is explained in detail in [163]. Both packages have further dependencies that require installation. These two frameworks, gdsCAD and Pyverilog, were used by my P&R tool in order to handle the input files needed and to demonstrate our P&R ideas on the IGA designs. Since they are open-source it is possible to see the inner data structures, procedures, and features implemented within them; and add/modify them whenever convenient/necessary.

There are many other flows and tools for different purposes, whether with commercial or free licenses, such as Symica [164], XicTools [165], eSim [166], Astran [167], MyHDL [168], KiCad [169], LayoutEditor [170], Electric [171], and so on and so forth.

Other interesting works concerning Analog IC Design Automation can be found in [172-176]. They comment on the main differences and challenges between the digital and analog design automation domains, and provide insights about design flows, tools, physical design and PCells.

More specific details of P&R tools and related algorithms are explained in detail in the following subchapter.

# 2.4. Placement and Routing

#### 2.4.1. Preliminary concepts

To better understand the P&R problem we will review henceforth some of the basics of computational science and algorithms, with special attention to their applicability on circuit design automation.

I must recommend the following reference books [177-182], since they are very convenient for the scope of this dissertation. Typically this kind of books have chapters where they introduce algorithmic complexity. To date, in the scientific mathematical/computational domain, a solvable problem, can be divided into P or NP problems. P problems are the ones that can be solved in Polynomial time by a

deterministic Turing machine [183, 184]; while NP problems are those that can be solved by a Non-deterministic Turing machine also in Polynomial time; i.e. a problem is in NP if we can test whether a supposed solution is correct in a fast manner (polynomial time). Typically time complexities for classifying algorithms' speed are expressed using the Big O notation; a subset of Bachmann–Landau (asymptotic) notations [185, 186]. Some of those complexities are shown in Table 3, ordered by speed. Generally the time complexities are considered for their worst case scenario although sometimes a solution might be found in less time, what is designated as best and average times. A chart with their corresponding convenience related to the number of elements (n) being processed is shown in Figure 10.

| Name (time) | Big O notation     |        |  |

|-------------|--------------------|--------|--|

| Constant    | O(1)               |        |  |

| Logarithmic | O(log n)           |        |  |

| Linear      | O(n)               |        |  |

| Log-linear  | O(n log n)         | Slower |  |

| Quadratic   | O(n <sup>2</sup> ) |        |  |

| Polynomial  | O(n <sup>k</sup> ) |        |  |

| Exponential | O(k <sup>n</sup> ) |        |  |

| Factorial   | O(n!)              |        |  |

Table 3. Most common time complexities.

As explained in [187], by the sum rule for the big O notation, the sum of different procedures with their own complexities can be reduced to the worst case complexity of all the considered procedures. This is because at some threshold point in the growth of the number of elements (n), the worst complexity will dominate over the others, thus they can be neglected when scaling up.

Figure 10. Time complexity convenience. 12

The choice between which data structures to use for representing different kinds of information is highly correlated with the speed and efficiency of the preferred algorithms. It is also important to take into account the number of elements (n) to be processed, since the scalability of a particular data structure might affect the optimality of an algorithm, even to the point of making it unfeasible. For our purposes, just as an example, we can take a look at the data structures proposed in [188] for netlist handling. Common representations of graphs include adjacency matrices or adjacency lists. The first ones consist in matrices with each row and column representing a vertex. Edges connect between them with their corresponding weight. The latter ones consist on a master list with all the vertices of the graph pointing to all the rest of the vertices to which they are connected to. Unlike adjacency lists, adjacency matrices are not good for sparse graphs, when most of the cells of the matrix are empty (i.e. vertices not connected). Problems usually do not require such high degree of connectivity  $(O(|V|^2)$  space).

Most programming languages have already built-in types (data structures) and procedures designed to optimize distinct operations; e.g. for appending elements on a list, getting and setting items, sorting, etc. They customarily allow to define proprietary data structures and procedures for specific purposes, or to import them from already existing libraries whenever convenient.

-

<sup>&</sup>lt;sup>12</sup> Image source: bigocheatsheet.com.

Partitioning, Placement, Floorplanning, Pin assignment and Routing are all different separated NP-complete problems [178, 189-191]. NP-complete problems are those that are both NP and NP-hard. The latter ones are those considered to be at least as hard as the hardest problems in NP. In other words, for a problem A to be NP-complete, A has to be in NP, and every problem in NP has to be reducible to A. Figure 11 represents a drawing of the different sets. For an in-depth analysis of these concepts I suggest the reading of [192, 193].

Figure 11. Euler diagram for P, NP, NP-complete and NP-hard set of problems. <sup>13</sup>

In practice, this means that it is not possible to find the unique best solution for any of our particular problems in a fast manner. It is common to search and apply heuristic algorithms to find the optimal or any good-enough solution that meet the requirements (cost functions), while trying to keep reasonable low time complexities.

We can classify algorithms in two ways: either by the results they produce, or by the way they work. When considering the results they obtain we can have the following two types:

- 1) Deterministic: these algorithms will always make the same decisions over any input, and therefore they will always produce the same output results for the same input data.

- 2) Stochastic: these algorithms make random decisions and, as a consequence, it is highly probable to have different output results for the same input data.

\_

<sup>&</sup>lt;sup>13</sup> Image source: Wikipedia.org.

On the other hand, if we want to classify algorithms considering how they work we can mention the following two types:

- 1) Constructive: they start selecting a component; then other components will be picked and added to the partial solution, according to specific criteria, until a complete solution is obtained. Once a component is chosen to be part of one partition it is never moved in future steps of the constructive procedure.

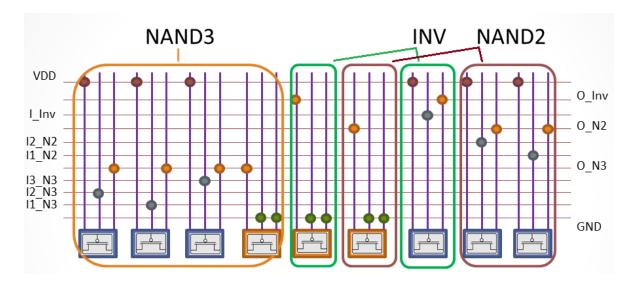

- 2) Iterative: they start receiving the input problem and an initial solution. They will try to improve the solution according to the targeted cost functions, and when no improvements can be done they will stop.