ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

# Improving the performance of an all-Si based thermoelectric micro/nanogenerator

## İnci Dönmez Noyan

Physics Department Universitat Autònoma de Barcelona

A thesis submitted for the degree of

Doctor of Philosophy (PhD) in Materials Science

under the supervision of:

Dr. Luis Antonio Fonseca Chácharo

Dr. Carlos Alberto Calaza Cabanas

Tutor: Dr. Aitor Lopeandía Fernández

PhD Thesis - 2018

## Abstract

This thesis presents the development of a thermoelectric microgenerator ( $\mu TEG$ ) with the aim of powering low power wireless sensor nodes for Internet of Things applications. The proposed  $\mu TEG$  is fabricated by means of silicon micromachining technologies and makes use of silicon (Si) and silicon/germanium (SiGe) nanowire (NW) arrays as thermoelectric material.

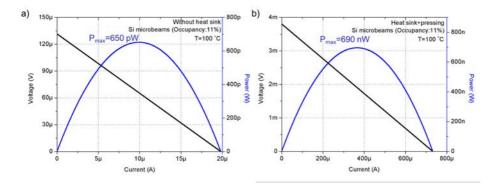

Specific technological routes are designed to increase the power density of the µTEG. Particularly, this thesis has been focused on increasing the power density through i) thermal and electrical optimization of the thermoelectric microplatform, ii) integration of a heat exchanger on the proposed µTEGs. The thermal performance of the µTEG is enhanced by reducing the parasitic thermal losses between the hot and cold ends which ended up in %34 decrease of the thermal conductance. The electrical performance, on the other hand is improved tremendously by lowering the device internal resistance 7 to 20 times. Both has been achieved through the redesign of the architecture and processing steps for µTEG. Even though the power densities obtained from the optimized µTEGs are close to meet the expectations for low power sensor nodes (10-100 μW/cm<sup>2</sup>), further improvement is aimed by the integration of a heat exchanger. Two different routes with different heat flow directions have been designed for the integration of a heat exchanger. With the integration of the heat exchanger, a significant amount of improvement has been observed for all tested µTEGs based on different thermoelectric materials (Si NWs, SiGe NWs and Si microbeams). µTEGs with integrated heat exchanger were able to harvest 41.2 (Si NWs), 45.2 (SiGe NWs) and 34.5 µW/cm<sup>2</sup> (Si microbeams) when they were placed on a waste heat source of 100 °C. This is 50-1000 times more than for similar devices without heat exchanger at the same hot plate temperature.

Results obtained in this thesis are well positioned compared with the state-of-the-art  $\mu TEGs$ . In addition, this thesis, together with the one performed in collaboration at IREC, reports for first time on the performance of SiGe NWs based  $\mu TEG$ .

## Resumen

Esta tesis presenta el desarrollo de un microgenerador termoeléctrico ( $\mu$ TEG) con el objetivo de alimentar nodos sensores inalámbricos de bajo consumo para aplicaciones en la Internet de las Cosas. El  $\mu$ TEG propuesto se ha fabricado mediante tecnologías de micromecanizado de silicio y haciendo uso de formaciones de nanohilos de silicio (Si) y de silicio/germanio (SiGe) como material termoeléctrico.

Se han definido rutas tecnológicas de fabricación adecuadas para aumentar la densidad de potencia del µTEG. En particular, esta tesis se ha centrado en aumentar dicha potencia a partir de i) la optimización térmica y eléctrica de la microplataforma termoeléctrica, y ii) integrando un intercambiador de calor en los µTEGs propuestos. Las prestaciones térmicas del µTEG se han mejorado reduciendo las pérdidas parásitas de calor entre las partes calientes y frías de la microplataforma, lo que ha resultado en una reducción del 34% en la conductancia térmica. Las prestaciones eléctricas, por otro lado, han mejorado aún más importantemente al reducir la resistencia interna del dispositivo entre 7 y 20 veces. Ambos logros se han conseguido mediante el rediseño de la arquitectura y de algunos de los procesos de fabricación del μTEG. Aunque las densidades de potencia obtenidas para los µTEG optimizados se acercan a las necesidades de nodos sensores de bajo consumo (10-100 µW/cm<sup>2</sup>), se ha intentado mejorar su comportamiento mediante la integración de un intercambiador de calor. Para dicha integración se han ensayado dos rutas diferentes, en función de la dirección del flujo de calor en el dispositivo. En cualquier caso, se ha podido observar un incremento significativo de prestaciones para todos los µTEGs considerados (Si NWs, SiGe NWs y Si microbeams). Los µTEGs con intercambiador de calor integrado han sido capaces de colectar densidades de potencia de 41.2 (Si NWs), 45.2 (SiGe NWs) and 34.5 µW/cm<sup>2</sup> (Si microbeams) cuando se han dispuesto sobre placas calientes a  $100\,^{\circ}\mathrm{C}$  de temperatura. Esto supone un incremento de 50-1000 veces con respecto a dispositivos similares sin el intercambiador de calor en esas mismas condiciones.

Los resultados obtenidos en esta tesis están bien posicionados en relación al estado del arte de  $\mu TEGs$ . Además, esta tesis, junto con otra también llevada a cabo en colaboración con el IREC, reportan por primera vez  $\mu TEGs$  basados en nanohilos de SiGe.

## Acknowledgements

I consider it my privilege to acknowledge the help, assistance and support of the many individuals without whom this thesis would not have been possible.

First and foremost, I would like to thank my advisor Dr. Luis Fonseca for his invaluable guidance and being a continuous source of support, patience, knowledge and influence for me. He has routinely gone beyond his duty to struggle against my concerns, visa problems, and have instilled great confidence in both myself and my work. I could not have imagined having a better advisor and mentor for my Ph.D. study.

Also, I would like to thank Dr. Carlos Calaza for co-supervising my thesis and Dr. Andrej Stranz for the fruitful discussions. I have enjoyed the opportunity to learn from their knowledge and experience. I am also indebted to Dr. Aitor Lopeandía Fernández for being the tutor of my thesis and for all his help since the beginning of my Ph.D. studies.

I find it very difficult to express my gratitude for Dr. Marc Salleras, the smartest and most adventurous colleague and friend that one person could ask for. Marc has provided me extensive personal and professional guidance and taught me more than I could ever give him credit for here. Moltes gràcies per tot!

I would not have been able to complete this work as I wanted without my dear companion Marc Dolcet, who has contributed a lot during the last year of this thesis work. We have shared many laughs and memories, and I really enjoyed the conversations we had during the breakfast breaks.

Perla, my dearest friend, thank you for sharing this journey with me. You were always there with a listening ear, supporting me in every aspect of my life. Thanks for the time that we spent both in and out. Roberto, I am profoundly grateful for your friendship and kindness. Sole, thank you for cheering us up even in hard times (and also for 'mate'). I would also like to thank my friends: Kutlu, Ceren, Civan, Cami, Mar, Irene, Onur, Gulçin, Başak, Xavi, Marina, Laura and Federico for making my life in Barcelona much more pleasant.

Thanks to IMB-CNM cleanroom staff for their painstaking efforts in fabricating the microgenerator and effectiveness in alleviating the challenges that I faced during the experimental research. I am especially indebted to Marta Duch and Marta Gerbolés for their valuable assistance and help. I feel so lucky to have a chance to work with them in Microsystems Lab. I would also like to thank Ana Sánchez, Roser Mas, Miguel Zabala, Javier Sanchez, Xavier Borrisé, Sara Duran and Alberto Moreno for their collaborations. I would also like to thank mechanical workshop for their efforts in fabricating various pieces when I needed. Additionally, I would like to acknowledge IMB-CNM administrative staff for their guidance throughout these years.

I have had an opportunity to collaborate with amazing researchers from IREC, Barcelona. I am specially indebted to Dr. Gerard Gadea and Dr. Mercè Pacios for their time, understanding and fun/useful conversations we had. I would also like to acknowledge Dr. Albert Tarancón and Dr. Álex Morata for their enthusiasm and valuable comments.

I would also like to thank Humberto Mata Rodríguez and Loreta Gutiérrez from D+T Microelectrónica, A.I.E for their overwhelming efforts to solve my paperwork problems, I greatly appreciate it.

I am eternally grateful to my parents and my parents-in-law for their unremitting encouragement, support and guidance. I also wish to thank my sisters: Merve, Melike and Aslı for being awesome and to my nieces: Ada and İdil for bringing joy to my life. Finally, I wish to thank my loving, supportive, encouraging, and patient husband Alican who provides me unending inspiration. This dissertation stands as a testament to your unconditional love and support.

# Contents

|   | Abs  | stract  |                                                     | i    |

|---|------|---------|-----------------------------------------------------|------|

|   | Res  | sumen   |                                                     | iii  |

|   | Ack  | knowle  | dgement                                             | v    |

|   | Noi  | mencla  | ature                                               | xiii |

|   | Sco  | pe of t | the Thesis                                          | xv   |

| 1 | Inti | roduct  | ion                                                 | 1    |

|   | 1.1  | Thern   | noelectric effect                                   | 3    |

|   | 1.2  | Thern   | noelectric materials                                | 5    |

|   |      | 1.2.1   | Thermoelectric materials efficiency                 | 5    |

|   |      |         | Literature review on thermoelectric materials       | 8    |

|   |      |         | 1.2.2.1 Si and SiGe nanostructures as ther-         |      |

|   |      |         | moelectric materials                                | 10   |

|   | 1.3  | Thern   | noelectric devices                                  | 14   |

|   |      | 1.3.1   | Thermoelectric devices efficiency                   | 16   |

|   |      | 1.3.2   | Literature review on thermoelectric devices . $\ .$ | 18   |

|   |      |         | 1.3.2.1 Miniaturized thermoelectric devices .       | 19   |

| 2 | Exp  | erime   | ntal methods                                        | 23   |

|   | 2.1  |         | riew                                                | 23   |

|   | 2.2  | Strate  | egy of the μTEG Fabrication                         | 23   |

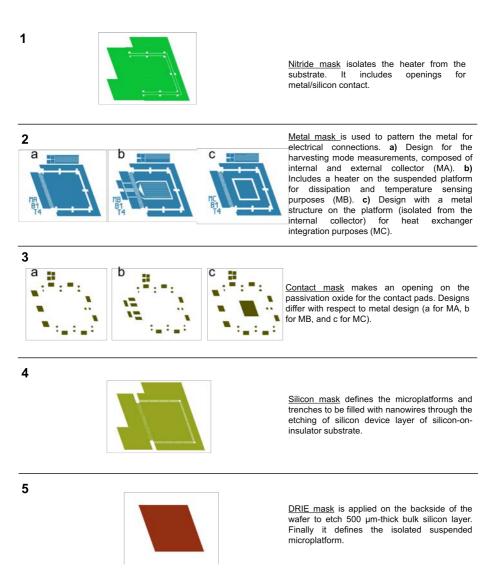

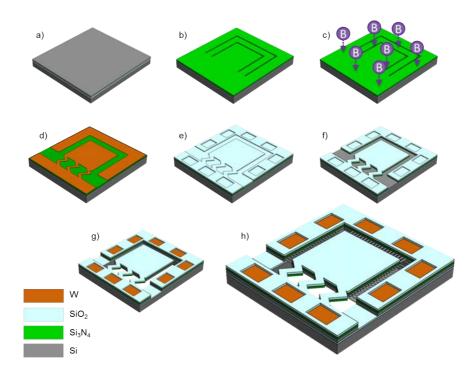

|   |      | 2.2.1   | Silicon technology processing for $\mu TEG$         | 25   |

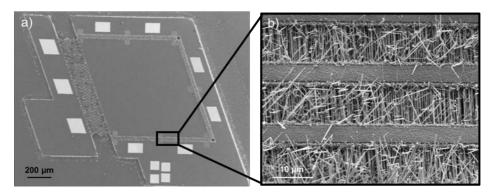

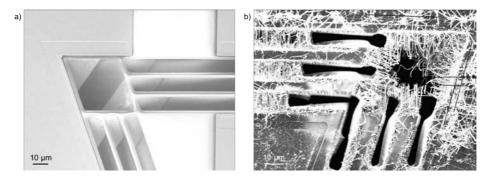

|   |      | 2.2.2   | Si and SiGe NW growth                               | 28   |

|   |      |         | 2.2.2.1 Overview                                    | 28   |

|   |      |         | 2.2.2.2 Galvanic displacement                       | 29   |

#### CONTENTS

|   |     | 2.2.2.3 CVD-VLS growth                                | 31  |

|---|-----|-------------------------------------------------------|-----|

|   | 2.3 | Thermoelectric characterization                       | 33  |

|   |     | 2.3.1 Contact resistance                              | 34  |

|   |     | 2.3.2 Temperature coefficient of resistance           | 36  |

|   |     | 2.3.3 Thermal conductance of the platforms            | 38  |

|   |     | 2.3.4 Seebeck coefficient                             | 39  |

|   |     | 2.3.5 Thermoelectric power                            | 40  |

| 3 |     | optimized all-Si based thermoelectric microgene       |     |

|   | ato | r                                                     | 43  |

|   | 3.1 | Overview                                              | 43  |

|   | 3.2 | Thermoelectric microgenerator design                  | 43  |

|   |     | 3.2.1 Platform thermal response optimization          | 45  |

|   |     | 3.2.2 Platform electrical response optimization       | 49  |

|   |     | 3.2.3 Other design considerations                     | 55  |

|   | 3.3 | Thermoelectric microgenerator fabrication: microplat- |     |

|   |     | form definition and NWs integration                   | 58  |

|   | 3.4 | Thermoelectric microgenerator characterization        | 64  |

|   |     | 3.4.1 Thermal conductance                             | 64  |

|   |     | 3.4.2 Seebeck coefficient                             | 71  |

|   |     | 3.4.3 Thermoelectric power                            | 76  |

|   | 3.5 | Discussion & summary                                  | 83  |

| 4 |     | egration of a heat exchanger on a μTEG                | 89  |

|   | 4.1 | Overview                                              | 89  |

|   | 4.2 | Preliminary studies                                   | 90  |

|   |     | 4.2.1 Forced convection                               | 90  |

|   |     | 4.2.2 Cold-finger approach                            | 95  |

|   | 4.3 | Routes for the integration of a heat exchanger        | 97  |

|   |     | 4.3.1 Top approach                                    | 99  |

|   |     | 4.3.2 Bottom approach                                 | 104 |

|   | 4.4 | Simulations with the assembled heat exchanger $$      | 106 |

|   | 4.5 | Thermoelectric power characterization with the assem- |     |

|   |     | bled heat exchanger                                   | 113 |

|   | 4.6 | Discussion & summary                                  | 119 |

|   | Cor | nclusions                                             | 125 |

|   | Ong | going & Future Work                                   | 129 |

|              |                                                                      | Contents |

|--------------|----------------------------------------------------------------------|----------|

|              | Scientific Contributions                                             | 133      |

|              | Appendix                                                             | 138      |

| $\mathbf{A}$ | Test structures for single NW characterization                       | 139      |

| В            | Studies to increase the fabrication yield  B.1 Cleaving of the wafer |          |

|              | Bibliography                                                         | 151      |

## Nomenclature

#### Abbreviations

μTEG Thermoelectric microgenerator

APCVD Atmospheric-Pressure Chemical Vapor Deposition

CQFP Ceramic Quad Flat Pack

CVD Chemical Vapor Deposition

DRIE Deep Reactive Ion Etching

FEM Finite Element Method

FIB Focused Ion Beam

HCl Hydrochloric acid

HF Hydroflouric acid

IMB-CNM Institute of Microelectronics of Barcelona, CSIC

IoT Internet of Things

IREC Catalonia Institute for Energy Research

KOH Potassium hydroxide

LPCVD Low-Pressure Chemical Vapor Deposition

MACE Metal-assisted Chemical Etching

MEMS Micro-Electro-Mechanical Systems

NW Nanowire

I

PCB Printed Circuit Board PECVD Plasma-Enhanced Chemical Vapor Deposition PMMA Poly(methyl methacrylate) RIE Reactive Ion Etching RTA Rapid Thermal Annealing SEM Scanning Electron Microscope Si Silicon Silicon-Germanium SiGe **SNAP** Superlattice Nanowire Pattern Transfer SOI Silicon-on-Insulator TCR Temperature Coefficient of Resistance TEG Thermoelectric Generator TLM Transmission Line Model VLS Vapor-Liquid-Solid **Symbols** Thomson coefficient β V/KEfficiency %  $\eta$ П Peltier coefficient V $\Omega \text{cm}^2$ Specific contact resistivity  $\rho_c$ Electrical conductivity S/cm $\sigma$ dNanowire diameter nmYoung's modulus (of Si) 130 GPa  $E_s$

A

Electric Current

| Thermal conductors                    | II//I/                                                                                                                                                                                                                                                              |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 nermai conductance                  | W/K                                                                                                                                                                                                                                                                 |

| Thermal conductivity                  | W/mK                                                                                                                                                                                                                                                                |

| Transfer length                       | $\mu m$                                                                                                                                                                                                                                                             |

| Power                                 | W                                                                                                                                                                                                                                                                   |

| Power density                         | $\mu W/cm^2$                                                                                                                                                                                                                                                        |

| Electrical resistance                 | $\Omega$                                                                                                                                                                                                                                                            |

| Contact resistance                    | $\Omega$                                                                                                                                                                                                                                                            |

| Sheet resistance                      | $\Omega/\mathrm{sq}$                                                                                                                                                                                                                                                |

| Seebeck coefficient                   | V/K                                                                                                                                                                                                                                                                 |

| Temperature, Temperature difference   | K                                                                                                                                                                                                                                                                   |

| Voltage, Voltage difference           | V                                                                                                                                                                                                                                                                   |

| Poisson's ratio (of Si)               | 0.28                                                                                                                                                                                                                                                                |

| Width                                 | m                                                                                                                                                                                                                                                                   |

| Figure of merit (device)              |                                                                                                                                                                                                                                                                     |

| Figure of merit (material)            |                                                                                                                                                                                                                                                                     |

| Temperature Coefficient of Resistance | ppm/K                                                                                                                                                                                                                                                               |

|                                       | Transfer length Power Power density Electrical resistance Contact resistance Sheet resistance Seebeck coefficient Temperature, Temperature difference Voltage, Voltage difference Poisson's ratio (of Si) Width Figure of merit (device) Figure of merit (material) |

## Scope of the thesis

This thesis presents a thermoelectric microgenerator ( $\mu$ TEG) fabricated using silicon micromachining technologies that makes use of silicon and silicon/germanium nanowires as thermoelectric material. The aim of the proposed all-Si  $\mu$ TEG is to harvest electricity when placed on a waste heat source by means of Seebeck effect.

Particularly, our efforts have been focused on increasing the power output through i) thermal and electrical optimization of the thermoelectric microplatform, ii) integration of a heat exchanger on the proposed  $\mu TEGs$ . Attained improvements from both the microplatform optimization and heat exchanger integration are presented.

The organization of this thesis is as follows:

Chapter 1 introduces the basics of the thermoelectricity, including thermoelectric effect and efficiency. Literature review on the state-of-the art of thermoelectric materials and devices is presented, paying attention to the Si nanowires based thermoelectric generation.

In **Chapter 2**, experimental methods used for the growth of nanowires and the device characterization techniques are described.

The Si nanowires based  $\mu$ TEG is presented in **Chapter 3**, including optimization of the microplatform design and microfabrication steps as well as the  $\mu$ TEG performance characterization. First results on the  $\mu$ TEG with SiGe nanowires are also discussed.

Chapter 4 focuses on the first proof-of-concept integration of heat exchanger on microplatforms. Different routes are described, their contribution to resulting performance presented both with simulations and experiments.

After discussing the results and further work planned in relation to the topic in **Conclusion** and **Future Work**, two appendixes are added to the thesis. **Appendix A** describes the labor invested in the development of test structures for single nanowire characterization. In **Appendix B**, the efforts to increase the fabricating yield of our  $\mu$ TEG are presented. These studies include the use of mechanical cleaving instead of wafer dicing to eliminate the breaking of a fragile structures on the device as well as the analysis of the stress of the specific layers deposited during the fabrication process.

# Chapter 1

## Introduction

Internet of Things (IoT) has started to spread rapidly in the last few years and is expected to gain further recognition as the Next Industrial Revolution. IoT basically refers to a system where items in the physical world embedded with sensors can communicate with the others via internet connection. According to BI Intelligence, there will be more than 55 billion IoT devices on Earth by 2025 [1]. Several environments will benefit from IoT, including, connected home, healthcare, smart environments, food services, transportation etc. Figure 1.1 summarizes the main application areas of IoT together with some examples.

For successful realization of IoT devices on several applications, they should be smart, autonomous, miniaturized, and they should have low-energy wireless communication capabilities to be able to collect data from all kinds of locations. Currently, most of the IoT devices are being powered by batteries which limit their operational lifetime. Replacing the battery will disturb the operation, increase the cost, and most importantly, it will end up with significant environmental implications. The use of environmental energy harvesting can self-power IoT sensors, it can extend the battery lifetime or even eliminate the need for the batteries. Considering the low-power requirements for wireless sensor nodes of IoT (10-100  $\mu W/cm^2$ ), the efforts are focused on microsystem based energy harvesting [4]. Micro-Electro-Mechanical Systems (MEMS) based energy harvesting has been attracting profound interest in the research and scientific community since its technology allows mass production, miniaturization

| Application |             | Examples                                                                                                                                  |

|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <b>(1)</b>  | Wearables   | Monitor and maintain human health and wellness; disease management, increased fitness, higher productivity                                |

|             | Homes       | Energy management, safety and security, chore automation, usage-<br>based design of appliances                                            |

|             | Vehicles    | Condition based maintenance, safer/smarter transportation, usage-based design, pre-sales analytics                                        |

|             | Cities      | Public spaces and infrastructure in urban settings; adaptive traffic control, smart meters, environmental monitoring, resource management |

| щŢ          | Factories   | Places with repetitive work routines, including hospitals and farms; operating efficiencies, optimizing equipment use and inventory       |

| <b>*</b>    | Healthcare  | Enhanced patient experience, reduced errors, in-home medical devices, improved disease management,                                        |

| Ä           | Retails     | Inventory optimization, smart customer relationship, faster/efficient logistics and supply chains                                         |

| *           | Offices     | Energy management and security in office buildings; improved productivity, mobile employees                                               |

|             | Education   | Smart devices to share the knowledge, self-directed learning, interactive education                                                       |

|             | Agriculture | Sensor based field and resource mapping, remote monitoring, predictive analytics                                                          |

Figure 1.1: Main application areas of Internet of Things together with some application examples. Adapted from [2], [3].

and easy integration with electronics [5]. In addition, the repeatability and high reliability of MEMS batch fabrication processes reduce the unit cost which can clearly contribute positively to their use for IoT devices.

Thermal energy is one of the environmentally available energy sources which can be harvested through thermoelectric generators. Thermoelectric generators can convert heat into electricity with long operational lifetimes and reliability, and they don't include any moving parts. Considering the excessive amount of waste heat that is produced in our daily life, harvesting at least some of this waste heat means a tremendous amount of power that can be used for several applications.

This thesis reports an all-Si based thermoelectric microgenerator ( $\mu$ TEG) fabricated using MEMS technology with the aim of powering low power wireless sensor nodes for IoT applications. Specific technological routes are designed to increase the power density of the  $\mu$ TEG which will be detailed in the following chapters. This chapter intends to explain the basic thermoelectric effects together with a short literature review on thermoelectric materials and devices.

#### 1.1 Thermoelectric effect

Thermoelectric effect refers to a phenomenon in which temperature difference generates electricity or vice versa. There exist three reversible thermoelectric effects: Seebeck effect, Peltier effect and Thomson effect. They are dubbed reversible as opposed to Joule effect, which is irreversible, although not always considered a thermoelectric effect in itself, but a loss mechanism.

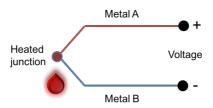

In 1821, Johann Thomas Seebeck discovered that a circuit made out of two dissimilar conductors (standard thermocouple configuration, depicted in Figure 1.2) would deflect a compass needle if their junctions are maintained at different temperatures. Initially, he interpreted his discovery as magnetism caused by temperature difference. Later it was realized what he found out was the new source of electric current. Applying a temperature differences to a material leads to diffusion of charge carriers from the hot side to the cold side. This diffusion creates an electric field which in turn builds up a thermally

Figure 1.2: The schematic of a basic thermocouple.

induced voltage across the material, which is

$$V = S\Delta T \tag{1.1}$$

In the thermocouple configuration, the voltage developed across both materials, V, is proportional to the temperature difference,  $\Delta T$ , and the ratio between them is the differential <u>Seebeck Coefficient</u> of materials A and B  $(S_A - S_B)$ . The sign of the Seebeck coefficient depends on the sign of the majority charge carriers present in the material. Therefore, it is positive for p-type and negative for n-type semiconductors or metals.

The second thermoelectric effect was discovered in 1834 by Jean Peltier using the same experimental setup that was used for the demonstration of Seebeck effect. Instead of establishing a temperature gradient between the junctions, the current was applied through the circuit ending up heating or cooling at the junction. It was found that the rate of heat ejection or absorption (q) was proportional to the applied electric current (I), and the constant of proportionality is defined by a coefficient named Peltier Coefficient,  $\Pi$ .

$$\Pi = \frac{q}{I} \tag{1.2}$$

The last of the thermoelectric effects, Thomson Effect, relates the rate of generation of reversible heat q when a current passes through a single conductor along which there is a temperature difference of  $\Delta T$ . Thomson Coefficient is defined by  $\beta$  in the following formula:

$$q = \beta I \Delta T \tag{1.3}$$

The units of  $\beta$  is the same with the Seebeck coefficient (V/K), and it is usually neglected for thermoelectric devices.

Seebeck, Peltier and Thomson effects are interrelated fundamentally by the The Thomson relations based on the use of classical thermodynamics of equilibrium reversible processes in the form:

$$\Pi = ST \tag{1.4}$$

$$\beta = T \frac{dS}{dT} \tag{1.5}$$

#### 1.2 Thermoelectric materials

Standard thermocouples are composed of two alternating n-type and p-type semiconductor elements. These thermoelements are classified with respect to their efficiencies defined by their material properties. This section aims to explain briefly the relationships between the factors affecting their performances/efficiencies. Next, literature reports on good thermoelectric materials will be shortly reviewed with an emphasis on silicon (Si) and silicon-germanium (SiGe) as thermoelectric materials.

#### 1.2.1 Thermoelectric materials efficiency

The efficiency of a thermoelectric material is defined by its dimensionless figure of merit, zT, which is a function of several parameters:

$$zT = \frac{S^2 \sigma}{k} T \tag{1.6}$$

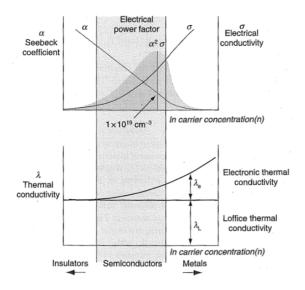

where  $\sigma$  is electrical conductivity, S is Seebeck coefficient and k is thermal conductivity of the material. The term  $S^2\sigma$  is referred as thermoelectric power factor. Thermoelectric figure of merit is defined with respect to mean operating temperature (T). Obviously, a material should have a large Seebeck coefficient and electrical conductivity as well as low thermal conductivity to have a high figure of merit.

Seebeck coefficient is a sum of electrical  $(S_e)$  and phonon-drag  $(S_{ph})$  contributions. The first contribution is a result of different charge carrier contribution rates at different temperature, while the latter arises from lattice vibrations that are carrying the heat. When

a temperature difference is applied across the material, phonons interact with charge carriers and contribute positively to their movements through the cold end.

Similar to Seebeck coefficient, thermal conductivity is also composed of two components. Lattice thermal conductivity,  $k_l$ , is the dominant contribution and is related to ability of phonons to conduct heat. Electrical thermal conductivity,  $k_e$ , on the other hand, arises from the ability of charge carriers to conduct heat.

Another parameter affecting the thermoelectric efficiency is electrical conductivity,  $\sigma$ , which is the measure of a material's ability to allow the transport of an electric charge. Metals have the highest electrical conductivity while semiconductors are occupying an intermediate position in terms of electrical conductivity with carrier concentration values between  $10^{16}$ - $10^{22}$ cm<sup>-3</sup>. Insulators, on the other hand, have very low electrical conductivity which is assumed as zero under normal conditions.

It is also important to note the effect of temperature on the thermoelectric properties. With increased temperature, the phonon-drag contribution of Seebeck coefficient decreases. Increased temperature also decreases the lattice thermal conductivity due to increased phonon-phonon scattering. Phonon-electron scattering also increases with temperature which ends up in low electrical conductivity for highly doped semiconductor. Therefore, an optimum temperature for each thermoelectric material should be defined for the desired thermoelectric applications.

To increase the thermoelectric efficiency, it is necessary to optimize a variety of conflicting properties. As can be seen from Eqn. 1.6, maximum zT can be achieved by manipulating the material properties to have high Seebeck coefficient, high electrical conductivity and low thermal conductivity.

Seebeck coefficient and electrical conductivity relate to the carrier concentration by the following equations:

$$S = \frac{8\pi^2 (k_B)^2}{3eh^2} m^* T \left(\frac{\Pi}{3n}\right)^{\frac{2}{3}}$$

(1.7)

$$1/\rho = \sigma = ne\mu \tag{1.8}$$

where n is the carrier concentration and  $m^*$  is the effective mass of

Figure 1.3: Schematic dependence of Seebeck coefficient, thermal conductivity, electrical conductivity and power factor on free carrier concentration. Taken from [7].

the carrier. Figure 1.3 can be correlated with Eqn. 1.7 to claim that Seebeck coefficient decreases as the carrier concentration increases. On the other hand, low carrier concentration results in low electrical conductivity (Eqn. 1.8) which is not desired in order to have a high figure of merit. Therefore, it is very critical to compromise between large Seebeck coefficient and high electrical conductivity to achieve maximum zT. This maximum usually occurs at carrier concentrations between  $10^{19}$  and  $10^{21}$  carriers per cm<sup>3</sup> [6].

Considering abovementioned parameters, semiconductors are the best candidates as thermoelectric materials. zT is linked to thermoelectric efficiency because it modulates the maximum attainable fraction of the Carnot efficiency for a given temperature difference. More information is given in Section 1.3.1. To refer a material as a good thermoelectric material, its dimensionless figure-of-merit (zT) should be higher than 0.5. [7]

# 1.2.2 Literature review on thermoelectric materials

From the previous section it is clear that the selection of materials for thermoelectric power generation involves the search for materials of high figure of merit (zT). In addition to that, thermoelectric materials should be capable of operating over a wide temperature range as much as possible, they should have reliable mechanical, metallurgical and thermal characteristics that allow their use in practical applications. The following recollection of thermoelectric materials options is neither exhaustive nor enters into an in-depth description of them. It only aims at showing the material families that are currently used and researched as well as the avenues for improving thermoelectric performance or applicability. The interested reader is advised to explore the cited references and the regularly published reviews on thermoelectric materials [8]–[14].

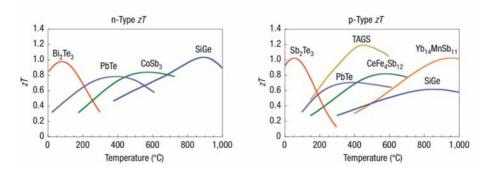

Several thermoelectric materials have been investigated for decades to improve the efficiency of the system using high zT materials. In the 1950s, generator efficiencies had reached 5\% and cooling from ambient to below 0 °C was demonstrated using Bi<sub>2</sub>Te<sub>3</sub> as thermoelectric material. Since then, Bi<sub>2</sub>Te<sub>3</sub> has been the most extensively studied and applied material for thermoelectric applications. Another high zT thermoelectric material is PbTe which is used for space applications as well as SiGe for radioisotope thermoelectric generators [15]. Several materials have been reported with high zT values due to their intrinsically low thermal conductivities such as Cu<sub>2</sub>S, Yb<sub>14</sub>MnSb<sub>11</sub>, Ag<sub>9</sub>TlTe<sub>5</sub>, AgSbTe<sub>2</sub>, BiCuSeO and SnSe. Figure 1.4 displays the state of the art thermoelectric materials with high figures of merit. Thermoelectric materials can be divided into three groups according to the optimal working temperatures; low, medium and high temperatures. Bi<sub>2</sub>Te<sub>3</sub>-based materials are stable up to 550 K so that they are mostly functional for low temperature applications. In the middle temperature range (550 to 900 K), different materials exist such as PbTe, Bi<sub>0.875</sub>Ba, clathrates, skutterudites and TAGS. For the high temperature applications above 900 K, SiGe, Cu<sub>2</sub>Se, Zintl compounds and Half-Heusler alloys are considered to be the most efficient materials. Oxides and silicides are aimed at enabling heat conversion at elevated temperatures. Further to their stability, they

Figure 1.4: Figure of merit (zT) of state-of-the-art commercial materials for thermoelectric power generation. Taken from [6].

are attractive also on view of their low cost and nontoxicity [14], [16], [17]. Silicides are also of wider interest because of their prospective compatibility with integrated technology, which would make them suitable candidates for microharvesting.

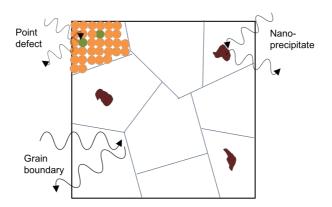

In the mid-90s, zT values higher than 1 were achieved thanks to breakthroughs in two different research approaches: exploring new materials with complex crystalline structures and resourcing to some dimensional engineering of the materials. New materials such as skutterudites and clathrates include loosely bonded atoms which cause phonon scattering with almost negligible impact on the electron transport [18]. For the latter approach, Dresselhaus and coworkers found that dimensional restriction can lead to a much enhanced efficiency over bulk thermoelectrics [19], [20]. They proposed that the use of nanostructures allows tuning the zT through new methods such as quantum confinement, modulation doping, and the enhanced influence of interfaces and surfaces. Once more, a successful strategy to increase zT has been introducing additional scattering mechanisms for phonons. Hierarchical structures have been designed including all-length scale structures to scatter broad spectrum of heat carrying phonons, as depicted in Figure 1.5. On the other hand, the predicted positive effect of the extreme dimensions reduction on Seebeck coefficient by quantum confinement of carriers has not been proved unambiguously in any material system experimentally.

Recently, organic and hybrid materials have been reported to exhibit figure of merits that are approaching to those of inorganic materials. Their optimization into devices have been studied especially

Figure 1.5: Some of the different phonon scattering mechanisms. Adapted from [25].

for low temperature wearable microgenerators [21]. Organometallic polymers have demonstrated the highest organic thermoelectric generator performance so far, with an attained power output of about 1  $\mu W/cm^2$  under a 30 K temperature difference [22]. However, these polymers require traditional cross-plane geometries and they are poorly processable. Organic and hybrid materials that are easily processable in large amounts such as carbon nanotubes (CNTs) loaded organic matrices [23] and PEDOT-based polymers [24] are being investigated intensely and are expected to perform better in the near future.

# 1.2.2.1 Si and SiGe nanostructures as thermoelectric materials

Lately, interest in thermoelectrics has gained momentum thanks to the advances in tailoring material properties by nanostructuring. As a matter of course, different materials have been studied, especially the ones which are not promising in their bulk form. In particular, silicon (Si) has been studied since it is cheap, abundant, non-toxic and extremely technologically enabling material. In its bulk form, Si has a high power factor  $(S^2\sigma)$  but also very high thermal conductivity (148 W/mK), which makes it a bad thermoelectric material with very low zT values (below 0.01). Therefore, efforts have been focused on lowering its thermal conductivity by introducing scattering mechanisms for phonons. This could be achieved by introducing second

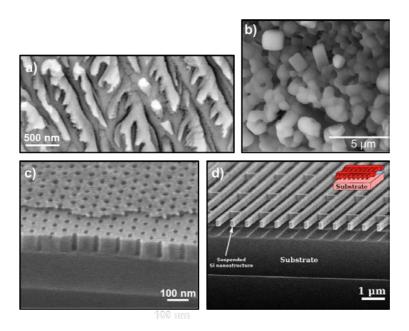

Figure 1.6: Different Si nanostructures fabricated to enhance their thermoelectric properties: nanoporous Si (a) [30], Si quantum dots (b) [35], holey Si (c) [33], suspended Si nanostructures (d) [34].

phase precipitates into Si, which has been reviewed lately by Narducci et al. [26] or nanostructuring. Several Si nanostructure geometries have been investigated in order to increase the zT by lowering its thermal conductivity. Thin layers of Si have been demonstrated as an efficient thermoelectric material [27], [28]. Very low thermal conductivities have been achieved using porous Si structures (0.1 W/mK at RT) [29], however, these structures exhibit very poor electrical conductivities which resulted in zT values similar to those of bulk Si [29], [30]. To control the thermal conductivity of a material independently from its electrical conductivity, Yu et al. [31] reported Si nanomesh structures that are periodically structured. Similar structures (called as holey Si by the authors) were demonstrated in Refs [32], [33] in which arrays of periodic holes were fabricated by block copolymer lithography. Pennelli et al. [34] proposed a thermoelectric generator using top-down fabricated Si nanostructures as thermoelectric materials. Some of the Si nanostructures fabricated for thermoelectric characterization/application purposes can be seen from Figure 1.6.

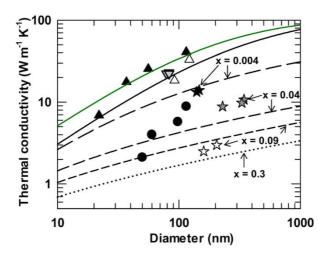

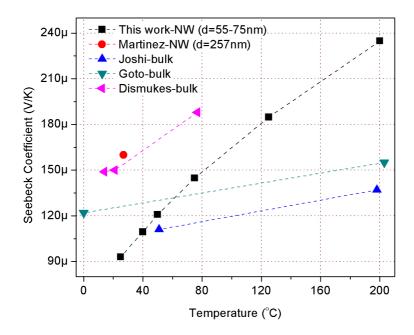

Papers by Boukai et al. [36] and Hochbaum et al. [37] have been the pioneers of the field by claiming that rough Si nanowires (NWs) can have zT of 0.6 at room temperature and 1 at lower temperatures. They independently argued that the reason of this high figure of merit is phonon scattering from the rough Si NW surfaces which caused almost 100 times decrease in the thermal conductivity of the NWs. Figure 1.7 demonstrates the length scale where the decrease of the thermal conductivity is taking place, in the vicinity of a 100 nm or below (already evident for thicker SiGe NW). Since then, even though the same zT values could not be achieved, a variety of studies have been reported addressing the enhancement of thermoelectric performance using Si NWs. Studies reporting the top-down fabrication of Si NW arrays are generally aiming at a vertical architecture for NWs arrangement using different techniques such as lithography which is followed by reactive ion etching [38]–[44], electroless etching [37] and metal-assisted chemical etching (MACE) [45]–[48]. For the application of vertical Si NW arrays into microgenerators, the mostly encountered adversity is to achieve a good thermal and electrical contact for the top side of the NWs. To overcome this problem and to provide mechanical stability to NW arrays, filler materials such as silicon dioxide (SiO<sub>2</sub>) and polyimide have been used to fill the gap between the NWs [40], [49]–[51]. Top-down techniques have also been demonstrated to fabricate NWs with planar geometries using e-beam lithography [52]–[57] and controlled etching and filling of recessed regions (CEFRR) [58]–[61] techniques. Bottom-up approaches are based on the growth of NWs by means of chemical vapor deposition (CVD). The mostly used CVD growth method for Si and SiGe NWS is vapor-liquid-solid (VLS), which enables the massive integration and low-cost production of NWs with respect to top down approaches. However, bottom-up approaches usually require complex procedures for the positioning of NWs inside the thermoelectric device. This problem is overcome by the monolithic integration of VLS-grown Si NWs into thermoelectric microgenerators which was first proposed by Davila et al. [62]. This thesis intends to further improve the power output obtained by such approach by optimizing the microgenerator design, and to show the first attempt to integrate SiGe NWs into the optimized microgenerator.

Figure 1.7: Thermal conductivity as a function of diameter for Si and  $Si_{1-x}Ge_x$  nanowires. Except for those labeled in the figure, the data are for Si nanowires. The symbols are for VLS Si nanowires (black triangles), RIE patterned Si nanowires (gray down triangles), electroless etched Si nanowires (black circles), Si nanowires (unfilled triangles) and  $Si_{1-x}Ge_x$  nanowires. Green and black lines are the calculations for Si and SiGe NWs, respectively. Taken from [63].

Regarding SiGe, it is already reported as a highly efficient thermoelectric material in its bulk form and has been used first in a number of space applications such as multihundred watt generators used on the LES 8/9 and the Voyager spacecrafts [64]. The high efficiency of SiGe arises from its reduced thermal conductivity due to the alloy-induced scattering of phonons. The use of SiGe low-dimensional structures aims to further decrease the thermal conductivity by enhanced phonon boundary scattering effect and integrate them into microdevices. Similar structures such as nanowires, nanomeshes, nanotubes have been demonstrated to have lower thermal conductivities [65], [66]. Si/SiGe superlattice structures have also been theoretically proposed and fabricated [67].

#### 1.3 Thermoelectric devices

A typical thermoelectric device consists of a given number of materials junctions, each one formed from two different semiconductor materials, one containing hole-charge carriers (p-type) and the other electron-charge carriers (n-type). These semiconductor materials are referred as the two legs of a thermocouple, and these thermocouples are connected electrically in series and thermally in parallel.

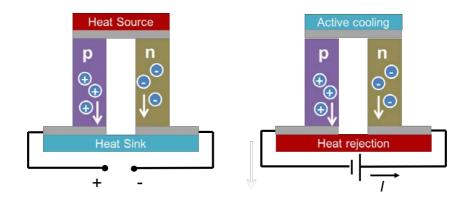

Thermoelectric devices can be categorized as thermoelectric coolers and thermoelectric generators. Basic thermocouples for both applications are illustrated in Figure 1.8. When a DC voltage is applied to the module terminals (current flowing from positive terminal to the negative terminal), electrons in the n-type element are attracted by positive pole of the supply voltage while holes in the p-type element are attracted by negative potential of the supply voltage and move in an opposite direction to the electron flow. The movement of charge carriers convey the heat away from the junction which results in cooling of the junction. This is called thermoelectric cooling (or heating, depends on the current direction), and it is mainly influenced by Peltier Effect. Currently, thermoelectric cooling devices are widely used in a variety of applications as refrigerators and air conditioners. They also serve for cooling the heat-producing device to keep it in normal operation, reducing the thermal noise and leakage current of electronic components.

Figure 1.8: Thermocouple composed of an n-type (negative thermopower and electron carriers) and a p-type (positive thermopower and hole carriers) semiconductor material connected through metallic electrical contact pads. Thermoelectric generation (left) and cooling (right) modes are displayed.

A thermoelectric device can also be used to generate power if a temperature difference is applied between the two ends of a thermocouple. This process is called *thermoelectric generation*, and is the main focus of this thesis. Heat source at the junction causes carriers to flow away from the junction and built up a voltage to the module terminals due to Seebeck Effect.

The advantages of thermoelectric devices are compactness, quietness and robustness (no moving parts), and being applicable for any size of heating/cooling source. Moreover, energy in the form of waste heat (0% efficiency) that would normally be lost may be converted into useful electrical energy (7–8% efficiency) using a thermoelectric power generator [68].

Thermodynamics of heat engines leads to lots of energy being wasted in form of low-grade heat. About two-thirds of energy is lost as waste heat in different scenarios of energy usage or conversion. Thermoelectricity offers a way to recover part of that waste heat back into the system in form of electricity. This is a way of greening industrial processes, or even energy conversion plants, saving extra consumption of fossil fuels and reducing the corresponding emissions. Thermoelectric generators devoted to energy recovery can be of medium size, large size and even gigantic size. Efficiency in

those applications, ranging from automotive to waste heat recovery from industrial plants, is important, but also other considerations related to the bill of materials (affordability, availability, environmentally friendliness) matter a lot: in the end a competitive €/W value is needed to give such technology a chance. A different application, harvesting, aims at getting convenience electricity from a heat source in order to be able to power an electric device in a situation where there is no access to the grid, e.g. charging a mobile from a campfire. In these cases, the size of the thermoelectric generator will depend on the device power requirements. A particular harvesting scenario, which is the one this thesis focuses in, is converting heat into electricity at the (sub)milliwatt scale to provide full power autonomy to sensing nodes deployed within wireless sensor networks. In order to deploy such sensors unobtrusively in IoT scenarios the nodes should be of small size, which also points to a small size for the microharvesters. This prospective situation of billions of small devices also has materials and technological constraints to sort out.

The efficiency of a thermoelectric device will be briefly explained in this section. Next, the recent works on the thermoelectric microgenerators will be emphasized.

### 1.3.1 Thermoelectric devices efficiency

The efficiency of a thermoelectric device not only depends on the materials figure of merit but also on the thermoelectric device itself. As previously commented, a thermoelectric device generally includes two alternating thermoelements which are connected thermally in parallel and electrically in series. The efficiency of a thermoelectric device  $(\eta)$  is defined as heat-to-electricity conversion and expressed by the formula:

$$\eta = \frac{P_{el}}{Q_{in}} \tag{1.9}$$

where  $P_{el}$  is the electrical output power dissipated at external load  $(R_{load})$ , and  $Q_{in}$  is the heat absorbed by the device.  $Q_{in}$  has contributions from the thermal conductance of the device (Eqn. 1.10), Peltier cooling (Eqn. 1.11) and Joule heating (Eqn. 1.12) as described above:

(Thomson contribution is neglected)

$$Q_1 = K(T_h - T_c) = kA \frac{\Delta T}{L} \tag{1.10}$$

$$Q_2 = \Pi I = ST_h I \tag{1.11}$$

$$Q_3 = -\frac{1}{2}R_{int}I^2 (1.12)$$

where k is the thermal conductivity, K is the thermal conductance of the device,  $R_{int}$  is the device internal resistance, and S and  $\Pi$  are the Seebeck and Peltier coefficients, respectively. Considering that the maximum power output is achieved when the  $R_{load} = R_{int}$ :

$$P_{el} = \frac{V^2}{4R_{int}} = \frac{S^2 \Delta T^2}{4R_{int}} \tag{1.13}$$

Therefore, efficiency of a thermoelectric device can be rewritten as:

$$n = \frac{\frac{S^2 \Delta T^2}{4R_{int}}}{kA \frac{\Delta T}{L} + ST_h I - \frac{1}{2}R_{int}I^2}$$

(1.14)

After some math,

$$n = \frac{T_h - T_c}{T_h} \frac{\sqrt{1 + ZT_m} - 1}{\sqrt{1 + ZT_m} + \frac{T_c}{T_h}}$$

(1.15)

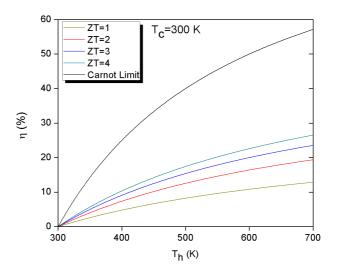

where  $T_m = (T_c + T_h)/2$ . The efficiency of a thermoelectric device is determined by ZT, which is different from the materials figure of merit, zT, with a capital Z. ZT includes the loss mechanisms in the device such as thermal and electrical contact resistances of the interconnects. To minimize the loss mechanisms through the whole device assembly, metallization should be perfectly electrically conducting and should be stable at high temperatures. In addition, the geometry of the thermoelectric legs should be carefully designed to optimize the total thermal conductance of the device. Thermal resistance between the boundaries of the components is also critical to minimize the losses. Figure 1.9 demonstrates the power generation

Figure 1.9: Power generation efficiency with respect to temperature of the hot side plotted for Carnot limit and different ZT values. Cold side temperature is taken as 300 K.

efficiencies with respect to hot side temperature for different ZT values calculated by Eqn. 1.15. Even though high ZT values larger than 1 are included in the graph (which would require even larger zT to account for device losses), the achieved efficiencies are far from the Carnot efficiency, which is  $(T_h - T_c)/T_h$ . It is worth noting that the device approach of this thesis will concurrently improve both zT (by thermoelectric material nanostructuring) and ZT (by reducing internal thermal and electric contact resistances due to monolithic integration).

## 1.3.2 Literature review on thermoelectric devices

Thermoelectric generators have been applied over a wide range of power outputs from microwatt conversion of body heat to power a wristwatch [69] up to hundreds of watts conversion of heat from a nuclear reactor for space applications [15]. Low power applications from the miniaturized thermoelectric generators will be summarized in the next section. Regarding the high power generation, thermoelectric

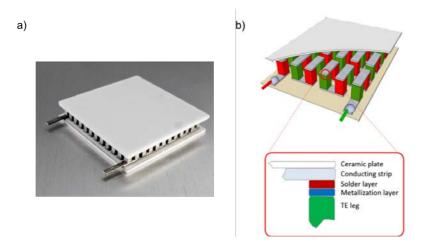

Figure 1.10: a) Typical bulk thermoelectric module from Kryotherm. b) The configuration of a thermoelectric module and the stacking layers between thermoelectric leg and the conducting strip [71].

generators are usually used for waste heat recovery [70]. These bulk TEGs are usually composed of individually mounted thermoelectric legs of 1 mm in size made of  $\rm Bi_2Te_3$  related semiconductor materials. They can generate up to tens of watts at maximum hot plate temperatures around 250 °C. Typical bulk TEG configuration can be seen from Figure 1.10. Since this thesis focuses on low power harvesting, more detailed review is presented on miniaturized thermoelectric generators.

#### 1.3.2.1 Miniaturized thermoelectric devices

With the emerging applications of Internet of Things, small and low power sensors which are provided energy by harvesting have started to become essential. However, there are certain difficulties and limitations in making highly miniaturized thermoelectric modules because of the fragile nature of the mostly used thermoelectric materials. In addition, the number of p/n couples fitting in a limited space available makes it impossible to obtain relatively high output voltage for power generation.

Micro and nanotechnologies are called to play a key role in the fabrication of miniaturized TEGs since they allow mass production with significant reduction in size. Although no longer in production,

Seiko [69] and Citizen [72] developed wristwatches powered by thermoelectrics. Two companies developed commercial thermoelectric microgenerators taking advantage of thin film technologies. Micropelt was the first company to deploy ready-to-use microcoolers and microgenerators in the market. They were using wafer level technology to mass produce thermoelectric microgenerators (µTEGs) with (Bi, Sb)<sub>2</sub>(Te, Se)<sub>3</sub> compound semiconductor thin films, however, they are reported as insolvent as of December 2015. The Nextreme company (bought by Laird technologies in 2013) used Bi<sub>2</sub>Te<sub>3</sub>-Sb<sub>2</sub>Te<sub>3</sub> staggered superlattices for n- and p-type thermoelectric legs. Both of these commercial products exhibited vertical TEG architectures in which thermoelectric legs stand like pillars on the substrate surface, and the same holds for the applied or generated temperature gradient. Therefore, the heat flow is perpendicular to the substrate surface. In the horizontal/planar architecture, thermoelectric legs are oriented parallel to the substrate surface, and the temperature gradient is applied or re-adapted along the substrate surface.

Taking advantage of the microfabrication techniques, new technologies with promising performance levels are in development which allow the use of common, abundant materials in the form of low dimensional structures such as thin films and nanowires. Si has been intensively studied since it is abundant, cheap and it can be easily integrated into current microfabrication technologies. Regarding Si thin films, planar configuration with horizontal gradients has been shown to be more effective since larger  $\Delta Ts$  can be achieved when the heat flow is parallel to the thin film. Perez-Marin et al. [27] reported µTEG based on 100 nm thick single crystalline Si layers, which exhibited power density of 4.5  $\mu W/cm^2$  at an imposed  $\Delta T$  of 5K across the structure. Infineon Technologies and TUM reported power density of 6.21  $\mu W/cm^2$  for  $\Delta T$  of 10 K across the chip using 400 nm thick Si layers as thermoelectric material [28]. In that study, an external  $\Delta T$  is applied by placing the chips between heatable thermochuck and a Peltier cooler.

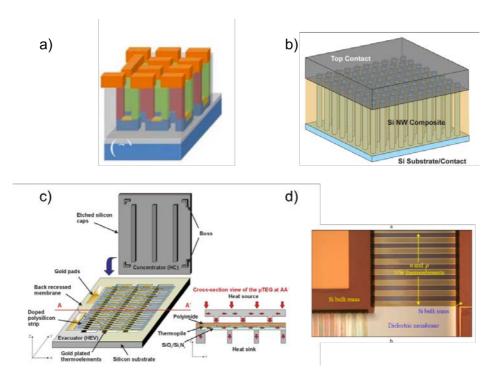

Motivated from high zT values reported by Boukai and Hochbaum et al. [36], [37], several research groups have been working on implementing Si NWs into  $\mu$ TEGs to test its applicability in low power generation devices. Figure 1.11 shows some of the approaches reported for Si NW based  $\mu$ TEGs. Li et al., [39] reports on a vertical

Figure 1.11: Different top down approaches for vertical (a-b) [39], [40] and planar (c-d) [73], [74] Si NWs based μTEGs.

μTEG with 1 μm tall Si NWs arrays, which consists of 540x540 wires in a device area of 5x5 mm². A low power output of 1.4 nW for an estimated  $\Delta T$  of 0.12 K across the Si NWs ( $\Delta T$  of 70 K across the experimental setup) is observed due to high wire and contact resistances. Similar vertical approach has been reported by Curtin et al.[40] with similar Si NW height, however, the gap between the NWs are filled with spin on glass to have a low thermal conductivity Si NW/spin on glass composite. With this approach, they achieved 29.3 μW of power output for a heater-imposed  $\Delta T$  of 56 K from a device area of 50x50 μm. Researchers at Imperial College [46] demonstrated two sided Si NW array/bulk TEG which is capable to produce 3.5 μW at an external temperature difference of 37 K.

Regarding planar architectures, Ziouche et al. [73] recently reported high thermal resistance  $\mu$ TEG that can generate a maximal output power of 12.3  $\mu$ W/cm<sup>2</sup> for an input heat of 2 W/cm<sup>2</sup>. In another study [74], stacked 950  $\mu$ m long top-down polysilicon Si NWs

demonstrated a Seebeck voltage of 500 mV from the preliminary measurements when  $\mu$ TEG is placed on a hot plate at 50 °C. Another recent study is the investigation of Si NW based  $\mu$ TEG on a flexible substrate which is reported by Choi et al. [38]. In this study, strain dependence of the thermoelectric performance is also discussed. Low thermoelectric performance is reported (1.3 nW at an applied  $\Delta$ T=52.1 K) due to high internal electrical resistance.

Aforementioned studies (both vertical and planar architectures) are based on top-down fabrication of the thermoelectric materials. The first implementation of bottom-up Si NWs into planar  $\mu$ TEGs has been reported by Davila et al. [62], [75]. This work follows the same approach, however, optimization of the  $\mu$ TEG performance is studied as well as the heat exchanger integration.

SiGe has been integrated into  $\mu$ TEGs as thin films by Infineon and IMEC [28], [76]. In [28], poly SiGe based  $\mu$ TEG produced 2.73  $\mu$ W/cm² when an external  $\Delta$ T of 8.5 K is applied. Ref. [76] reports on a power output of 0.45  $\mu$ W for an external temperature difference of 29 K. There is only one attempt from Imperial College [77] to demonstrate SiGe NW arrays output power. However, in that study, Si bulk or Si NWs are used as a n-type leg while including SiGe NW arrays as a p-type leg built by MACE process. The attained power outputs (and power densities) were very low (1 nW for  $\Delta$ T of 2-3 K), which was attributed to high internal electrical resistances. This thesis, and another one performed in collaboration at IREC, reports for first time on the performance of SiGe NWs based  $\mu$ TEGs.

# Chapter 2

# Experimental methods

# 2.1 Overview

In this chapter, the route of the fabrication process of the  $\mu$ TEG is briefly described. A detailed description and optimization steps will be explained in Chapter 3. Next, experimental procedure for the integration of Si and SiGe NWs in the predefined trenches of the fabricated  $\mu$ TEG is explained. Finally, experimental techniques and setups used for the characterization of the  $\mu$ TEG are presented. A more detailed fabrication description including the optimization steps considered in this thesis will be explained in Chapter 3. Experimental details on the heat exchanger integration will be presented in Chapter 4 together with the other details/characterizations of the assembled  $\mu$ TEG.

# 2.2 Strategy of the µTEG Fabrication

The idea behind the proposed thermoelectric microgenerator ( $\mu$ TEG), which is merging top-down silicon micromachining technology with bottom-up silicon nanowire (Si NW) growth, was first presented by Davila et al.[62], [75], [78]. One of the main objectives of this thesis is to improve the design of the  $\mu$ TEG to prevent parasitic heat losses and increase the power output.

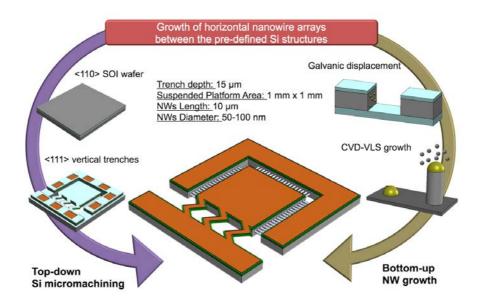

A basic sketch of the fabrication route of a single thermocouple can be seen in Figure 2.1. Top-down micromachining techniques on

Figure 2.1: Schematic of the fabrication route for a single thermocouple with typical dimensions involved.

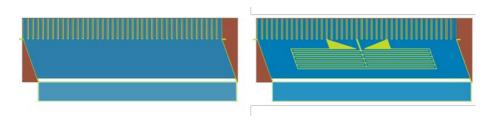

silicon on insulator (SOI) substrates are used to fabricate a microplatform composed of a suspended Si platform surrounded by a bulk Si rim. When placed on a waste heat source, the suspended platform and the bulk Si rim act as a cold side and a hot side of the generator, respectively. After completing the fabrication of the microplatform, p-type Si and SiGe NW arrays have been integrated laterally by a bottom-up Vapor-Liquid-Solid (VLS) method between the isolated suspended platform and the bulk Si rim on top of a SOI substrate.

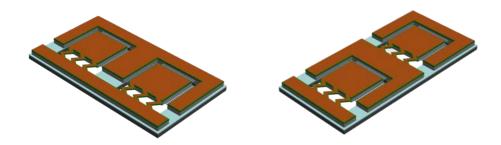

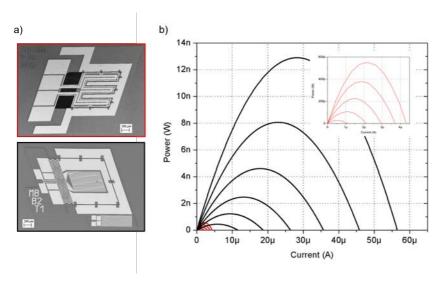

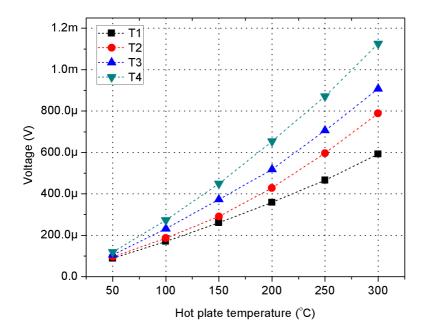

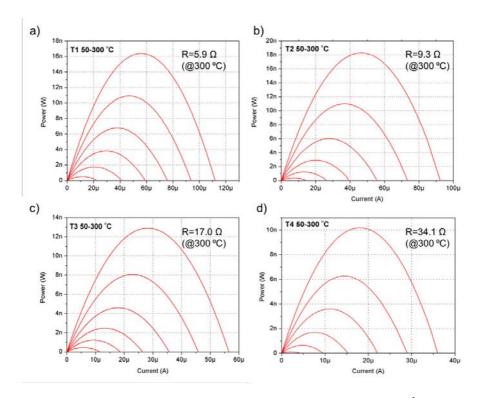

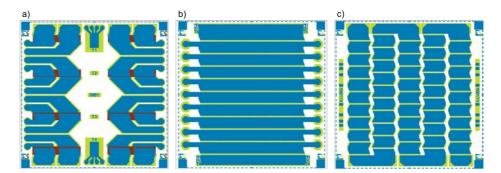

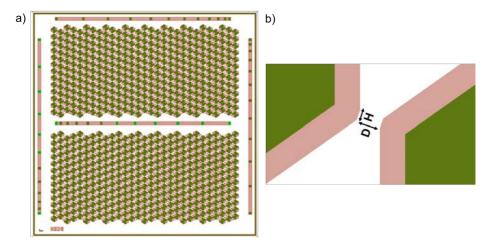

For technological simplicity, our planar µTEG is fabricated employing a uni-leg architecture, in which the thermocouple is formed by a semiconductor thermoelectric material (p-type Si or SiGe NW arrays) and a metal layer. The proposed architecture for the single thermocouple is easily scalable to parallel or serial connections in order to increase the current or voltage, respectively, of the final microgenerator (Figure 2.2).

Figure 2.2: Parallel (left) and series (right) connection of devices to increase the power output.

## 2.2.1 Silicon technology processing for μTEG

The structural core of our planar microthermoelectric device is fabricated using standard microelectronic methods, lithography and thin film processes, combined with micromachining steps. In case the reader is not familiar with such silicon processing steps, they are briefly described in the following paragraphs:

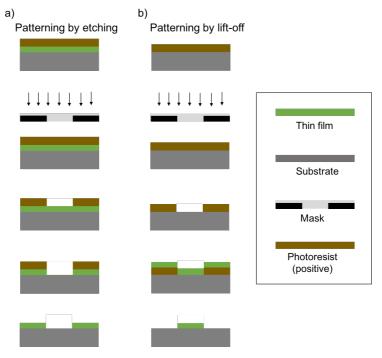

Lithography: By means of this technique a wafer level 2D pattern containing microfeatures is replicated on a photosensitive resist layer spun on a silicon substrate. Such features are reproduced in chrome in a glass or quartz mask that is put above the resist coated wafer in contact or at a close distance to faithfully transfer optically those motives after being shone with UV light. After this exposure, the resist is then chemically developed and those areas that received no light remain in the wafer (in case the photoresist used is of 'positive' nature; the opposite effect is achieved if using a 'negative' resist). In addition to the device features, ancillary alignment motives are also transferred in order to serve as a reference for the alignment of subsequent masks. The reiteration of different mask levels and corresponding patterns configure the device architecture. Figure 2.3 illustrates the lithography and patterning steps.

**Patterning**: The resist pattern on top of a given thin film layer is then used as an etch mask when the wafer is exposed to a wet bath or a dry (plasma based) process that is tailored to remove the layer that is kept unprotected by the resist, and whose etch progresses at an adequate differential rate with respect the etch of the resist

Figure 2.3: Photolithography and pattern definition by means of a) wet/dry etching and b) lift-off. Illustration shows the case with positive photoresist.

mask itself (attending to the different thickness of both layer and resist). The resist remnants after the process are eliminated (ashed) using a O<sub>2</sub> plasma. Usually, the resist is patterned on top of the layer on which the pattern wants to be reproduced. In the particular case of a lift-off (Figure 2.3b), the order is reversed: the resist is deposited and patterned first, and then the layer is placed on top of it. The resist is then chemically removed (using a dissolvent and ultrasounds), a process that lifts from the wafer the portions of the layers attached to the resist. In order to obtain the desired effect, the resist should reflect the negative pattern intended for the layer. Also due to the chemical and mechanical nature of the removal process, a much thicker resist than the layer itself is recommended.

Wet etch: As mentioned above, different wet etchings are tailored for different layers by preparing solutions that contain chemical species that react with the target layer by forming soluble com-

pounds. A wet etch usually progresses isotropically, meaning that the etch evolves laterally as well as in depth.

Dry etch: Alternatively, a given layer can be etched away by means of a plasma process that increases the reactivity of etchant gases that react with the target layer producing volatile compounds. A dry etch usually has a physical directional component (kinetic milling of the layer by impinging of ions). The resulting etch profile is more vertical than when using a wet etchant.

Thin film processes: the layers to be etched need to be laid on the wafers first. This can be achieved through different means. One is making some species, normally in gas phase, to react with the silicon itself (or previous layers) like the oxidation of silicon or polysilicon layers. Such processes usually require high enough temperatures. If the involved species contain all the precursors needed for the layer in mind, this can be obtained in the process atmosphere itself and be chemically deposited in the substrate. The temperature required is usually lower, and although the process can take place at atmospheric pressure (APCVD), it is common to do it at low pressure (LPCVD). If part of the thermal energy needed to activate the reaction of the precursors is provided electrically by means of a plasma enhanced process (PECVD), the deposition can take place at even lower temperatures, making the process compatible with the presence of materials, like metals, with lower temperature stability. Metals themselves are usually deposited by means of sputtering techniques, in which inert ions as Ar are directed by a plasma towards a target of the material (metal) to be deposited. The metal is etched from the target and ends up deposited as a film on the opposing substrate. It is usually a low temperature process.

Micromachining: When instead of vertically patterning a given thin layer, it is removed in a way that a self-standing structure is formed, we are talking about micromachining. If such process takes place by removing laterally a sacrificial layer, the process is called surface micromachining. If the removed layer is partly the silicon itself, usually in a quasi-vertical fashion, the process is called bulk micromachining. This silicon etch can proceed both by wet means or dry processes. In this thesis both are used for defining the microgenerator. For wet etching a KOH anisotropic etchant has been

used. KOH etches silicon but the etch rate depends on local atom densities. That means that more 'dense' planes as (111) are etched much slower than (100) ones, so that the silicon is carved following crystallographic patterns. Resist is not a good mask for such processes, dielectric layers such as oxide and nitride are needed instead. A dry approach, deep reactive ion etching (DRIE), can be used to remove silicon away defining high aspect ratio walls/holes. Usually DRIE uses the so called Bosch process, in which an etch step and a passivation step (local polymer deposition) are subsequently repeated by cycling different specialty gases as many times as needed leaving behind deep vertical scalloped walls. The whole thickness of a silicon wafer can be etched in this way. If this is the case, a thick resist may not be enough as a mask. Alternative materials that are more slowly etched away are needed, such as aluminum or a thick oxide.

A detailed description of the  $\mu$ TEG microfabrication process is given in Chapter 3. Next section describes the experimental details on the bottom-up growth of NWs.

## 2.2.2 Si and SiGe NW growth

#### 2.2.2.1 Overview

The µTEG reported in this thesis requires the horizontal integration of the Si-based NW arrays, which can be achieved by techniques such as electron beam lithography [53], [55], superlattice nanowire pattern transfer (SNAP) [36], conventional KrF lithography [44], [79] and chemical vapor deposition (CVD) [80]–[82]. Although the latter is less accurate, it allows high-level control over NW composition, direction, diameter, crystal structure and doping. Also as a bottom-up method, it does not require top-down patterning after ultra-fine-pitch lithography. Its scalability, easy application, and high growth rates also make CVD the most preferred method for growth of Si-based NWs.

The following subsections describe the NW growth using the optimized conditions of CVD-VLS process. It is important to note that optimization of the growth process has been conducted at IREC and detailed in Ref [83].

#### 2.2.2.2 Galvanic displacement

The VLS mechanism is assisted by a metal catalyst which is deposited by a galvanic displacement method. Gold (Au) is selected as a metal catalyst for the growth of NW arrays for the following reasons [38], [84]:

- Au can be selectively seeded, which is a critical requirement for the proposed microgenerator. NW arrays should only grow on the predefined trenches to be used as thermoelectric material. Growth of NWs is not desired on the rest of the device to prevent unwanted electrical/thermal contributions.

- Since the eutectic temperature of Au-Si alloy is low (363°C), it allows the nanowire growth at moderate temperatures.

- High solubility of Si and Si/Ge in Au-Si eutectic alloy enables a fast growth in comparison to other catalyst materials.

- Au is extremely stable in ambient conditions.

The approach used for the deposition of Au nanoparticles is called galvanic displacement method, which is a type of electroless deposition method that takes place under aqueous, room temperature conditions. The mechanism of galvanic displacement on Si surface is presented in Figure 2.4. It occurs by simultaneous redox processes that result in charge exchange on Si surface.

Those simultaneous redox reactions leading to the deposition of Au nanoparticles on a Si surface are as following:

$$Si(s) + 6 F^{-}(aq) \longrightarrow SiF_6^{2-} + 2 e^{-}$$

$Au^{3+}(aq) + 3 e^{-} \longrightarrow Au(s)$

Where (aq) and (s) represent aqueous and solid phases, respectively. When Si is exposed to a hydrofluoric acid (HF) containing solution, it dissolves as silicon hexafluoride (SiF<sub>6</sub>) and avoids the formation of silicon oxide (SiO<sub>2</sub>) on the surface. At the same time, Au is deposited on the Si surface with a known size and density that is determined by solution properties.

For the deposition of Au nanoparticles in this thesis, Au microemulsions are prepared by mixing an aqueous solution with an

Figure 2.4: Galvanic displacement mechanism on a Si surface [84].

organic phase. The aqueous solution consists of deionized (DI) water with 0.01 M Sodium tetrachloroaurate(III) dihydrate (NaAuCl<sub>4</sub>) and 0.2 M HF. The organic phase, on the other hand, is composed of nheptane with 0.33 M sodium bis(2-ethylhexyl) sulfosuccinate (AOT, a surfactant). The ratio of DI water to surfactant is represented by R, and it directly affects the size distribution and dispersion homogeneity of Au nanoparticles [81], [83]. For the NWs synthesized for this thesis, R is optimized to be 168 which is achieved by mixing the same amount of volumes of both aqueous and organic solutions.

The process starts with immersing the chips in HF (5%) for 5 min to remove the native oxide on the Si trench walls. Chips are then rinsed with DI water, isopropanol (IPA) and dried with compressed nitrogen (N<sub>2</sub>). Next, they are dipped in sonicated microemulsions which are prepared by mixing and aqueous solution with an organic phase with the proportions described in the above paragraph. Dipping time is critical to obtain a homogeneous distribution of nanoparticles especially in deep trenches. Even though a dipping time of 30 s is enough to obtain homogeneously distributed nanoparticles on bare Si substrates, 10 min is required to reach the bottom of the trenches (15 µm deep vertical walls) of the proposed µTEG. Following each dipping, the chips are subsequently immersed in cleaning baths of acetone, DI water and IPA, and dried gently with compressed N<sub>2</sub>. At this point, Au forms a disordered pattern formed by agglomerated crystallites. To obtain well-defined particles, the samples are

then annealed in air at 400°C for 30 min using both heating and cooling ramps of 20°C min<sup>-1</sup>. The galvanic displacement method employed is the same for both Si and SiGe NWs.

#### 2.2.2.3 CVD-VLS growth

The VLS growth is a bottom-up 1D crystal growth mechanism that is assisted by a metal catalyst. It usually occurs at high temperatures, therefore processes such as chemical vapor deposition (CVD), molecular beam epitaxy [85], laser ablation [86] and carbothermal reduction [87] are generally used. In this thesis, the CVD technique is used for VLS growth of NWs.

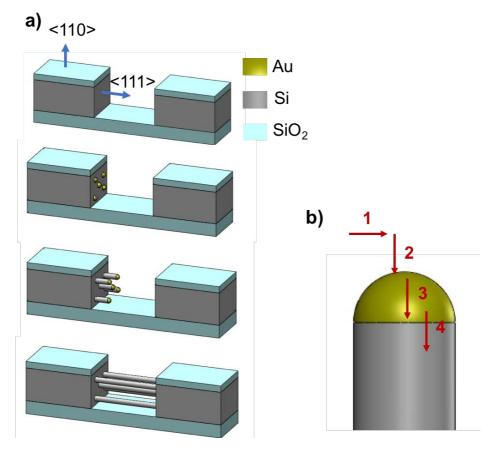

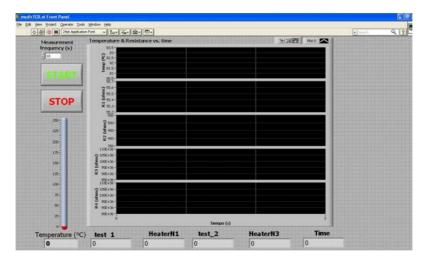

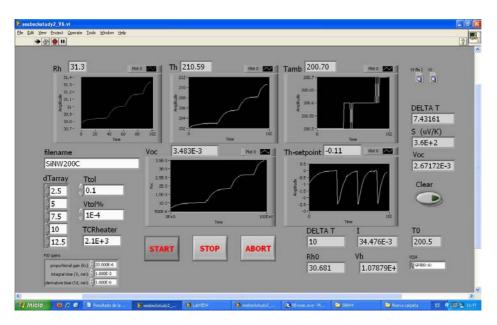

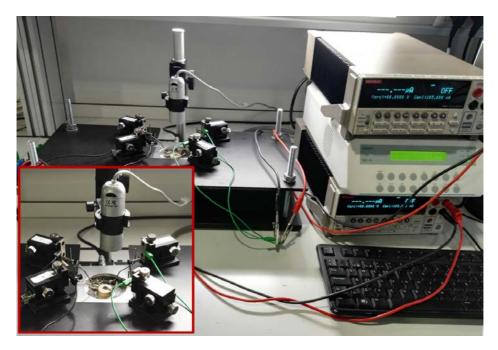

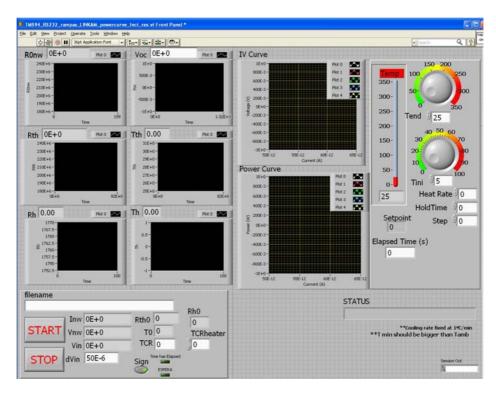

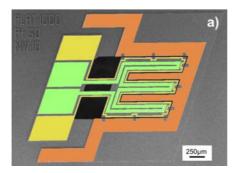

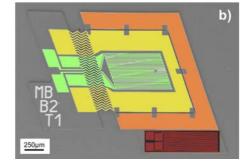

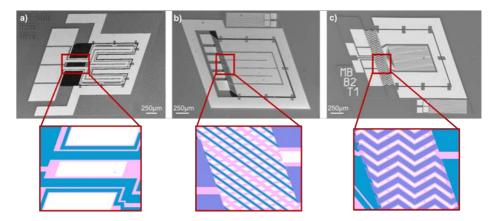

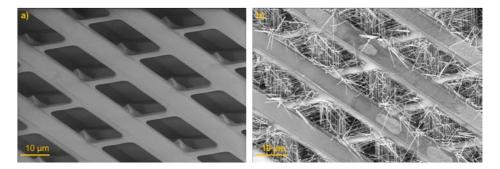

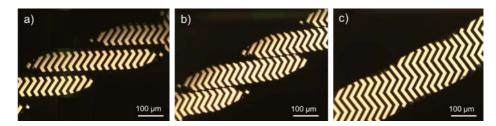

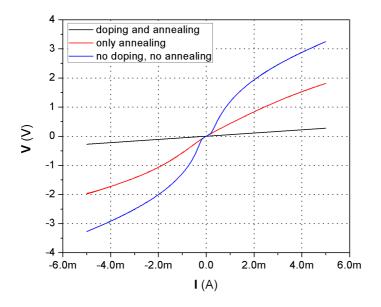

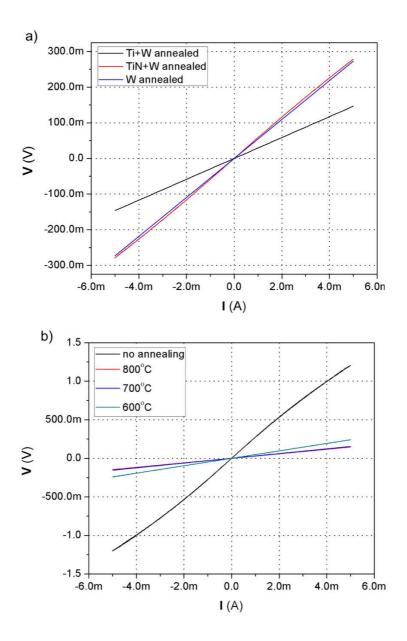

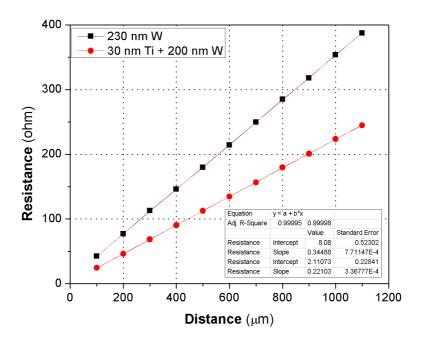

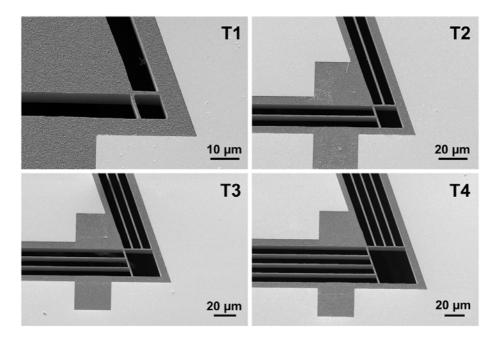

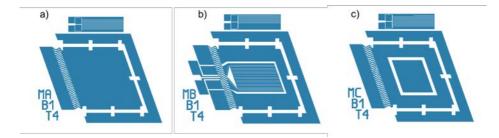

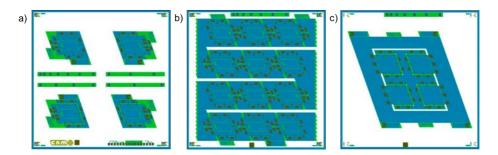

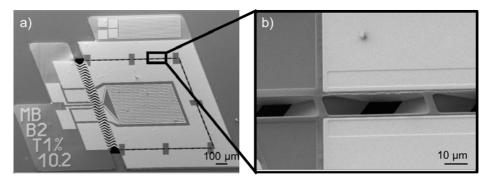

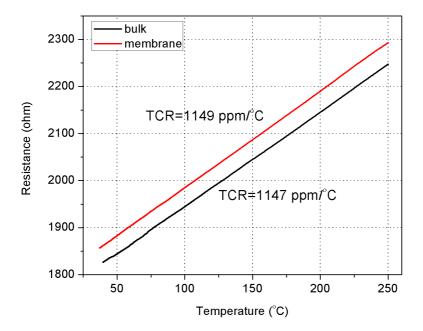

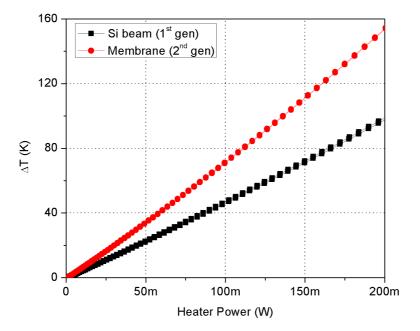

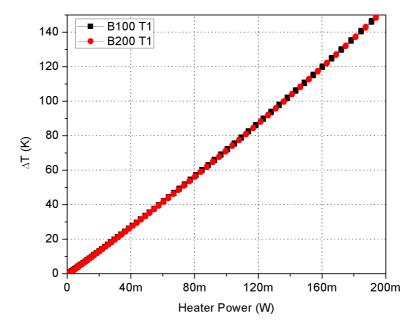

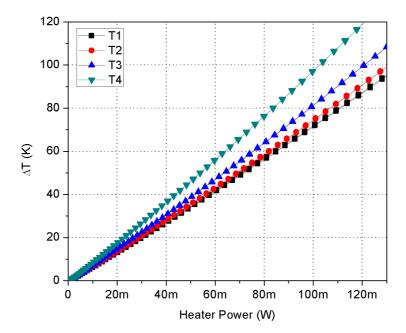

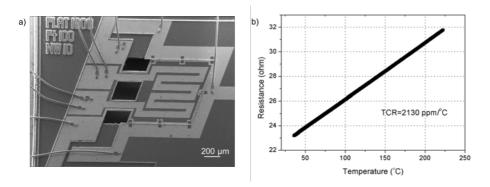

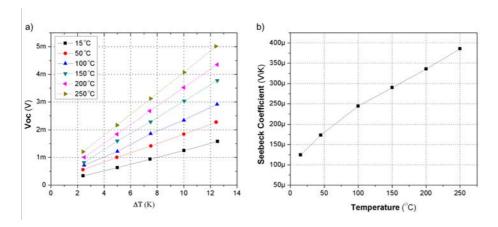

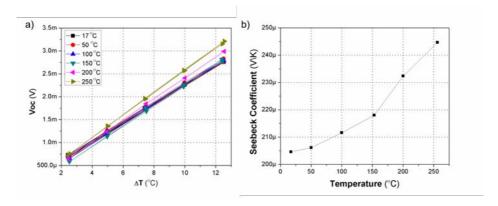

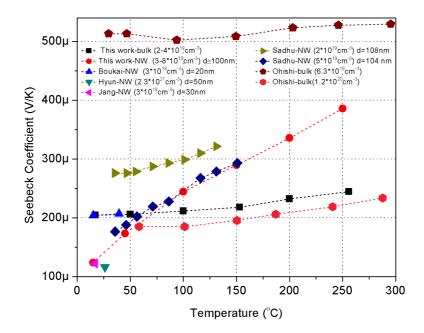

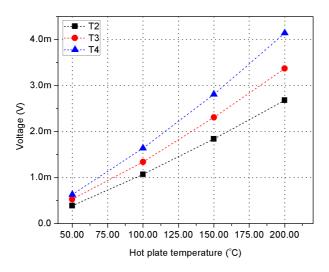

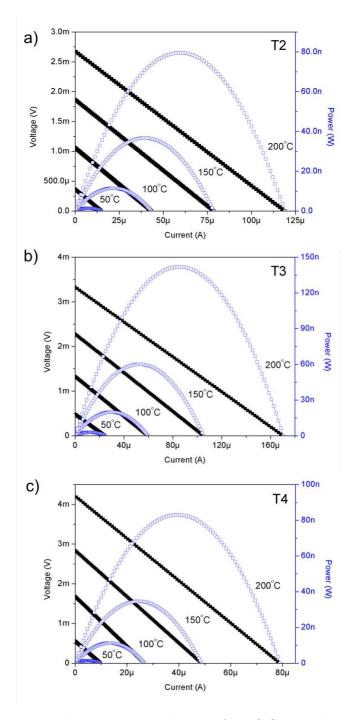

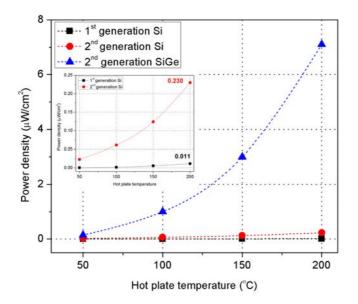

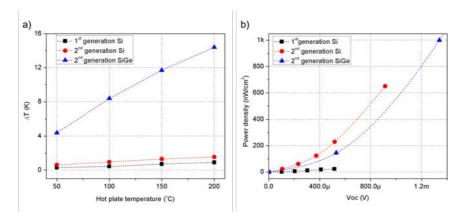

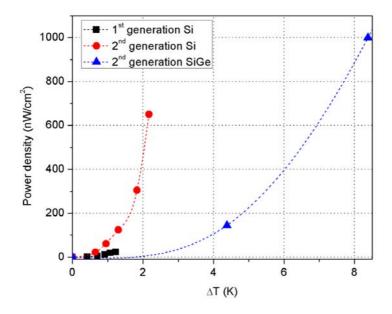

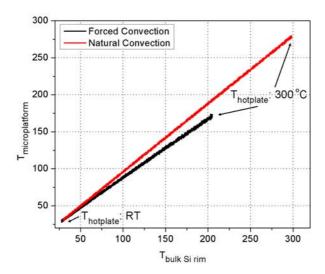

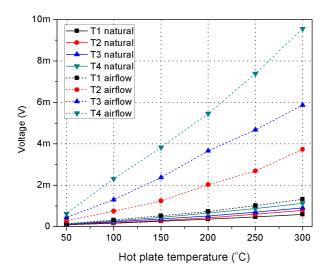

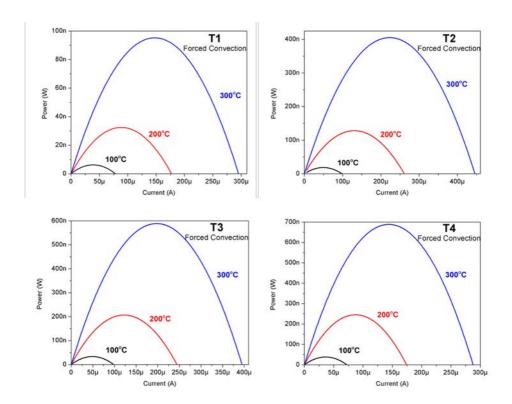

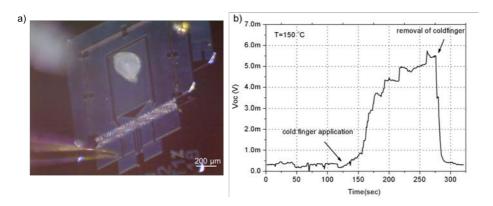

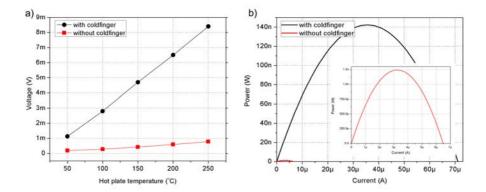

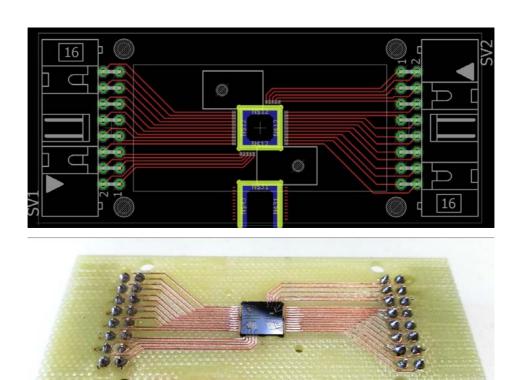

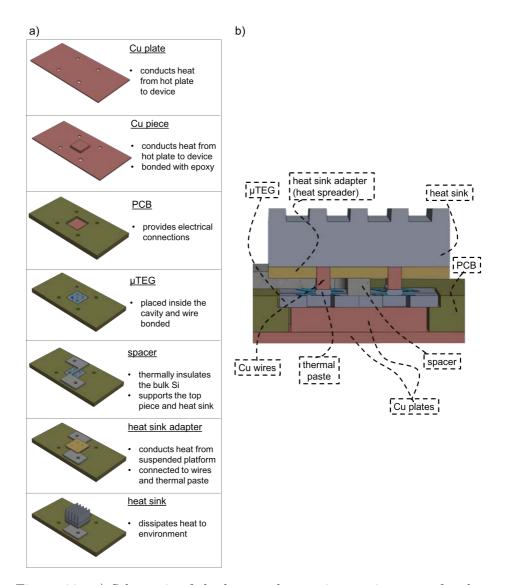

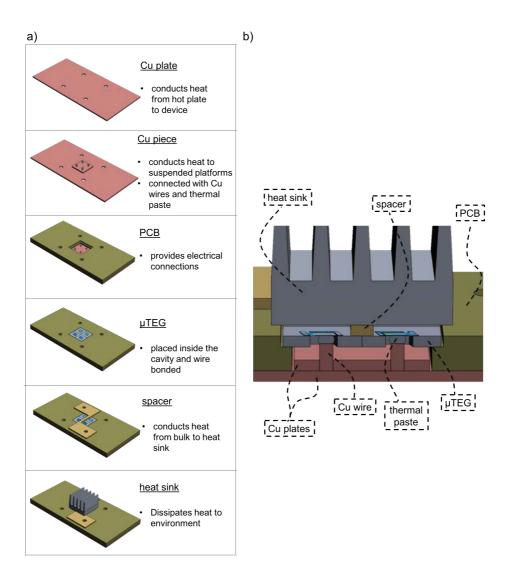

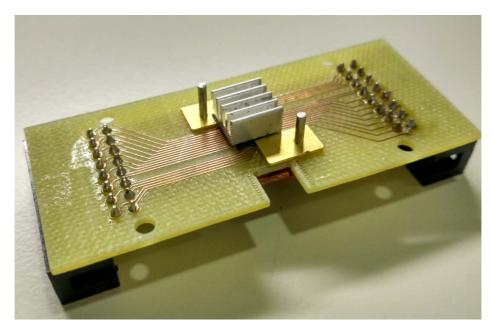

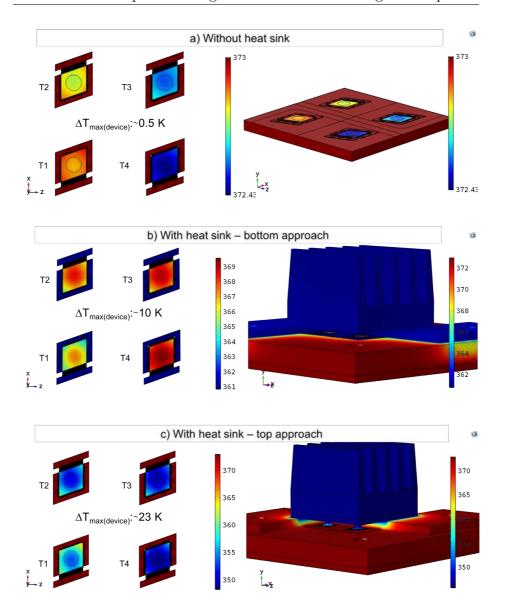

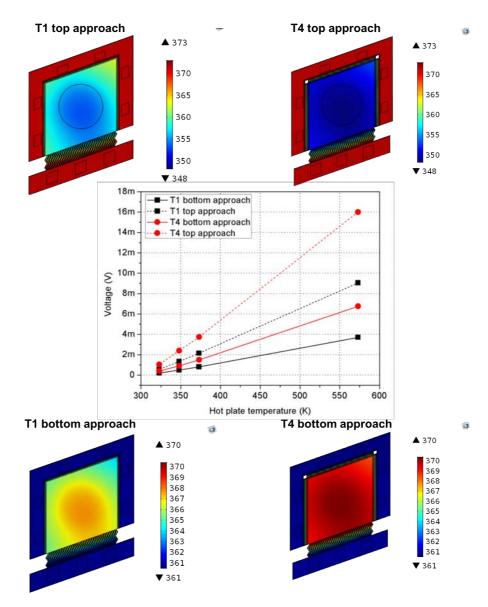

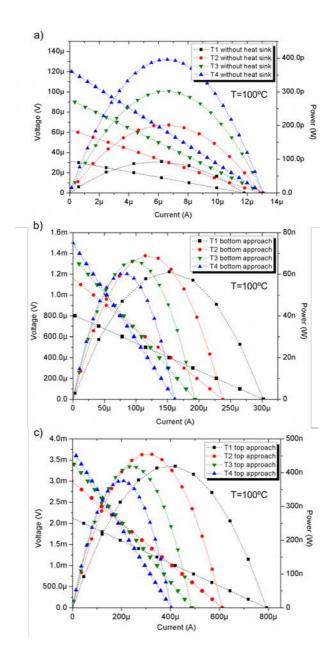

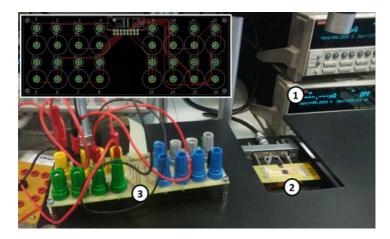

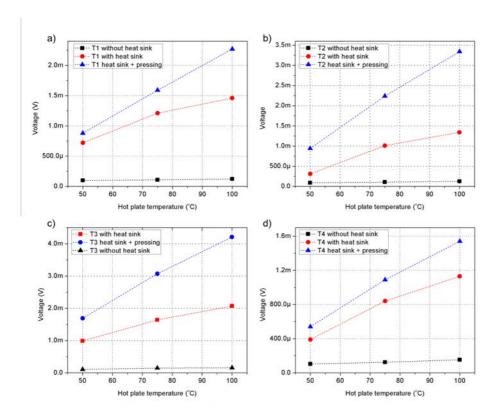

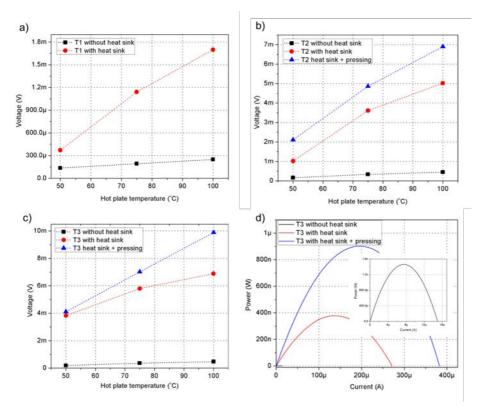

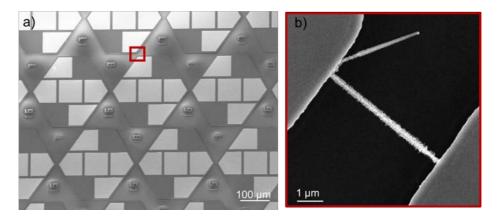

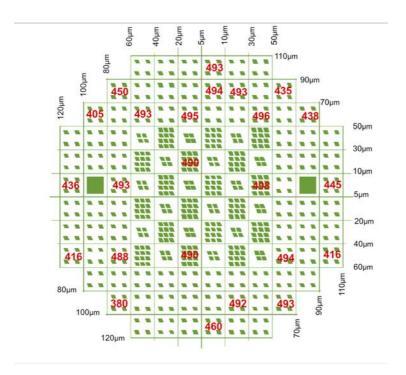

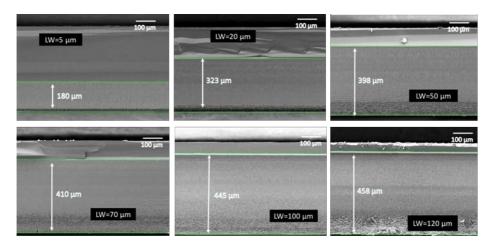

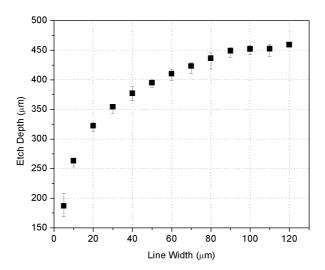

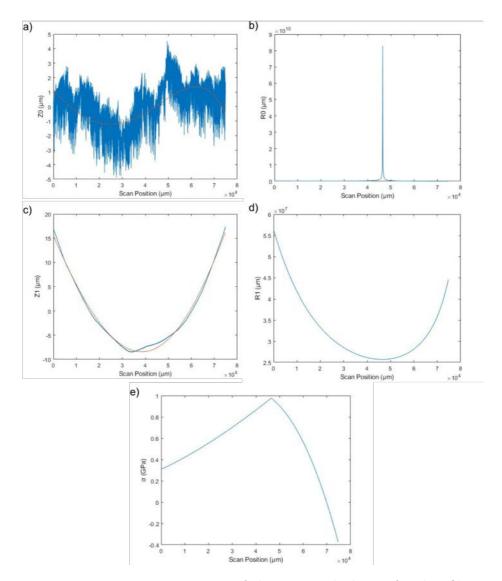

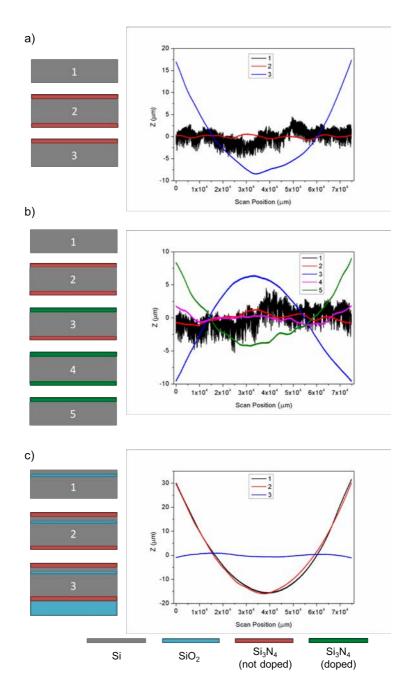

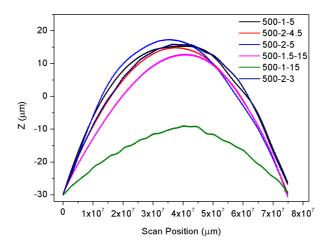

Previous studies show that NWs grow preferentially perpendicular to (111) surfaces [82], [88]. Taking advantage of this, (110) surface oriented SOI wafers (hence with vertical (111) surfaces) are chosen as substrates to grow NWs laterally. Figure 2.5 describes the VLS mechanism for the lateral NW growth between the predefined trenches of the microgenerator with vertical (111) surfaces. The concept of growing NWS as a bridge between the pre-fabricated microdevices has been introduced before [62], [82], [89], [90]. When samples are exposed to a vapor precursor at high temperature, metal catalyst nanoparticles start to adsorb the vapor components of the precursor and form a liquid alloy. With time, the alloy becomes supersaturated and drives the precipitation of the component at the liquid-solid interface to minimize the free energy of the alloy system. This starts crystal NW growth and continues while vapor components are supplied [91]. When NW reaches the opposite trench wall, it welds to the trench wall and continues its growth in the other <111> direction [82]. Since the mechanism involves a vapor phase (precursor), a liquid phase (catalyst alloy), and a solid phase (precipitated NWs) at the same time, it is called VLS mechanism.