**ADVERTIMENT.** L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús estableties per la següent llicència Creative Commons:  [http://cat.creativecommons.org/?page\\_id=184](http://cat.creativecommons.org/?page_id=184)

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons:  <http://es.creativecommons.org/blog/licencias/>

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license:  <https://creativecommons.org/licenses/?lang=en>

Tesis doctoral

---

**Diseño, fabricación y caracterización de

dispositivos de conmutación resistiva

basados en estructuras TiN/Ti/HfO<sub>2</sub>/W**

---

Samuel Poblador Cester

*Perteneciente al*

Programa de Doctorado en Ingeniería Electrónica y de Telecomunicación

*Directoras:*

Dra. Francesca Campabadal Segura

Dra. Mireia Bargalló González

*Tutora Académica:*

Dra. Montserrat Nafría Maqueda

Julio 2021

La Dra. Francesca Campabadal Segura, Profesora de Investigación del Institut de Microelectrònica de Barcelona, IMB-CNM (CSIC) y la Dra. Mireia Bargalló González, investigadora del Institut de Microelectrònica de Barcelona, IMB-CNM (CSIC),

CERTIFICAN:

que la Tesis titulada “Diseño, fabricación y caracterización de dispositivos de conmutación resistiva basados en estructuras TiN/Ti/HfO<sub>2</sub>/W” ha sido realizada por Samuel Poblador Cester en el Institut de Microelectrònica de Barcelona, IMB-CNM, del CSIC, bajo su supervisión y en cumplimiento de los requisitos del Programa de Doctorado en Ingeniería Electrónica y de Telecomunicación.

Y para certificarlo, firman la presente:

Dra. Francesca Campabadal Segura

Dra. Mireia Bargalló González

Dra. Montserrat Nafría Maqueda

Samuel Poblador Cester

Bellaterra (Cerdanyola del Vallès), Julio 2021.

## *Agradecimientos*

Ha sido gracias a la colaboración de muchas personas, ya sea directa o indirectamente, que esta tesis haya visto la luz. A todas ellas mi más sincera gratitud.

En primer lugar, quiero dar las gracias a mis directoras, Francesca y Mireia, por haberme dado la oportunidad de poder realizar el doctorado en este gran centro, curioso a veces, que es el Instituto de Microelectrónica de Barcelona. Gracias a ellas, y a sus consejos, he aprendido mucho durante estos años, tanto a nivel académico como a cualquier otro. Como no, agradecer a mi super compi de grupo Marcos, presente durante prácticamente todo el doctorado, el gran apoyo ofrecido, así como a Maricruz, Rosa, Dani, Mercedes, Martí y Jordi, con los que también he compartido a temporadas grupo.

También me gustaría agradecer a Salva y Helena por el buen recibimiento durante mi estancia en Valladolid, y a Oscar y Guillermo, por el buen trato que me dieron.

Obviamente quiero dar un tremendo agradecimiento a todas las personas de sala blanca, sin las que mis dispositivos solo serían posibles en la imaginación. En especial a toda la gente a la que le he dado la tabarra un poco de más, como a Josep María, con todas mis preguntas sobre el stepper, a Roser, Carles y Samuel, de grabados secos, a Marta y Nuria de grabados húmedos, y a Miguel, al que siempre iban dirigidos mis primeros sondeos. Ya os haya nombrado o no, muchas gracias. De igual manera, estoy muy agradecido a toda la gente que siempre ha hecho posible una estancia agradable en el CNM, ya sea echando un cable en cualquier problema o con un simple saludo o sonrisa en el pasillo.

Por otro lado, quiero agradecer la convivencia a los colegas de despacho que he tenido, Pablo, Sergi, Marcos, Miguel..., a los compañeros con los que empecé aquel lejano 2 de mayo de 2016, Albert, Samuel, Andrea, Ricard, Rosana y Marc y, en general, a todos los amigos y compañeros del CNM con los que he compartido buenos momentos, ya sea desde una barbacoa hasta un lasertag.

Y obviamente, como o no, a mis padres y a mis amigos, que me conocen bien y pase lo que pase siempre están ahí.

Finalmente, recordar que esta tesis doctoral ha sido realizada gracias a la financiación del Ministerio de Ciencia e Innovación a través del contrato pre-doctoral BES-2015-076009, y en el marco de los proyectos RS-FACSIMILE (TEC2014-52152-C3-1-R) y RS-FACSIMILE2 (TEC2017-84321-C4-1-R), en el Instituto de Microelectrónica de Barcelona del Centro Nacional de Microelectrónica del Consejo Superior de Investigaciones Científicas.

## Resumen

En los últimos años se ha suscitado un gran interés por los dispositivos de conmutación resistiva debido al potencial que poseen para revolucionar el mundo de la electrónica. Esta tesis se centra en el diseño, la fabricación y la caracterización de estos dispositivos con una combinación concreta de materiales, TiN/Ti/HfO<sub>2</sub>/W, que permiten una integración total con las actuales tecnologías de fabricación nano y microelectrónica y que presentan un tipo de conmutación resistiva bipolar basada en la creación y disolución parcial de filamentos conductores nanométricos.

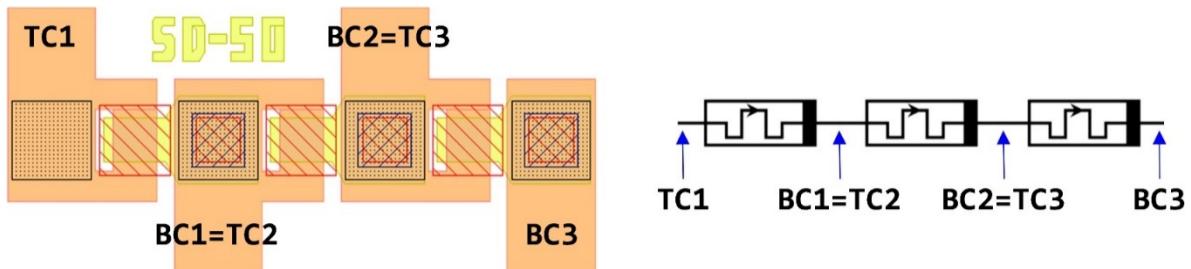

Después de un primer capítulo en el que se introduce el fenómeno de la conmutación resistiva y los mecanismos físicos que la hacen posible, en el segundo capítulo se describe el proceso de fabricación seguido para obtener este tipo de dispositivos mediante dos configuraciones constructivas diferentes, en cruce y aislada. Posteriormente, después de mostrar los dispositivos obtenidos y la caracterización física de estos, se indican los resultados experimentales sobre su comportamiento eléctrico. Durante los dos siguientes capítulos se estudian las características de la conmutación resistiva bipolar que exhiben estos dispositivos individualmente mediante la aplicación de ciclos de barrido de voltaje mediante rampas y de ciclos de trenes de pulsos, ya sea en secuencias bajo parámetros eléctricos constantes (capítulo 3) o modificados automáticamente ciclo a ciclo para evaluar su respuesta multinivel (capítulo 4). Seguidamente, se analiza el comportamiento eléctrico de la asociación en antiserie de dos dispositivos, asociación que da lugar al fenómeno conocido como conmutación resistiva complementaria (capítulo 5). Para completar el estudio de estos dispositivos, en el capítulo 6 se indaga sobre la naturaleza física de su filamento conductor mediante una nueva metodología que permite localizarlo y clasificarlo para averiguar el estado eléctrico de cualquier dispositivo antes de realizar el procedimiento experimental. A continuación, en el capítulo 7 se presenta el diseño de unas nuevas máscaras fotolitográficas para poder realizar la fabricación de nuevos dispositivos, tanto simples como complejos (con dos o más celdas MIM por dispositivo), usando tres tipos de configuración: en cruce, aislada y en cruce aislado, que es una combinación de las dos primeras; además se muestran los resultados de la caracterización física y eléctrica realizada a estos nuevos dispositivos. Finalmente, en el octavo capítulo se recogen las conclusiones más relevantes de los resultados obtenidos en el desarrollo de la tesis.

## Resum

Als darrers anys s'ha generat un gran interès pels dispositius de commutació resistiva degut al potencial que presenten per revolucionar el món de l'electrònica. Aquesta tesi doctoral se centra en el disseny, la fabricació i la caracterització d'aquests dispositius amb una combinació concreta de materials, TiN/Ti/HfO<sub>2</sub>/W, que permeten una integració total amb les actuals tecnologies de fabricació nano i microelectrònica i que presenten un tipus de commutació resistiva bipolar basada en la creació i dissolució parcial de filaments conductors nanomètrics.

Després d'un primer capítol en el que s'introduceix el fenomen de la commutació resistiva i els mecanismes físics que la fan possible, al segon capítol es descriu el procés de fabricació que s'ha fet servir en aquesta tesi per a obtenir aquest tipus de dispositius mitjançant dues configuracions constructives diferents, en creuament i aïllada. Posteriorment, i després de mostrar els dispositius obtinguts i la seva caracterització física, s'indiquen els resultats experimentals sobre el seu comportament elèctric. Als dos capítols següents s'estudien les característiques de la commutació resistiva bipolar d'aquests dispositius individualment mitjançant l'aplicació de cicles d'escombrat de voltatge mitjançant rampes i de cicles de trens de polsos, tant en seqüències amb paràmetres elèctrics constants (capítol 3) o modificats automàticament cicle a cicle per tal d'avaluar la resposta multinivell (capítol 4). Seguidament, es presenta l'anàlisi del comportament elèctric de l'associació en antiserie de dos dispositius, associació que dóna lloc al fenomen conegut com a commutació resistiva complementaria (capítol 5). Per a completar l'estudi d'aquests dispositius, al capítol 6 es proposa una nova metodologia per analitzar la naturalesa física del filament conductor, metodologia que permet localitzar el filament i classificar-lo per tal de conèixer l'estat elèctric del dispositiu abans de realitzar el procediment experimental. A continuació, al capítol 7 es presenta el disseny d'un conjunt de màscares fotolitogràfiques per a poder fabricar nous dispositius, tant simples com complexos (amb dues o més cel·les MIM per dispositiu), fent servir tres tipus de configuració: en creuament, aïllada i en creuament aïllat, que és una combinació de les dues primeres. A més a més, es mostren els resultats de la caracterització física i elèctrica dels dispositius fabricats amb aquest nou conjunt de màscares. Finalment, al vuitè capítol es recullen les conclusions més rellevants dels resultats obtinguts al llarg del desenvolupament de la tesi.

## **Summary**

In recent years, there has been a great interest in resistive switching devices due to their potential to revolutionize the world of electronics. This thesis focuses on the design, fabrication and characterisation of this type of devices with a specific combination of materials, TiN/Ti/HfO<sub>2</sub>/W, which allows full integration with current nano and microelectronic fabrication technologies and shows bipolar resistive switching that is based on the creation and partial dissolution of nanometric conductive filaments.

After a first chapter in which the phenomenon of resistive switching and the physical mechanisms that make it possible are introduced, in the second chapter the fabrication process to obtain this type of devices with two different constructive configurations, cross-point and isolated, is described. Subsequently, after showing the fabricated devices and their physical characterisation, the experimental results of their electrical behaviour are indicated. During the next two chapters, the bipolar resistive switching characteristics exhibited by these devices are studied by applying voltage sweep cycles by means of ramps, and train pulses cycles, either in sequences under constant electrical parameters (chapter 3) or automatically modified, cycle by cycle, to evaluate their multilevel response (chapter 4). Next, the electrical behaviour of the anti-series association of two devices is analysed, a combination which gives rise to the so-called phenomenon complementary resistive switching (chapter 5). To complete the study of these devices, in chapter 6 the physical nature of their conducting filament is investigated by means of a new methodology that allows to locate and classify them in order to find out the electrical state of the device before carrying out the experimental procedure. Then, in chapter 7 the design of new photolithographic masks is presented which permit the fabrication of new devices, both simple and complex (with two or more MIM cells per device), using three types of configuration: cross-point, isolated and isolated cross-point, which is a combination of the first two. In addition, the results of the physical and electrical characterisation of these new devices are showed too. Finally, in chapter 8, the most relevant conclusions of the results obtained in the development of the thesis are summarized.

# ÍNDICE

|                                                                                                                  |           |

|------------------------------------------------------------------------------------------------------------------|-----------|

| <b>1. INTRODUCCIÓN</b>                                                                                           | <b>1</b>  |

| <b>1.1 CONMUTACIÓN RESISTIVA</b>                                                                                 | <b>1</b>  |

| 1.1.1 Fenómeno de la conmutación resistiva                                                                       | 1         |

| 1.1.2 Modos de operación                                                                                         | 2         |

| 1.1.3 Mecanismos físicos responsables                                                                            | 4         |

| 1.1.4 Elección de materiales                                                                                     | 7         |

| 1.1.5 Mecanismo físico en dispositivos TiN/Ti/HfO <sub>2</sub> /W                                                | 9         |

| <b>1.2 APLICACIONES</b>                                                                                          | <b>10</b> |

| 1.2.1 Memorias                                                                                                   | 10        |

| 1.2.2 Computación neuromórfica                                                                                   | 11        |

| 1.2.3 Memorias crossbar sin selector                                                                             | 12        |

| 1.2.4 Puertas lógicas y FPGAs                                                                                    | 13        |

| <b>1.3 OBJETIVOS DE LA TESIS Y METODOLOGÍA</b>                                                                   | <b>14</b> |

| <b>2. TECNOLOGÍA DE FABRICACIÓN</b>                                                                              | <b>17</b> |

| <b>2.1 TECNOLOGÍA DE FABRICACIÓN DE DISPOSITIVOS EN CRUCE</b>                                                    | <b>17</b> |

| <b>2.2 FABRICACIÓN DE DISPOSITIVOS CON CONFIGURACIÓN EN CRUCE</b>                                                | <b>20</b> |

| <b>2.3 TECNOLOGÍA DE FABRICACIÓN DE DISPOSITIVOS AISLADOS</b>                                                    | <b>24</b> |

| <b>2.4 FABRICACIÓN DE DISPOSITIVOS CON CONFIGURACIÓN AISLADA</b>                                                 | <b>27</b> |

| <b>3. CARACTERIZACIÓN DE CONMUTACIÓN RESISTIVA CON CARACTÉRISTICA BIPOLAR</b>                                    | <b>33</b> |

| <b>3.1 PROCEDIMIENTO EXPERIMENTAL DE CARACTERIZACIÓN ELÉCTRICA DE LA CONMUTACIÓN RESISTIVA</b>                   | <b>33</b> |

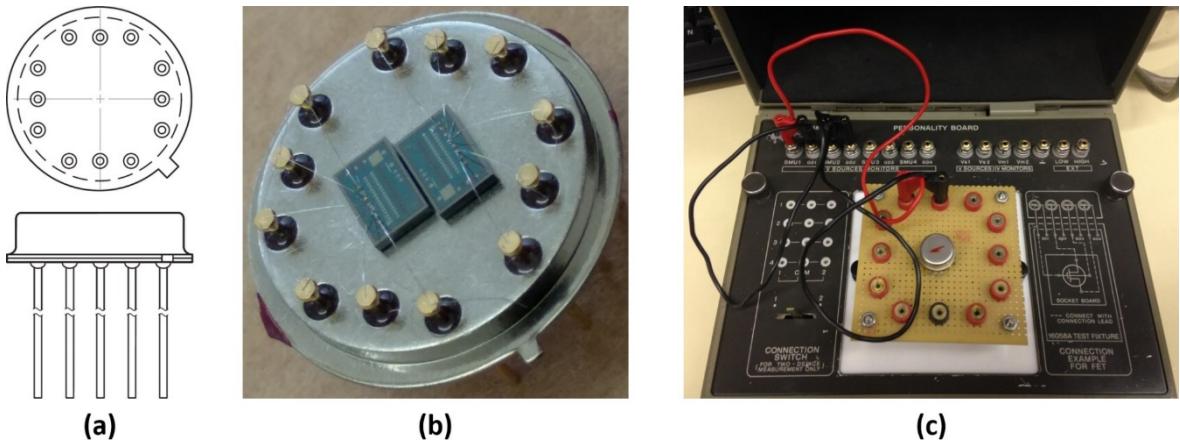

| 3.1.1 Montaje instrumental                                                                                       | 33        |

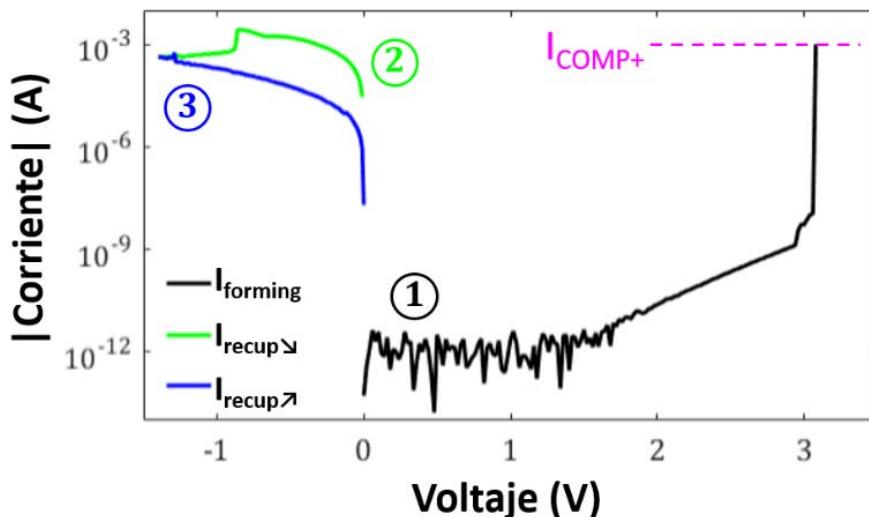

| 3.1.2 Caracterización del proceso de forming                                                                     | 35        |

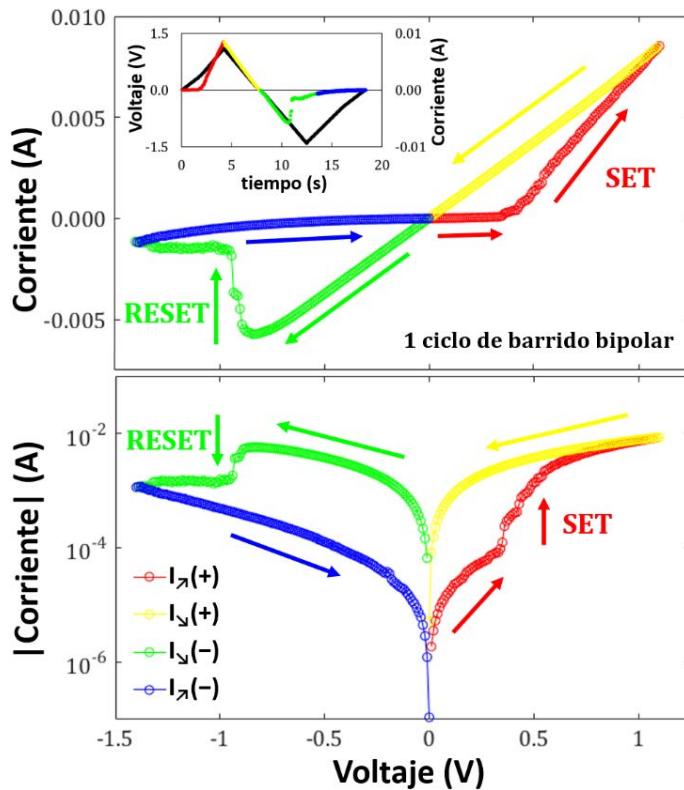

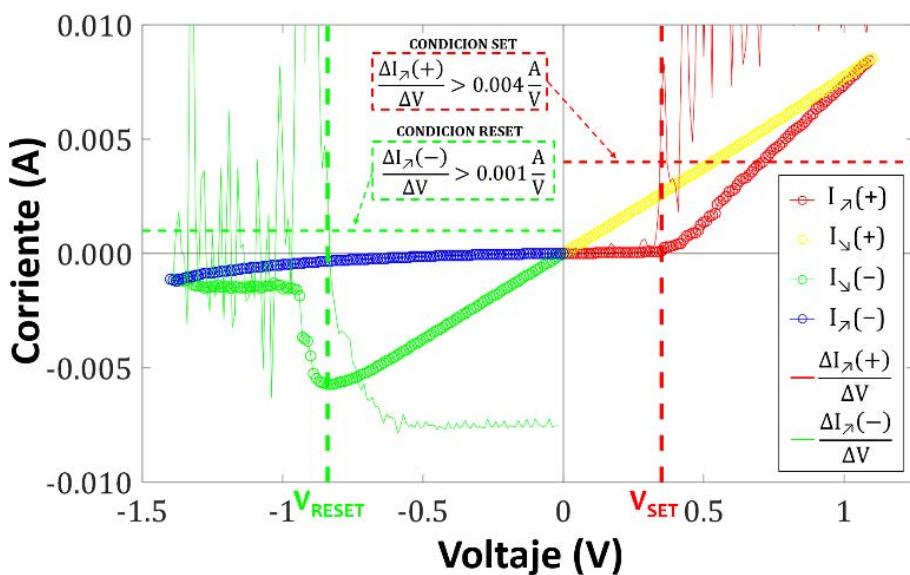

| 3.1.3 Caracterización del fenómeno de la conmutación resistiva                                                   | 36        |

| <b>3.2 RESULTADOS Y DISCUSIÓN</b>                                                                                | <b>39</b> |

| 3.2.1 Medidas con barridos de rampas                                                                             | 39        |

| 3.2.2 Medidas con trenes de pulsos                                                                               | 49        |

| 3.2.3 Evaluación del efecto del aumento V <sub>LIM-</sub>                                                        | 50        |

| <b>3.3 CONCLUSIONES</b>                                                                                          | <b>58</b> |

| <b>4. INVESTIGACIÓN DE LA CAPACIDAD MULTINIVEL DE CONMUTACIÓN RESISTIVA MEDIANTE RAMPAS Y PULSOS PROGRAMADOS</b> | <b>61</b> |

| <b>4.1 PROCEDIMIENTO EXPERIMENTAL DE LA CARACTERIZACIÓN MULTINIVEL</b>                                           | <b>62</b> |

| 4.1.1 Esquema de medida multinivel por barridos                                                                  | 62        |

| 4.1.2 Esquema de medida multinivel por pulsos                                                                    | 63        |

| <b>4.2 RESULTADOS Y DISCUSIÓN</b>                                                                                | <b>64</b> |

| 4.2.1 Evaluación del multinivel por barridos                                                                     | 64        |

| 4.2.2 Evaluación de multiniveles discretos por pulsos                                                            | 67        |

| 4.2.3 Evaluación del comportamiento analógico                                                                    | 68        |

|                                                                                                            |            |

|------------------------------------------------------------------------------------------------------------|------------|

| <b>4.3 CONCLUSIONES</b>                                                                                    | <b>70</b>  |

| <b>5. CONMUTACIÓN RESISTIVA COMPLEMENTARIA</b>                                                             | <b>71</b>  |

| <b>5.1 PROCEDIMIENTO DE CARACTERIZACIÓN ELÉCTRICA DEL FENÓMENO DE CONMUTACIÓN RESISTIVA COMPLEMENTARIA</b> | <b>71</b>  |

| 5.1.1 Montaje instrumental                                                                                 | 71         |

| 5.1.2 Metodología experimental                                                                             | 72         |

| <b>5.2 RESULTADOS Y DISCUSIÓN</b>                                                                          | <b>74</b>  |

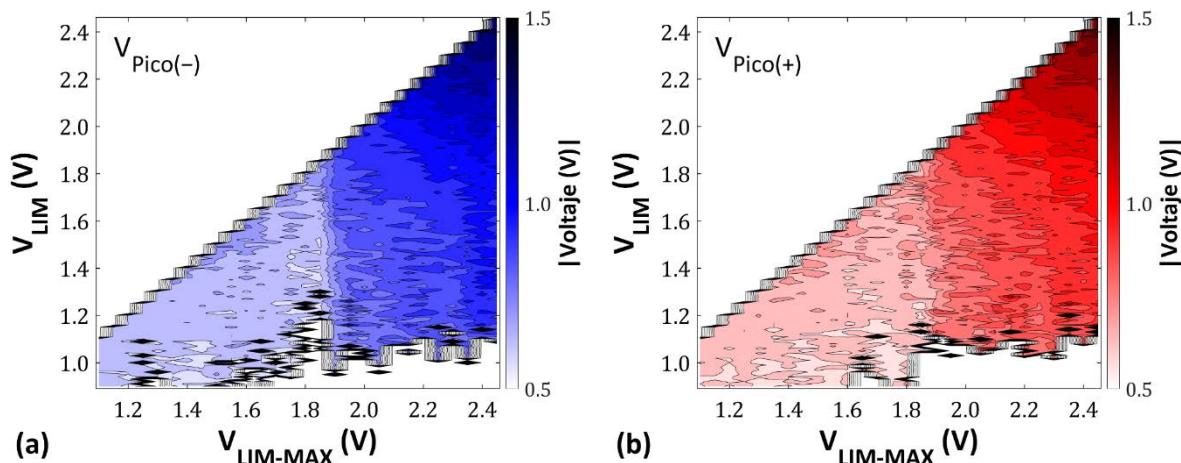

| 5.2.1 Caracterización de un ciclo de CRS                                                                   | 74         |

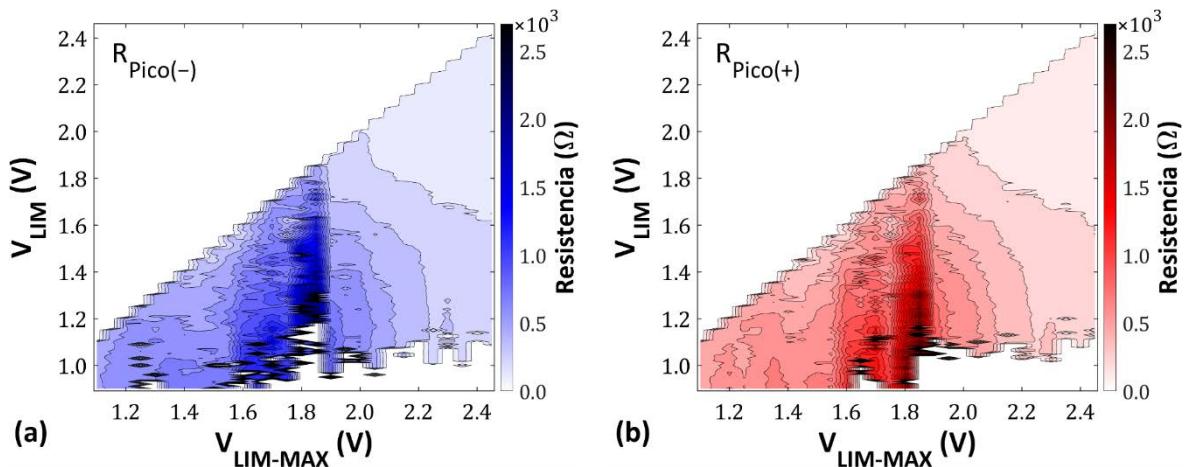

| 5.2.2 Caracterización de la variabilidad ciclo a ciclo de CRS                                              | 77         |

| 5.2.3 Caracterización en función de un pequeño incremento de V <sub>LIM</sub>                              | 80         |

| 5.2.4 Caracterización en función de la variación en zigzag de V <sub>LIM</sub>                             | 82         |

| <b>5.3 CONCLUSIONES</b>                                                                                    | <b>87</b>  |

| <b>6. CARACTORIZACIÓN FÍSICA DE ESTRUCTURAS FILAMENTARIAS MEDIANTE UNA NUEVA METODOLOGÍA</b>               | <b>89</b>  |

| <b>6.1 PROCEDIMIENTO EXPERIMENTAL</b>                                                                      | <b>90</b>  |

| <b>6.2 RESULTADOS Y DISCUSIÓN</b>                                                                          | <b>93</b>  |

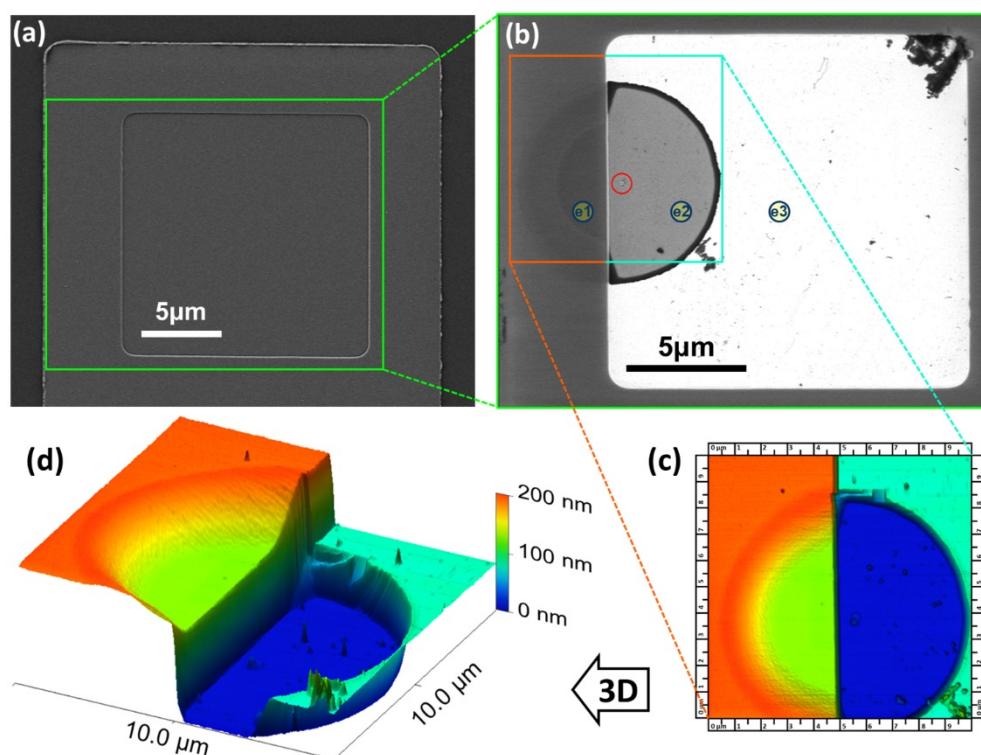

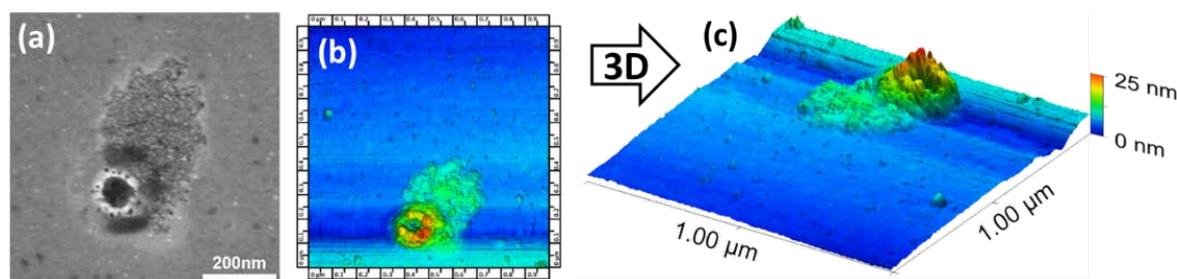

| 6.2.1 Localización de las estructuras filamentarias                                                        | 93         |

| 6.2.2 Hipótesis de la formación del microplato                                                             | 95         |

| 6.2.3 Morfología de un microplato                                                                          | 96         |

| 6.2.4 Análisis composicional de un microplato                                                              | 98         |

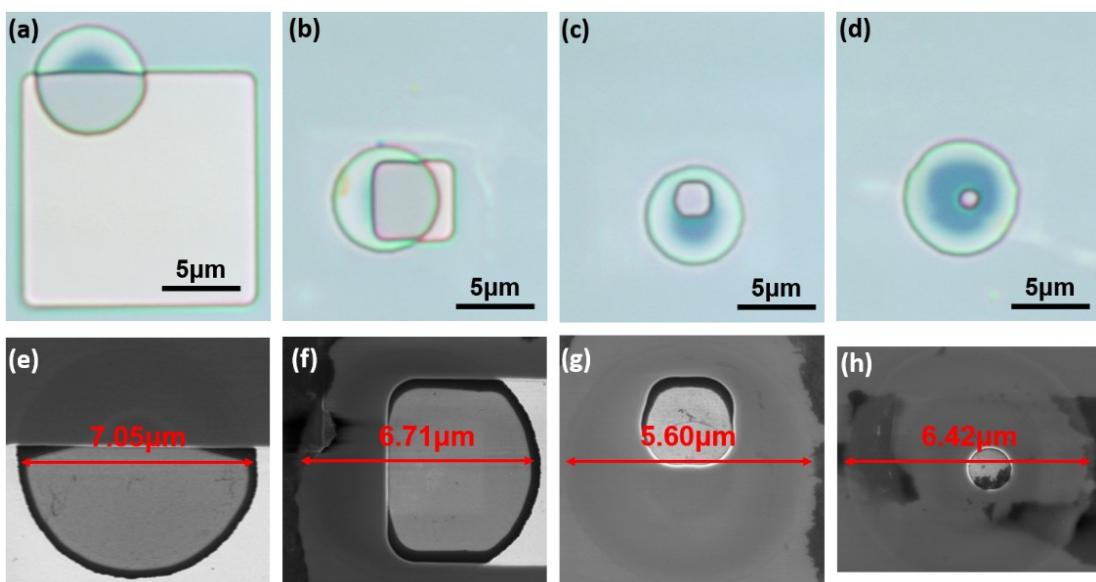

| 6.2.5 Dependencia del tamaño de los microplatos                                                            | 101        |

| 6.2.6 Caracterización del filamento conductor                                                              | 103        |

| <b>6.3 CONCLUSIONES</b>                                                                                    | <b>104</b> |

| <b>7. DISEÑO, FABRICACIÓN Y CARACTORIZACIÓN DE NUEVOS DISPOSITIVOS</b>                                     | <b>105</b> |

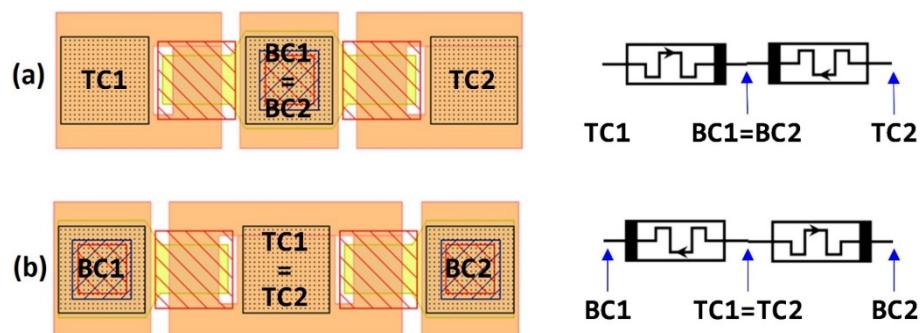

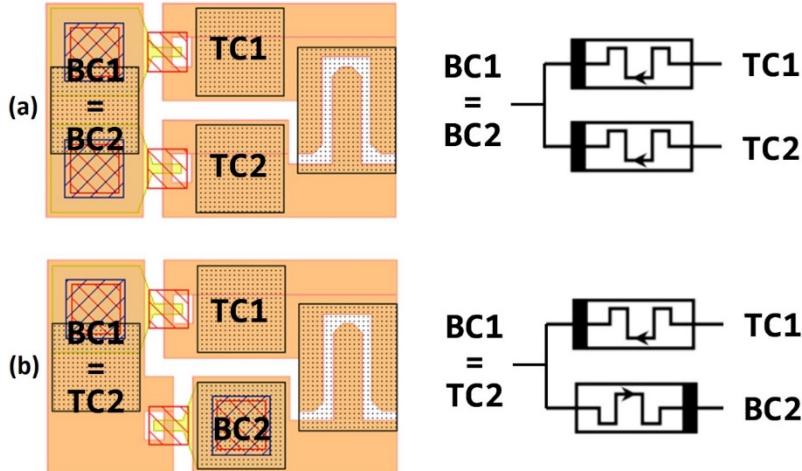

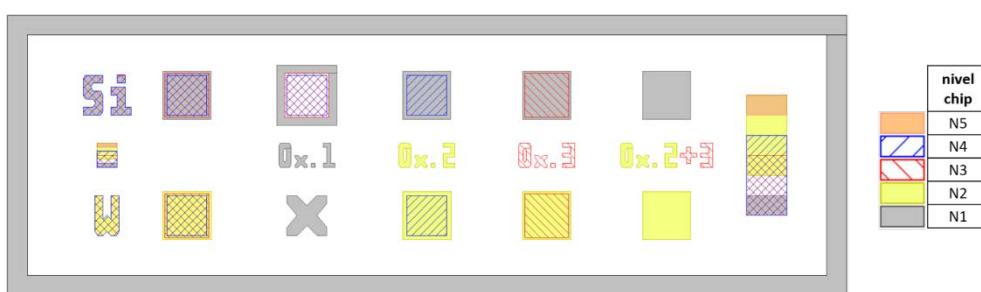

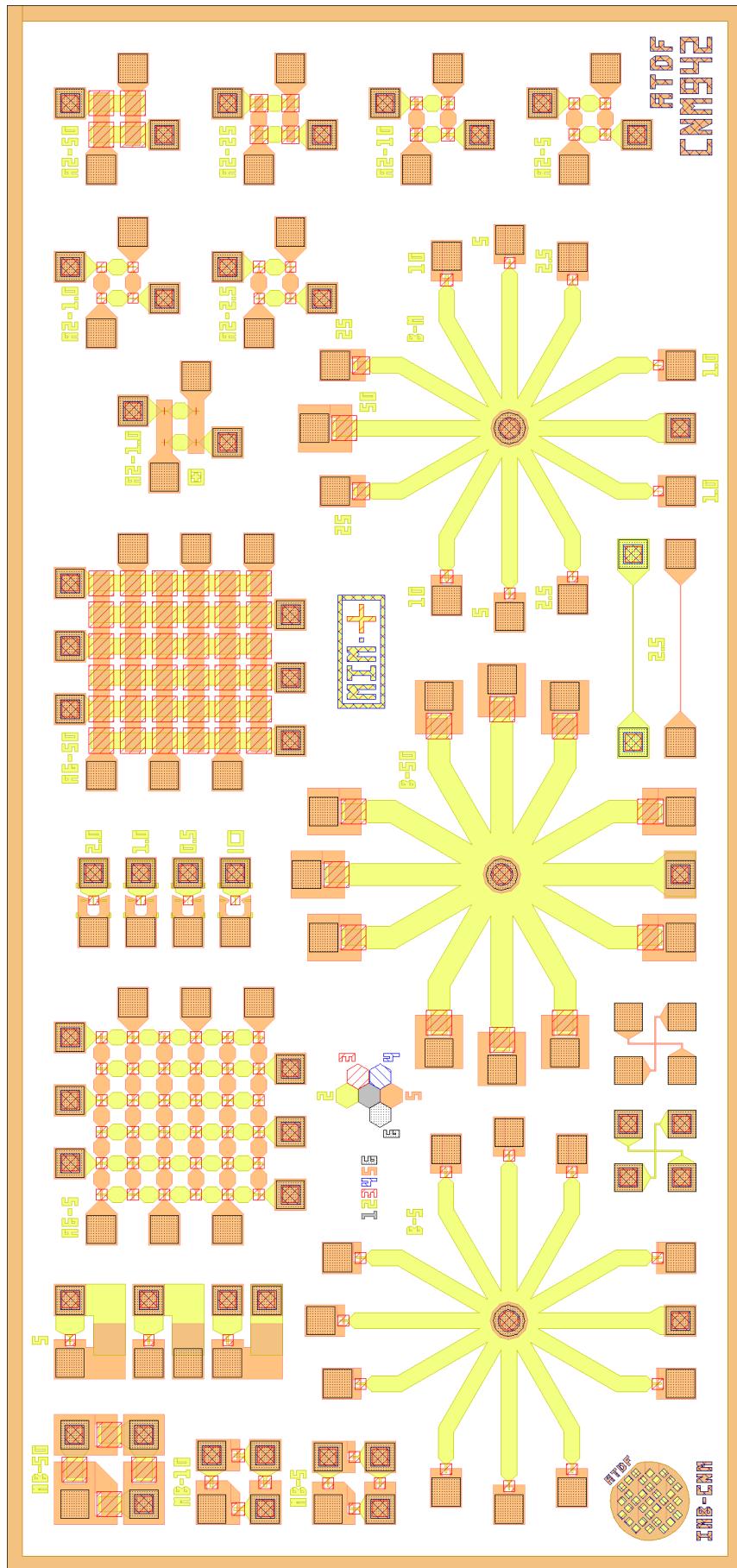

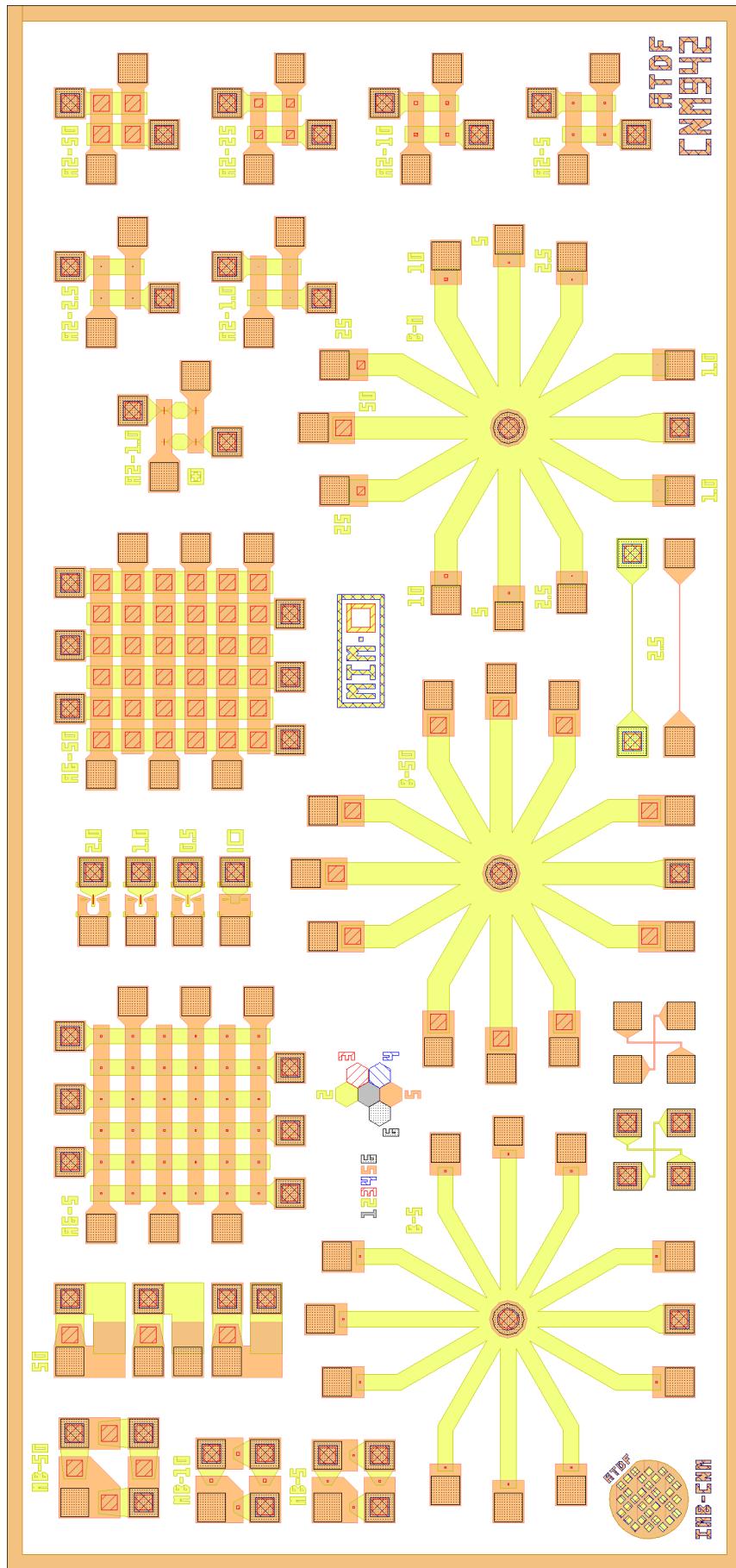

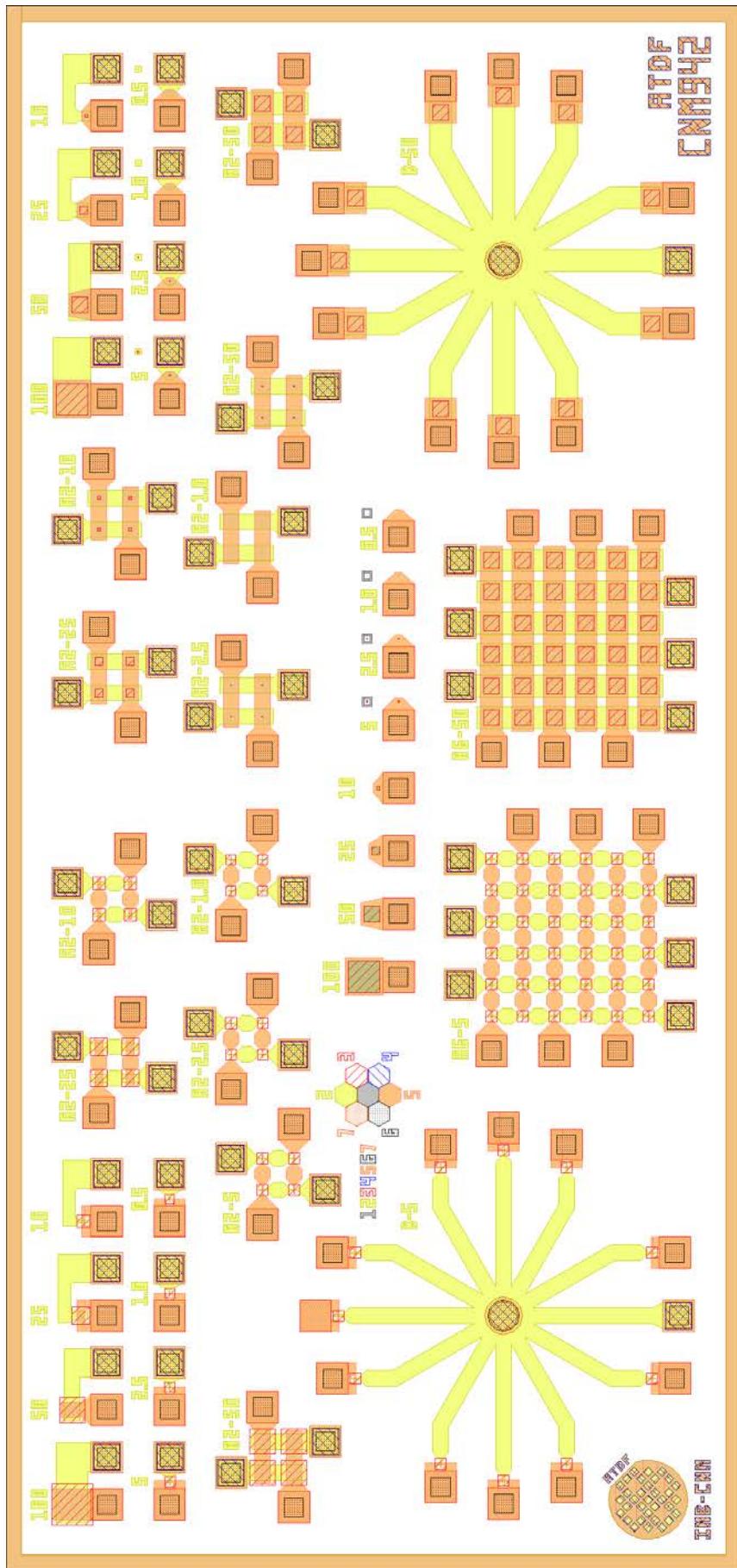

| <b>7.1 DISEÑO DE NUEVOS DISPOSITIVOS</b>                                                                   | <b>105</b> |

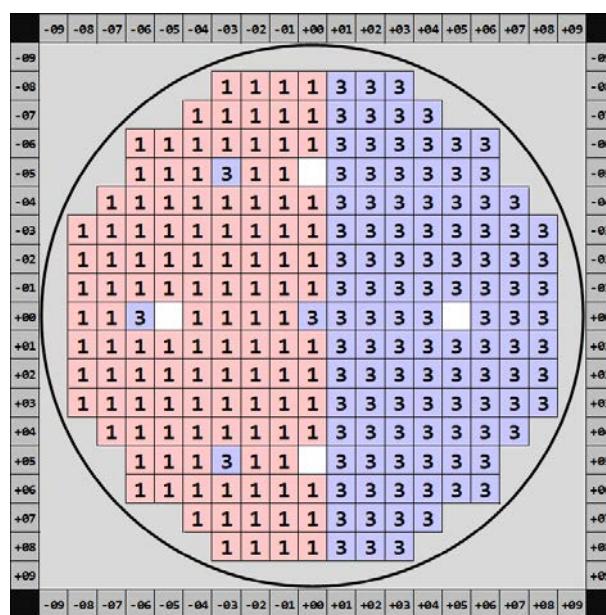

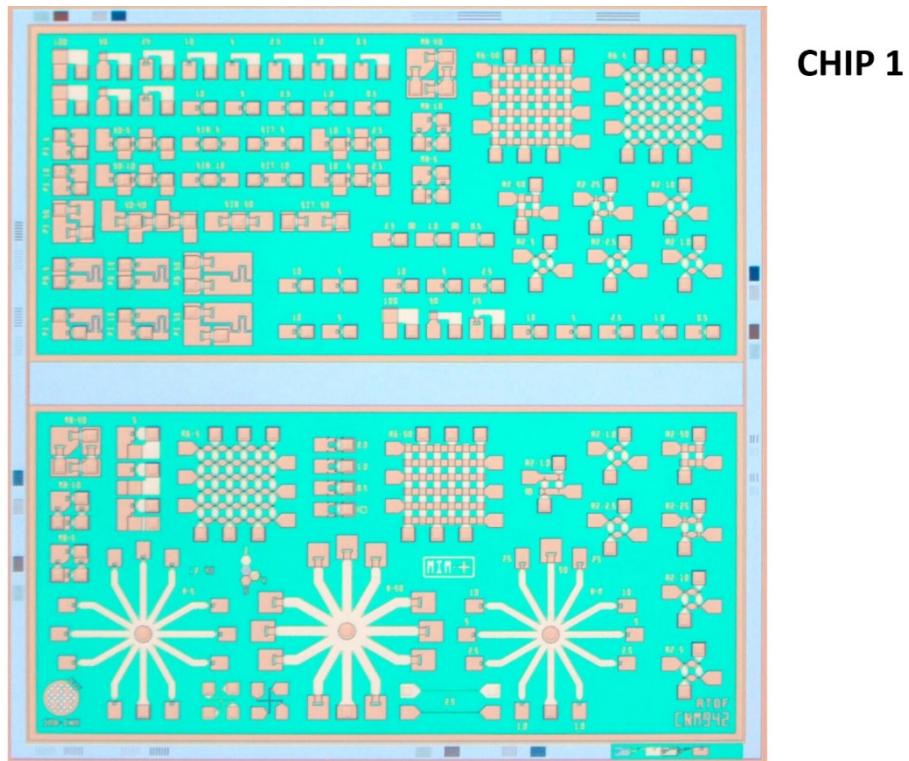

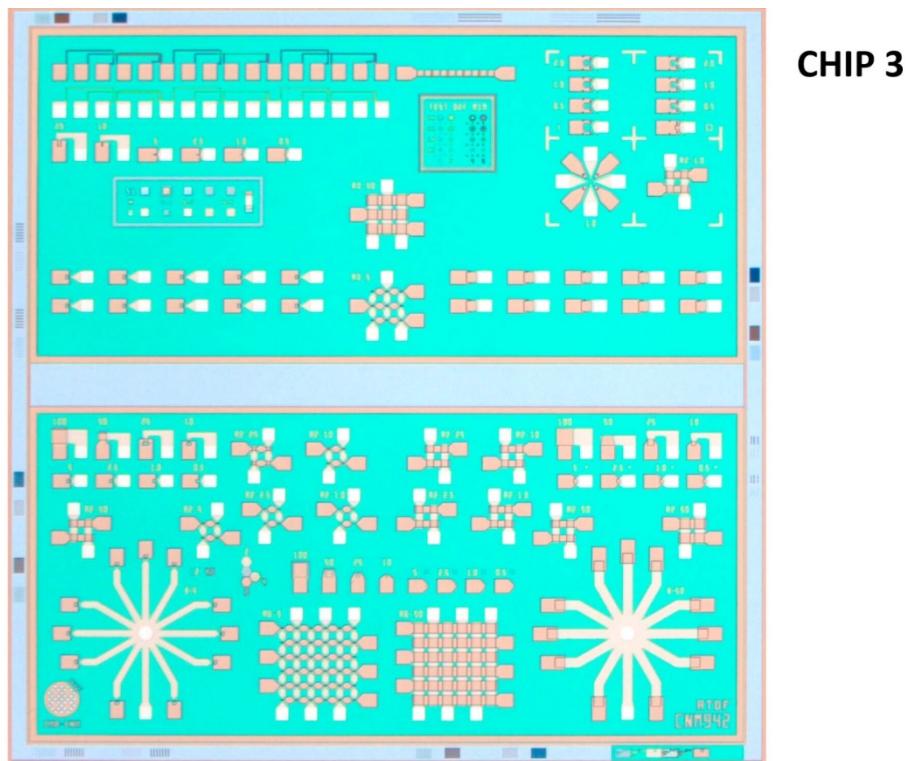

| 7.1.1 Diseño de retículo para stepper                                                                      | 105        |

| 7.1.2 Configuraciones topológicas                                                                          | 111        |

| 7.1.3 Dispositivos simples                                                                                 | 112        |

| 7.1.4 Dispositivos complejos                                                                               | 114        |

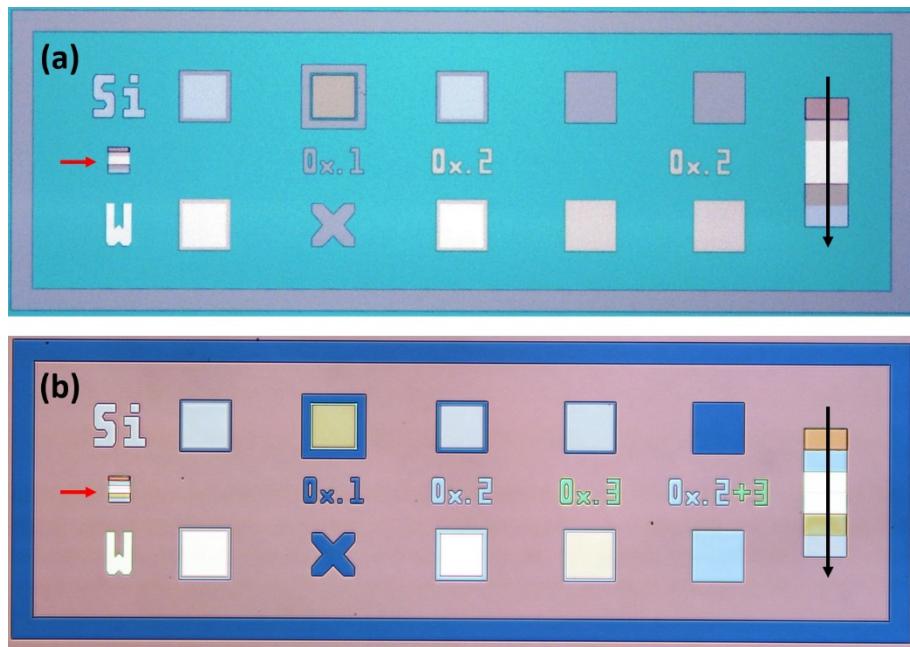

| 7.1.5 Zonas de test                                                                                        | 115        |

| <b>7.2 TECNOLOGÍA DE FABRICACIÓN</b>                                                                       | <b>117</b> |

| 7.2.1 Dispositivos en cruce sin capa de aislamiento                                                        | 118        |

| 7.2.2 Dispositivos con capa de aislamiento                                                                 | 121        |

| <b>7.3 FABRICACIÓN DE DISPOSITIVOS</b>                                                                     | <b>122</b> |

| 7.3.1 Fabricación de obleas con dispositivos sin aislamiento                                               | 122        |

| 7.3.2 Fabricación de obleas con dispositivos con aislamiento                                               | 126        |

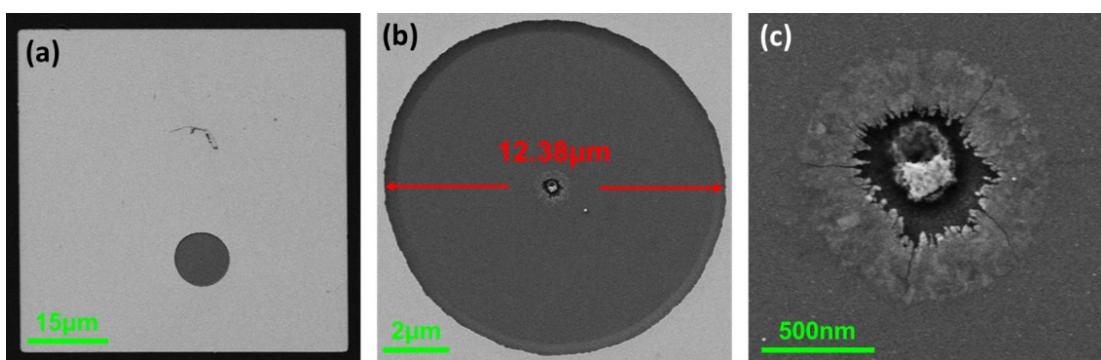

| <b>7.4 CARACTORIZACIÓN FÍSICA</b>                                                                          | <b>134</b> |

| 7.4.1 Inspección de las configuraciones topológicas                                                        | 134        |

| 7.4.2 Espesor de las capas depositadas                                                                     | 137        |

| <b>7.5 CARACTORIZACIÓN ELÉCTRICA</b>                                                                       | <b>142</b> |

| 7.5.1 Montaje instrumental y metodología experimental                                                      | 142        |

| 7.5.2 Resultados en dispositivos simples                                                                   | 144        |

| 7.5.3 Resultados en dispositivos complejos                                                                 | 149        |

| <b>7.6 CONCLUSIONES</b>                                                                                    | <b>155</b> |

|                                          |                   |

|------------------------------------------|-------------------|

| <b><u>8. CONCLUSIONES</u></b>            | <b><u>157</u></b> |

| <b><u>CONTRIBUCIONES CIENTÍFICAS</u></b> | <b><u>161</u></b> |

| <b><u>PREMIOS</u></b>                    | <b><u>165</u></b> |

| <b><u>REFERENCIAS</u></b>                | <b><u>167</u></b> |

| <b><u>ACRÓNIMOS</u></b>                  | <b><u>175</u></b> |

| <b><u>APÉNDICE</u></b>                   | <b><u>177</u></b> |

# **1. Introducción**

---

## **1.1 Conmutación resistiva**

### **1.1.1 Fenómeno de la conmutación resistiva**

La conmutación resistiva, más conocida por su término inglés “resistive switching”, es un fenómeno físico que se observó por primera vez en los años 60 [1,2] en dispositivos tricapa en los que una capa delgada de dieléctrico se encontraba entre dos electrodos. Se descubrió que la resistencia eléctrica del dispositivo podía ser variada o conmutada debido a la aplicación de un campo, o una corriente eléctrica, que proporcionaba una condición de estrés eléctrico capaz de generar un cambio estructural en el material dieléctrico. Las dos características principales que definen este fenómeno son la reversibilidad y la no volatilidad del cambio producido en el valor de la resistencia, es decir, que, con la aplicación repetida de un voltaje o una corriente, los valores de resistencia pueden ser modificados cíclicamente y recuperados (reversibilidad) y, además, si no se aplica ningún estímulo eléctrico posterior el valor de la resistencia permanece constante durante un largo periodo de tiempo (no volatilidad). Estos dispositivos, en los que se da el fenómeno de la conmutación resistiva son conocidos como dispositivos memristivos o memristores. La palabra memristor está formada por la contracción de las palabras memoria y resistor, y expresa el hecho de que es un dispositivo que “tiene memoria”, es decir, el valor de la

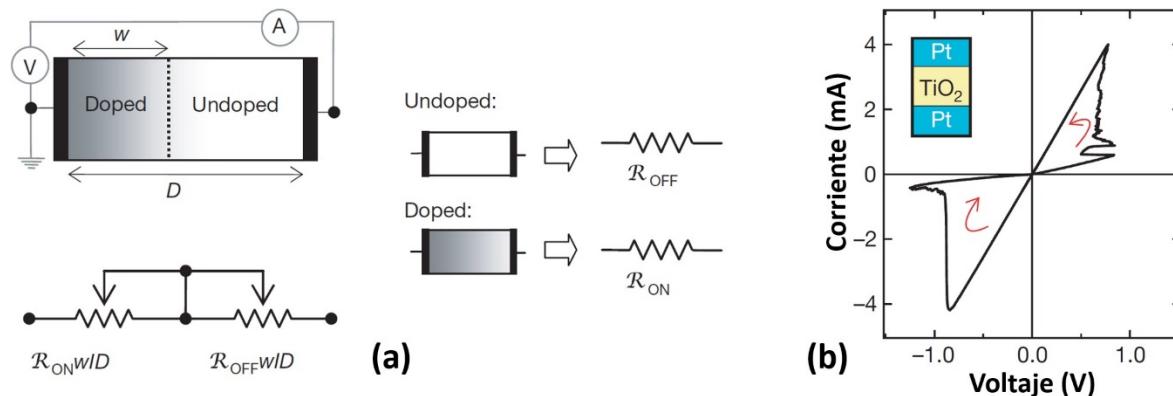

resistencia en un momento determinado depende de las condiciones eléctricas a las que ha sido sometido previamente. Fue en 1971 cuando Leon Chua predijo matemáticamente la existencia de este dispositivo y lo introdujo como el cuarto elemento de circuito pasivo fundamental [3], completando a los otros tres elementos de dos terminales ya existentes, la resistencia, el condensador y la bobina. A diferencia de los condensadores y de las bobinas, los memristores no almacenan energía y, además, no pueden ser construidos combinando los otros elementos. No fue hasta 2008, que un grupo de Hewlett-Packard anunció el descubrimiento de este dispositivo (ver **Figura 1-1**), un dispositivo fabricado con una configuración en cruce cuyos electrodos eran de Pt y su capa de dieléctrico de 5 nm de espesor compuesta por una capa de TiO<sub>2</sub> junto con otra de TiO<sub>2-x</sub> [4].

**Figura 1-1.** (a) Modelo simplificado del comportamiento eléctrico de la resistencia variable del memristor: D, espesor de la capa de dieléctrico; w, variable que indica el estado del dispositivo;  $R_{ON} \ll R_{OFF}$ , valores de resistencia de dos estados resitivos. (b) Curva corriente-tensión de un ciclo de conmutación resistiva de un dispositivo Pt/TiO<sub>2-x</sub>/Pt. Adaptado de [4].

Generalmente en los elementos memristivos tricapa, el electrodo superior es siempre metálico, mientras que el electrodo inferior puede ser metálico o semiconductor. Así pues, desde un punto de vista estructural, dependiendo de la combinación utilizada, se pueden obtener dos tipos de memristores, los MIM (metal-insulator-metal) y los MIS (metal-insulator-semiconductor).

### 1.1.2 Modos de operación

En la observación del fenómeno de la conmutación resistiva, se ha comprobado que el comportamiento está relacionado fuertemente con los materiales utilizados para los electrodos y la capa del dieléctrico, e incluso se ha podido observar que no todas las combinaciones de materiales experimentan un fenómeno de conmutación resistiva.

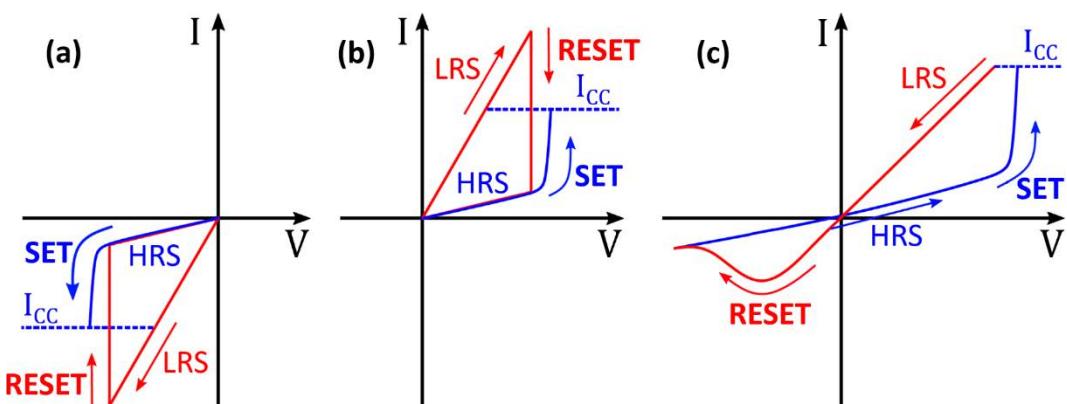

Aunque no es necesario en todos los tipos de materiales [5], por norma general, en la mayoría de los dieléctricos es necesaria la realización previa de una etapa, a la que se denomina proceso de forming, para que se pueda observar posteriormente el comportamiento de conmutación resistiva en el dispositivo. En esta etapa inicial mediante la aplicación de un estrés eléctrico al dispositivo, se produce la degradación de la capa de dieléctrico que hará cambiar el valor de resistencia original del dispositivo virgen a otro muy inferior en un proceso de SET, es decir, el dispositivo habrá cambiado a un estado de baja resistencia o LRS (Low Resistance State) [6]. Un aspecto importante para tener en consideración durante este proceso inicial de forming es el establecimiento de un límite máximo en la corriente ( $I_{CC}$ ) durante la medida para impedir que se produzca una ruptura completa e irreversible de la capa de dieléctrico, que imposibilitaría la presencia de la conmutación resistiva. Una vez concluida esta etapa inicial de forming, al dispositivo se le aplica un estímulo eléctrico, ya sea un voltaje o una corriente, que lo obligue a conmutar mediante un proceso de RESET a un estado de alta resistencia o HRS (High Resistance State). A partir de este momento el dispositivo puede conmutar entre ambos estados gracias a la aplicación sucesiva de voltajes o corrientes. Dependiendo del comportamiento eléctrico general del dispositivo durante este fenómeno, se pueden distinguir dos tipos de conmutación resistiva, la unipolar y la bipolar (ver **Figura 1-2**), si bien es cierto que hay dispositivos con combinaciones de materiales en las que ambos tipos de conmutación coexisten como en Pt/TiO<sub>2</sub>/Pt [7], TiN/HfO<sub>2</sub>/Pt [8], Au/SrTiO<sub>3</sub>/Pt [9] y Al/NiO/ITO [10].

**Figura 1-2.** Esquemas representativos de la característica corriente-tensión (I-V) de los modos de conmutación unipolar negativa (a), unipolar positiva (b) y bipolar (c).

### Conmutación resistiva unipolar

En este tipo de comportamiento la conmutación del dispositivo entre ambos estados resistivos se logra aplicando el voltaje en la misma polaridad. En general, al aplicar el estímulo eléctrico al dispositivo para que cambie al estado menos resistivo LRS hay que limitar la corriente para evitar la ruptura irreversible de la capa de dieléctrico, ya que en la transición SET la corriente aumenta de manera abrupta y sin limitación puede producirse la ruptura dieléctrica irreversible. Sin embargo, para el proceso opuesto no es necesario, ya que durante la transición RESET el dispositivo conmuta al HRS haciendo que la corriente disminuya. Como se puede observar en las **Figura 1-2a,b**, la conmutación unipolar se puede considerar positiva o negativa dependiendo de la polaridad del voltaje que hay que aplicar para producir la conmutación del dispositivo. Ejemplos de dispositivos con conmutación resistiva unipolar son:

- Unipolar negativa en dispositivos Pt/TiO<sub>2</sub>/Ru y Al/TiO<sub>2</sub>/Ru [11].

- Unipolar positiva en dispositivos W/SiO<sub>x</sub>/Si y TiW/SiO<sub>x</sub>/TiW [12], TiN/NiO/Pt, W/NiO/Pt y Pt/ Nb<sub>2</sub>O<sub>5</sub>/Pt [13].

### Conmutación resistiva bipolar

En este caso el cambio de estado resistivo se da a polaridades opuestas, es decir, las transiciones SET y RESET se dan para cada una de las dos polaridades (ver **Figura 1-2c**). Este comportamiento es muy común y se observa en un gran número de dieléctricos (TiO<sub>2</sub>, TaO<sub>x</sub>, HfO<sub>x</sub>, Al<sub>2</sub>O<sub>3</sub>, Cr<sub>2</sub>O<sub>3</sub>, SiN, BaTiO<sub>3</sub>) o incluso en óxido de grafeno [14,15]. En general, dependiendo de la combinación de materiales utilizada y los límites de voltaje aplicados, puede ser necesario o no la limitación de corriente durante la transición SET para impedir la destrucción de la capa de dieléctrico.

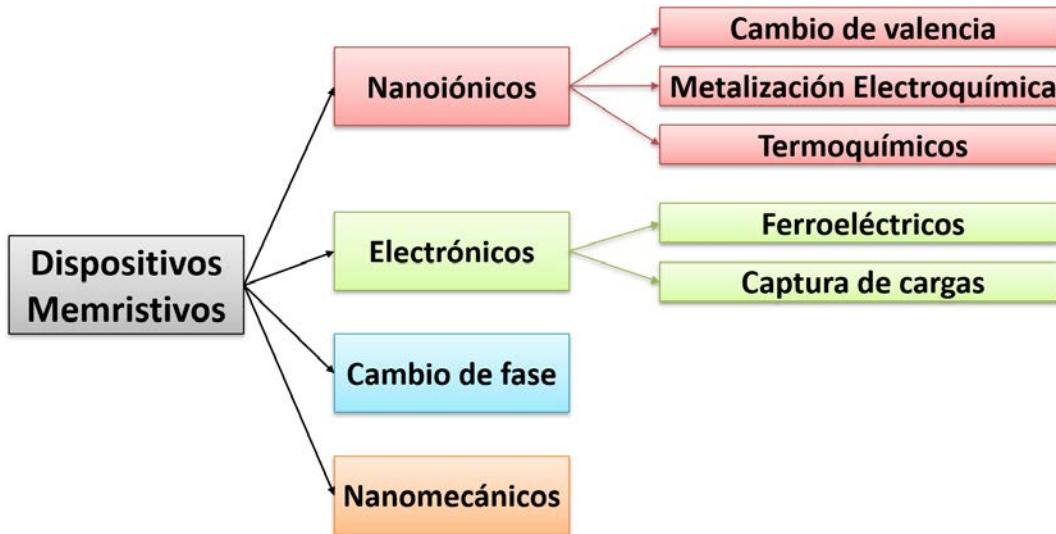

### 1.1.3 Mecanismos físicos responsables

Desde el momento en que la conmutación resistiva se descubrió y se observó que era un fenómeno físico reproducible en una cantidad elevada de combinaciones de materiales con un comportamiento que posee un gran potencial para su incorporación a diferentes sistemas en el campo de la electrónica, ha habido una intensa investigación sobre los mecanismos físicos responsables que pueden explicar el cambio del valor de la resistencia que se produce en estos y que depende fuertemente tanto del dieléctrico usado, como de

la composición de los electrodos. Así pues, dependiendo del mecanismo físico que provoca la conmutación resistiva, los dispositivos se pueden clasificar en cuatro tipos [16], como se indica en la **Figura 1-3** y que se describen brevemente a continuación:

1. **NANOIÓNICOS.** En estos dispositivos los cambios estructurales que provocan el cambio en la resistencia se deben al mecanismo de transporte de iones [17,18]. Dependiendo de cómo se lleva a cabo el mecanismo se puede distinguir tres subcategorías:

- a. **Cambio de valencia.** En este caso el movimiento de iones corresponde a un desplazamiento de los iones de oxígeno del óxido metálico que constituye la capa del dieléctrico por la aplicación de un campo eléctrico externo. Dependiendo de la polaridad de este campo se lleva a cabo una reacción redox en la que, o se generan vacantes de oxígeno por la migración de los iones (reducción) o estas vacantes son llenadas de nuevo por la vuelta de los iones (oxidación). Durante este proceso cíclico redox, el mecanismo de la conmutación resistiva se lleva a cabo por la creación/destrucción de un filamento conductor constituido por vacantes de oxígeno y que une ambos electrodos metálicos.

- b. **Metalización electroquímica.** En este caso el dispositivo debe tener un electrodo con un metal activo, es decir, cuyos iones puedan difundir en la capa del dieléctrico, y el otro electrodo con un metal inerte, es decir, térmicamente muy estable. En este caso la migración iónica corresponde a la difusión de los iones del metal activo en el interior de la capa de dieléctrico, los cuales formaran el filamento conductor entre ambos electrodos. La aplicación cíclica de voltaje es la que generará las condiciones térmicas y eléctricas necesarias para la difusión del metal y, por tanto, la creación del filamento y su disolución.

- c. **Termoquímicos.** En este caso pueden estar presentes ambos mecanismos físicos descritos previamente, pero actuando en una polaridad, y con la diferencia que la migración de iónica es inducida por el campo eléctrico y efectos térmicos debido al efecto Joule.

2. **ELECTRÓNICOS.** En estos dispositivos el mecanismo que lidera la conmutación resistiva está relacionado con el cambio de la conducción electrónica. Se dividen en dos subcategorías:

- a. **Ferroeléctricos.** La capa que está entre los electrodos es de un material ferroeléctrico y con la aplicación de un campo eléctrico se puede modificar la polarización del material haciendo que cambie la resistencia y, por tanto, provocando la conmutación resistiva del dispositivo [19].

- b. **Captura de cargas.** En este caso el dispositivo posee una capa de dieléctrico en la cual los electrones pueden ser atrapados o liberados por la aplicación de un campo eléctrico externo provocando el cambio de la resistencia del dispositivo [20].

3. **CAMBIO DE FASE.** Estos dispositivos se obtienen cuando se emplean calcogenuros para su fabricación. La base de su funcionamiento está en la propiedad que tienen estos materiales de cambiar su red atómica desde un estado amorfo, en el cual el dispositivo se encontraría en un estado de baja resistencia, a un estado cristalino, correspondiente al estado de alta resistencia. Para producir el cambio de fase es necesario la introducción de calor al sistema, que puede provenir de una fuente de calor externa o por una corriente eléctrica elevada [21].

4. **NANOMECÁNICOS.** En este caso se utilizan fuerzas mecánicas que provocan cambios en el nano sistema, como por ejemplo en un sistema formado por una sola molécula o un nanotubo de carbono cuyo cambio de configuración provoca la conmutación del estado resistivo del dispositivo [22].

Figura 1-3. Clasificación de los dispositivos memristivos según el mecanismo físico.

#### 1.1.4 Elección de materiales

Como se ha detallado, hay una multitud de combinaciones de materiales que producen la conmutación resistiva, aunque basada en diferentes mecanismos físicos. Con el paso de los años cada vez hay un abanico mayor e incluso últimamente se está experimentando con materiales de origen orgánico como hojas de loto [23], albúmina [24] y quitosano [25]. En el contexto de esta tesis, sin embargo, nos centramos en memristores con materiales cuyas principales características sean:

- Compatibilidad con tecnologías CMOS para una posible integración futura con cualquier circuito integrado.

- Disponibilidad de los procesos de fabricación necesarios.

Con estos requisitos, los materiales elegidos para fabricar las tres capas de las estructuras MIM han sido:

1. **Wolframio** para el electrodo inferior. Es un metal muy apropiado debido a que químicamente es muy inerte y no se oxida con el aire a temperatura ambiente [26,27]. Este hecho es muy conveniente debido a que si tanto las pistas del electrodo inferior, como el contacto eléctrico de este, se oxidan, el aumento de la resistencia eléctrica del material debido a este cambio se puede traducir en una disminución del control eléctrico que se puede tener sobre el dispositivo. Además, tiene una gran conductividad eléctrica, hecho que permite fabricar el electrodo

inferior con una capa más delgada, sin que se incremente sobremanera la resistencia del dispositivo, factor que será clave en algunos dispositivos y posee también una buena conductividad térmica que favorece la disipación del calor generado durante los ciclos de conmutación resistiva.

2. **Óxido de hafnio** para la capa de dieléctrico. Es un material que se lleva empleando desde el 2007 para la fabricación de transistores en microprocesadores [28] lo que lo convierte en una buena opción a la hora de incorporarse en un proceso de fabricación conjunta con transistores. De hecho, debido a esta integración con la tecnología de fabricación CMOS convencional, los dispositivos RRAM filamentarios basados en HfO<sub>2</sub> son actualmente un tema de intensa investigación [29–31].

3. Un apilamiento de **nitruro de titanio sobre titanio** para el electrodo superior. Esta elección se debe principalmente a que entre la amplia variedad de combinaciones de materiales exploradas para la interfaz dieléctrico/electrodo, la opción de las RRAM basadas en Ti/HfO<sub>2</sub> ha logrado uno de los resultados más prometedores en términos de comportamiento de conmutación resistiva bipolar [32,33]. El mecanismo físico de la conmutación resistiva de los dispositivos basados en Ti/HfO<sub>2</sub> puede atribuirse a la formación y ruptura parcial de filamentos conductores deficientes en oxígeno, donde la capa de Ti, que presenta una alta afinidad por el oxígeno, actúa como un material captador de iones. De esta manera, parte de los iones O<sup>2-</sup> de la capa de HfO<sub>2</sub> en contacto con la superficie de la capa metálica del electrodo superior tienden a migrar hacia el Ti favoreciendo la formación del filamento conductor responsable del fenómeno de la conmutación resistiva [34]. El uso de una capa de Ti sobre la capa de HfO<sub>2</sub> proviene de la buena adherencia que algunos metales muestran sobre capas de óxidos, como también ocurre con el Cr [35]. Esta propiedad hace que estén muy presentes en las combinaciones de estructuras MIM, siendo la combinación Ti/HfO<sub>2</sub> es la más prometedora. El TiN es un material que presenta una buena adhesión e integración que con el Ti. Este material cerámico con propiedades metálicas posee una gran estabilidad química a temperatura ambiente mientras que conduce bien el calor y la electricidad [36–38] convirtiéndolo en un candidato ideal.

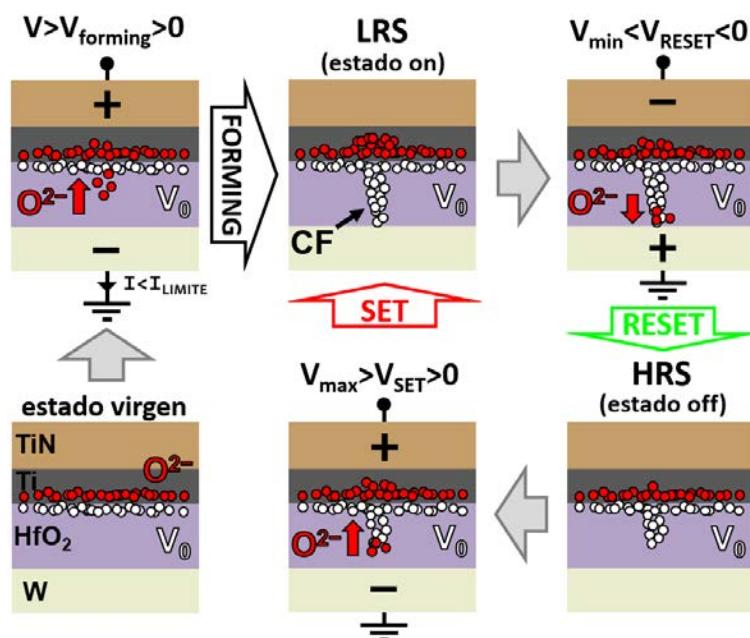

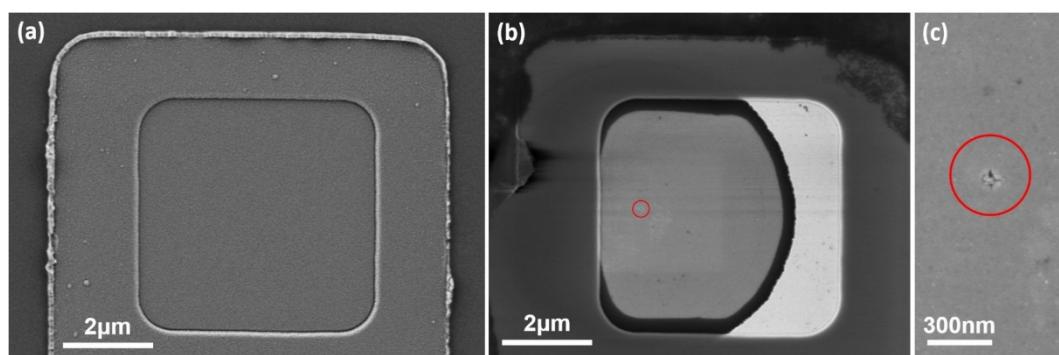

### 1.1.5 Mecanismo físico en dispositivos TiN/Ti/HfO<sub>2</sub>/W

En la **Figura 1-4** se muestra una representación esquemática del proceso físico responsable del fenómeno de la conmutación resistiva bipolar que va a estar presente en los dispositivos cuya estructura MIM va a estar fabricada con los materiales elegidos TiN/Ti/HfO<sub>2</sub>/W [39], concretamente de tipo nonioónico con cambio de valencia. Inicialmente, después de que el dispositivo haya sido fabricado (estado virgen), se crea una cierta cantidad de vacantes de oxígeno ( $V_0$ ) justo debajo de la interfaz Ti/HfO<sub>2</sub> debido a la gran afinidad por el oxígeno del Ti. Durante el proceso de forming se aplica una rampa de voltaje positivo hasta un valor que asegura que se produce un SET, es decir, el estado del dispositivo, inicialmente en estado virgen, cambia al LRS al crearse un filamento conductor rico en vacantes de oxígeno en la capa de HfO<sub>2</sub> [40]. A continuación, se aplica una rampa de voltaje negativo que produce un RESET, es decir, el estado del dispositivo comuta al HRS debido a que el filamento se rompe parcialmente al recombinar las vacantes con los iones de oxígeno. Finalmente, se aplica una rampa de voltaje positivo durante la que se produce un SET, es decir, el dispositivo comuta otra vez al LRS debido a que se ha producido un proceso de recuperación del filamento conductor, generando vacantes de

**Figura 1-4.** Representación esquemática de los mecanismos físicos que explican el comportamiento de la conmutación resistiva. Inicialmente, en un dispositivo virgen, en la zona del dieléctrico adyacente al Ti hay una región substequímica de HfO<sub>x</sub>. Durante el proceso de forming, un filamento conductor rico en vacantes de oxígeno se forma. Este filamento se rompe y recupera parcialmente en cada ciclo de conmutación resistiva cuando el dispositivo comuta de HRS a LRS (SET) y de LRS a HRS (RESET) respectivamente.

oxígeno, el cual proporciona generalmente un comportamiento tipo óhmico al dispositivo [41].

## 1.2 Aplicaciones

Debido al gran abanico de posibilidades existente entre todos los tipos de elementos memristivos, y el potencial que presentan [42,43], actualmente se está llevando a cabo una gran actividad de investigación para integrar estos dispositivos en una gran variedad de aplicaciones de diversa índole como aplicaciones de seguridad [44,45], resolución de problemas matemáticos [46], sistemas de control [47] o incluso computación cuántica [48,49], pero las que más destacan son las cuatro siguientes:

### 1.2.1 Memorias

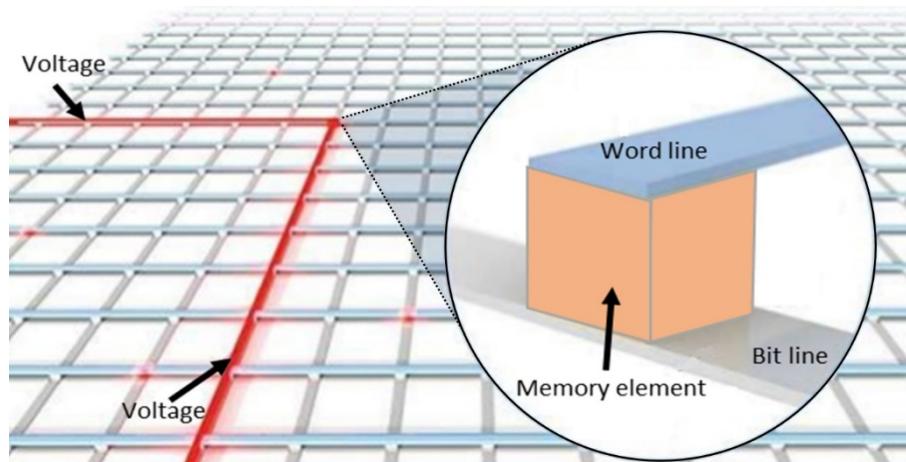

Dentro de todo el abanico de posibles aplicaciones que se han planteado para los memristores, la más estudiada ha sido sin lugar a dudas la del funcionamiento como dispositivos de memoria. En las memorias de acceso aleatorio resistivas o RRAM (Resistive Random Access Memories) el funcionamiento es muy sencillo, cada celda de memoria, como la representada en la **Figura 1-5**, almacenaría un bit, que sería 0 o 1, según el estado resistivo del elemento, HRS o LRS.

**Figura 1-5.** Representación gráfica de una matriz crossbar 2D donde se accede a cada elemento del registro aplicando el voltaje adecuado a las líneas de palabra y bit. Adaptado de [16].

En general las RRAM son unas candidatas muy prometedoras para el futuro almacenaje de información digital debido a que: poseen una gran velocidad de cambio de estado resistivo,

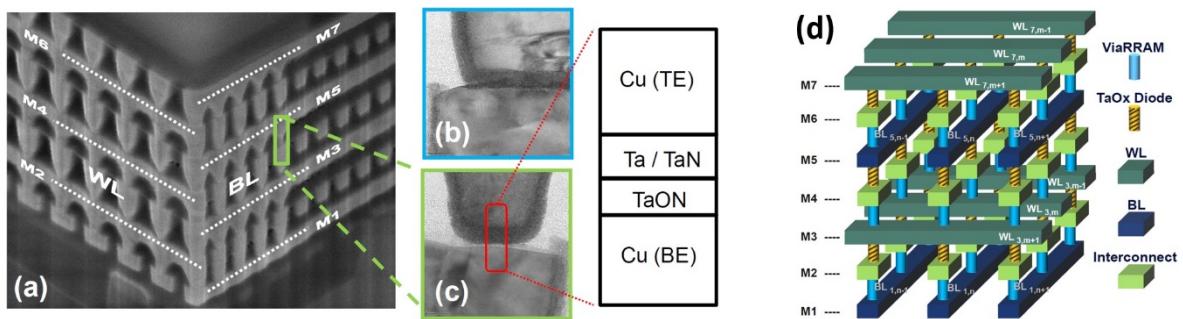

lo que permite obtener memorias con una alta frecuencia de trabajo; muestran una gran robustez, traduciéndose en memorias con más ciclos de vida; muestran una buena retención de los estados resistivos, lo cual permite obtener memorias fiables, y su tamaño es menor que los actuales transistores, posibilitando fabricar memorias de mayor densidad [14,50,51]. La primera memoria RRAM fabricada, en 2002, fue una matriz de 64 bits usando una tecnología CMOS con una resolución de 500 nm [52], aunque hoy en día ya se han realizado los primeros intentos de la fabricación de stacks en 3D para incrementar enormemente la densidad de almacenaje, como se puede ver en la **Figura 1-6** donde se muestra una RRAM 3D conseguida con una tecnología CMOS de 28 nm [53].

**Figura 1-6.** (a) Imagen SEM de una RRAM 3D. (b) Imagen TEM de una pista estándar de Cu. (c) Imagen TEM de una celda de memoria de área 30×30 nm<sup>2</sup>. (d) Diagrama de las capas apiladas en la RRAM 3D. Adaptado de [53].

### 1.2.2 Computación neuromórfica

Uno de los usos más prometedores para esta floreciente tecnología es en el campo de la computación neuromórfica, en la cual los dispositivos memristivos se usan como elementos de conexión sináptica entre los elementos electrónicos que funcionan como neuronas (ver **Figura 1-7a**) en circuitos neuromórficos inspirados en sistemas biológicos, los cuales exigen un comportamiento predecible y capacidades de aprendizaje [54–57]. Esta toma de rol por parte de los memristores es posible gracias a que la conmutación resistiva que presentan les confiere un comportamiento analógico multinivel que puede establecer un “peso sináptico”, en función del valor de su resistencia, que permite replicar la plasticidad que tiene una sinapsis biológica real cuando quiere fortalecer o debilitar la conexión entre dos neuronas. Adicionalmente, además del planteamiento utilizando un memristor para cada sinapsis neuronal, también se está estudiando la posibilidad de

emular la conexión sináptica haciendo uso de un puente de memristores (ver **Figura 1-7b**) [58].

**Figura 1-7.** (a) Diagrama representativo de la equivalencia entre una conexión neuronal biológica y un memristor. Adaptado de [57]. (b) Circuito de un puente de memristores. El peso sináptico se puede controlar variando el voltaje de entrada ( $V_{in}$ ). Adaptado de [58].

### 1.2.3 Memorias crossbar sin selector

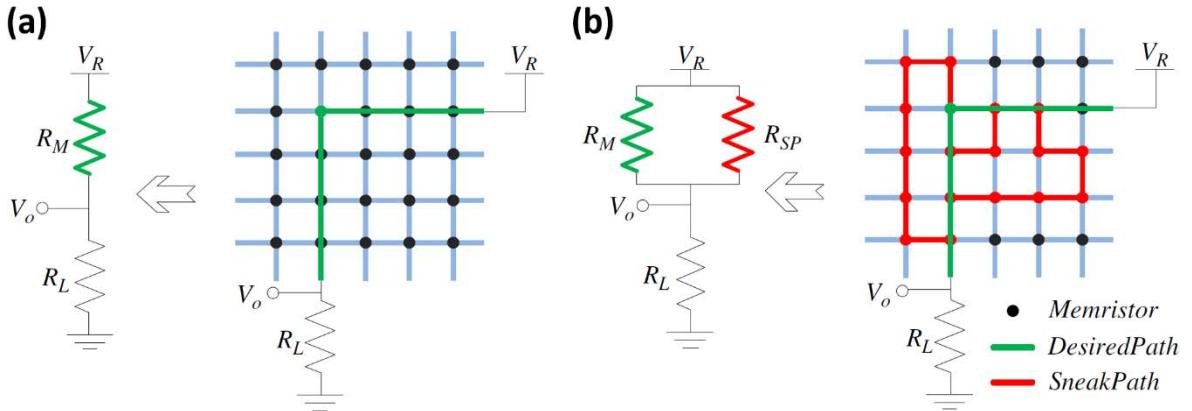

Una de las formas más eficientes y usadas de fabricación de memristores para la funcionalidad observada en los dos puntos anteriores es el de la disposición en una matriz (o array) de dispositivos, ya que proporciona una mayor densidad de dispositivos y una mayor eficiencia energética, además de permitir una alta interconexión entre ellos emulando la alta interconexión que existe en las redes neuronales biológicas [59–61]. Como contrapartida, este modo de organización presenta un problema, el sneak-path [62] que se muestra en la **Figura 1-8**. Este efecto se produce cuando al realizar una operación de lectura de un dispositivo determinado en la matriz, el valor obtenido puede estar modificado por los valores de los dispositivos vecinos que se encuentran en la misma fila, o columna, ya que una parte significativa de la corriente que fluye a través de este dispositivo puede fluir a través de los vecinos. Ante tal problema se han propuesto varias soluciones [62,63] siendo la del uso auxiliar de diodos o transistores para cada dispositivo memristivo una de las más extendidas. Sin embargo, entre estas opciones, hay una en la que no hace falta utilizar ningún otro elemento electrónico aparte de los propios memristores con la consiguiente simplificación en el proceso de fabricación. Esta solución está basada en la conmutación resistiva complementaria, o CRS (Complementary Resistive Switching), un comportamiento que se obtiene al asociar dos dispositivos, que presenten conmutación resistiva bipolar, en una disposición antiserie [64–67].

**Figura 1-8.** Esquemas eléctricos del circuito equivalente para: (a) caso ideal en el que la corriente sólo fluye a través del elemento de memoria seleccionado y (b) caso real donde la corriente serpentea a través de de caminos no deseados (sneak paths). Extraido de [63].

### 1.2.4 Puertas lógicas y FPGAs

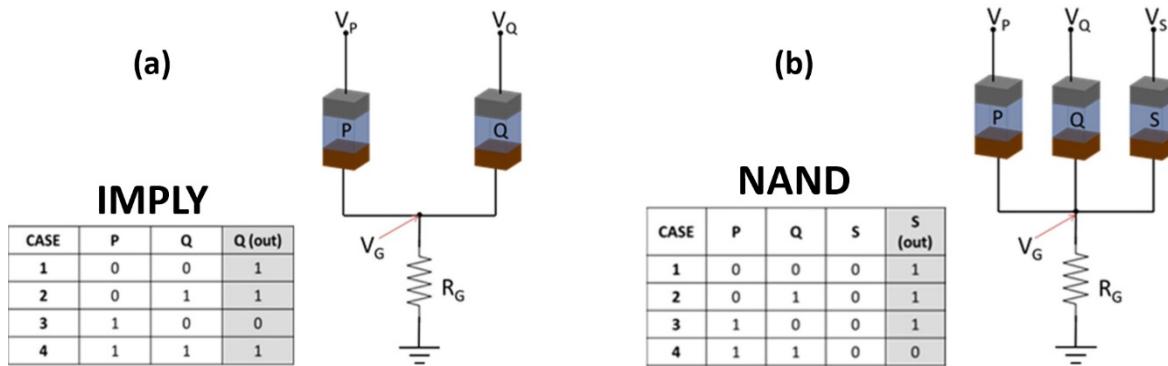

Los memristores pueden funcionar tanto como elementos de memoria como para implementar operaciones lógicas [68] como se puede observar en la **Figura 1-9** donde se muestran dos funciones lógicas implementadas por dos circuitos constituidos por memristores. Adicionalmente, se ha desarrollado una nueva metodología para el desarrollo de puertas lógicas donde el valor de la resistencia de un memristor es usada como un valor lógico [69,70]. Esta dualidad operativa puede permitir un paso evolutivo en el uso de estos dispositivos para aplicaciones lógicas en el campo de la computación, ya que actualmente, en los sistemas convencionales de computación, la unidad memoria y la unidad de procesamiento se encuentran separadas y gracias al uso de memristores, ambas podrían integrarse en un único módulo. Este desarrollo e implementación de los memristores como elementos en circuitos lógicos también proporciona la oportunidad de integrar estos dispositivos en las matrices de puertas lógicas programables o FPGA (Field Programmable Gate Array), permitiendo obtener arquitecturas más pequeñas, con mayor rendimiento y un menor consumo [71,72].

Figura 1-9. (a) Tabla de verdad y esquema del circuito eléctrico de la función lógica IMPLY. (b) Tabla de verdad y esquema del circuito eléctrico de la función lógica NAND. Adaptado de [70].

### 1.3 Objetivos de la tesis y metodología

Como se ha podido ir contemplando durante este capítulo de introducción, la investigación en el campo de los dispositivos electrónicos que presentan el fenómeno de la conmutación resistiva está tomando una gran relevancia en los últimos años debido al gran potencial que exhiben para múltiples aplicaciones. Debido a tal motivación, esta tesis doctoral se ha propuesto la fabricación de dispositivos en tecnología de silicio basados en estructuras MIM con HfO<sub>2</sub> y su posterior estudio y caracterización con vistas a optimizar la tecnología de fabricación de estos dispositivos y alcanzar una visión más profunda en los aspectos físicos y tecnológicos. Específicamente, los objetivos principales que se han planteado han sido:

1. La fabricación de dispositivos, con estructuras MIM, que presenten conmutación resistiva y su caracterización física.

2. La medida y el análisis de las características eléctricas de conmutación resistiva (fiabilidad, durabilidad, variabilidad...) de los dispositivos fabricados para evaluar su potencial para las diferentes aplicaciones en las que podrían ser integrados.

3. El diseño de nuevas máscaras fotolitográficas, que permitan la fabricación de nuevos dispositivos, tanto simples como complejos, la fabricación de estos y su posterior caracterización física y eléctrica.

La metodología empleada para alcanzar los objetivos propuestos y que se desarrolla a lo largo de esta memoria ha consistido en los siguientes puntos:

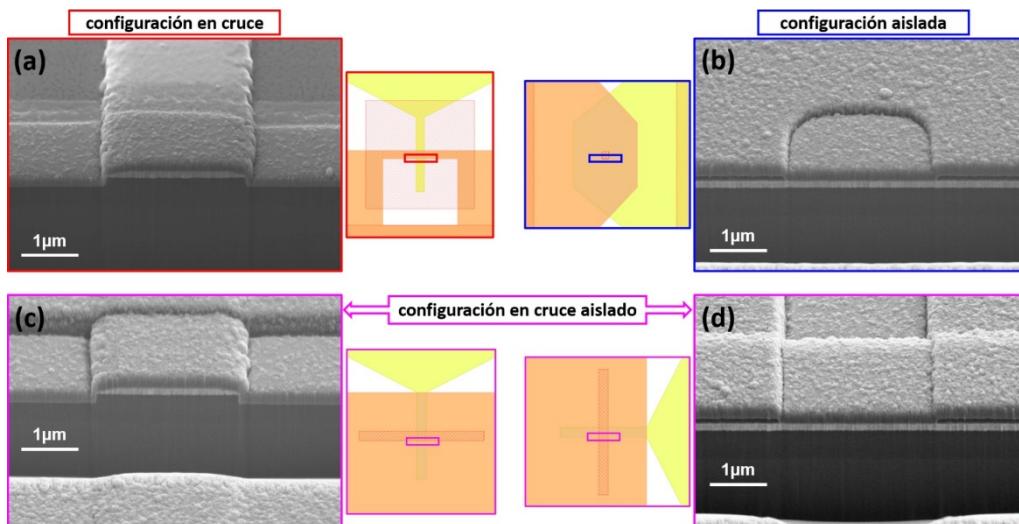

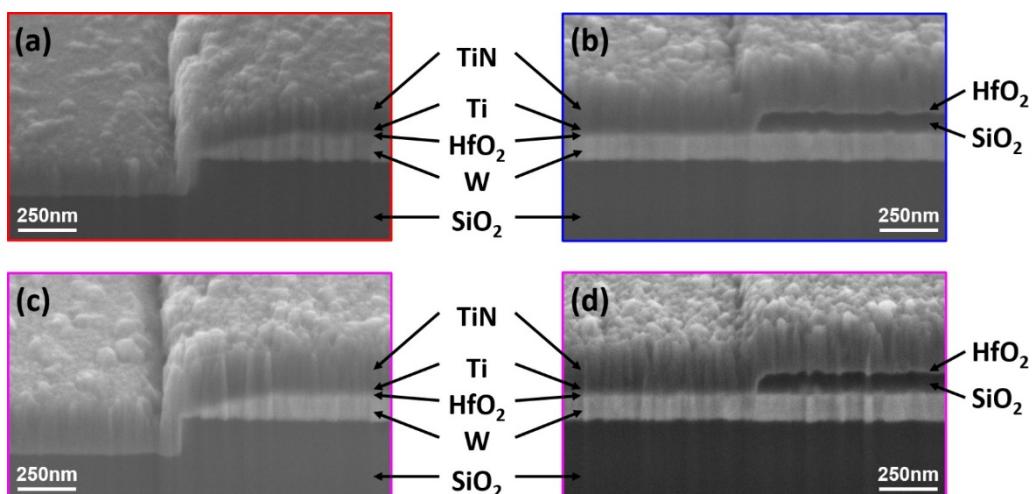

En primer lugar, se han fabricado dispositivos TiN/Ti/HfO<sub>2</sub>/W, sobre obleas de silicio de 100 mm de diámetro, usando un juego de máscaras fotolitográficas de contacto ya existentes que han permitido obtener este tipo de dispositivos mediante dos configuraciones constructivas diferentes, en cruce y aislada. La fabricación se ha realizado íntegramente en la sala blanca del Instituto de Microelectrónica de Barcelona (IMB-CNM, CSIC). Una vez fabricados los lotes de obleas con los dispositivos e inspeccionados ópticamente los distintos lotes de obleas, se ha llevado a cabo la caracterización física de las diferentes configuraciones de estructuras MIM fabricadas mediante un equipo SEM con un FIB incorporado, que ha permitido estudiar las secciones de estas estructuras. Estos resultados se muestran en el **capítulo 2**.

Posteriormente se ha procedido a caracterizar eléctricamente los dispositivos, realizando medidas eléctricas sobre oblea en una mesa de puntas usando un analizador de parámetros de semiconductores controlado mediante Matlab. Para estudiar y analizar el comportamiento de la conmutación resistiva en los dispositivos fabricados se han aplicado ciclos de barrido de voltaje mediante rampas y ciclos de trenes de pulsos. En el **capítulo 3** se describen los resultados obtenidos aplicando largas secuencias de estos ciclos manteniendo los parámetros de las medidas eléctricas constantes, mientras que en el **capítulo 4** se muestran los resultados obtenidos variando los parámetros durante las medidas. Este modo de medida se ha aplicado con la intención de evaluar la capacidad multinivel de conmutación resistiva que pueden poseer estos dispositivos.

Una vez observado el buen comportamiento en los dispositivos, se ha procedido a caracterizar el fenómeno de la conmutación resistiva complementaria que se da cuando dos dispositivos, que poseen conmutación resistiva, se asocian en antiserie. En este caso, como se indica en el **capítulo 5**, se han aplicado ciclos de barrido de voltaje mediante rampas, tanto en medidas con parámetros eléctricos fijos, como en medidas en los que se han ido variando los parámetros, para evaluar el comportamiento de este fenómeno en ambos regímenes.

Una vez realizada la caracterización eléctrica, se ha realizado un análisis del fenómeno físico subyacente en los dispositivos para lo que se ha desarrollado de una nueva metodología, presentada en el **capítulo 6**, en la que mediante un grabado químico de la capa metálica del electrodo superior y una posterior caracterización física de las estructuras MIM de los

dispositivos, se han podido localizar los filamentos conductores en las estructuras MIM de los dispositivos, así como determinar el estado eléctrico en el que se encontraban antes de realizar este procedimiento experimental.

Finalmente, en el **capítulo 7** se describe el nuevo conjunto de máscaras fotolitográficas diseñadas para poder fabricar nuevos dispositivos, tanto simples como complejos (con dos o más celdas MIM por dispositivo), usando tres tipos de configuración: en cruce, aislada y en cruce aislado, que es una combinación de las dos primeras. En el mismo capítulo se describen los procesos de fabricación empleados para la fabricación de dispositivos mediante el nuevo conjunto de diseños, así como los resultados experimentales obtenidos de la caracterización eléctrica de los dispositivos simples y complejos fabricados.

Del conjunto de resultados alcanzados se ha llegado a las conclusiones descritas en el **capítulo 8**, finalizando esta memoria con un listado de las contribuciones científicas publicadas en el marco de esta tesis doctoral.

## **2. Tecnología de fabricación**

---

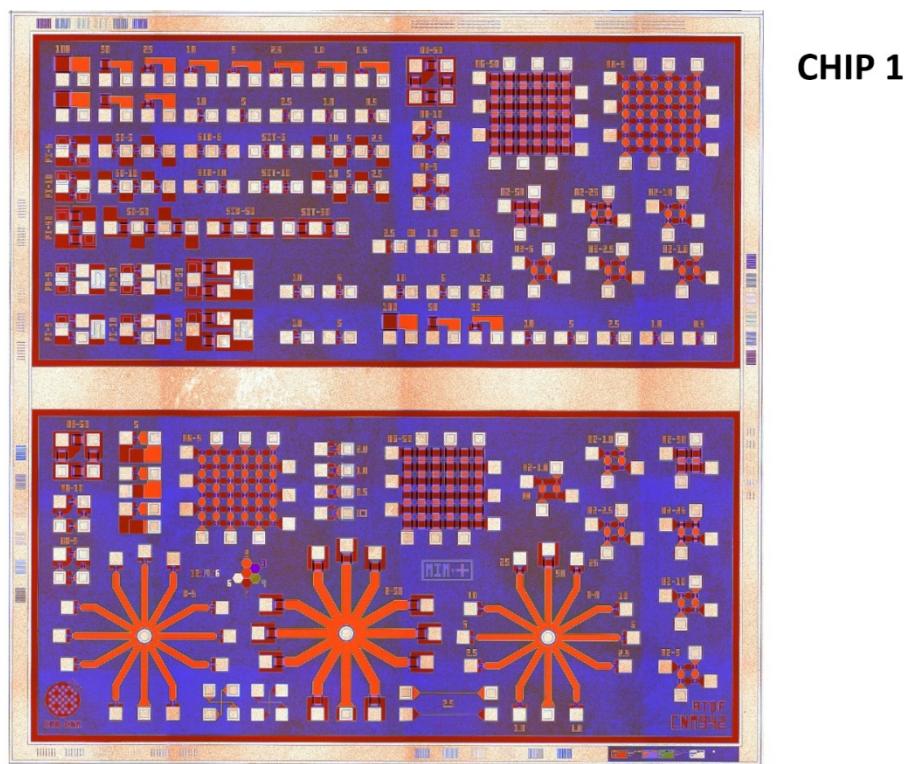

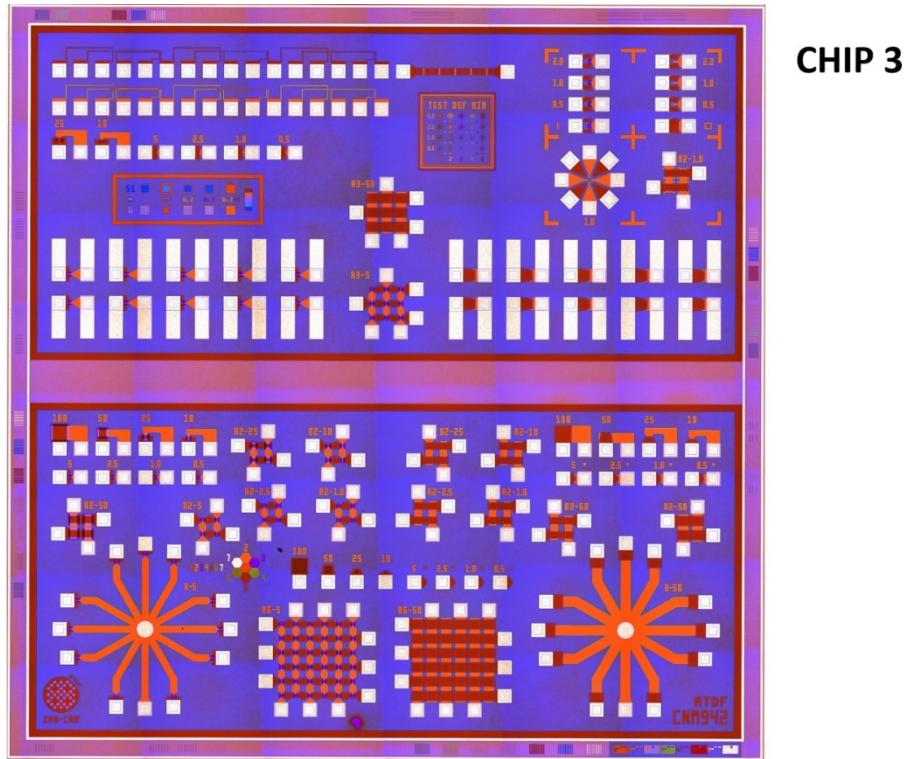

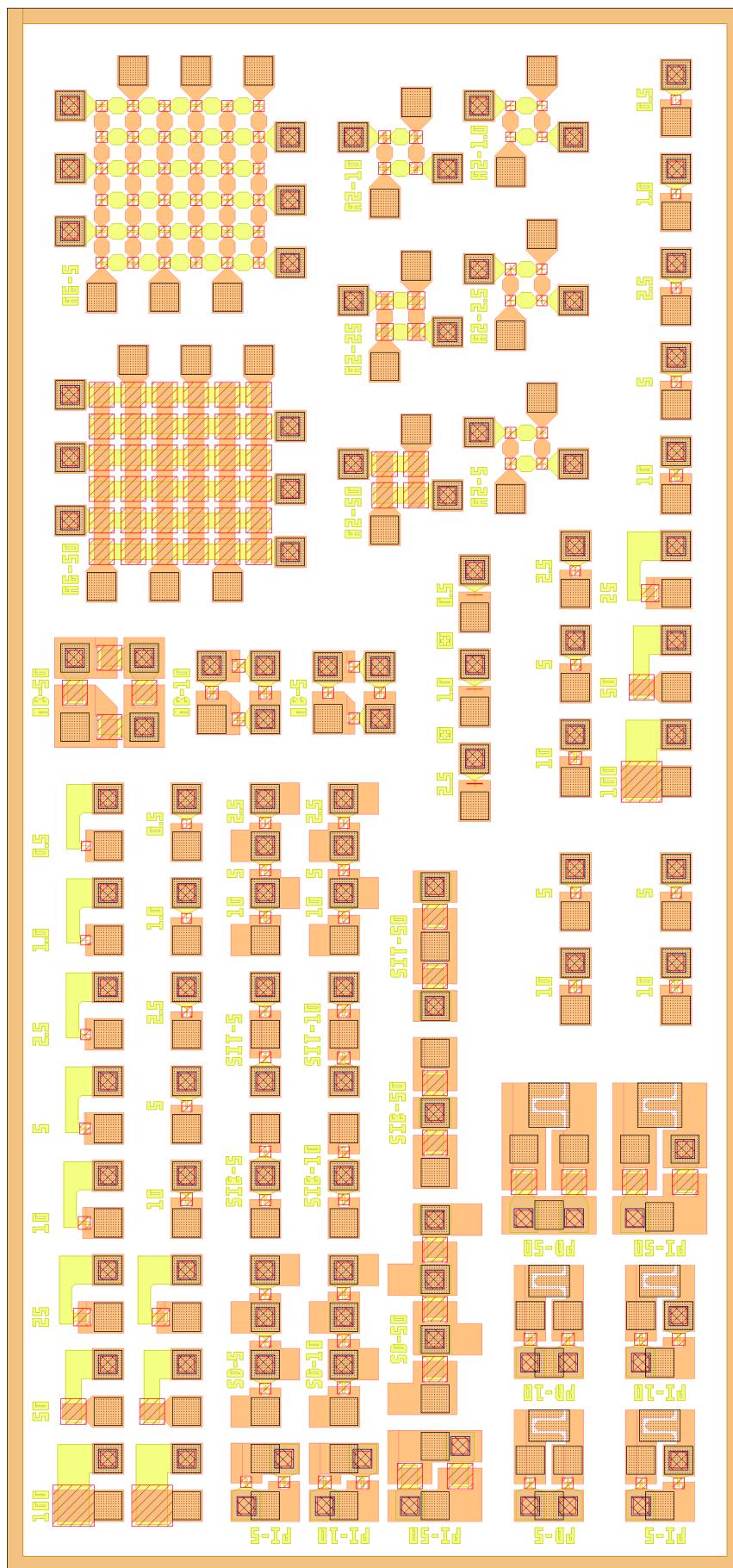

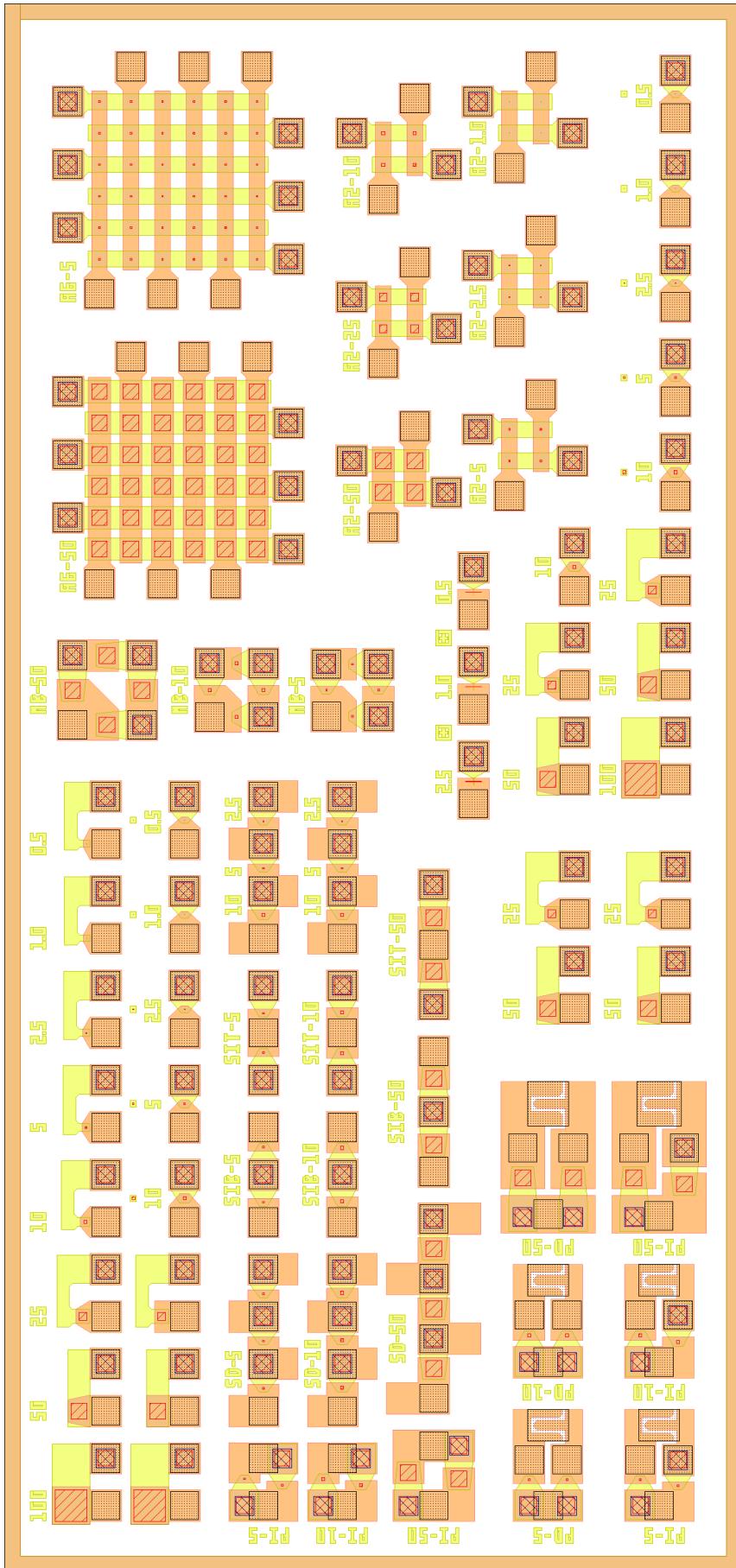

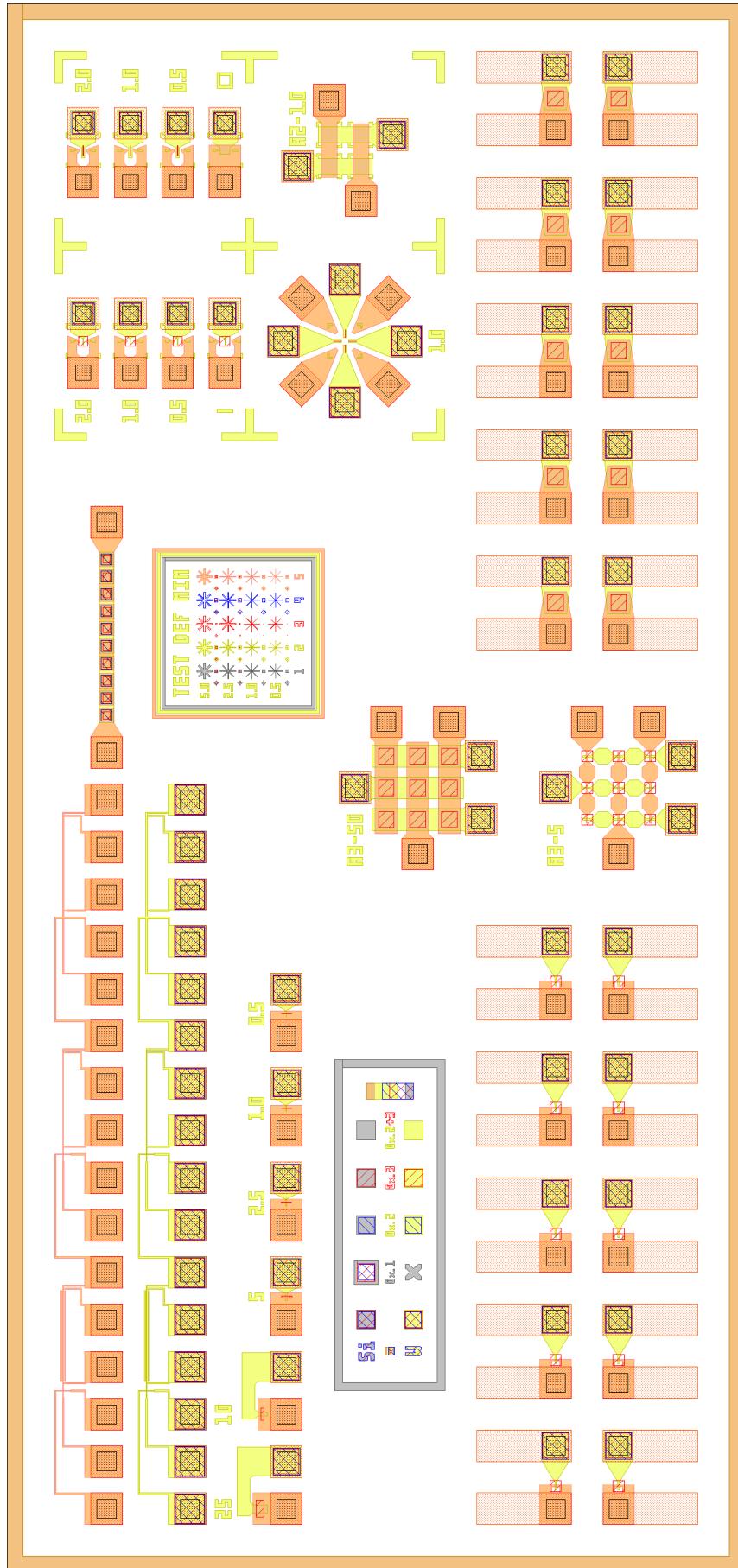

A lo largo de esta tesis doctoral hemos fabricado y caracterizado una variedad de estructuras Metal-Aislante-Metal (MIM) de distintas características físicas. En una primera etapa, se ha usado el conjunto de máscaras CNM733 ya disponible [73], que permite fabricar estructuras MIM y estructuras Metal-Aislante-Semiconductor (MIS) de distintas áreas junto con estructuras CBR para el test de líneas de metal. Las obleas fabricadas han permitido estudiar en profundidad la comutación resistiva de los dispositivos, y a partir de los resultados obtenidos, en una segunda etapa, se ha diseñado un nuevo conjunto de máscaras cuyas características, tecnología asociada y resultados son el objeto del capítulo 7.

A continuación, pasamos a describir la tecnología empleada para la fabricación de los dispositivos de las dos configuraciones estudiadas en la primera etapa, así como los resultados tecnológicos correspondientes a los distintos lotes de obleas fabricados.

### **2.1 Tecnología de fabricación de dispositivos en cruce**

La primera opción para la fabricación de una estructura MIM corresponde a la configuración en cruce o cross-point, en la que la celda MIM está definida por un cruce entre dos pistas metálicas, una perteneciente al electrodo superior y otra al electrodo

inferior sobre el que se deposita la capa de dieléctrico. En este caso, el tamaño de la celda MIM, o lo que es lo mismo, el área activa del dispositivo, está definida por el ancho de estas pistas metálicas en el cruce. Para la fabricación de estos dispositivos son necesarios 3 niveles de máscaras fotolitográficas:

- Nivel 1. Define el electrodo inferior de los dispositivos.

- Nivel 2. Define el electrodo superior de los dispositivos.

- Nivel 3. Define las aperturas en la capa de dieléctrico que constituirán los pads para el contacto eléctrico al electrodo inferior de los dispositivos.

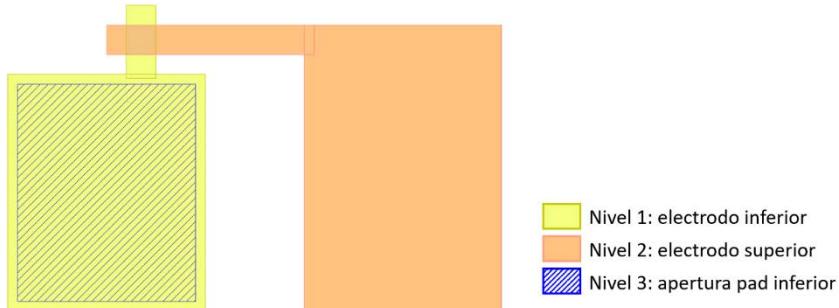

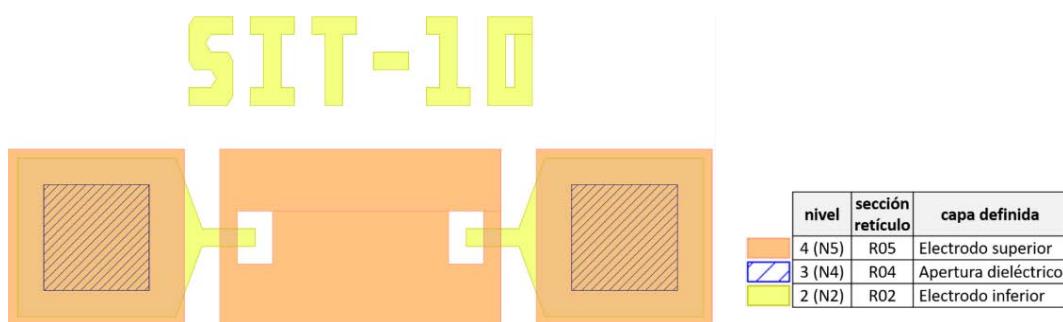

En la **Figura 2-1** se muestra el layout con los tres niveles de máscara de un dispositivo de configuración en cruce, análogo al disponible en el conjunto de máscaras CNM733.

**Figura 2-1.** Layout de un dispositivo MIM de configuración en cruce.

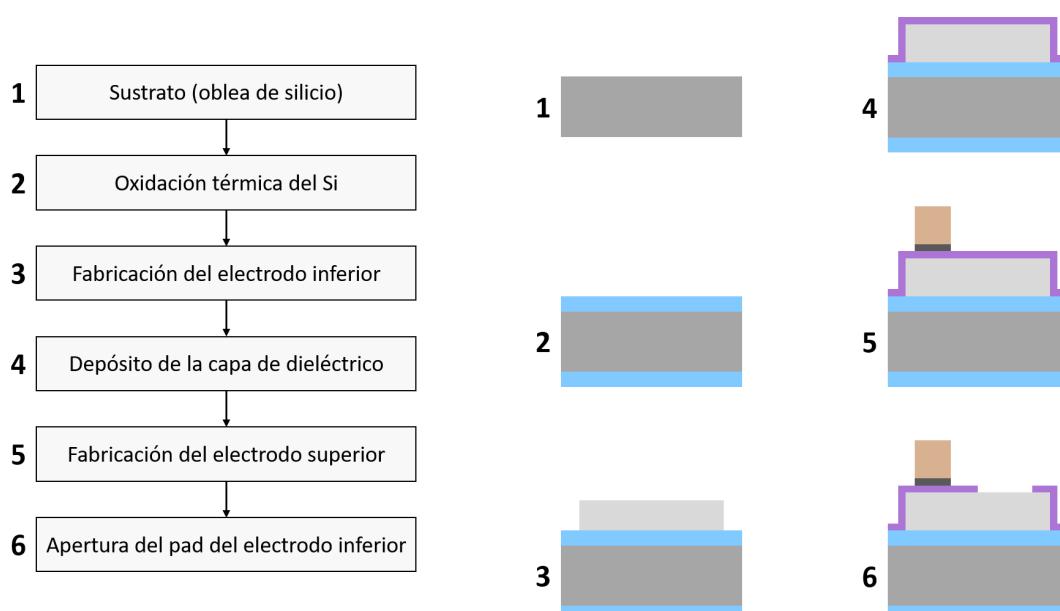

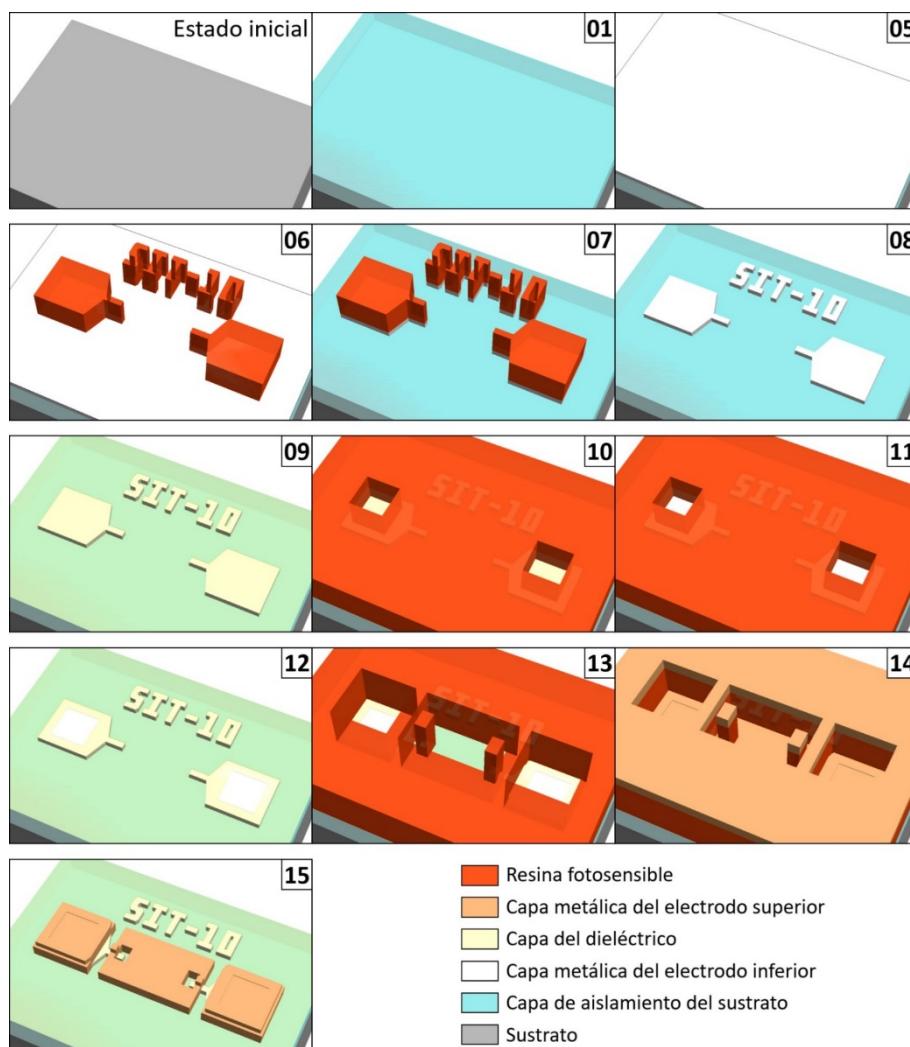

El diagrama de flujo del proceso de fabricación es el que se indica en la **Figura 2-2** junto con una representación esquemática del estado de la oblea después de cada módulo de proceso.

En base a los tres niveles de máscara, la fabricación de los dispositivos consistirá en la siguiente secuencia de etapas:

1. Crecimiento de una capa de óxido de aislamiento. Para aislar eléctricamente el dispositivo del silicio del substrato, se crece una capa de óxido mediante una etapa de oxidación térmica del silicio.

2. Deposición del metal del electrodo inferior. Mediante una etapa de deposición por sputtering se deposita una capa del metal que constituirá el electrodo inferior del dispositivo.

3. Fotolitografía con la máscara Nivel 1. Se definen los motivos en la fotoresina que se desean transferir al metal del electrodo inferior.

4. Grabado de metal. Se graba la capa de metal no protegida por la fotoresina.

5. Eliminación de la resina. En la superficie de la oblea quedan motivos de metal de acuerdo a los existentes en la máscara Nivel 1.

6. Deposición de la capa de aislante. Se deposita una capa delgada de material dieléctrico mediante la técnica Atomic Layer Deposition (ALD).

7. Deposición del metal del electrodo superior. Mediante una etapa de deposición por sputtering se deposita una capa del metal que constituirá el electrodo superior del dispositivo.

8. Fotolitografía con la máscara Nivel 2. Se definen los motivos en la fotoresina que se desean transferir al metal de electrodo superior.

9. Grabado de metal. Se graba la capa de metal no protegida por la fotoresina.

10. Eliminación de la fotoresina. En la superficie de la oblea quedarán ya definidos los motivos de metal de acuerdo a los existentes en la máscara Nivel 2.

11. Fotolitografía con la máscara Nivel 3. Se definen los motivos en la fotoresina que constituirán los pads de contacto al electrodo inferior, que está totalmente recubierto por la capa de dieléctrico.

**Figura 2-2.** Diagrama de flujo del proceso de fabricación, con una representación esquemática del estado de la oblea después de cada módulo de proceso.

12. Grabado de óxido. Se graba el óxido depositado por ALD en las áreas no protegidas por la fotoresina, que corresponden a los pads de contacto al electrodo inferior.

13. Eliminación de la resina. El dispositivo está terminado.

## 2.2 Fabricación de dispositivos con configuración en cruce

Siguiendo la tecnología descrita en el apartado anterior, se han fabricado dispositivos TiN/Ti/HfO<sub>2</sub>/W, es decir, estructuras MIM con W como electrodo inferior, HfO<sub>2</sub> como aislante y un apilamiento TiN sobre 10 nm de Ti, como electrodo superior.

Como ya se ha comentado, se han usado los niveles correspondientes del conjunto de máscaras CNM733 adecuados para la fabricación de estructuras MIM. Estos niveles son:

- L2, de campo claro, para la definición del electrodo inferior

- L3, de campo oscuro, para la definición del electrodo superior

- L4, de campo oscuro, para la apertura del pad de contacto al electrodo inferior.

Usando estos niveles de máscara, la fabricación de los dispositivos consiste en:

1. Crecimiento de una capa de óxido de silicio de 200 nm de espesor mediante un proceso de oxidación térmica del silicio a 1100 °C, de manera que la capa de óxido crece en ambas caras de la oblea.

2. Deposición por sputtering de una capa de W del espesor deseado.

3. Fotolitografía con la máscara L2 utilizando fotoresina positiva.

4. Grabado seco de la capa de W.

5. Eliminación de la resina.

6. Crecimiento de una capa de 10 nm de HfO<sub>2</sub> mediante la técnica Atomic Layer Deposition (ALD). Para ello se ha usado un equipo Savannah 200 de Cambridge Nanotech, a una temperatura de 225 °C y usando Tetrakis(dimetilamido)Hafnio (TDMAH) como precursor de hafnio, H<sub>2</sub>O como precursor de oxígeno, y N<sub>2</sub> como gas portador y de purga. El espesor nominal de la capa de HfO<sub>2</sub> es de 10 nm y en cada proceso de deposición realizado se ha ajustado el número de ciclos ALD para la obtención sobre una oblea testigo de una capa de dicho espesor, según medida por elipsometría usando un índice de refracción de n = 2.07.

7. Deposición por sputtering de una capa de 10 nm de Ti.

8. Deposición por sputtering de una capa de TiN del espesor deseado.

9. Fotolitografía con la máscara L3 utilizando fotoresina negativa.

10. Grabado seco del apilamiento de metal formado por la capa de TiN sobre 10 nm de Ti.

11. Eliminación de la fotoresina.

12. Fotolitografía con la máscara L4 utilizando fotoresina positiva.

13. Grabado seco de la capa de HfO<sub>2</sub>

14. Eliminación de la resina.

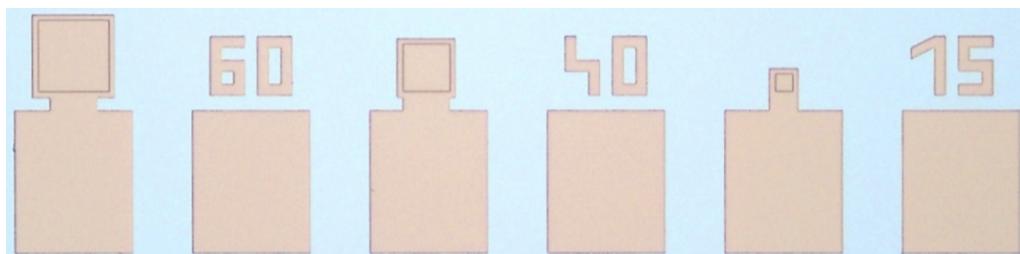

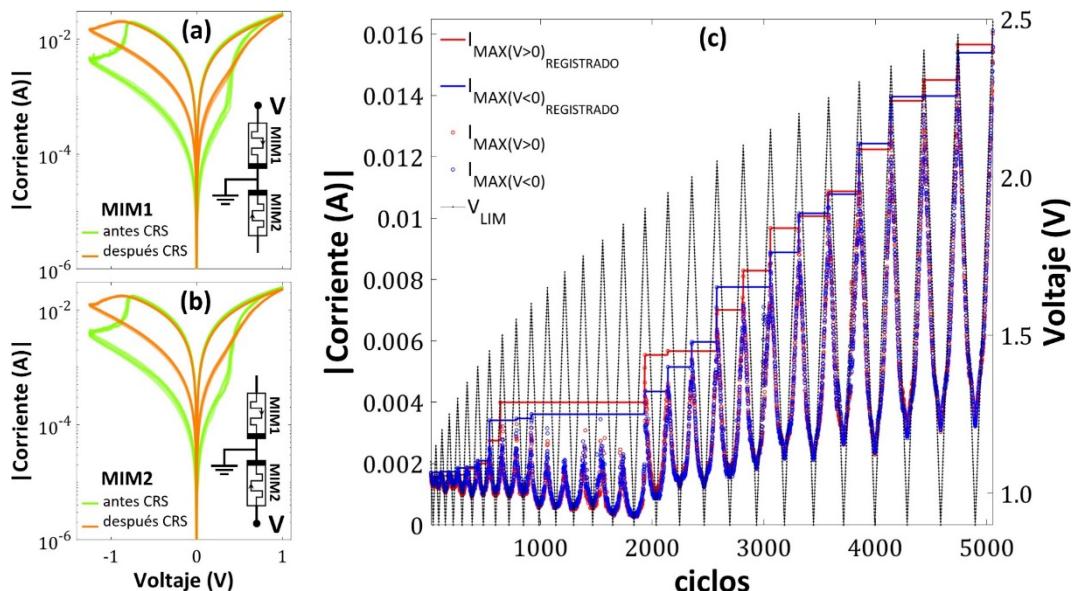

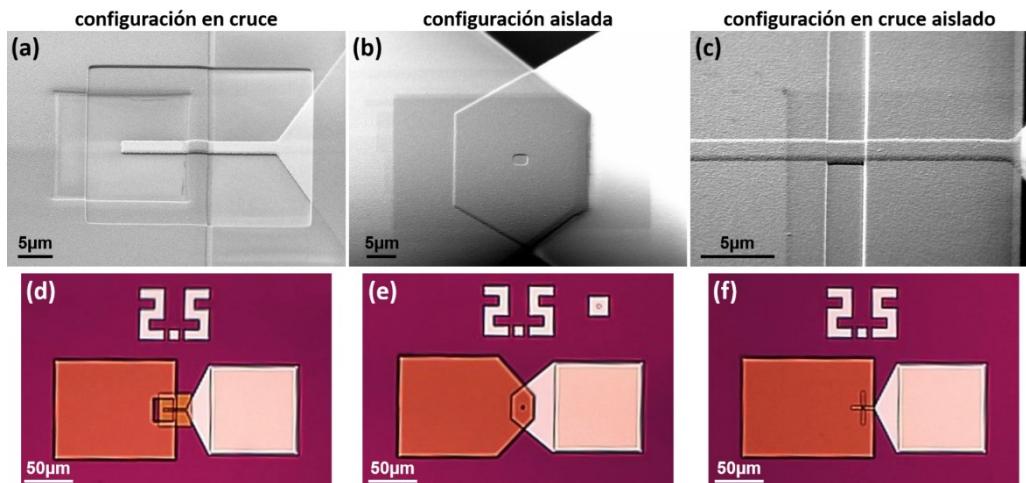

En la **Figura 2-3** se muestra una imagen tomada al microscopio óptico del conjunto de estructuras MIM de distintas áreas que se fabrican mediante el conjunto de máscaras CNM733, con valores que van de  $2 \times 2 \mu\text{m}^2$  hasta  $100 \times 100 \mu\text{m}^2$ .

**Figura 2-3.** Imagen óptica de una fila de dispositivos TiN/Ti/HfO<sub>2</sub>/W de varios tamaños.

Los resultados que se presentan en esta tesis doctoral en estructuras en cruce corresponden a dos obleas con espesores distintos de las capas de metal como se indica en la **Tabla I**. La motivación para disponer de estructuras con espesores de metal distinto se debe a que las características eléctricas de las capas de metal pueden afectar las prestaciones de los dispositivos de conmutación resistiva, a través de la resistencia serie que las líneas de metal aportan [74].

| #Oblea        | W (nm) | HfO <sub>2</sub> (nm) | Ti (nm) | TiN (nm) |

|---------------|--------|-----------------------|---------|----------|

| <b>8356-2</b> | 200    | 10                    | 10      | 200      |

| <b>9512-3</b> | 300    | 10                    | 10      | 300      |

**Tabla I.** Espesores de las capas de las estructuras MIM.

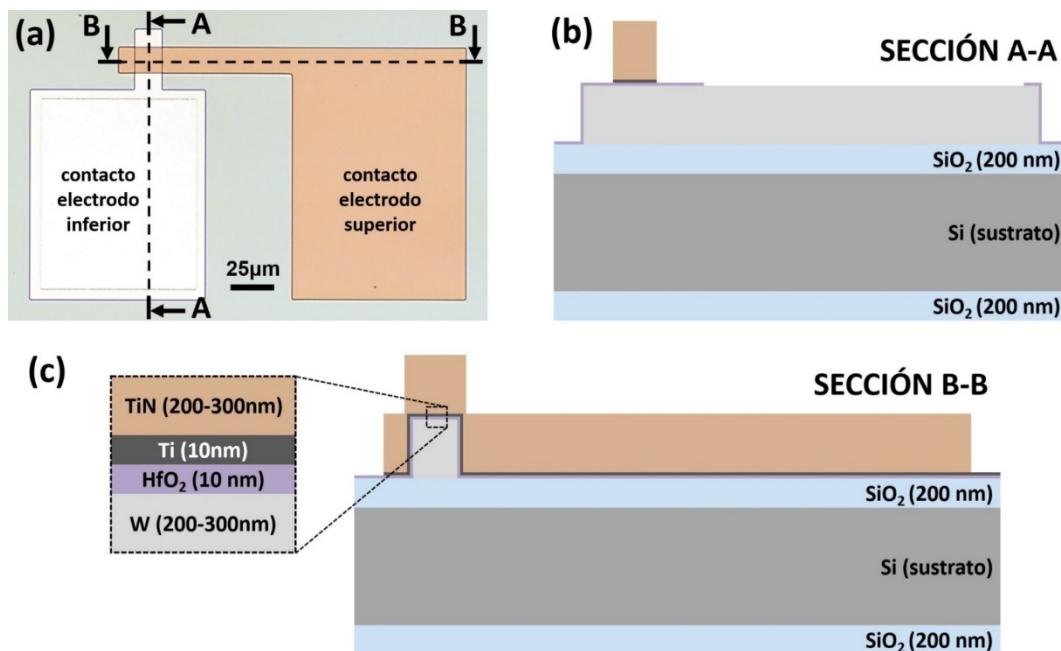

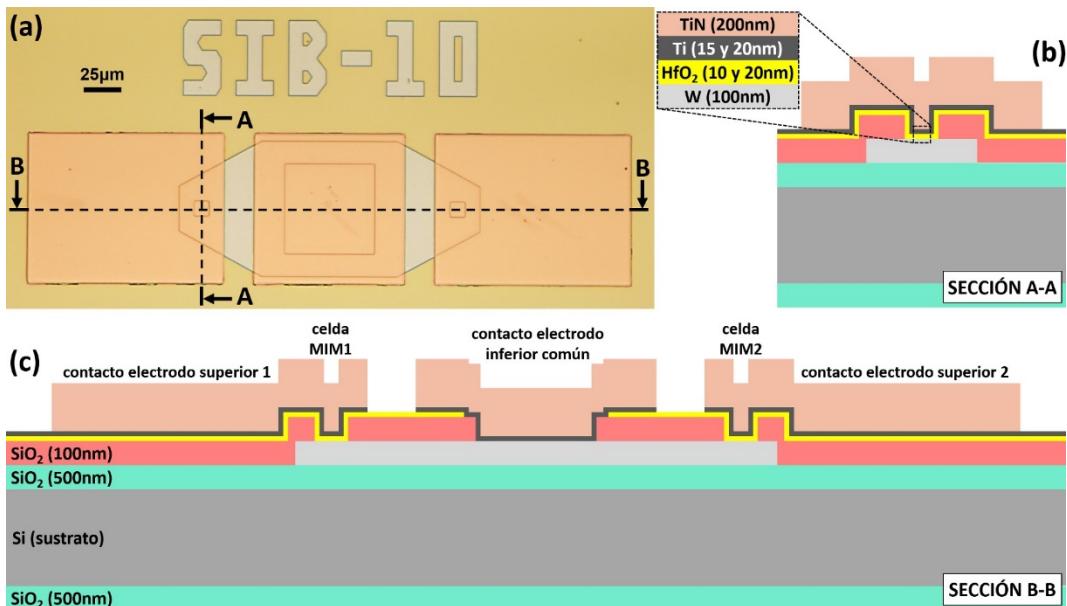

En la **Figura 2-4** se muestra un dispositivo fabricado con este tipo de configuración y un tamaño de área activa de  $15 \times 15 \mu\text{m}^2$  con las correspondientes representaciones esquemáticas de las secciones A-A y B-B.

**Figura 2-4.** (a) Imagen óptica de un dispositivo TiN/Ti/HfO<sub>2</sub>/W de configuración cross-point y una área activa de  $15 \times 15 \mu\text{m}^2$ . Las secciones del electrodo inferior / superior a nivel de la celda MIM, indicadas respectivamente por los planos de corte A-A / B-B, están representadas en (b) y (c). Adicionalmente en (c) se indica los espesores en los que se han fabricado los dispositivos caracterizados y medidos.

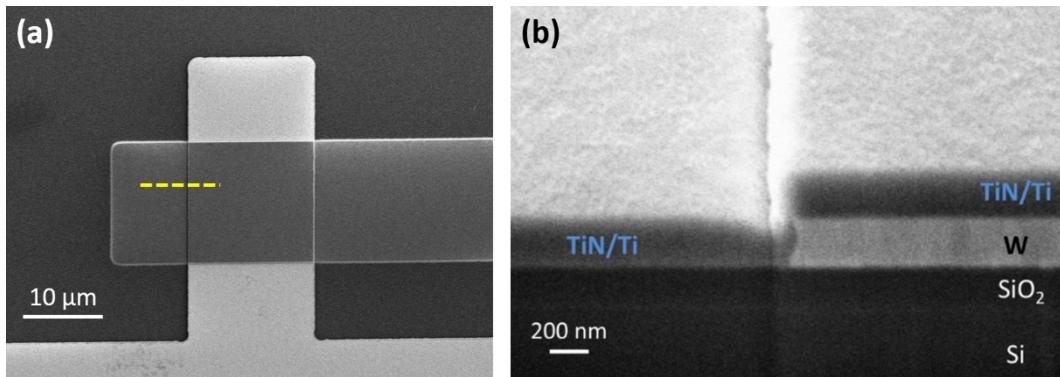

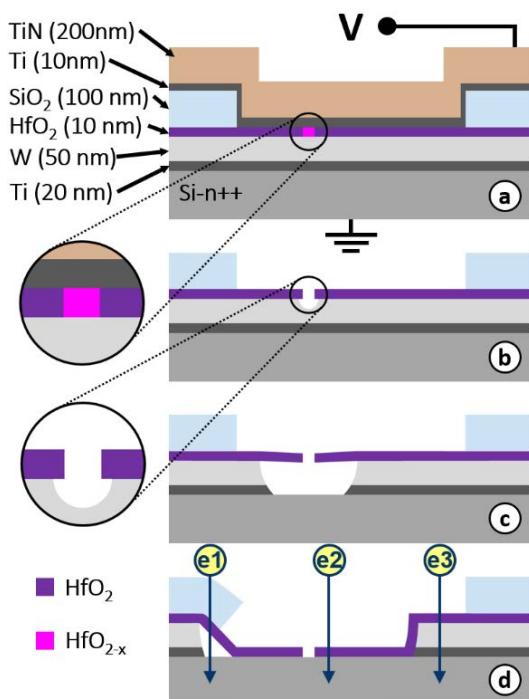

En la **Figura 2-5** se muestra la imagen de una estructura  $15 \times 15 \mu\text{m}^2$  tomada mediante microscopía electrónica de barrido (SEM) de una vista superior (a) y de un corte transversal realizado mediante FIB (Focused Ion Beam) (b), para el caso de una estructura con metales de espesor nominal de 200 nm. Dado el bajo espesor de la capa de HfO<sub>2</sub>, esta no se aprecia en una imagen SEM. En la **Figura 2-5b** se aprecia claramente la no conformidad del depósito del metal, con un espesor menor en la pared vertical, por lo que este será un punto débil en el funcionamiento eléctrico del dispositivo, de manera que al pasar una corriente eléctrica se puede provocar la fusión del metal en estos puntos débiles, por efecto Joule. En la misma figura se observa también cómo el grabado seco de la capa de W, que constituye el electrodo inferior, presenta una pared no vertical sino cóncava por lo que, si este efecto pudiera representar un punto débil, sería preciso modificar el proceso de grabado para paliarlo.

**Figura 2-5.** (a) Imagen SEM de la vista superior de un dispositivo TiN/Ti/HfO<sub>2</sub>/W de configuración cross-point, área activa de 15×15 μm<sup>2</sup> y metales con espesores de 200 nm. (b) Imagen SEM de un corte FIB de la estructura de (a) en la zona indicada con la línea discontinua.

Una vez terminado el proceso de fabricación, para estudiar las características de las líneas de metal, se han utilizado las estructuras CBR de test de las líneas de metal de anchura nominal de 2 y 5 μm, incluidas en cada chip del conjunto de máscaras CNM733 [73]. La medida de las características eléctricas de las estructuras CBR nos ha permitido obtener la resistencia por cuadro ( $R_{cuadro}$ ) de cada metal, así como la anchura eléctrica efectiva de las líneas de las estructuras de test.

Los resultados obtenidos para el caso del W, usado como electrodo inferior en la estructura MIM, incluyendo valor medio y desviación estándar sobre un conjunto de 99 chips, se indican en la **Tabla II**.

| W      | CBR – 2 μm |                     | CBR – 5 μm   |                     |              |

|--------|------------|---------------------|--------------|---------------------|--------------|

|        | #Oblea     | $R_{cuadro}$ (Ω/sq) | Anchura (μm) | $R_{cuadro}$ (Ω/sq) | Anchura (μm) |

| 8356-2 |            | 1.29 ± 0.16         | 2.37 ± 0.16  | 1.32 ± 0.16         | 5.48 ± 0.17  |

| 9512-3 |            | 1.01 ± 0.17         | 2.46 ± 0.22  | 1.04 ± 0.20         | 5.59 ± 0.24  |

**TABLA II.** Características de las líneas de metal de W medidas en las estructuras de test CBR.

Los resultados obtenidos para las dos obleas indican una buena repetitividad del proceso y una buena uniformidad de características en oblea. Además, al aumentar el espesor de la capa de metal, efectivamente el valor de  $R_{cuadro}$  disminuye, aunque ligeramente menos de lo esperado. La menor diferencia entre resistencias asociadas a los metales con respecto a lo esperado puede dar lugar a un efecto menos relevante en las características de conmutación resistiva de los dispositivos. A pesar de ello, sí representará una mejora un

aumento del espesor en términos de fiabilidad, pues la densidad de corriente será menor y las líneas de metal podrán soportar mayores corrientes sin ser degradadas por efecto Joule.

En cuanto al apilamiento de TiN sobre una capa de 10 nm de Ti, los resultados obtenidos se indican en la **Tabla III** junto con los de las líneas de W para la misma oblea.

| 9512-3 | CBR – 2 μm  |                            | CBR – 5 μm   |                            |

|--------|-------------|----------------------------|--------------|----------------------------|

|        | Metal       | R <sub>cuarto</sub> (Ω/sq) | Anchura (μm) | R <sub>cuarto</sub> (Ω/sq) |

| W      | 1.01 ± 0.17 | 2.46 ± 0.22                | 1.04 ± 0.20  | 5.59 ± 0.24                |

| TiN/Ti | 4.16 ± 0.53 | 1.39 ± 0.20                | 4.16 ± 0.44  | 4.38 ± 0.50                |

**TABLA III.** Características de las líneas de metal de W y TiN medidas en las estructuras de test CBR.

Como se observa en la **Tabla III**, el electrodo superior constituido por el apilamiento TiN/Ti es más resistivo que el inferior y, además, el proceso de definición de la anchura de líneas ha dado lugar a líneas más estrechas que las nominales. Este hecho tiene dos consecuencias: por un lado, el área activa de las estructuras será inferior al nominal y, por otro lado, la resistencia serie que el electrodo superior introducirá en el funcionamiento de las estructuras será mayor que el teóricamente previsto. Hay que señalar que este resultado se añade al hecho de que, por el diseño de las estructuras, el número de cuadros de metal del electrodo inferior es menor que el del electrodo superior [75]. Así, en el caso de las estructuras MIM de  $5 \times 5 \mu\text{m}^2$ , el número de cuadros de W es de 7.2, mientras que el número de cuadros de TiN/Ti es de 16.2, por lo que la resistencia serie sería de aproximadamente 75 Ω.

## 2.3 Tecnología de fabricación de dispositivos aislados

La tecnología para la fabricación de dispositivos en cruce descrita en los apartados anteriores utiliza tres niveles de máscara y etapas de grabado seco para la estructuración de las capas de metal que constituyen los electrodos inferior y superior de las estructuras MIM. Con el fin de ensayar una alternativa tecnológica que no necesite del grabado de capas de metal, y en la que las áreas de los dispositivos estén determinadas por una sola etapa de grabado, hemos propuesto la siguiente tecnología que permite la fabricación de

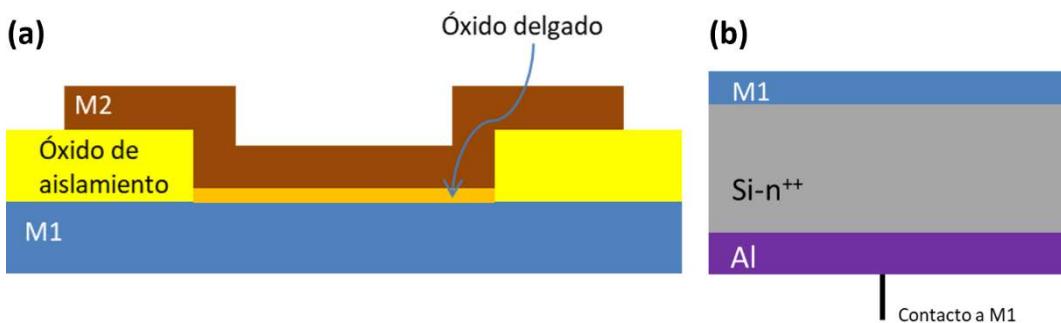

dispositivos a los que llamamos de configuración aislada. La propuesta consiste en utilizar una capa de óxido de aislamiento sobre el metal del electrodo inferior del dispositivo. En esta capa de óxido se definen unas aperturas que constituirán las áreas activas de los dispositivos MIM, como se indica en la **Figura 2-6a**, y, por tanto, el área estará determinada por una única etapa de grabado. Además, la opción de la definición de celdas MIM por un cruce de pistas metálicas adolece de un inconveniente, como se ha podido observar (**Figura 2-5b**), que es el estrechamiento que se produce en la pista metálica del electrodo superior al cubrir el escalón en el cruce con la pista metálica inferior por la no conformidad del depósito del metal. Adicionalmente, si el proceso de fabricación generara irregularidades en el borde de la pista del metal inferior, la estructura en cruce presentaría puntos débiles. La opción tecnológica mediante la definición por una apertura en una capa de aislamiento mejora también este problema.

**Figura 2-6.** (a) Vista transversal esquemática de una estructura MIM de configuración aislada. (b) Contacto eléctrico al electrodo inferior a través de la cara posterior de la oblea.

Como se observa en la vista transversal, esta propuesta sería análoga a la utilizada para la fabricación de estructuras MIS, con la diferencia de que en nuestro caso necesitamos definir una estructura MIM, es decir, el óxido delgado debe estar sobre un metal. Para ello, depositaremos la capa de metal del electrodo inferior (M1 en la **Figura 2-6**) sobre toda la superficie de una oblea de silicio que sea muy poco resistiva, es decir, que esté altamente dopada. Y así, mediante una metalización de la cara posterior de la oblea podremos contactar eléctricamente con el metal M1, como se muestra en la **Figura 2-6b**.

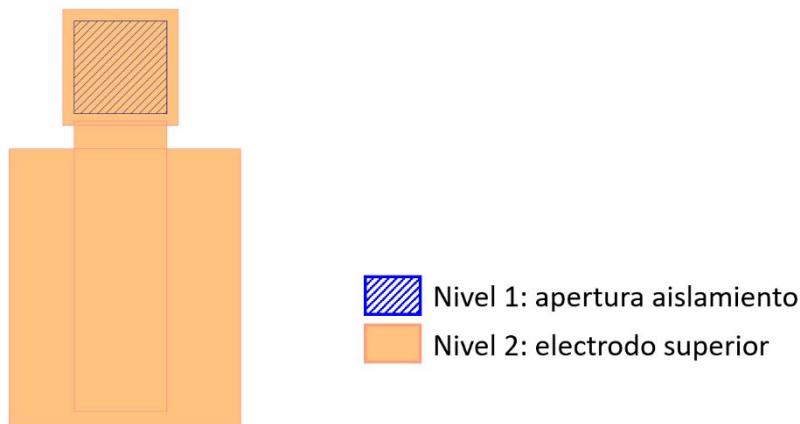

Bajo estas condiciones, para la fabricación de una estructura MIM aislada, serán necesarios dos niveles de máscara:

- Nivel 1. Define la apertura del óxido de aislamiento que será el área activa del dispositivo.

- Nivel 2. Define el electrodo superior de los dispositivos.

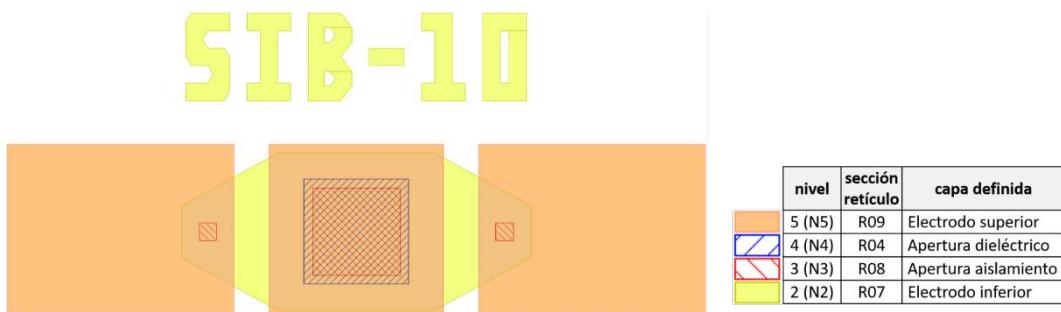

En la **Figura 2-7** se muestra el layout con los dos niveles de máscara de un dispositivo de configuración aislada, análogo al disponible en el conjunto de máscaras CNM733 para la fabricación de estructuras MIS.

**Figura 2-7.** Layout de un dispositivo MIM de configuración aislada.

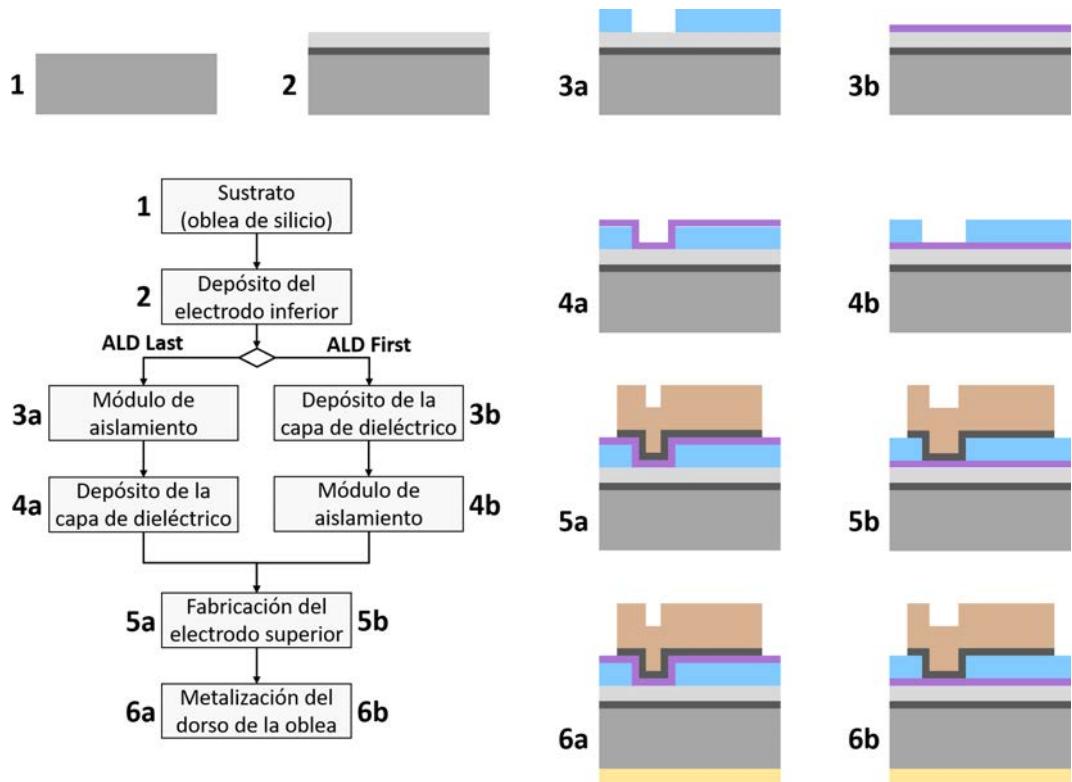

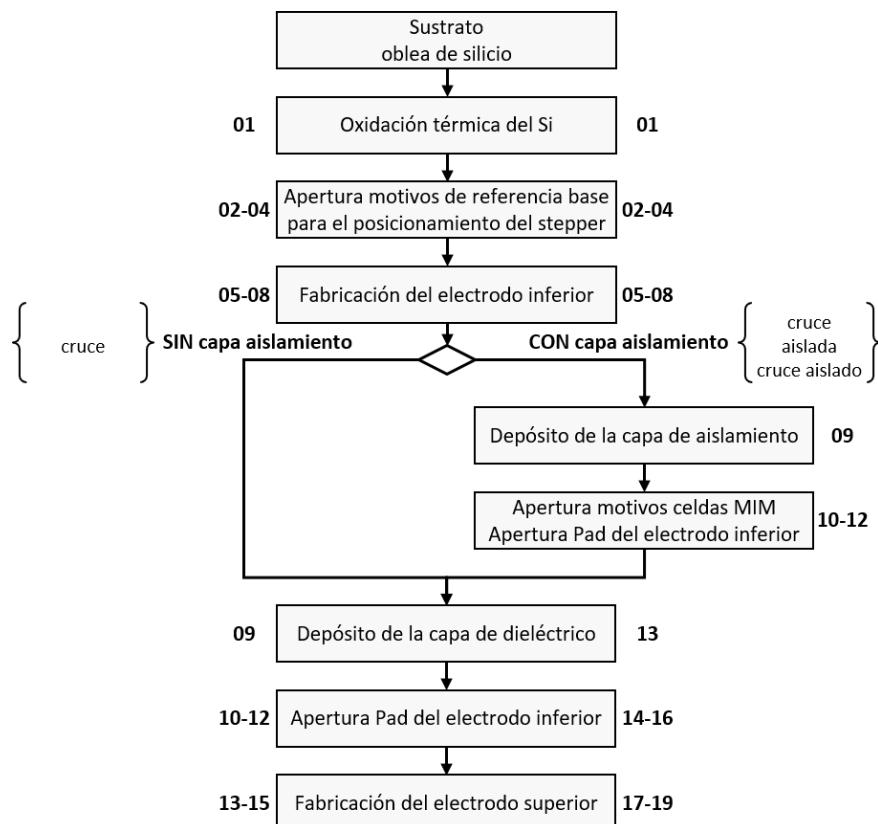

El diagrama de flujo del proceso de fabricación para esta propuesta es el que se indica en la **Figura 2-8** junto con una representación esquemática del estado de la oblea después de cada módulo de proceso. Como vemos, existen dos posibilidades según la etapa de deposición de la capa delgada de aislante de la estructura MIM se realice antes (ALD First) o después (ALD Last) del módulo de proceso del óxido de aislamiento. Aunque en ambos casos la celda MIM activa es la misma, las etapas tecnológicas que constituyen el módulo de proceso del aislamiento serán distintas, como se detallará en la sección 2.4.

**Figura 2-8.** Diagrama de flujo del proceso de fabricación de dispositivos MIM de configuración aislada, con una representación esquemática del estado de la oblea después de cada módulo de proceso.

## 2.4 Fabricación de dispositivos con configuración aislada

Para la evaluación de la tecnología propuesta, se han empleado los niveles del conjunto de máscaras CNM733 diseñados para la fabricación de estructuras MIS, es decir:

- L1, de campo oscuro, para la apertura del óxido de aislamiento.

- L2, de campo claro, para la definición del electrodo superior.

En base a estas máscaras, el proceso de fabricación de dispositivos TiN/Ti/HfO<sub>2</sub>/W de configuración aislada consiste en las siguientes etapas:

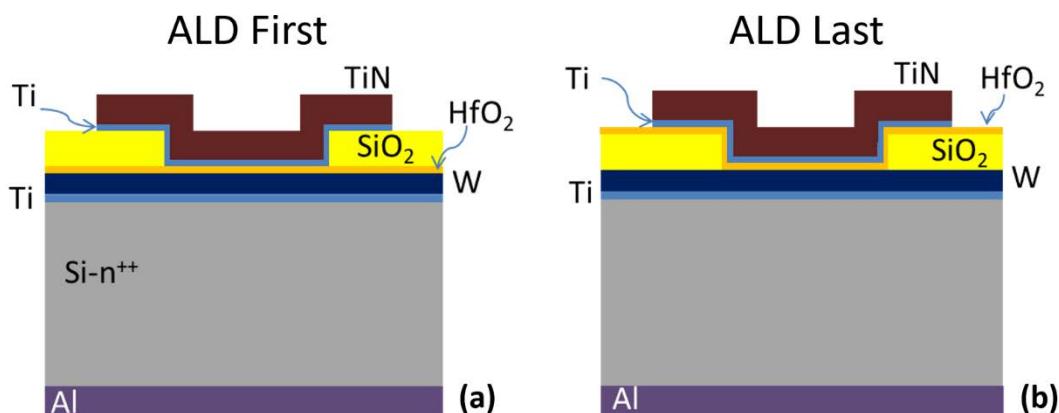

1. Depósito del electrodo inferior sobre toda la superficie de una oblea de silicio de 100 mm de diámetro, de 275 µm de espesor y con una resistividad de 0.1 Ω·cm. Para favorecer la adherencia del metal del electrodo inferior, W, se ha depositado en primer lugar una capa de 20 nm de Ti y posteriormente una capa de 50 nm de W, en ambos casos mediante sputtering. Hay que señalar que el espesor de la capa de W ha tenido que ser limitado para evitar la fractura de la capa por tensiones mecánicas.

En función de en qué momento del procesado se deposite la capa delgada de dieléctrico, el proceso seguirá las etapas que se describen a continuación:

#### **Opción ALD First**

2. Crecimiento de una capa de 10 nm de HfO<sub>2</sub> mediante ALD, en un equipo Savannah 200 de Cambridge Nanotech, a T = 225 °C y usando Tetrakis(dimetilamido)Hafnio (TDMAH) como precursor de hafnio, H<sub>2</sub>O como precursor de oxígeno, y N<sub>2</sub> como gas portador y de purga. El espesor nominal de la capa de HfO<sub>2</sub> es de 10 nm y en cada proceso de deposición realizado se ha ajustado el número de ciclos ALD para la obtención sobre una oblea testigo de una capa de dicho espesor, según medida por elipsometría usando un índice de refracción de n = 2.07.

3. Deposición de una capa de 100 nm de SiO<sub>2</sub> mediante PECVD (Plasma Enhanced Chemical Vapor Deposition) utilizando SiH<sub>4</sub> y O<sub>2</sub> como precursores.

4. Fotolitografía con la máscara L1 usando fotoresina positiva.

5. Grabado húmedo de la capa de óxido PECVD. El grabado progresará hasta llegar a la capa de HfO<sub>2</sub>, momento en el que la velocidad de grabado vertical se reduce drásticamente, al ser el HfO<sub>2</sub> muy resistente a las soluciones grabadoras de SiO<sub>2</sub>. Hay que señalar que es importante la total eliminación del óxido de aislamiento puesto que, en caso contrario, el dieléctrico de la estructura MIM sería una bicapa de HfO<sub>2</sub> y SiO<sub>2</sub> con lo que las características de conmutación resistiva podrían quedar comprometidas.

6. Eliminación de la resina.

#### **Opción ALD Last**

2. Deposición de una capa de 100 nm de SiO<sub>2</sub> mediante PECVD utilizando SiH<sub>4</sub> y O<sub>2</sub> como precursores.

3. Fotolitografía con la máscara L1 usando fotoresina positiva.

4. Grabado seco de la capa de óxido PECVD. El grabado progresará hasta llegar a la capa de W. Análogamente a la opción ALD First, es importante la total eliminación del óxido de aislamiento puesto que, en caso contrario, el dieléctrico de la estructura MIM sería una bicapa de HfO<sub>2</sub> y SiO<sub>2</sub> con lo que las características de conmutación resistiva podrían quedar comprometidas.

5. Eliminación de la resina.

6. Crecimiento de una capa de 10 nm de  $\text{HfO}_2$  mediante ALD, en un equipo Savannah 200 de Cambridge Nanotech, a  $T = 225^\circ\text{C}$  y usando Tetrakis(dimetilamido)Hafnio (TDMAH) como precursor de hafnio,  $\text{H}_2\text{O}$  como precursor de oxígeno, y  $\text{N}_2$  como gas portador y de purga. El espesor nominal de la capa de  $\text{HfO}_2$  es de 10 nm y en cada proceso de deposición realizado se ha ajustado el número de ciclos ALD para la obtención sobre una oblea testigo de una capa de dicho espesor, según medida por elipsometría usando un índice de refracción de  $n = 2.07$ .

A partir de este punto, la secuencia es la misma para las dos opciones y consiste en la estructuración del metal de electrodo superior mediante la técnica de lift-off, es decir,

7. Fotolitografía con la máscara L2 usando fotoresina negativa.

8. Deposición por sputtering de una capa de 10 nm de Ti.

9. Deposición por sputtering de una capa de TiN de 200 nm de espesor.

10. Eliminación de la resina y, por tanto, estructuración del metal por lift-off.

11. Metalización del dorso de la oblea mediante sputtering con una capa de 500 nm de Al.

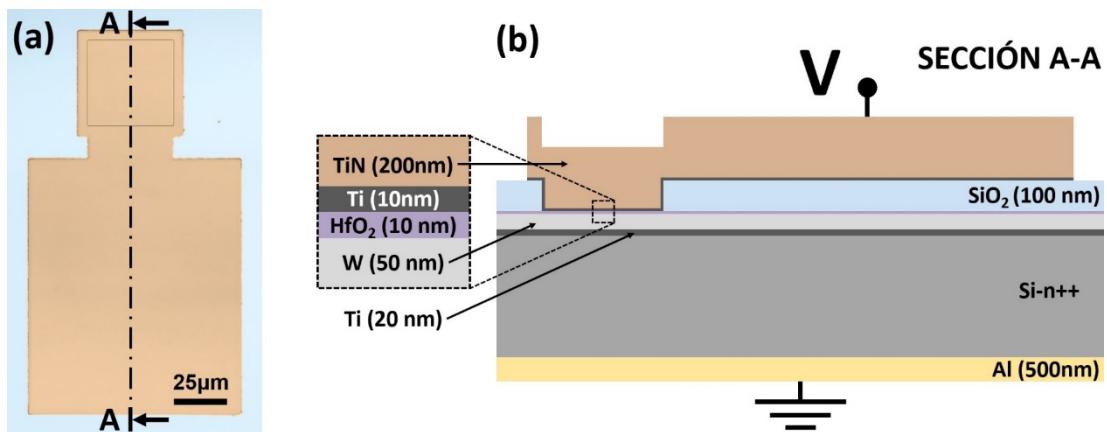

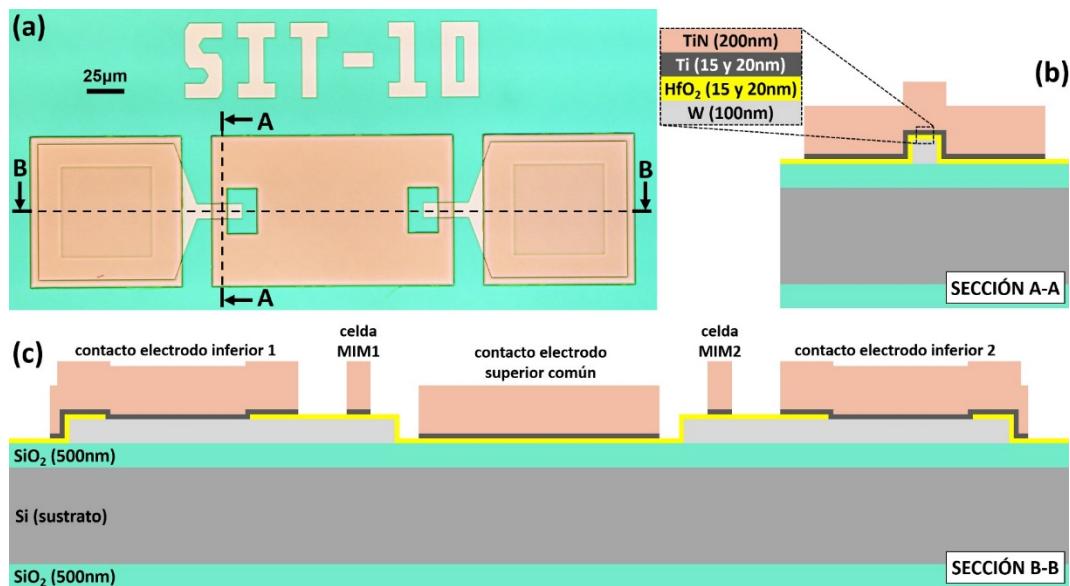

Una vista transversal esquemática de las estructuras TiN/Ti/ $\text{HfO}_2$ /W resultantes de las opciones ALD First y ALD Last se muestra en la **Figura 2-9**.

**Figura 2-9.** Vista transversal esquemática de las estructuras MIM de configuración aislada siguiendo la opción tecnológica (a) ALD First o (b) ALD Last.

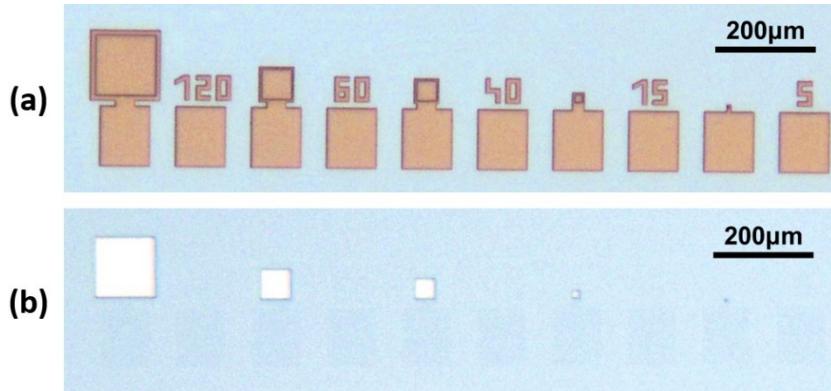

Siguiendo esta tecnología, se han fabricado distintas obleas (ver **Tabla IV**) utilizando los niveles del conjunto de máscaras CNM733 para estructuras MIS, con áreas activas de

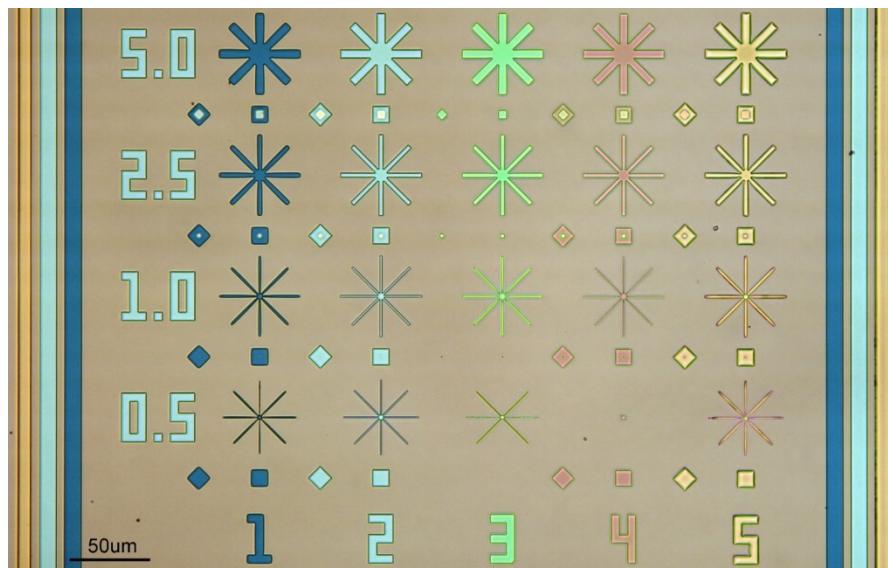

geometría cuadrada y cuyas dimensiones van desde 120×120 μm<sup>2</sup> hasta 1×1 μm<sup>2</sup>. En la **Figura 2-10** se muestra una fotografía tomada a través de un microscopio óptico de un subconjunto de dispositivos de distinta área.

**Figura 2-10.** Imagen óptica de una fila de dispositivos de configuración aislada de varios tamaños.

Las obleas que se han fabricado siguiendo esta tecnología y de cuyos dispositivos se presentan las características de conmutación resistiva en esta tesis, son las que se indican en la **Tabla IV**. En ella se incluye el número de ciclos ALD empleado para el crecimiento de una capa de 10 nm de HfO<sub>2</sub> de acuerdo con la determinación previa de la cinética de deposición sobre una oblea de test. Como se indica, la uniformidad de espesor en oblea es notable, por lo que la variabilidad de dispositivo a dispositivo en oblea del fenómeno de conmutación resistiva no podrá ser atribuida a un espesor de óxido distinto sino a la propia estocasticidad del fenómeno de la conmutación resistiva.

| #Oblea         | Tecnología | # ciclos ALD | HfO <sub>2</sub> (nm) |

|----------------|------------|--------------|-----------------------|

| <b>10050-1</b> | ALD first  | 104          | 9.9 ± 0.1             |

| <b>10132-1</b> | ALD last   | 104          | 9.9 ± 0.1             |

| <b>10371-1</b> | ALD first  | 97           | 9.7 ± 0.2             |

**Tabla IV.** Características de las obleas con dispositivos de configuración aislada.

En la **Figura 2-11** se muestra una fotografía de un dispositivo fabricado con la opción ALD First junto con una representación esquemática de la sección AA.

**Figura 2-11.** (a) Imagen de microscopía óptica de un dispositivo TiN/Ti/HfO<sub>2</sub>/W de configuración aislada y un área activa de 40×40 μm<sup>2</sup>. (b) Representación de la sección longitudinal del dispositivo en (a) indicado por el plano de corte A-A.

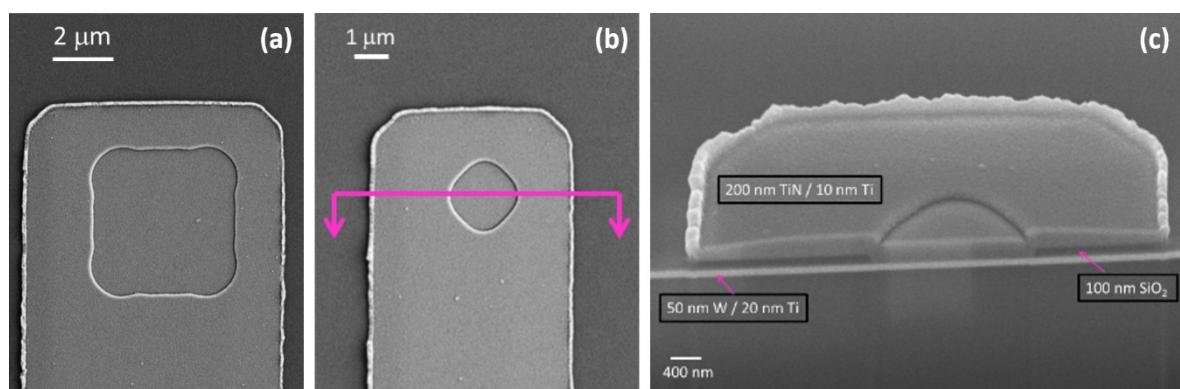

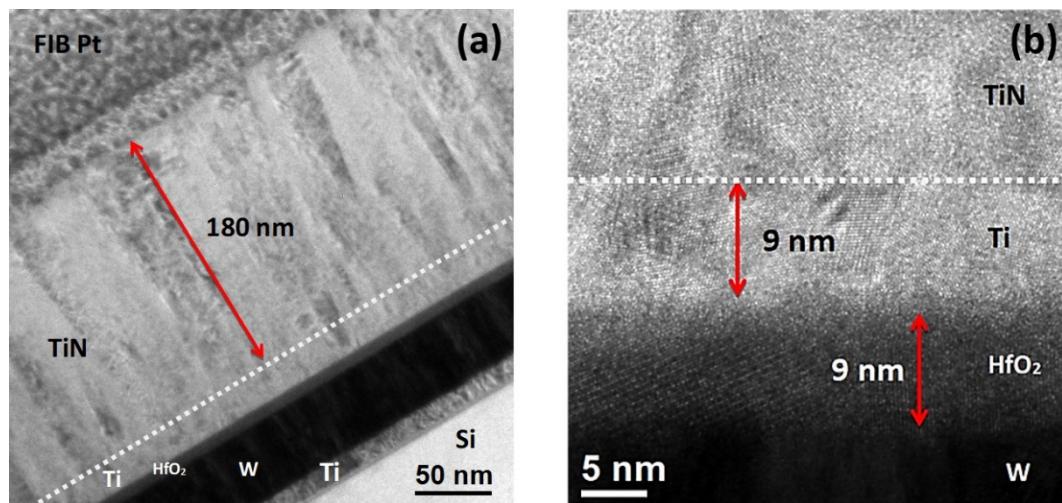

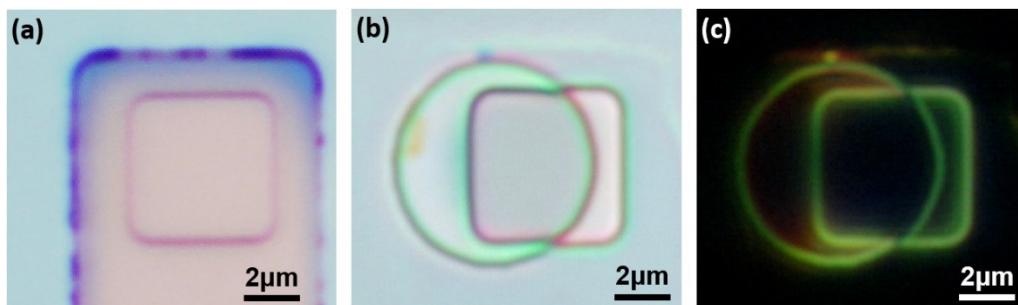

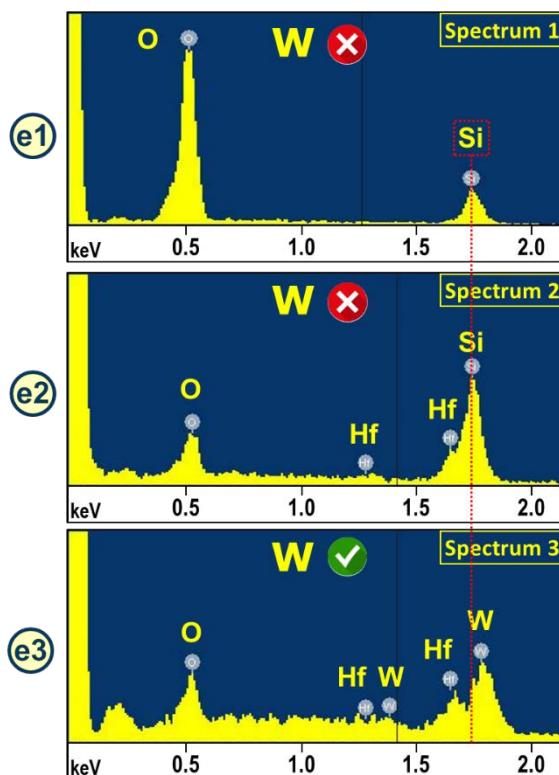

Los resultados de la inspección SEM de los dispositivos de configuración aislada se muestran en la **Figura 2-12**, para el caso de dispositivos en tecnología ALD First, en los que la apertura del óxido de aislamiento se ha realizado mediante grabado húmedo. Como se observa, las dimensiones en máscara quedan bien replicadas para estructuras de áreas mayores que 2×2 μm<sup>2</sup>, pero para las de estas dimensiones hay una pérdida significativa de dimensiones, por no haberse abierto completamente el motivo definido en la etapa fotolitográfica.

**Figura 2-12.** (a) Imagen SEM de la vista superior de una estructura de área activa en máscara de 5×5 μm<sup>2</sup> y (b) de 2×2 μm<sup>2</sup>, de la oblea 10371-1. (c) Imagen SEM del corte realizado por FIB en la zona indicada en (b).

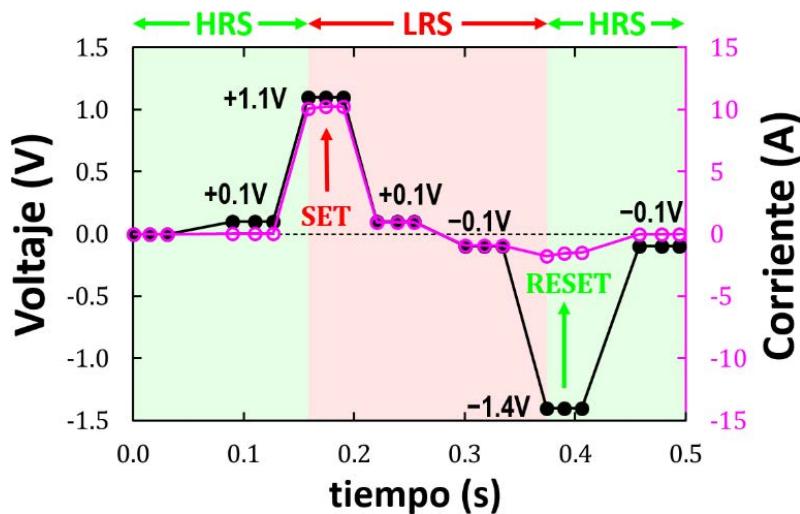

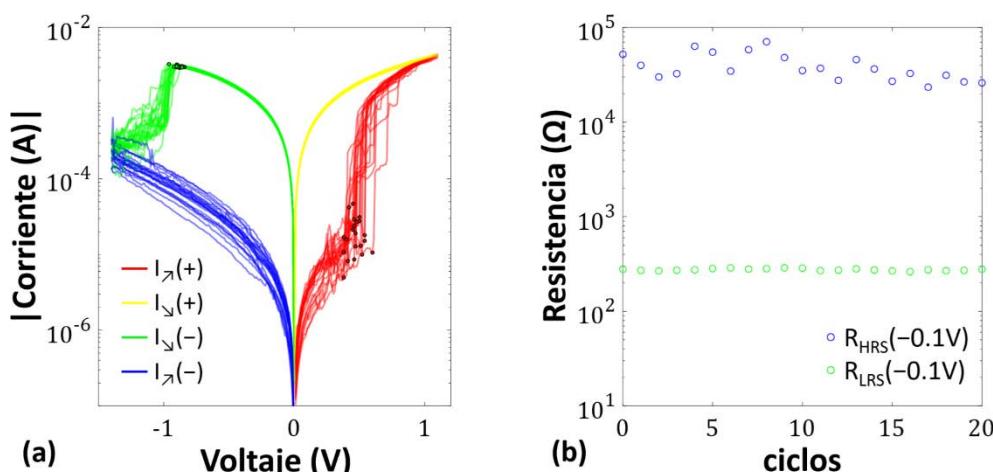

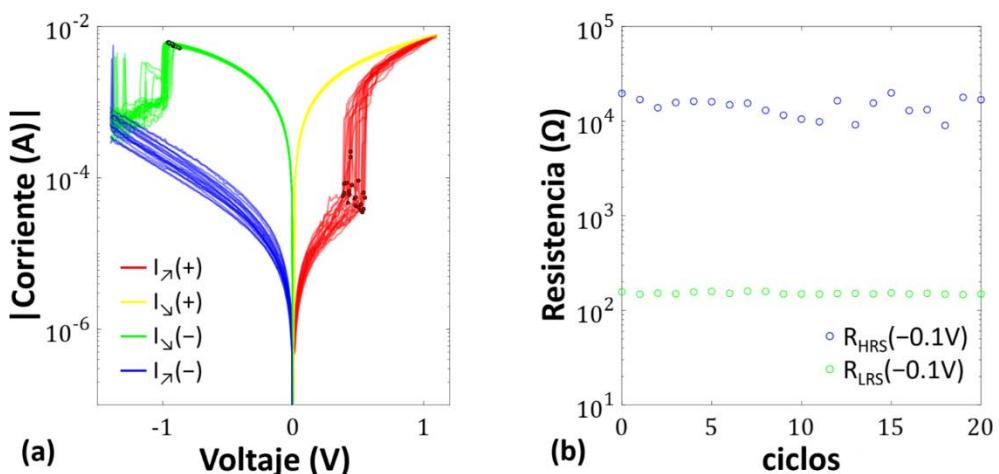

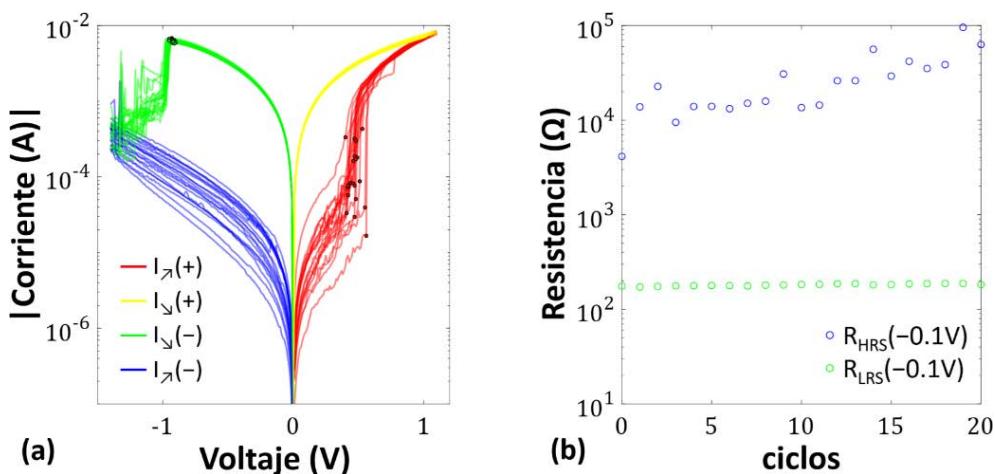

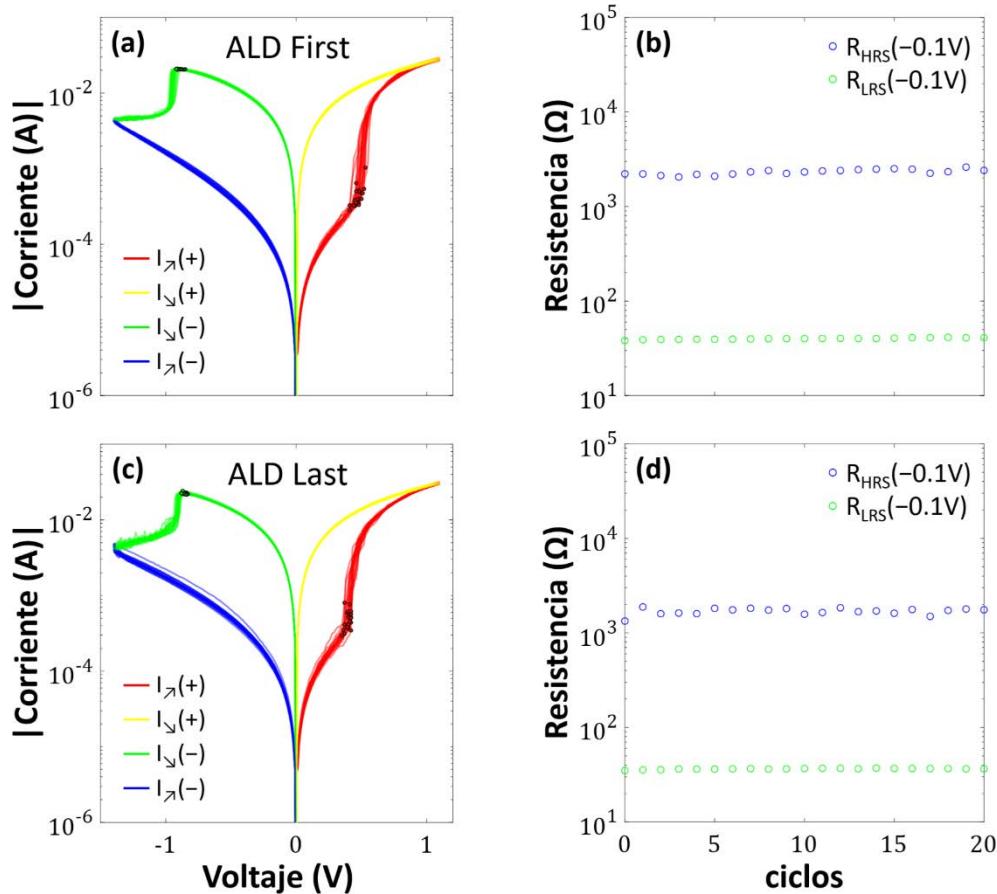

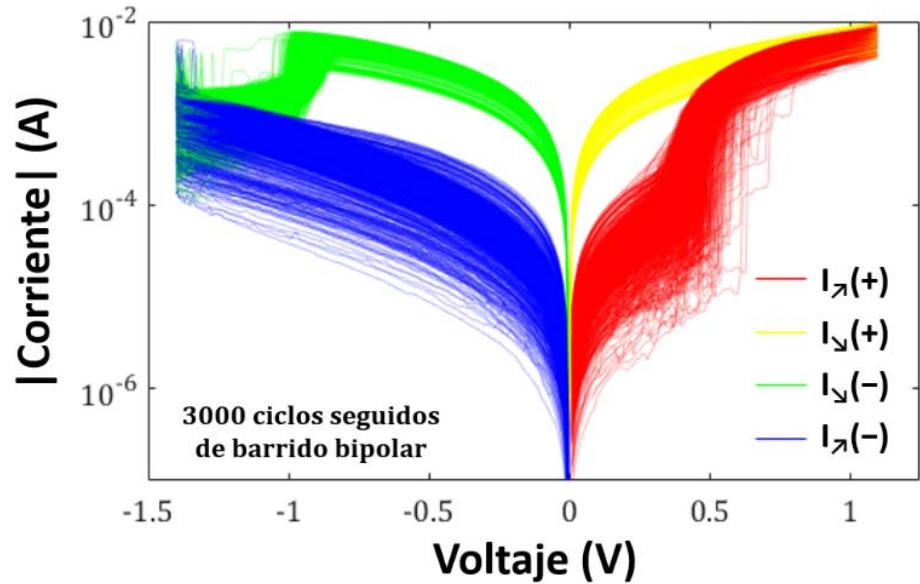

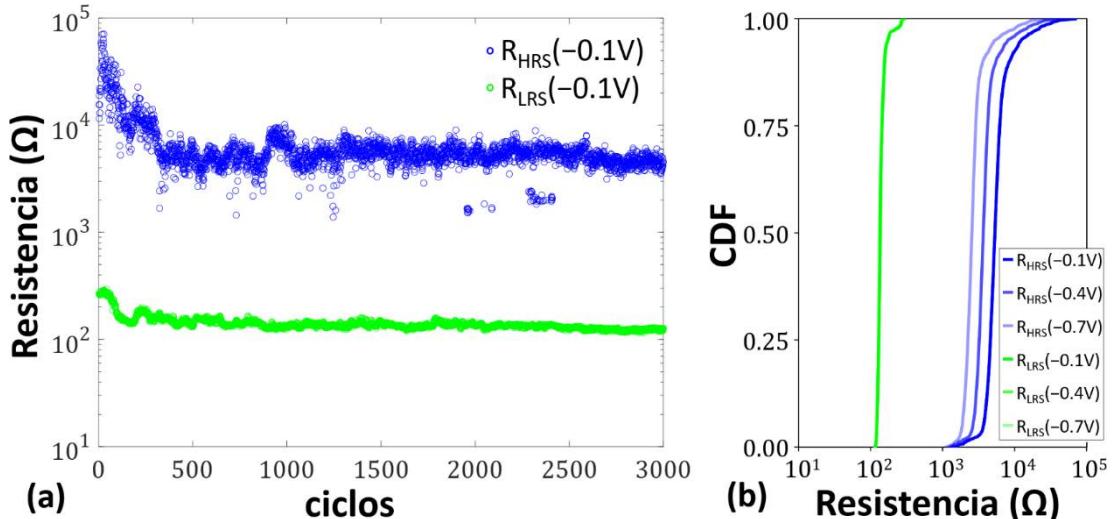

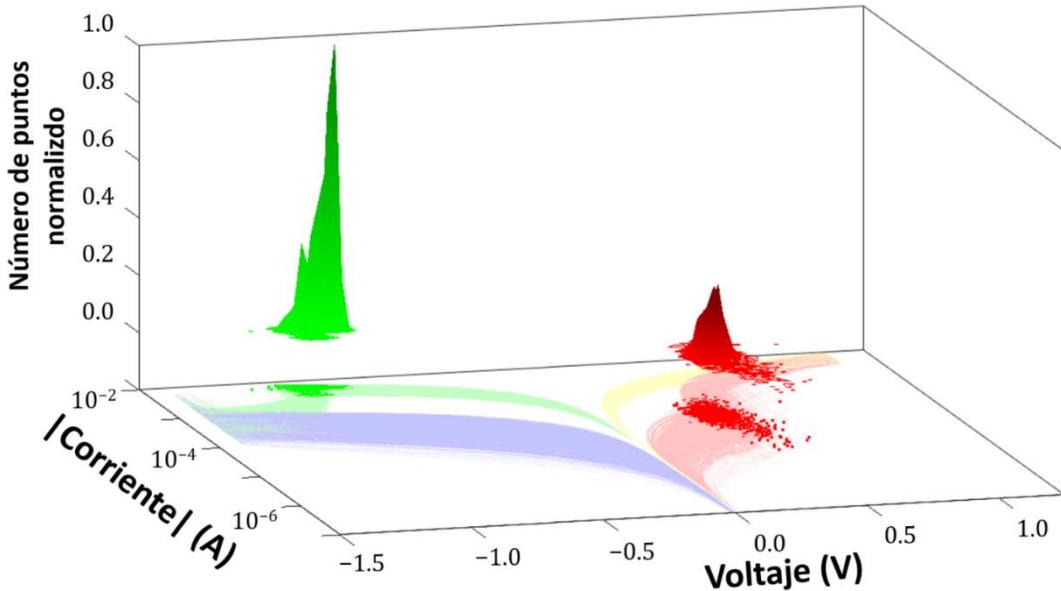

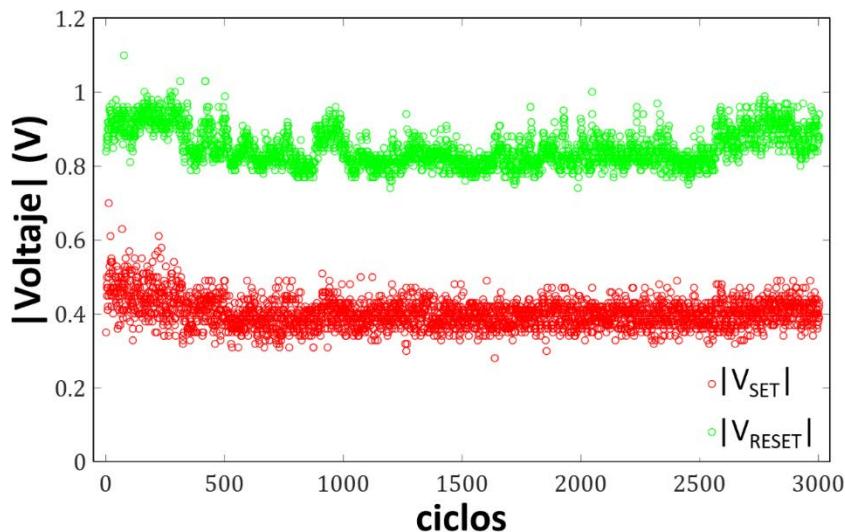

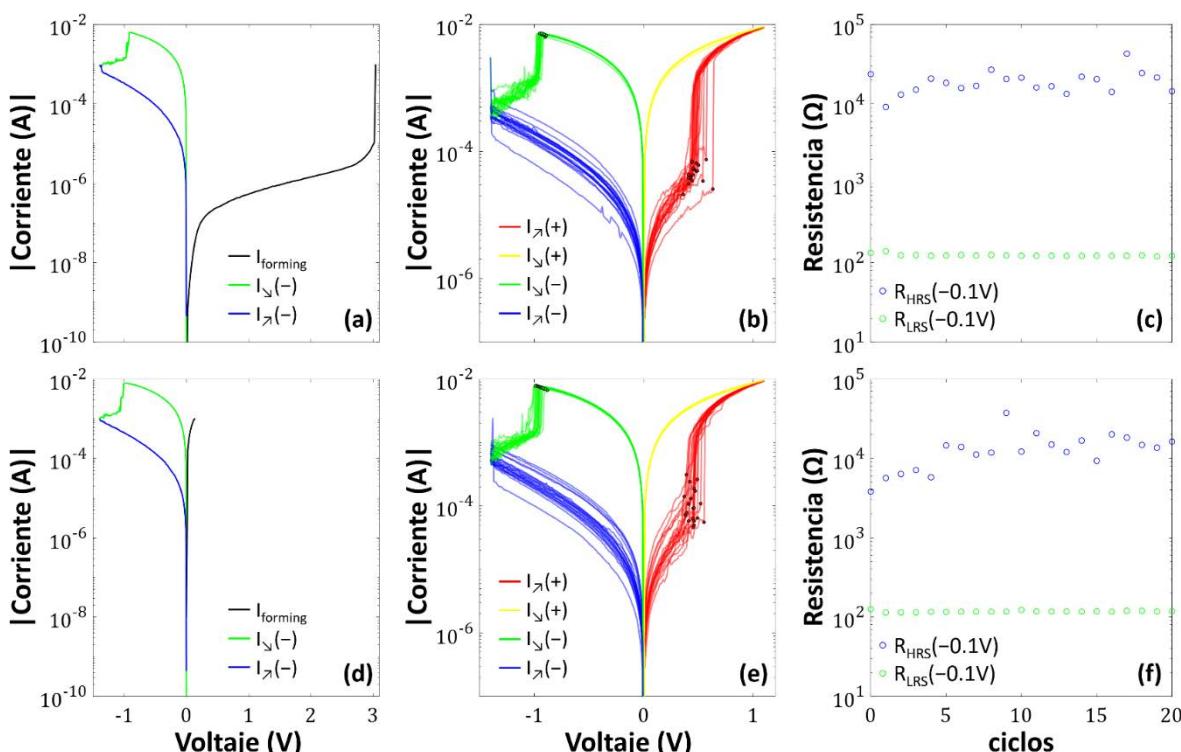

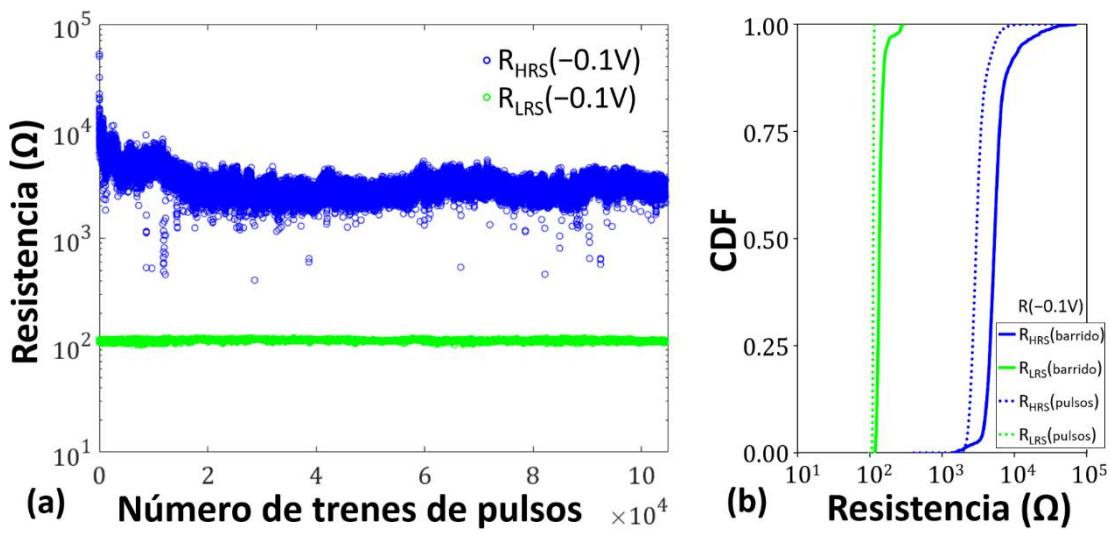

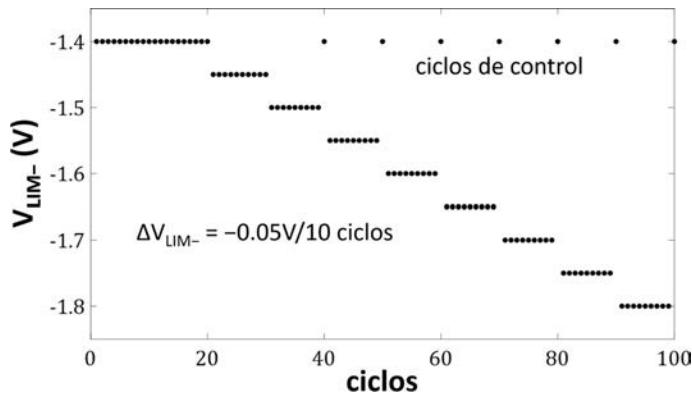

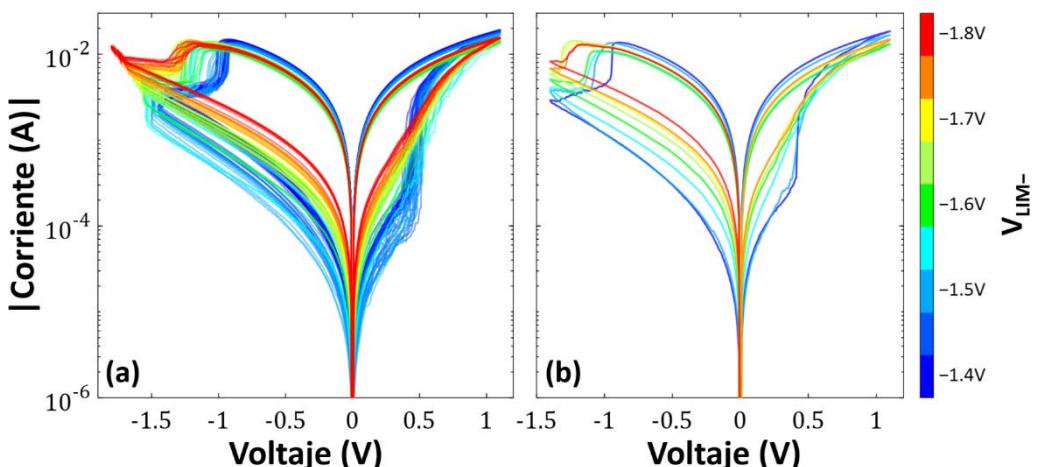

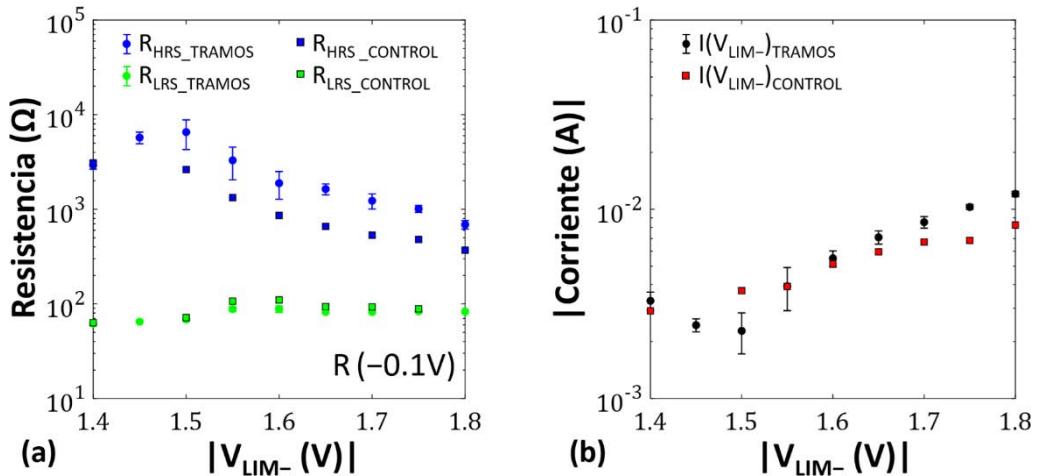

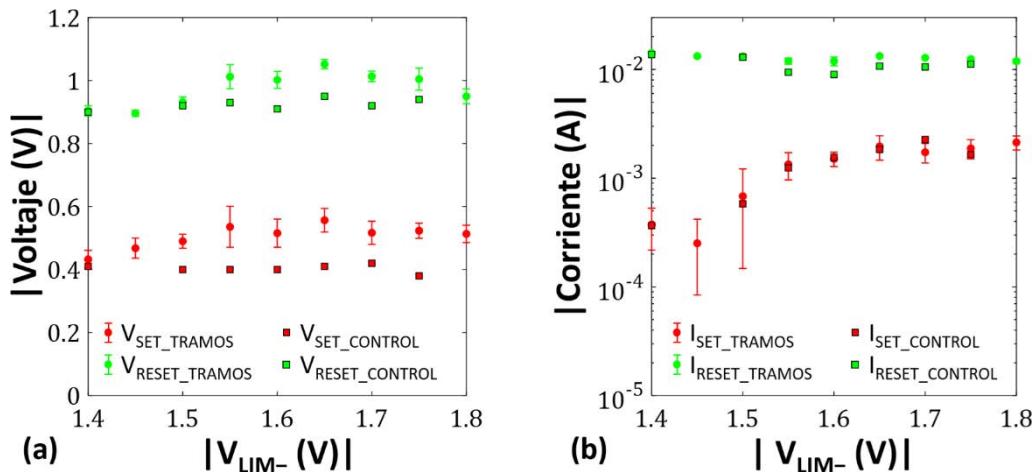

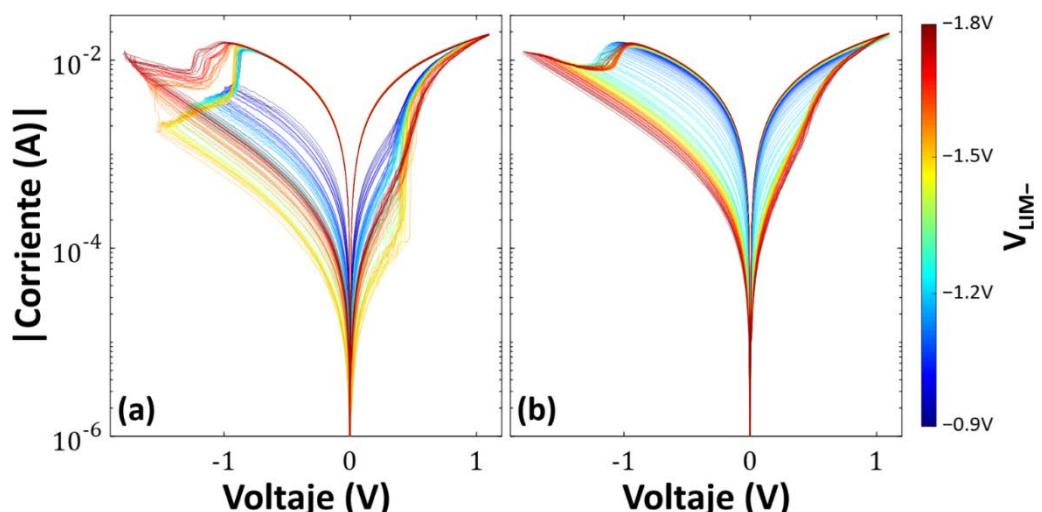

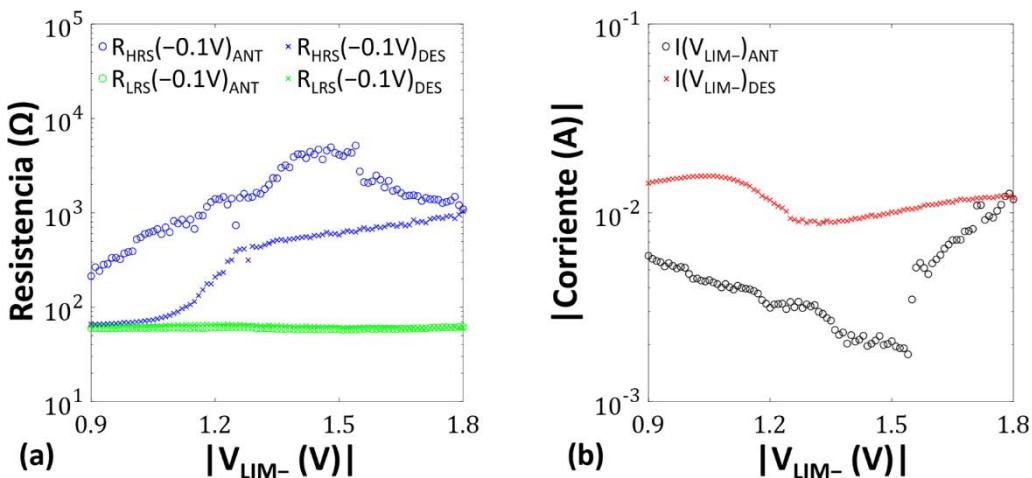

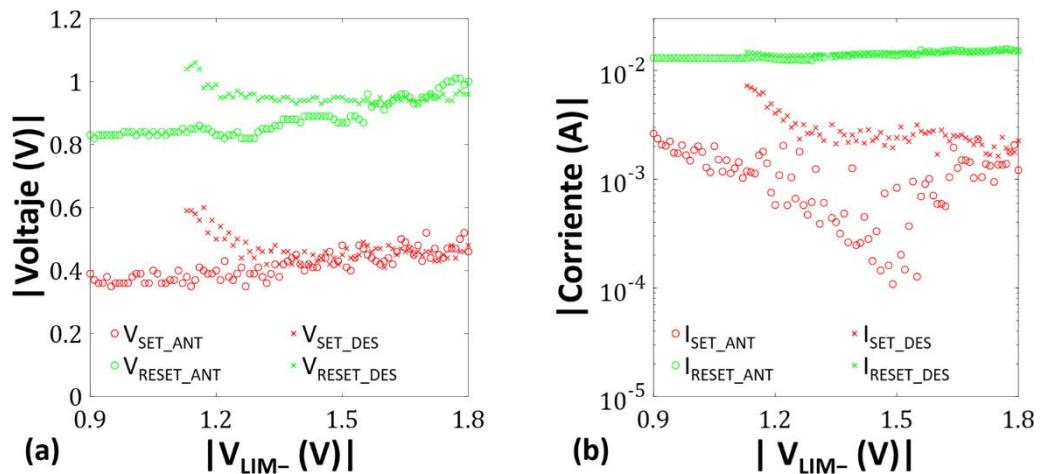

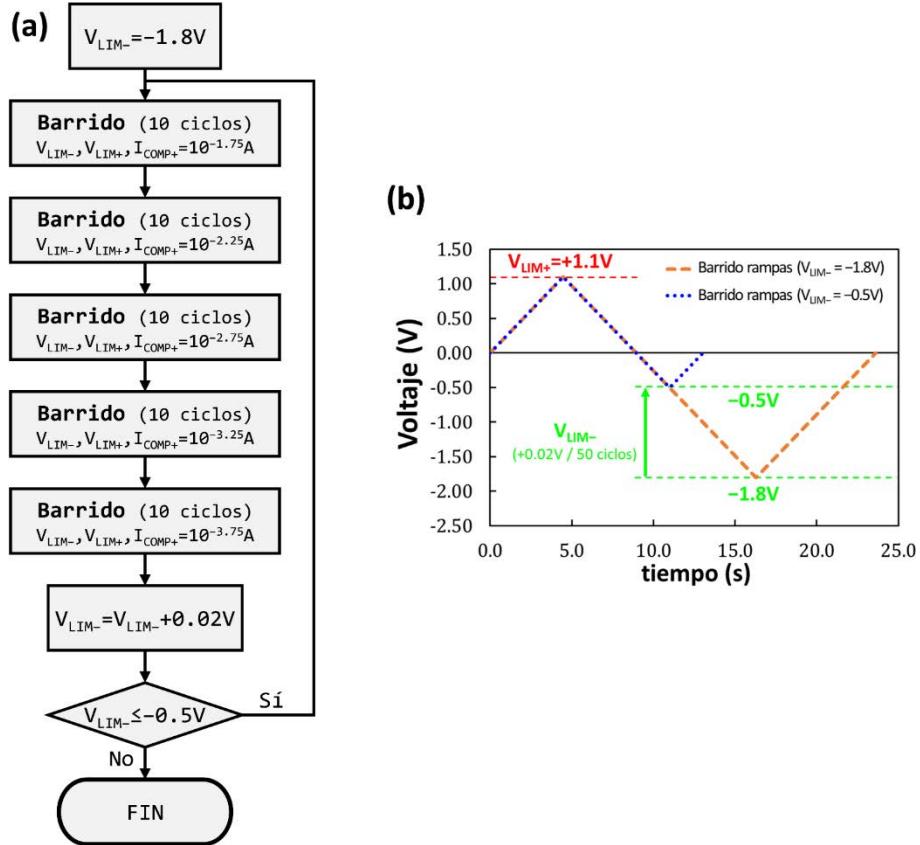

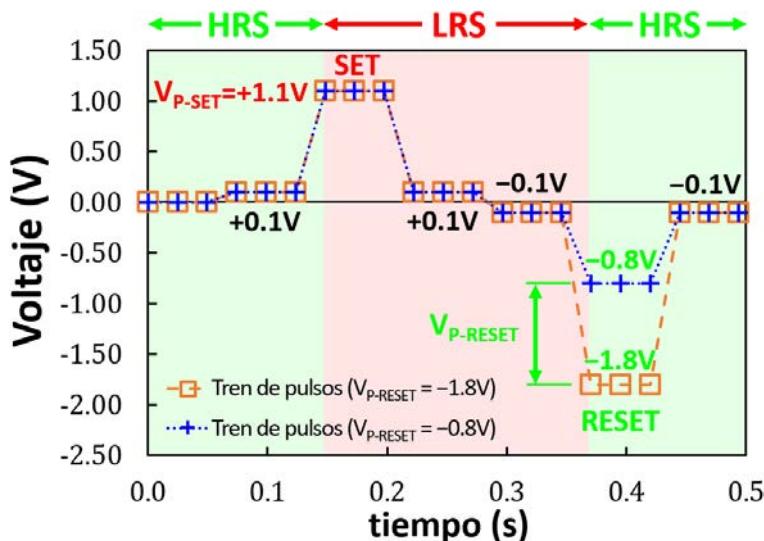

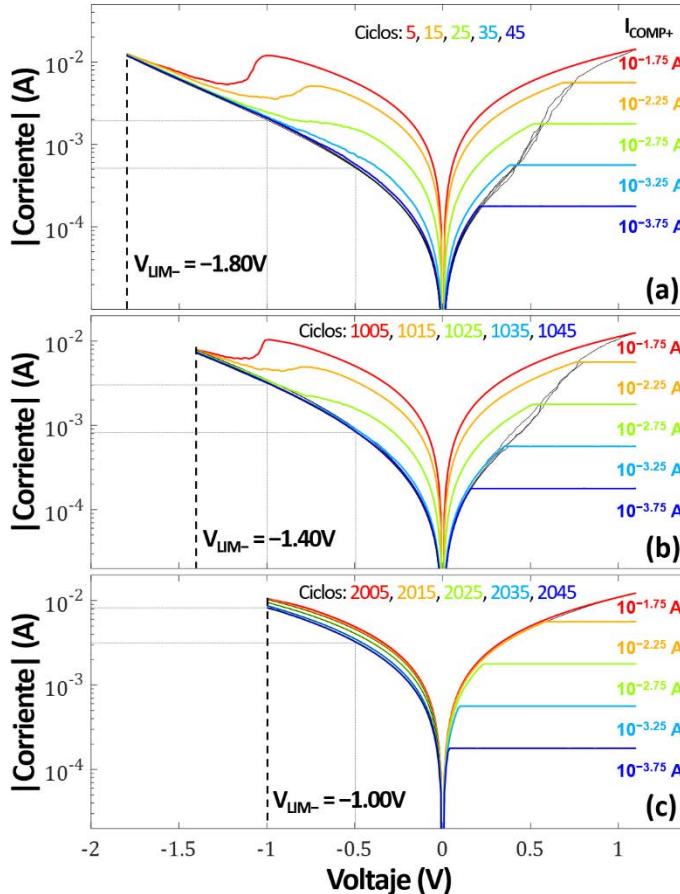

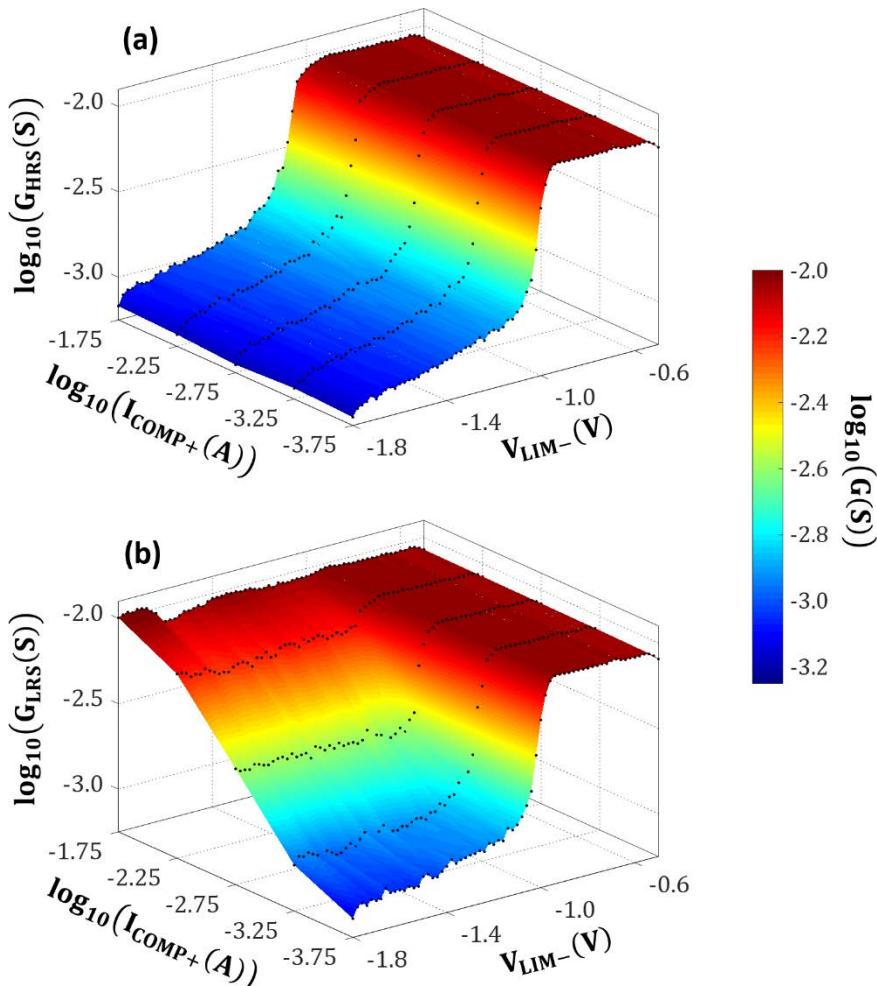

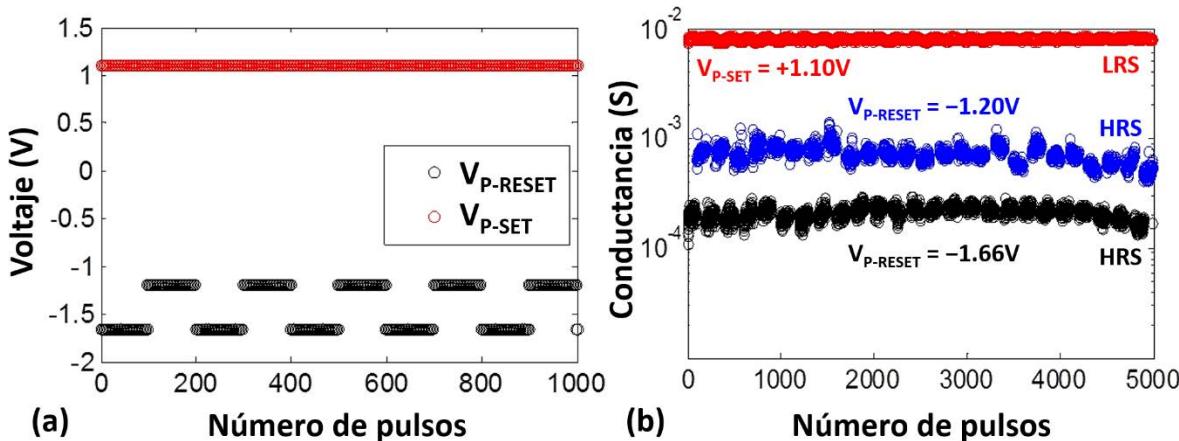

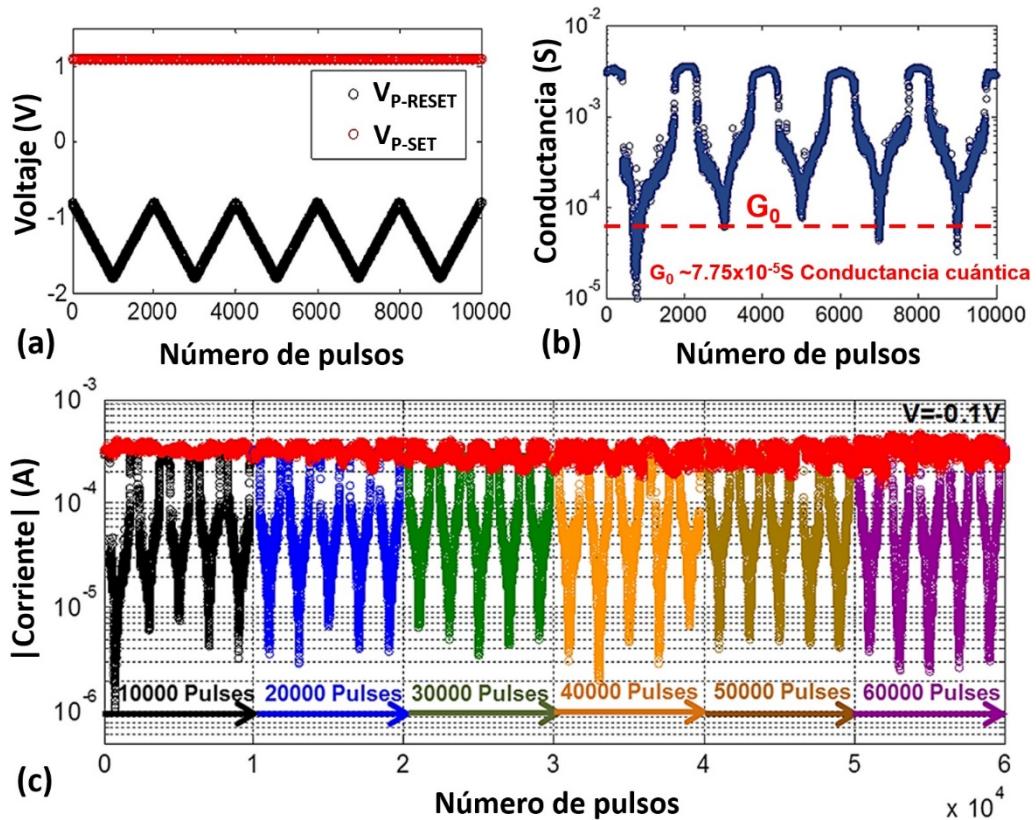

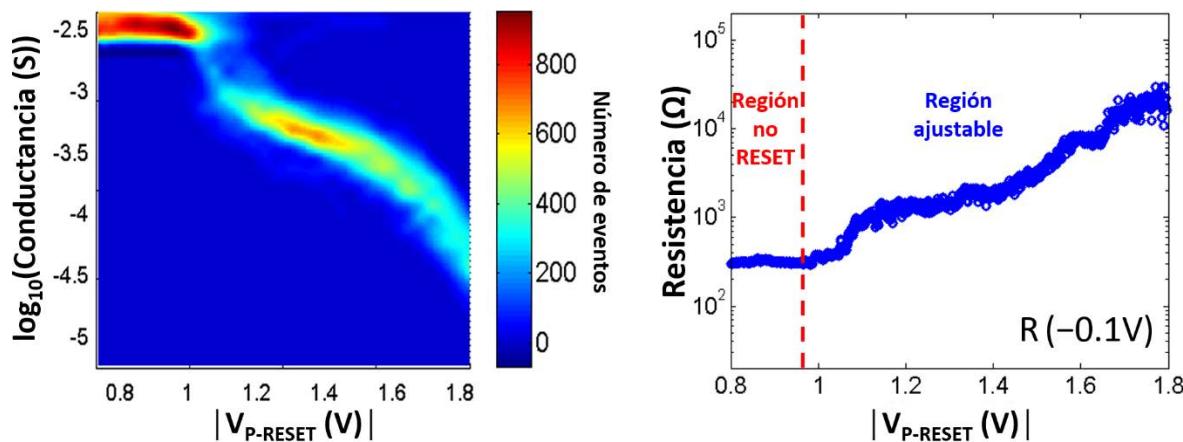

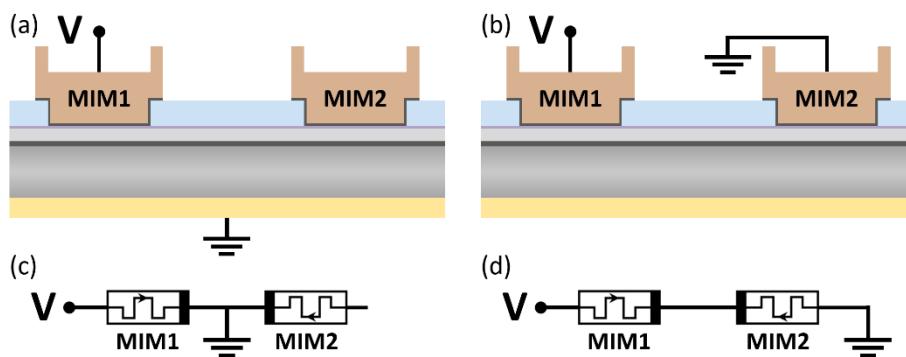

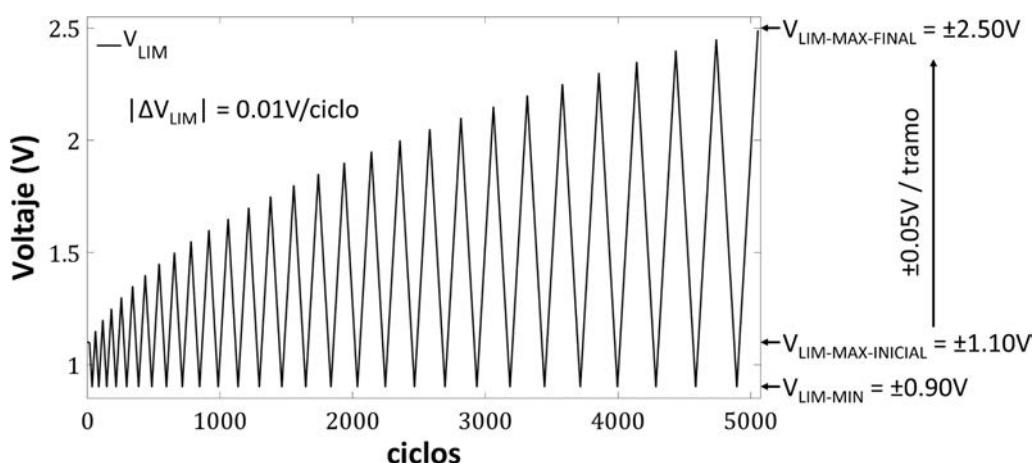

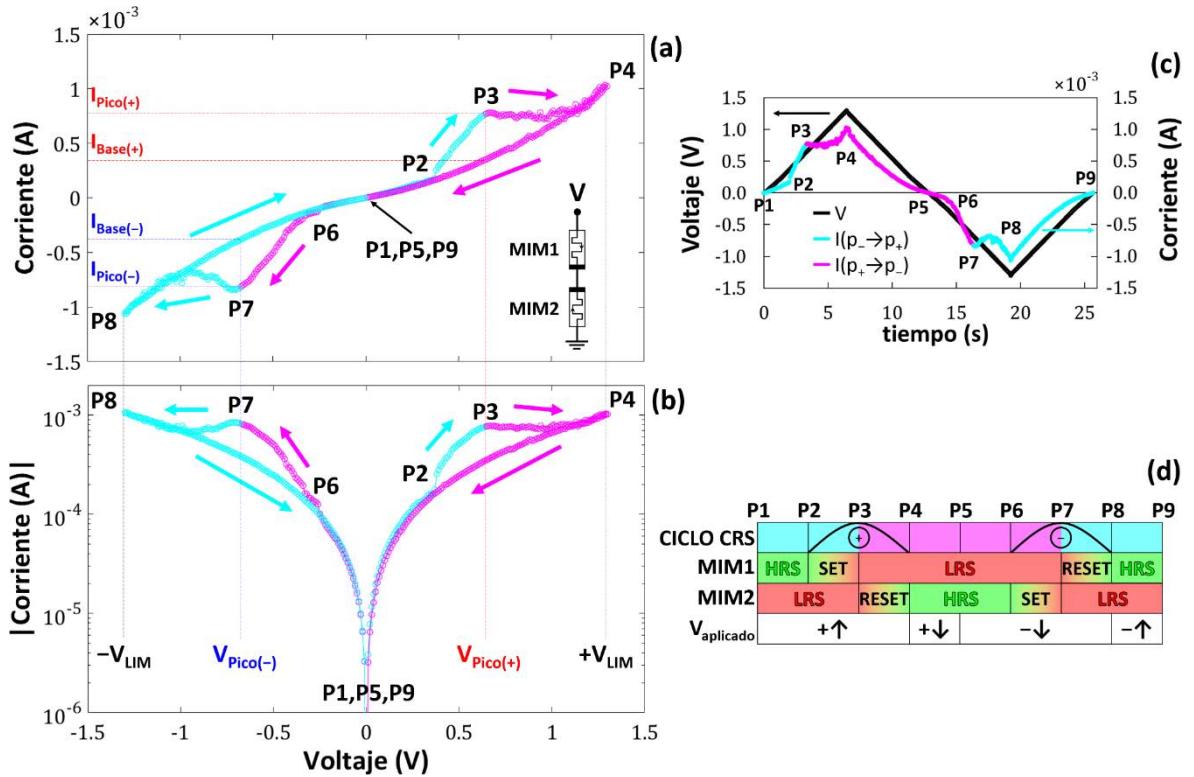

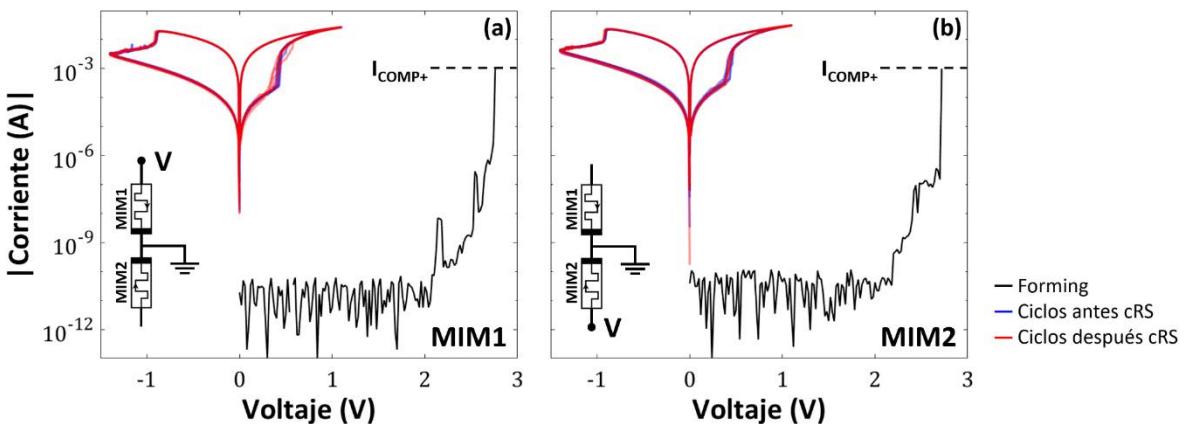

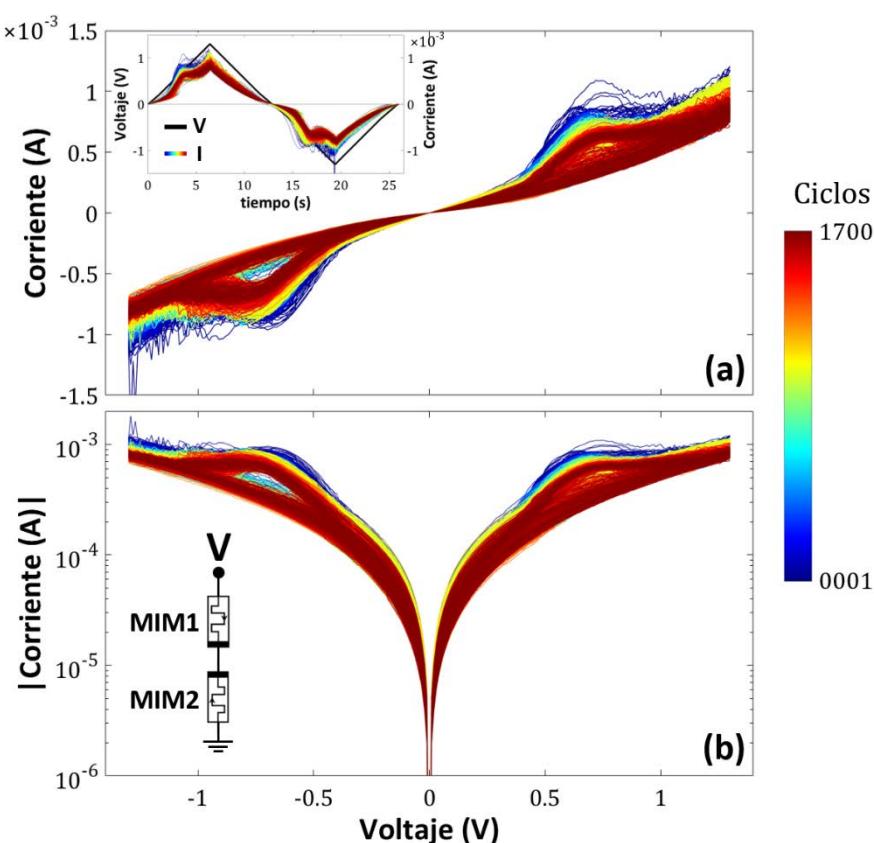

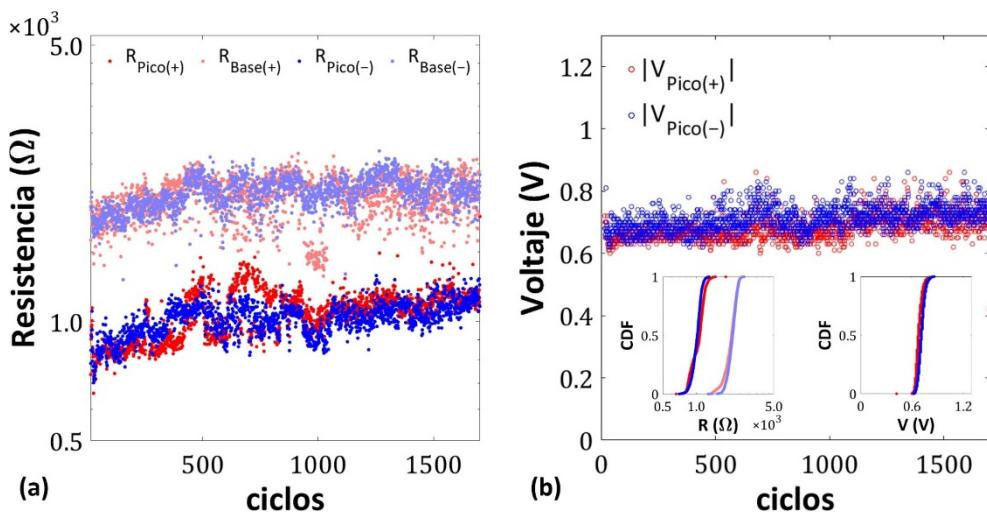

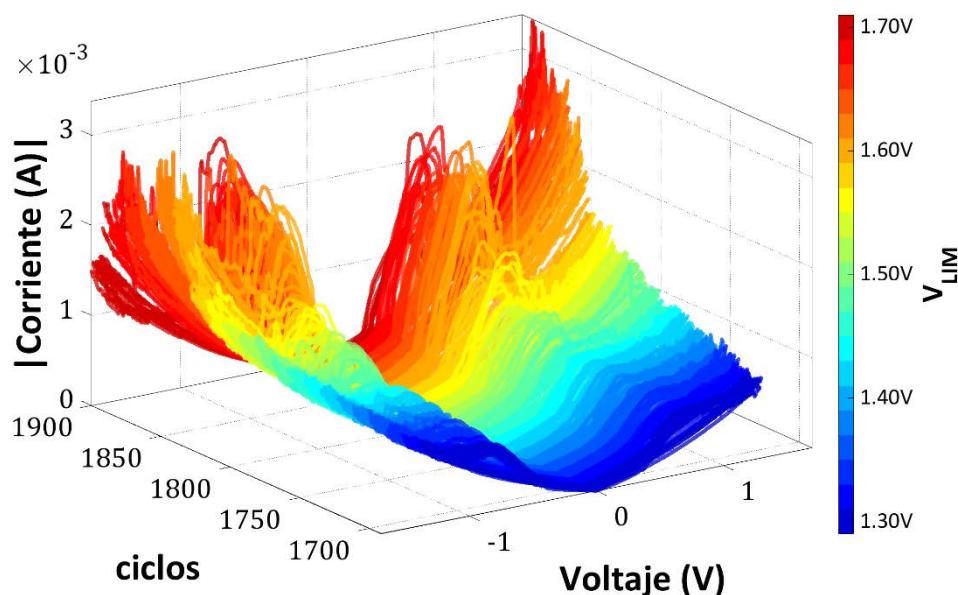

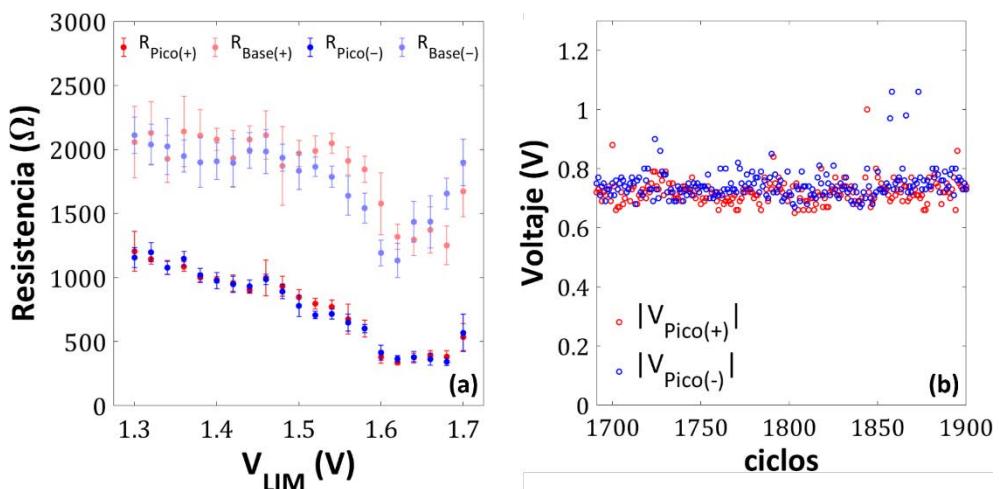

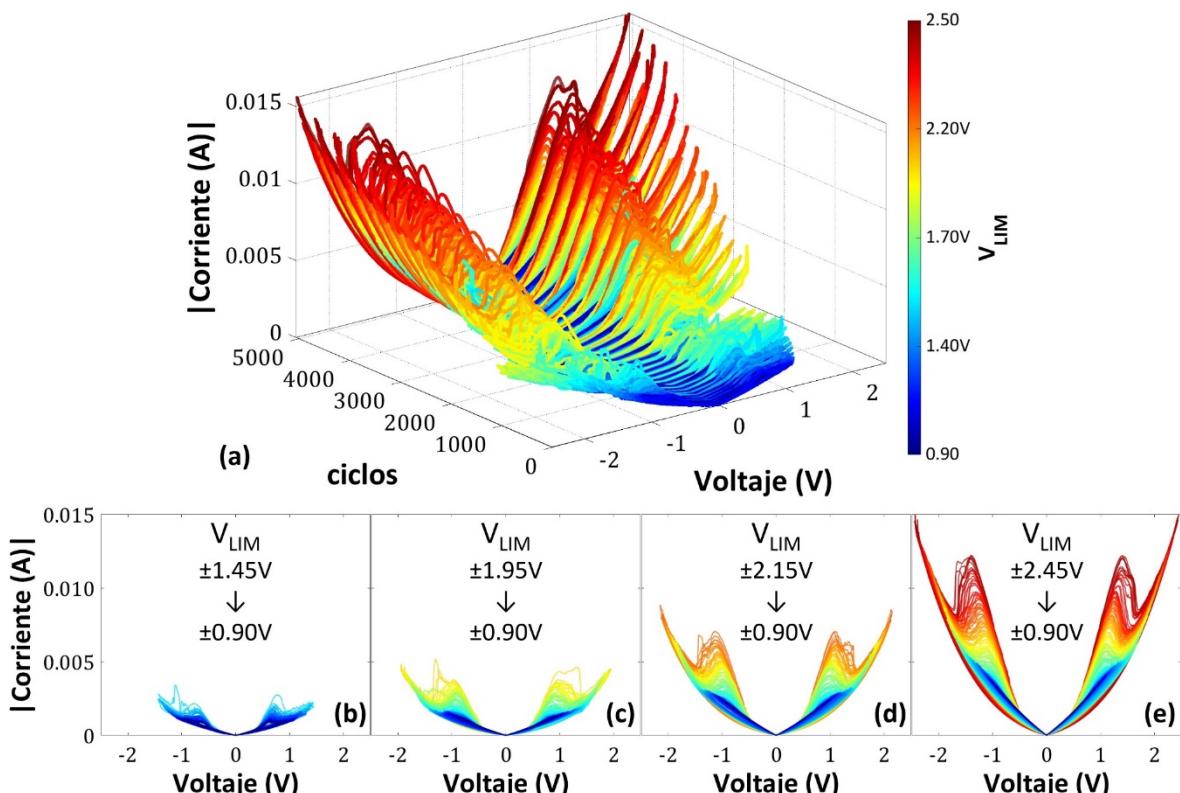

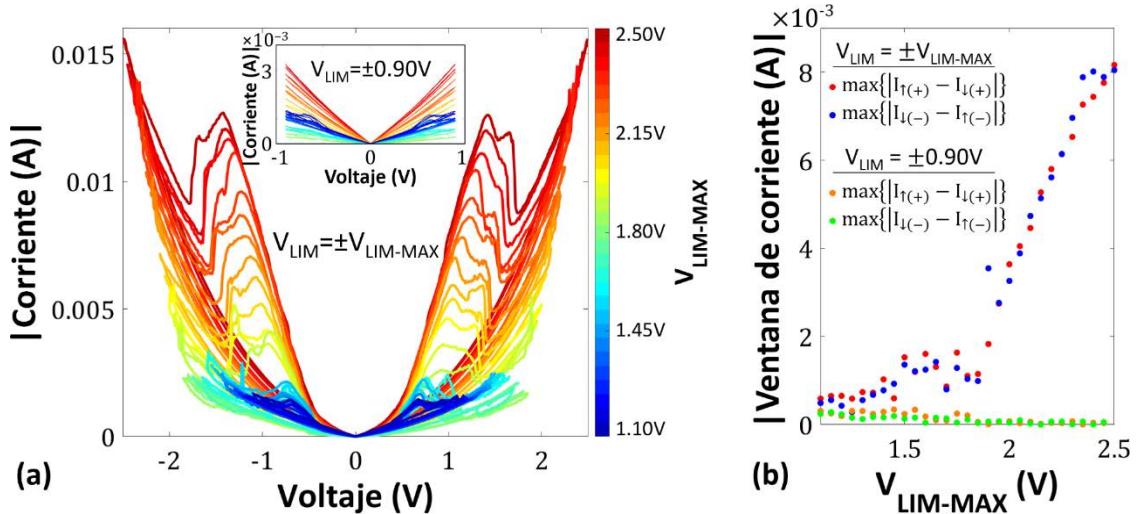

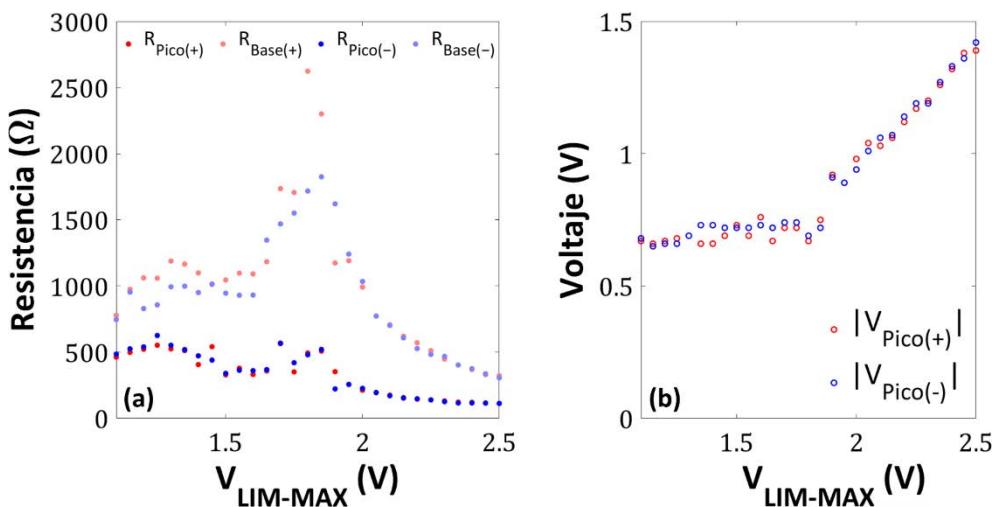

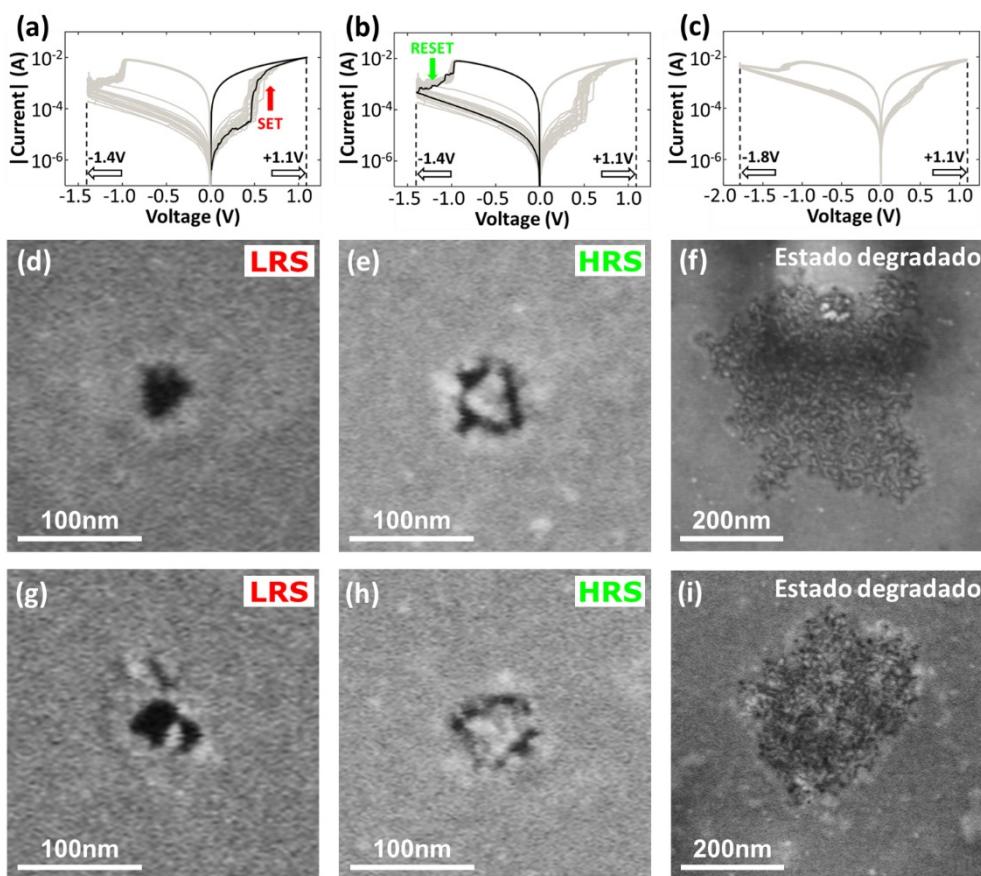

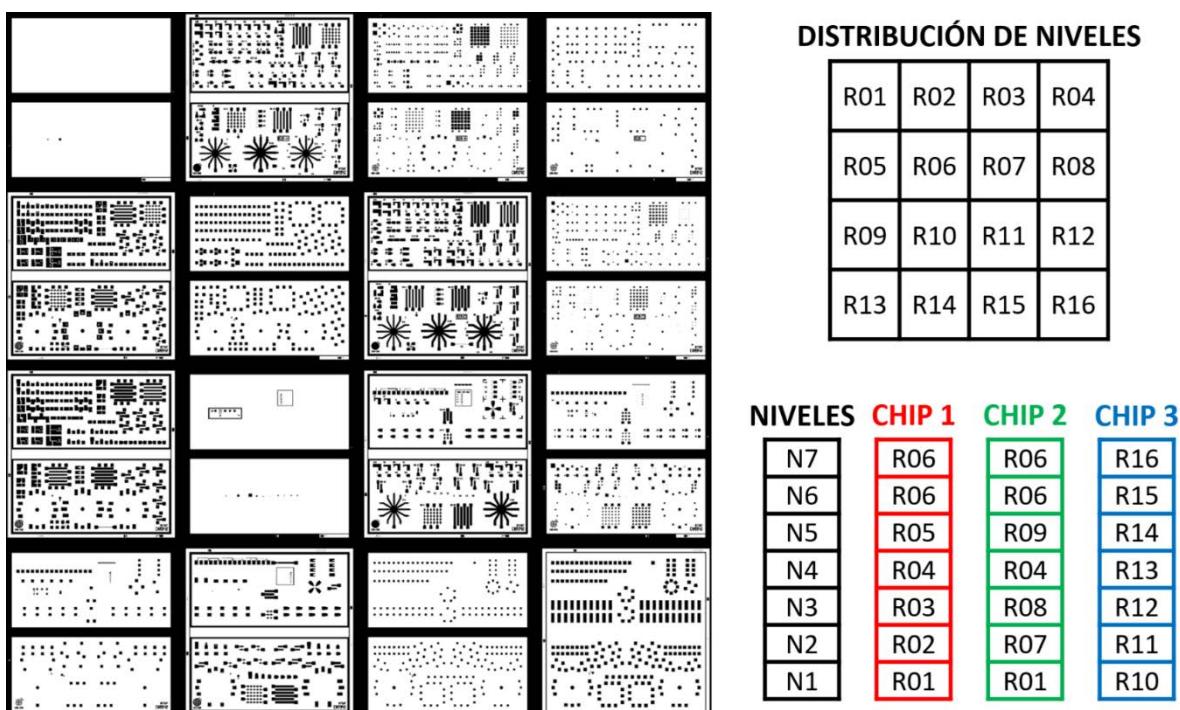

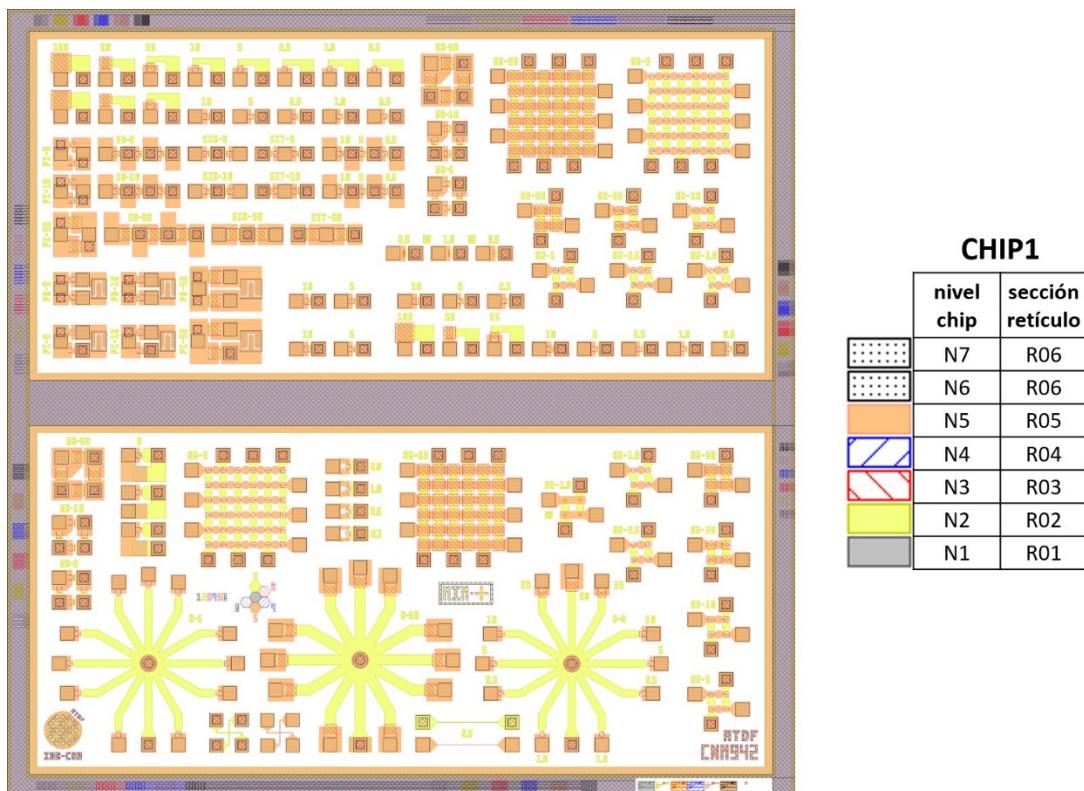

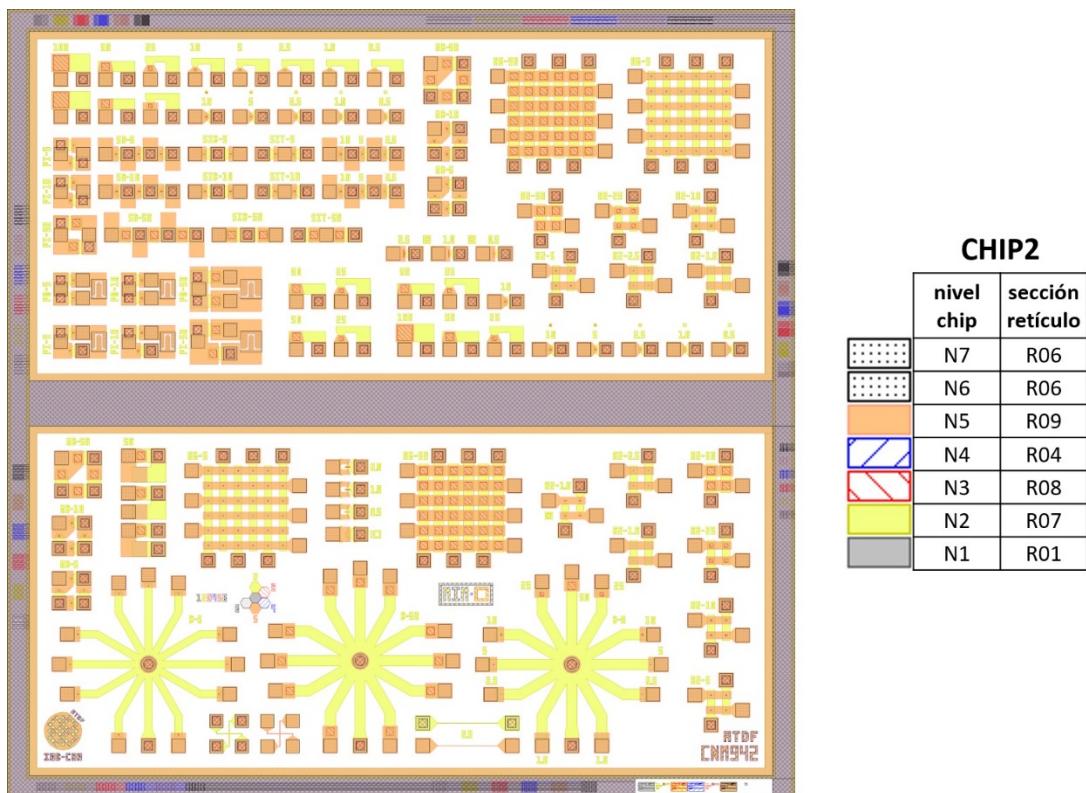

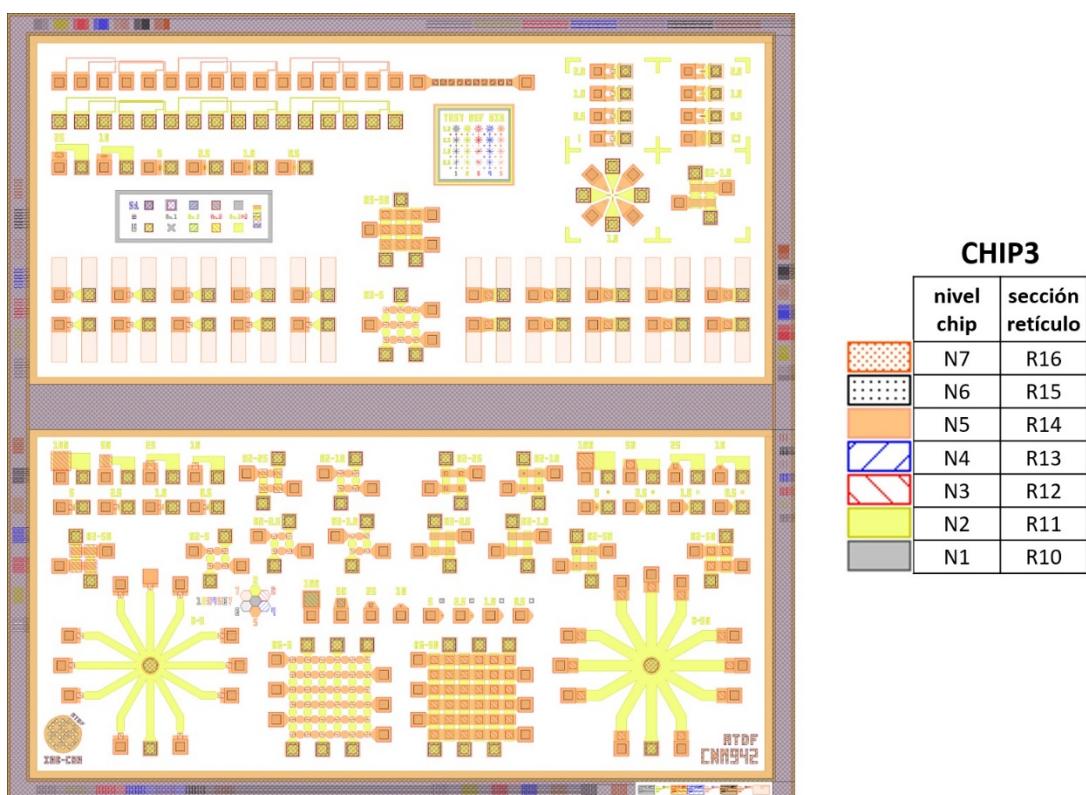

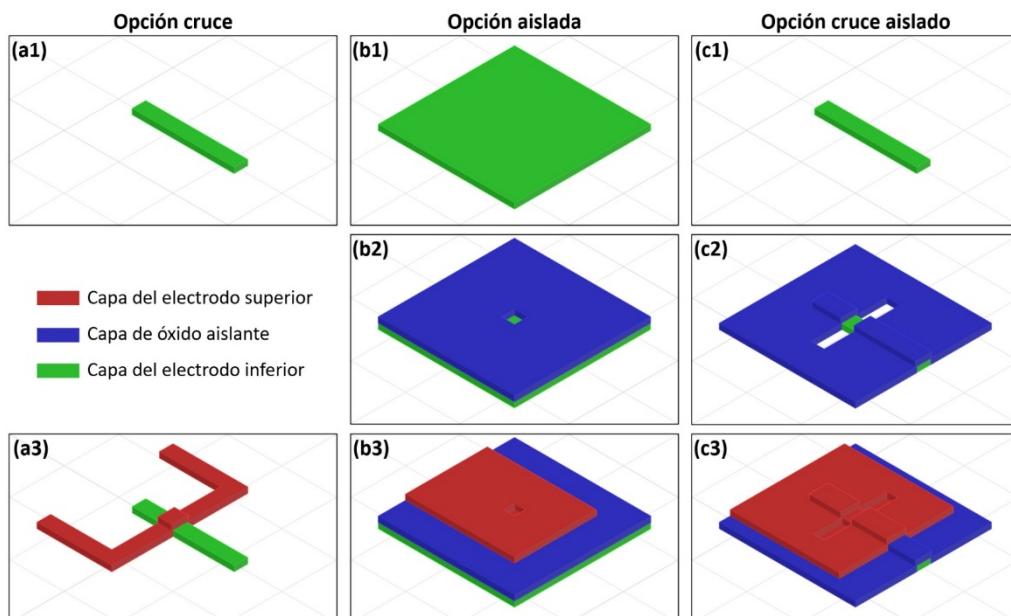

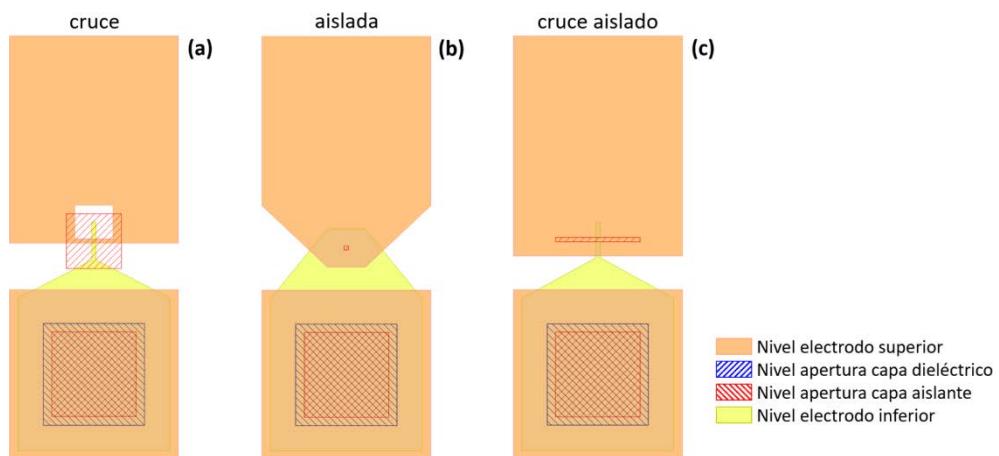

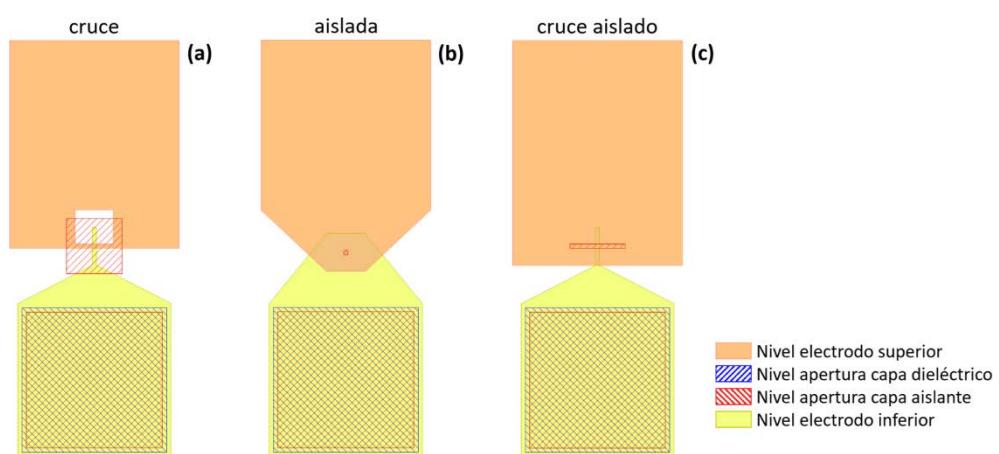

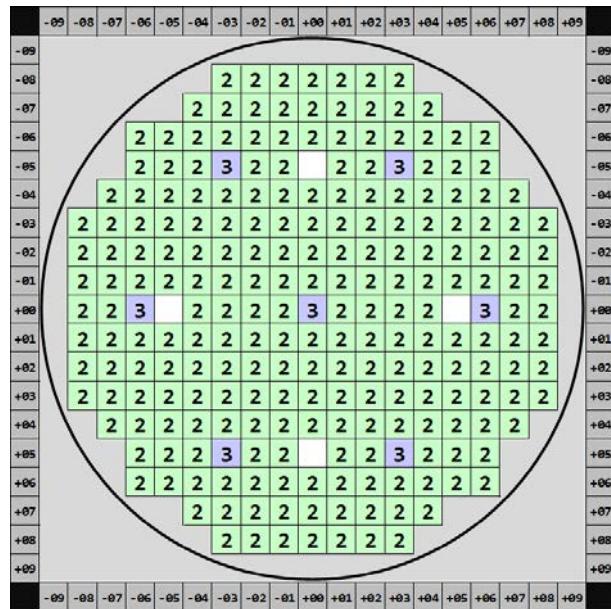

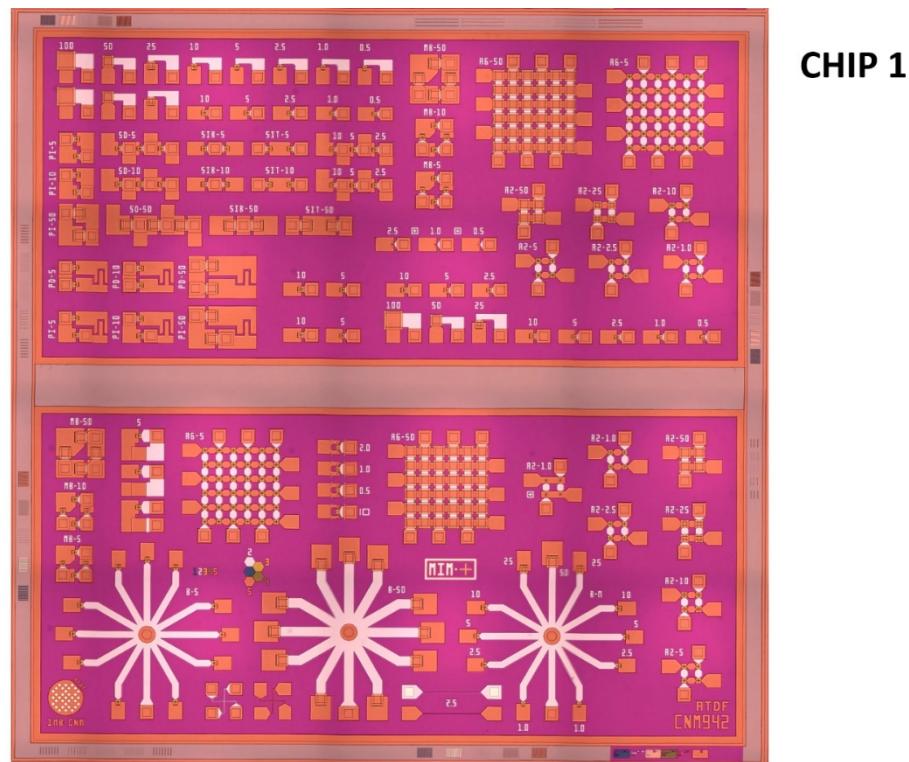

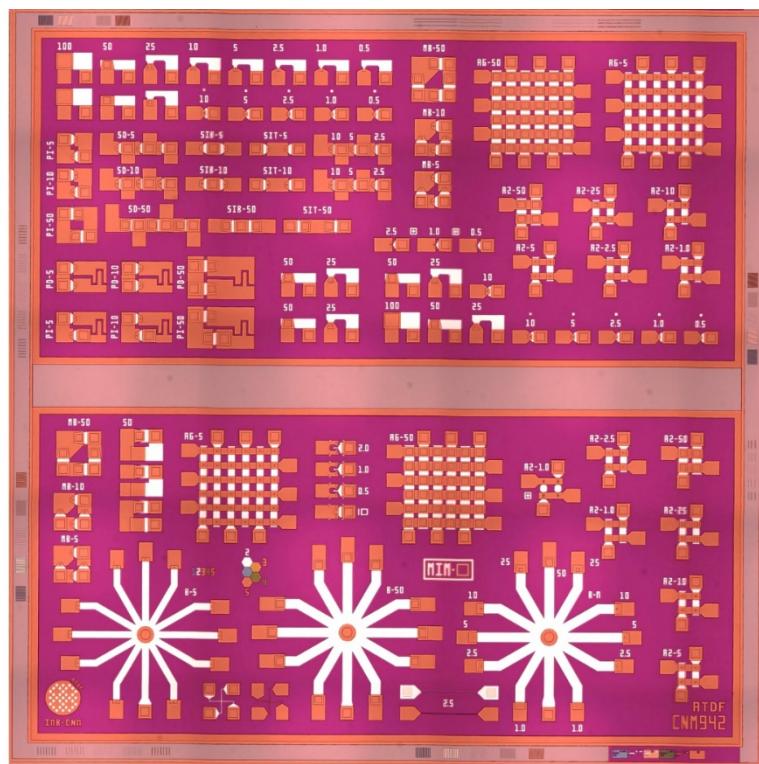

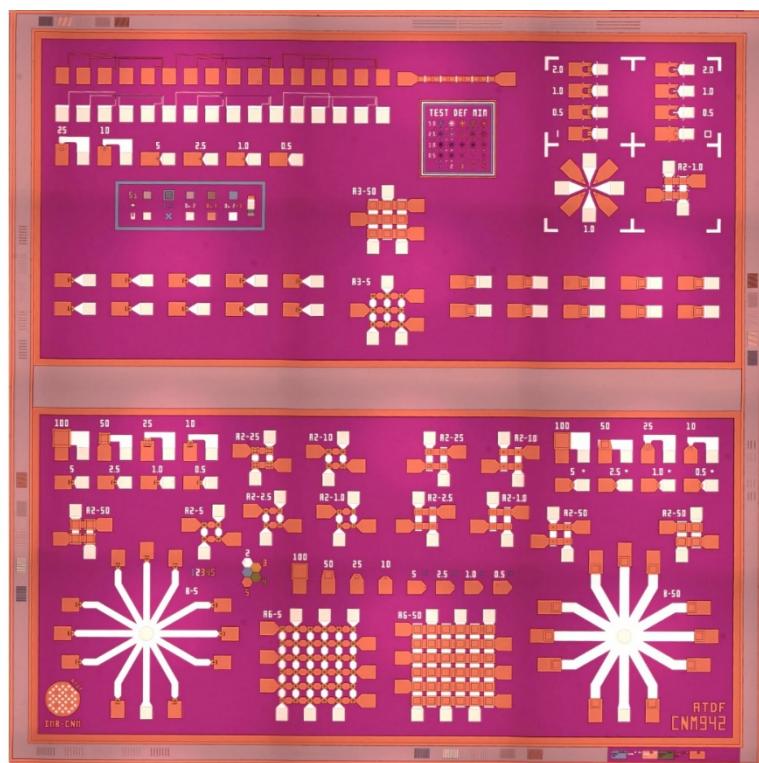

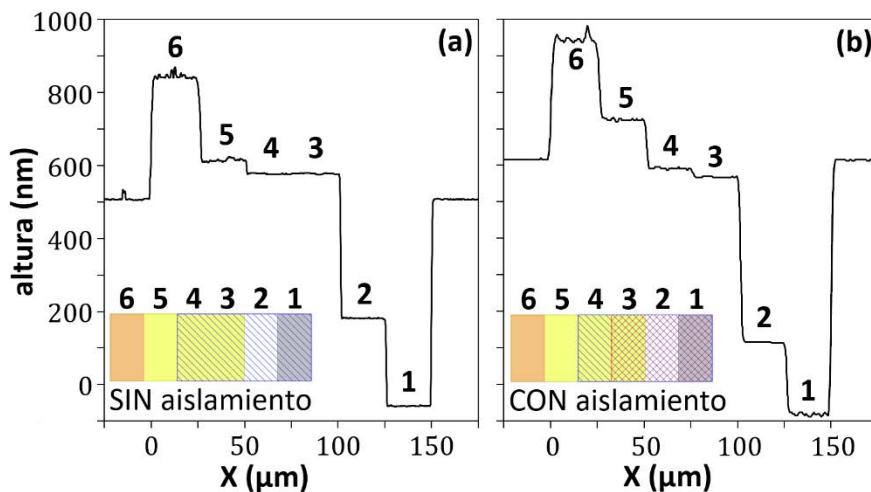

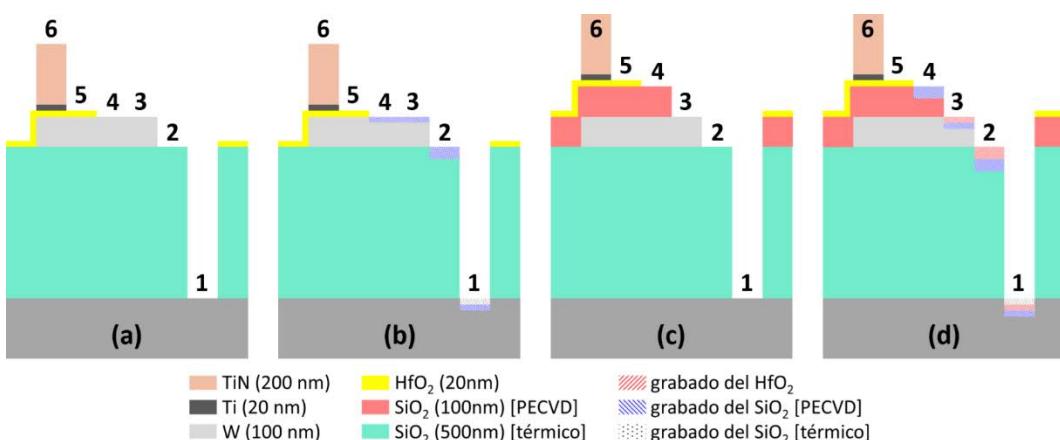

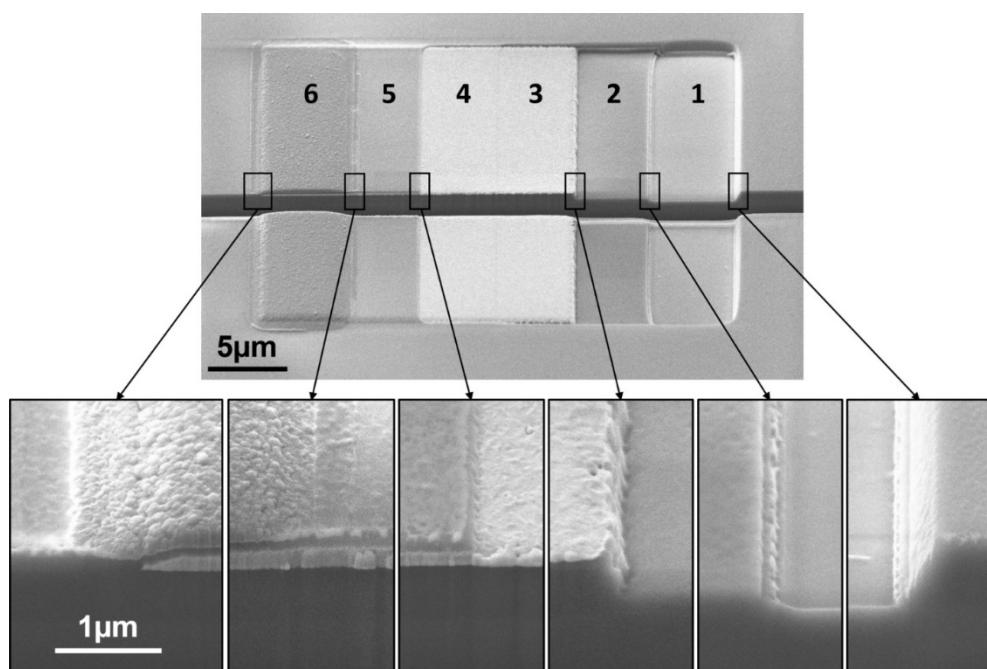

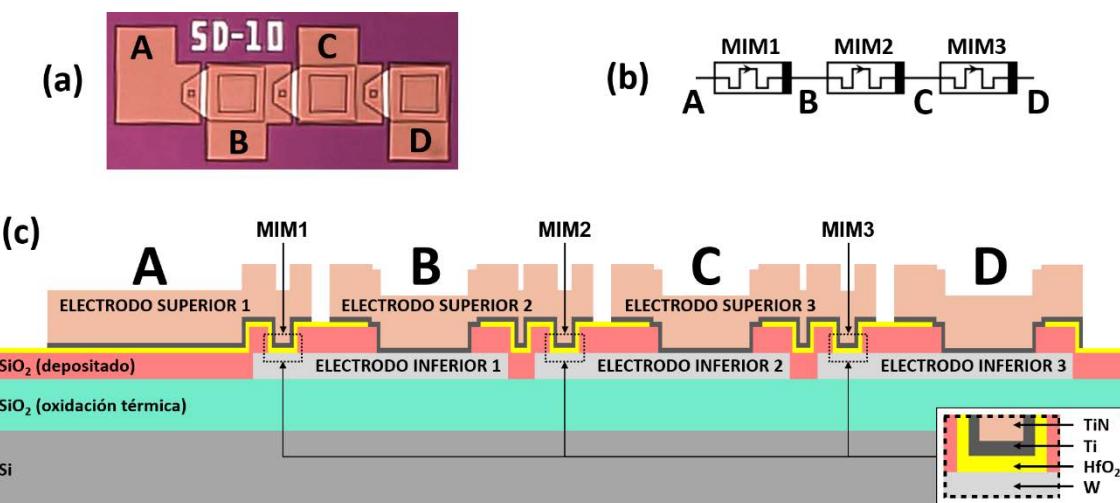

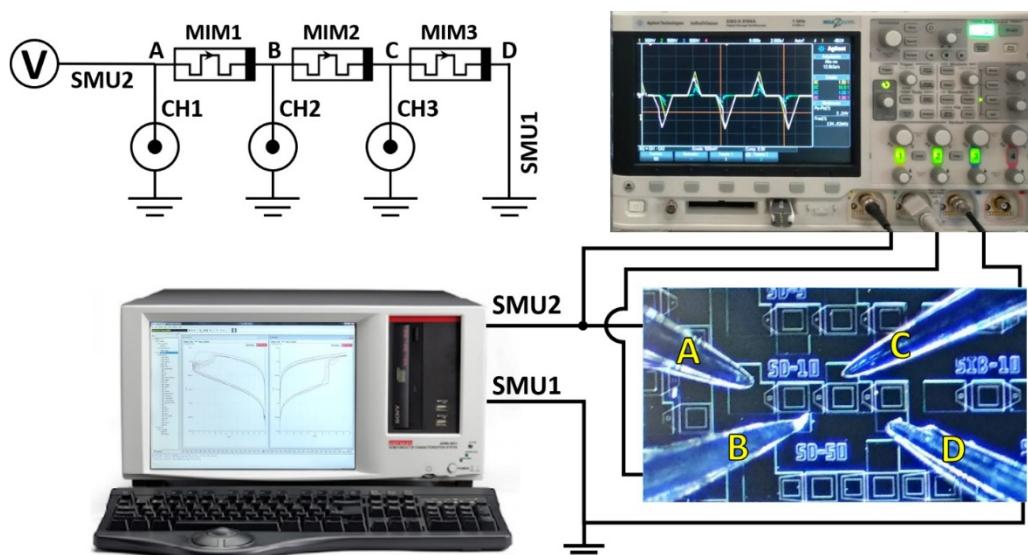

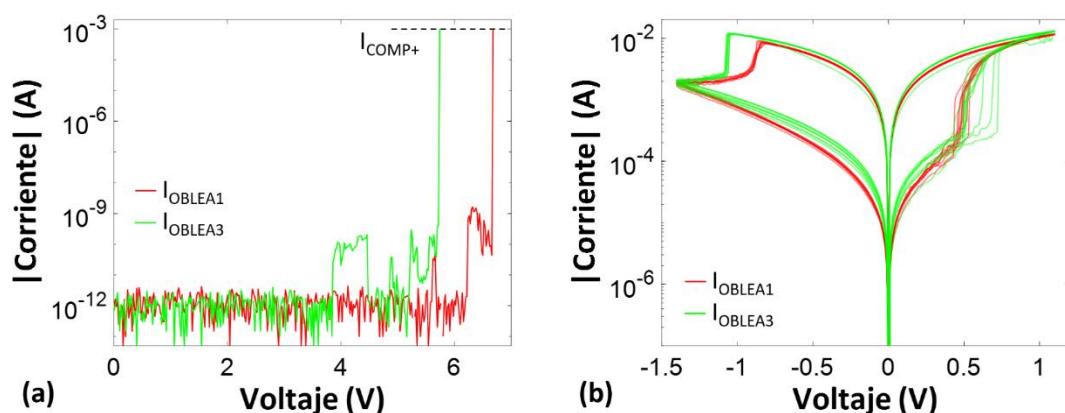

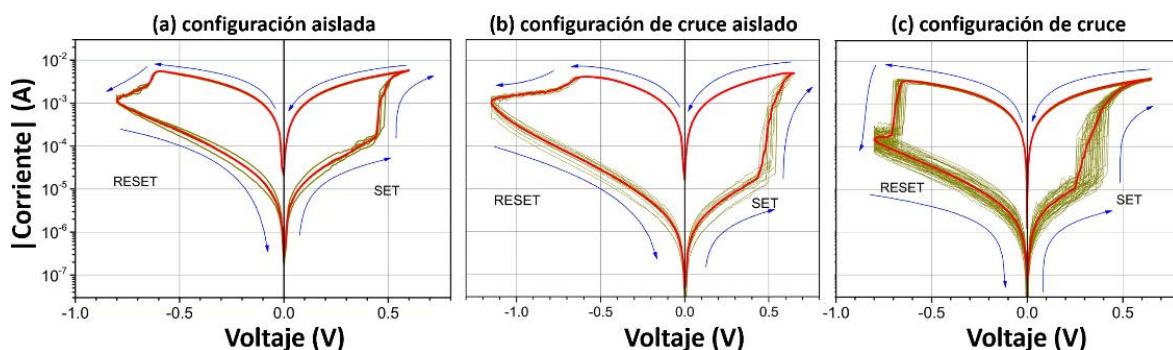

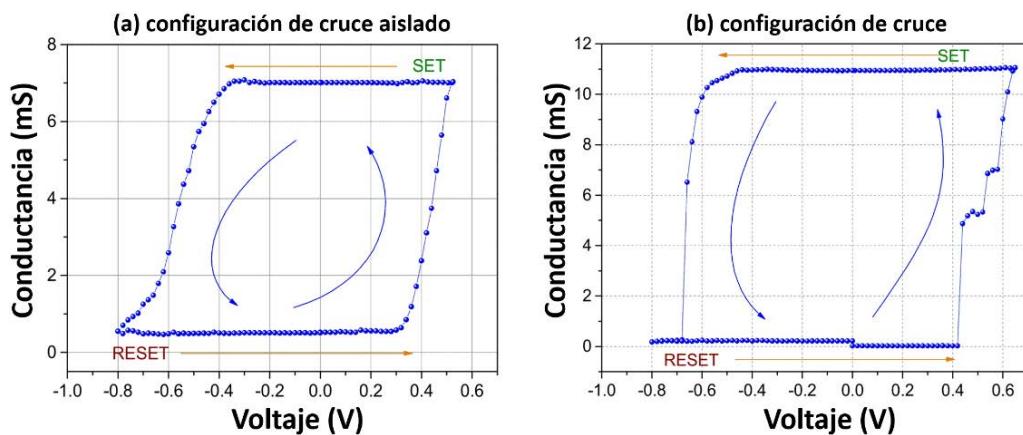

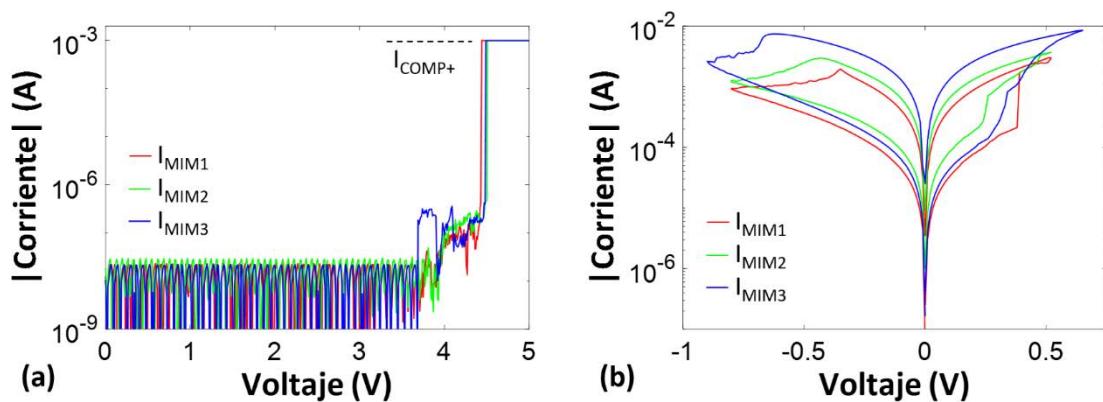

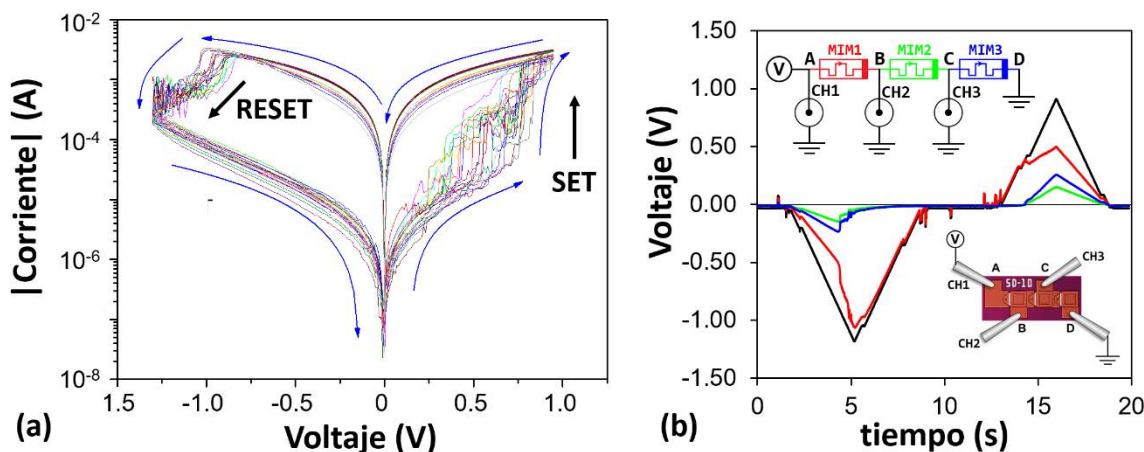

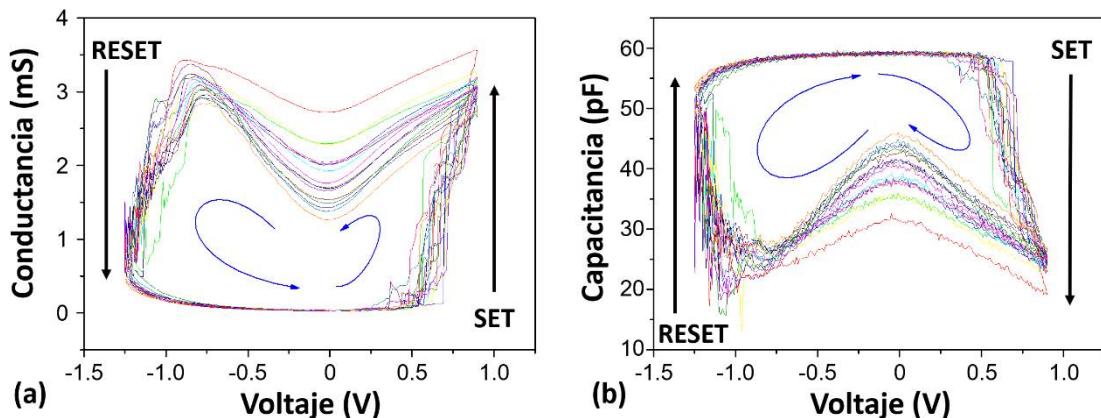

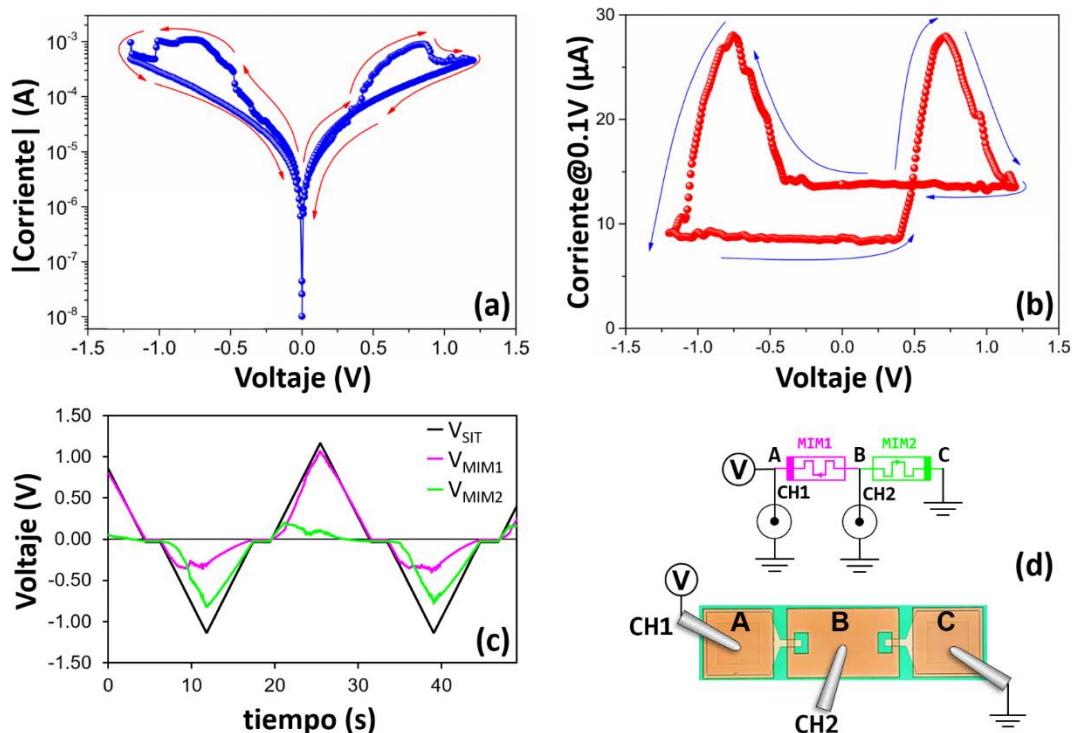

Una inspección del corte transversal realizado mediante FIB (**Figura 2-12c**) nos permite observar el corte transversal real de las estructuras. En esta inspección vemos que se ha producido el fenómeno conocido como “fencing” en el metal al ser estructurado mediante una etapa de lift-off, de manera que parte del metal del electrodo superior en las paredes