ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

# Modelling and Physical Design Automation for Organic and Printed Devices and Circuits

Ph.D. Thesis Dissertation

Author: Supervisors:

August Arnal Rus Eloi Ramon i Garcia, Lluís Terés Terés

UNIVERSITAT AUTÒNOMA DE BARCELONA (UAB)

September 2021

Bellaterra, Catalonia

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Dr. Eloi Ramon i Garcia

Dr. Lluís Terés Terés

Universitat Autònoma de Barcelona Electronic Engineering Departament PhD programme in Electronic and Telecommunication Engineering

This work was carried out at Institut de Microelectrònica de Barcelona (IMB-CNM), Universitat Autònoma de Barcelona (UAB), Barcelona, Spain, and Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany.

© 2021 August Arnal Rus

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

Si tant busques busques, al final trobes trobes.

Josep López, "Lopes"

# Agraïments

M'agradaria agrair en primer lloc als meus pares: August i Fina, per l'educació que m'han donat i el suport incondicional que han mostrat en tot moment en qualsevol de les meves decisions aconsellant-me sàviament. Aprofito per també agrair a les meves germanes: Helena i Anaïs, i a la meva parella, Raquel, el seu afecte. Dono les gràcies també a la resta de la meva família i als que ens han deixat, pel seu acompanyament d'ençà que tinc memòria.

Donar les gracies als meus amics de Sabadell: Sergi, Ferran, Pol, Bernat i Pau, per les innumerables històries tan bones com dolentes que hem viscut i seguirem vivint. Com oblidar la gent de la universitat: Vicente, Alejandro, Javier, Toni, Alberto i Adrià, que van acompanyar-me durant la meva formació com a enginyer i durant els petits moments que ens permetia fer alguna ximpleria.

Per altra banda agrair a l'Eloi i en Lluís l'oportunitat de realitzar aquesta tesi i d'estar involucrat en múltiples projectes que m'han fet avançar en el món professional. Agrair els companys del grup ICAS i remarcar específicament els del grup de Printed: Carme, Roger, Miquel, Alba, Sandra, Mijal, Silvia, Alex, Álvaro i Matías, per tots els cafès i menjars distesos i la seva ajuda desinteressada en qualsevol circumstància, a més de la seva amistat.

També agrair a la gent que ha estat amb mi pel CNM: Marcos, Samuel, Jose, Joan, Carlos, Edu, Miguel, David, Stefania, Albertito, Fantasma, Jordi, Joan, Jofre, Ricardo, Paco, Txema, Roger i Roger, on hem compartit xerrades, objectius i alguna que altra festa i barbacoa/calçotada, espero seguir sent invitat quan es tornin a celebrar! He intentat de no oblidar-me de ningú, però segur que em deixo algú de forma no intencionada i li demano les meves més sinceres disculpes.

Agrair a tota la gent del KIT per acollir-me tan bé, amb qui vaig aprendre altres maneres de treballar i amb qui vaig poder compartir temps i experiències que segur que no oblidaré mai, en especial a la Jasmin, Surya, Gabriel i Greta per la seva companyia tant professionalment com personalment.

I per acabar, agrair la feina de la comunitat Open Source per posar a disposició de tothom les eines desenvolupades per ells que possibiliten un avanç tecnològic més ràpid en permetre fer ús de les seves llibreries de manera lliure.

#### **Abstract**

In recent years, the interest in the manufacture of low-cost electronic systems has been on the rise due to increasing efforts of using sensors in Smart Cities and Industry 4.0. Multiple low-cost applications are beginning to appear, such as RFID stickers for product identification, flexible displays, or smart tags among others. Due to this need, Organic and Printed Electronics has positioned itself as an alternative technology to silicon with competitive advantages thanks to innovative materials and manufacturing methods in the world of electronics, allowing the production of low-cost, flexible, lightweight, large area and biodegradable devices. Despite this interest, there is still a lot of work to be done related to device modeling, design and simulation of complex circuits.

This thesis focus on the development of a Process Design Kit (PDK) with the necessary methodologies for the elaboration of an industrial model, which incorporates the DC and AC behavior of organic transistors, combined with the variations introduced by environmental factors and the intrinsic variability of the device. The PDK has been developed with a large automatic component, so it can evolve at the same time as the organic devices to be used.

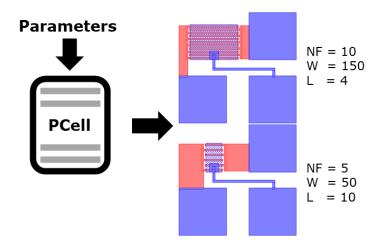

Within the framework of the thesis, an automatic electrical characterization environment has been developed with an output that provides the reports of devices and models allowing the analysis of a large number of transistors and their parameters. At the same time, a study of how it is affected by different external factors such as light, humidity or temperature, and the incidence of the application over and over again of potentials in the terminals has been done. The physical design part of the PDK is based on a set of Parameterized Cells (PCells), made in such a way that they are correct by design and combined with automatic methods allow the generation of arrays of devices and circuits in a reduced time. Multiple different devices and circuits have been made following this methodology in order to be able for characterization and modeling using the tools developed in the PDK.

The results of this thesis have allowed applying the knowledge in two different manufacturers of organic devices with the aim of design flexible systems. One of the great achievements of this thesis is the simulation and design of a 16-bit RFID tag developed by using organic technology and based on the methods developed and implemented in the developed PDK. On the other hand, the implemented tool allows following the evolution of the devices without a greater intervention on it, allowing advancing with new devices, creating and parameterizing models without great efforts.

#### Resum

Durant aquests darrers anys, l'interès per la fabricació de sistemes electrònics de baix cost ha anat augmentant degut a l'esforç en la sensorització de les ciutats intel·ligents i la indústria 4.0. Han anat apareixent múltiples aplicacions de baix cost, com per exemple, adhesius RFID per la identificació de productes, pantalles flexibles o etiquetes intel·ligents entre d'altres. Per aquesta necessitat, l'Electrònica Orgànica i Impresa s'ha posicionat com a tecnologia alternativa al silici amb uns avantatges competitius importats gràcies als materials i mètodes de fabricació innovadors en el món de l'electrònica, permetent l'elaboració de dispositius de baix cost, flexibles, lleugers, de gran àrea i biodegradables. Tot i aquest interès, hi ha molta feina encara per fer en relació amb el modelatge de dispositius, el disseny i la simulació de circuits complexos.

Aquesta tesi està enfocada al desenvolupament d'un Process Design Kit (PDK) amb les metodologies necessàries per a l'elaboració d'un model industrial que incorpora el comportament DC i AC dels transistors orgànics, combinat amb les variacions introduïdes pels factors ambientals i la variabilitat intrínseca del dispositiu. El PDK s'ha desenvolupat amb una gran component automàtica, de tal forma que pugui evolucionar en paral·lel als dispositius orgànics a ser usats.

En el marc de la tesi s'ha desenvolupat un entorn de caracterització elèctrica automàtica que genera informes dels dispositius i dels models permetent l'anàlisi de gran quantitat de dispositius i els seus paràmetres. Al mateix temps, s'ha dut a terme un estudi de com l'afecten els diferents factors externs com la llum, humitat o temperatura, i la incidència de l'aplicació de potencials en els terminals de forma repetitiva. La part de disseny físic del PDK està basat en un conjunt de cel·les parametritzades (PCells) elaborades de tal forma que siguin correctes per disseny i que combinades amb mètodes automàtics permeten la generació de matrius de dispositius i circuits en un temps reduït. S'han realitzat múltiples dispositius i circuits diferents seguint aquesta metodologia per tal de poder ser caracteritzats i modelats usant les eines desenvolupades en el PDK.

Els resultats d'aquesta tesi han permès aplicar els coneixements en dos fabricants de dispositius orgànics amb l'objectiu de dissenyar circuits orgànics. Un dels grans assoliments d'aquesta tesi és la simulació i disseny d'una etiqueta RFID de 16 bits elaborada mitjançant tecnologia orgànica i basada en els mètodes desenvolupats i implementats en el PDK desenvolupat. Per altra banda, l'eina implementada permet seguir l'evolució dels dispositius sense una intervenció major en la mateixa, permetent avançar amb els nous dispositius, creant i parametritzant models sense grans esforços.

# **Table of Contents**

| Agraïments                                                 | V     |

|------------------------------------------------------------|-------|

| Abstract                                                   | VII   |

| Resum                                                      | IX    |

| Table of Contents                                          | XI    |

| List of Figures                                            | XV    |

| List of Tables                                             | XXIII |

| Glossary                                                   | XXV   |

| List of symbols                                            | XXXI  |

| 1 Dissertation Summary                                     | 1     |

| 1.1 Objectives of the thesis                               | 1     |

| 1.2 List of publications                                   | 2     |

| 1.3 Thesis outline                                         | 3     |

| 1.4 Thesis Framework                                       | 4     |

| 2 State of the art                                         | 7     |

| 2.1 Printed and organic electronics fabrication            | 8     |

| 2.1.1 Types of materials                                   | 8     |

| 2.1.2 Fabrication techniques                               | 11    |

| 2.2 Overview of printed and organic electronics technology | 14    |

| 2.2.1 Device Types                                         | 15    |

| 2.2.2 Organic circuits                                     | 16    |

| 2.3 Overview of automation systems                         | 21    |

| 2.3.1 Electrical automation solution                       | 23    |

| 2.4 Overview of organic PDK                                | 25    |

| 2.4.1 PDK Components                                       | 27    |

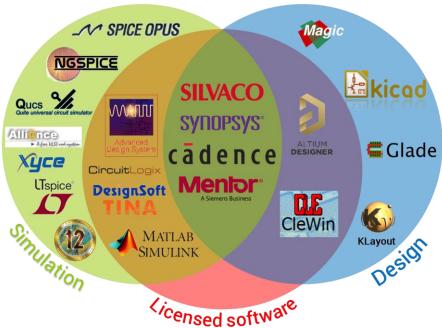

| 2.4.2 Well-known software in the organic field             | 28    |

| 2.4.3 Organic PDKs                                         | 29    |

| 2.4.4 OTFT models                                          | 32    |

| 2.4.5 Model Classification                                 | 37    |

| References                                                | 38   |

|-----------------------------------------------------------|------|

| 3 Layout Design                                           | 49   |

| 3.1 Automatic layout generation of single gate devices    | 51   |

| 3.2 Automatic layout generation of dual gate devices      | 63   |

| References                                                | 73   |

| 4 Device Modelling                                        | 75   |

| 4.1 Overview of characterization and modelling techniques | s 76 |

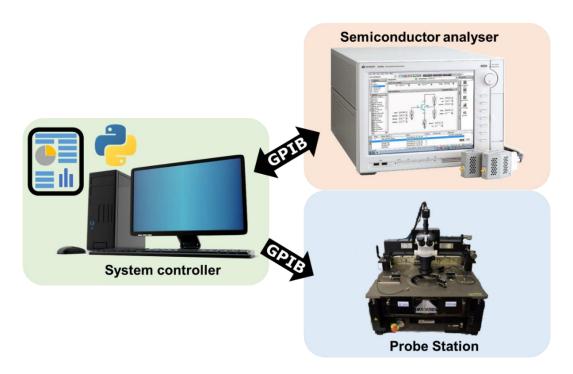

| 4.2 Automatic characterization system                     | 77   |

| 4.3 Automatic modelling procedure                         | 80   |

| 4.4 Diodes                                                | 84   |

| 4.5 OTFT                                                  | 86   |

| 4.5.1 Performance and key parameters                      | 88   |

| 4.5.2 DC                                                  | 89   |

| 4.5.3 AC                                                  | 92   |

| 4.5.4 Parameter variability                               | 98   |

| References                                                | 105  |

| 5 Device Simulation                                       | 111  |

| 5.1 Device variability study                              | 113  |

| 5.1.1 Model Parameter Variability                         | 118  |

| 5.2 Circuit simulation                                    | 120  |

| 5.3 Robust design                                         | 122  |

| 5.3.1 Inspection                                          | 123  |

| 5.3.2 Robust Dual Threshold circuit                       | 123  |

| References                                                | 136  |

| 6 RFID System Design                                      | 145  |

| 6.1 RFID basics                                           | 145  |

| 6.2 RFID Architectures                                    | 150  |

| 6.3 RFID tag simulation                                   | 159  |

| 6.4 RFID tag layout design                                | 165  |

| References                                                | 171  |

| 7 Conclusions                                             | 173  |

| 7.1 Outlook                                               | 175  |

# **List of Figures**

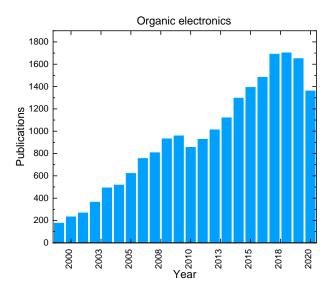

| Figure 1. Publications by year in the organic electronics field (source: Web of Science at March 2021)                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

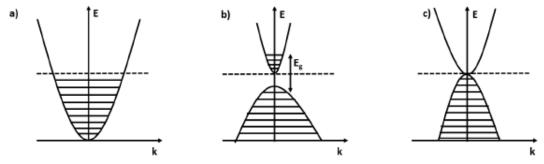

| <b>Figure 2.</b> Band Structures (energy vs momentum) of <b>A)</b> metal, <b>B)</b> ITO and <b>C)</b> Graphene. The dotted line represents the Fermi energy. The valence and the conduction band overlap for metals and in ITO, the Fermi level lies beyond the bandgap, Eg, in the conduction band due to doping. In Graphene, there exists six double cones at which the conduction and valence bands touch [23]                                               |

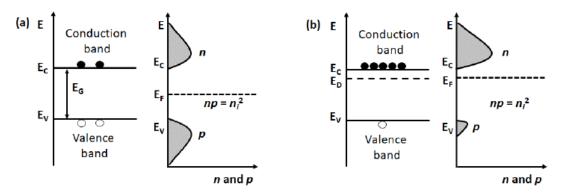

| <b>Figure 3.</b> N-type doping of a semiconductor. <b>A)</b> Intrinsic semiconductor has equal number of electrons and holes. The fermi level lies in the middle of the bandgap. <b>B)</b> Addition of electron donor increases the electron concentration, and the fermi level shifts towards the conduction band [23]                                                                                                                                          |

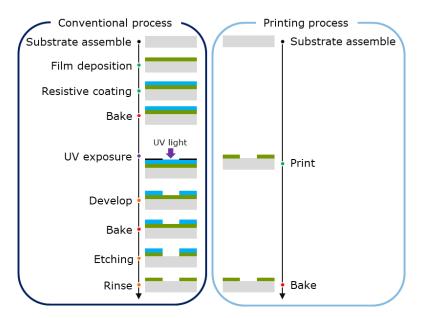

| Figure 4. Conventional subtractive fabrication compared with the additive process                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 5. Scheme of the classification of Printing techniques [30] 12                                                                                                                                                                                                                                                                                                                                                                                            |

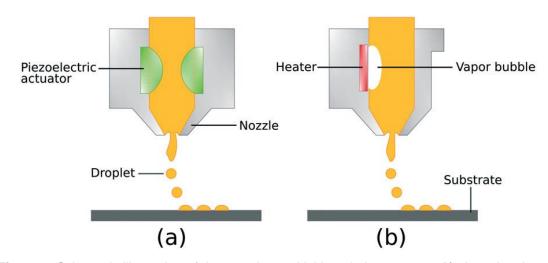

| Figure 6. Schematic illustration of drop-on-demand inkjet printing process:  A) piezoelectric DOD mode and B) thermal DOD mode [32]                                                                                                                                                                                                                                                                                                                              |

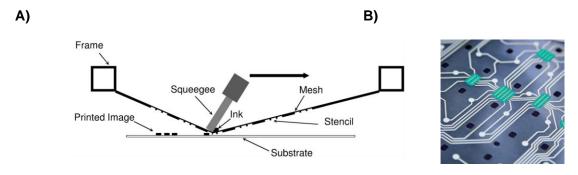

| <b>Figure 7</b> . <b>A)</b> Scheme of the screen printing technology. <b>B)</b> Picture of a circuit fabricated using screen printing technology [33]                                                                                                                                                                                                                                                                                                            |

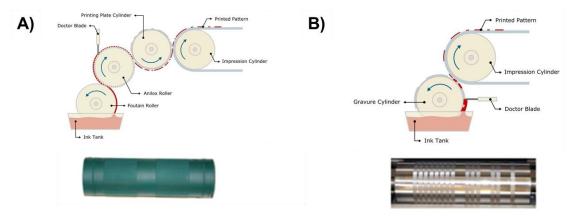

| Figure 8. Schematic diagram of A) Flexography and B) Gravure [34] 14                                                                                                                                                                                                                                                                                                                                                                                             |

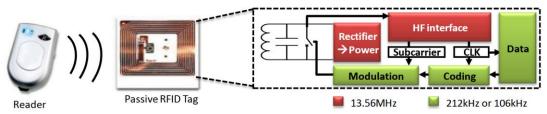

| Figure 9. A basic RFID system comprises a reader and a passive tag [40].                                                                                                                                                                                                                                                                                                                                                                                         |

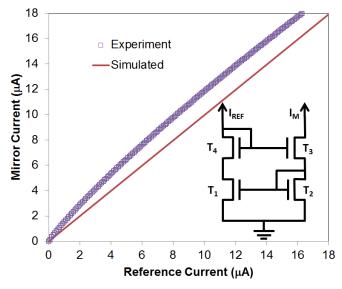

| <b>Figure 10.</b> Comparison of experimental and simulated performance of the current mirror circuit shown in the inset. The transistors were nominally identical with W = 2500μm and L = 50μm [44]                                                                                                                                                                                                                                                              |

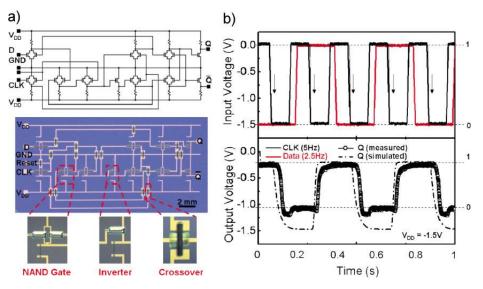

| <b>Figure 11.</b> Printed D flip-flop circuit. <b>A)</b> Circuit diagram (top) and optical image of the circuit (bottom). The magnified images show the three most important features of the printed circuit. <b>B)</b> Dynamic response of the device. The red and black lines in the top panel represent the data and clock signals respectively. The open circles in the bottom panel show the output response and the dashed line the simulated output [46]. |

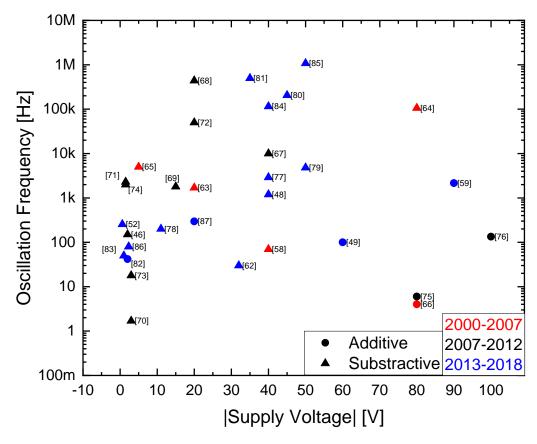

| Figure 12. Ring oscillators with different processing based on OE 20                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 13. Photograph of the 8-bit Arithmetic Logic Unit (ALU)-foil [10] 21                                                                                                                                                                                                                                                                                                                                                                                      |

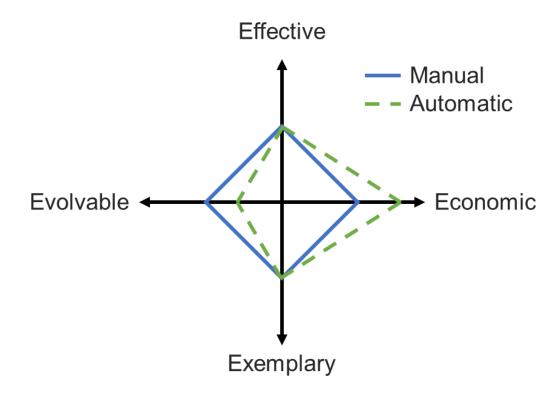

| Figure 14. Test case performance for manual or automatic test 22                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 15 Test automation development process 23                                                                                                                                                                                                                                                                                                                                                                                                                 |

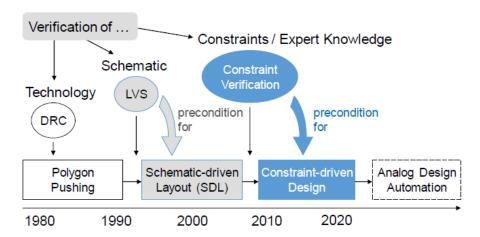

| <b>Figure 16</b> . Evolution of analog physical design methodologies towards the goal of a fully automated analog design flow [65]24                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

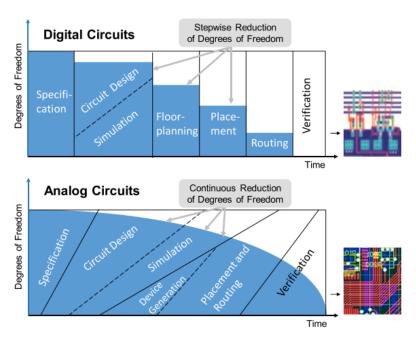

| <b>Figure 17</b> . Simplified design flow for digital circuits and for the analog counterparts where steps typically overlap and are tightly linked [65] |

| Figure 18. Generic methodology for full-custom circuit design supported EDA                                                                              |

| tools                                                                                                                                                    |

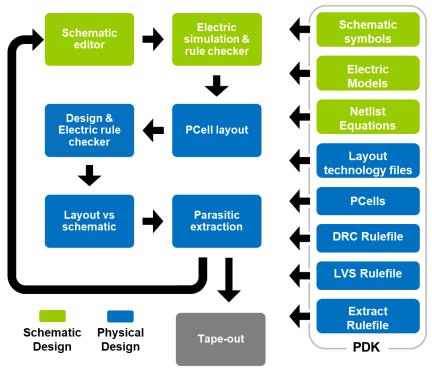

| Figure 19. Mobility and threshold voltage bending dependence [66] 26                                                                                     |

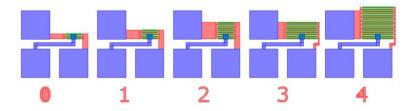

| <b>Figure 20.</b> PCell workflow, parameters variation in Number of Fingers (NF), finger Width (W) and channel Length (L)                                |

| Figure 21. EDA tools used in the organic electronics field                                                                                               |

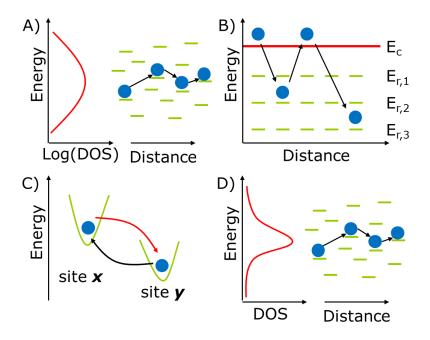

| Figure 22. A) Variable Range Hopping, B) Multiple Trapping and Release, C) Polaron model and D) Disorder model. Density Of States as (DOS)               |

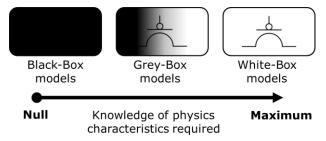

| Figure 23. Box model representation                                                                                                                      |

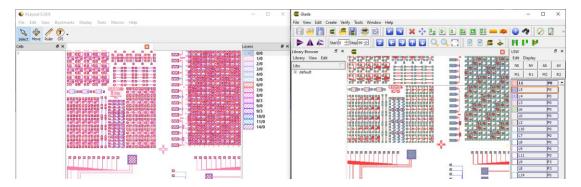

| Figure 24. KLayout (left) and Glade (right) layout tools                                                                                                 |

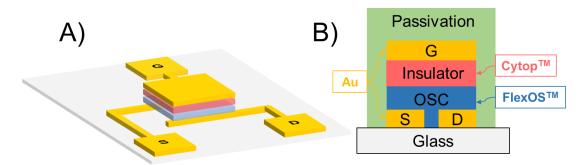

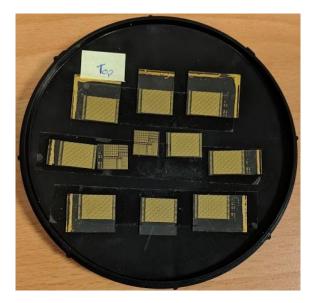

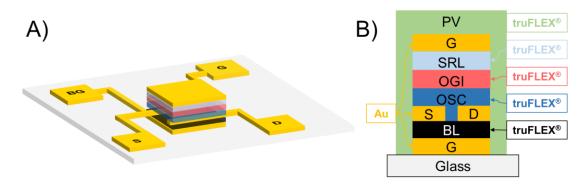

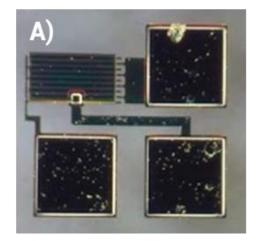

| Figure 25. A) OTFT architecture and B) stack of materials                                                                                                |

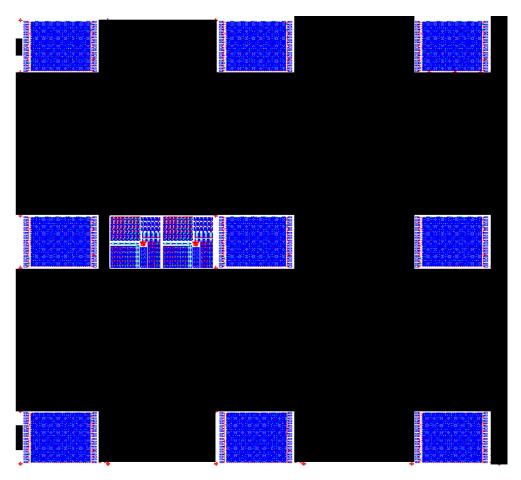

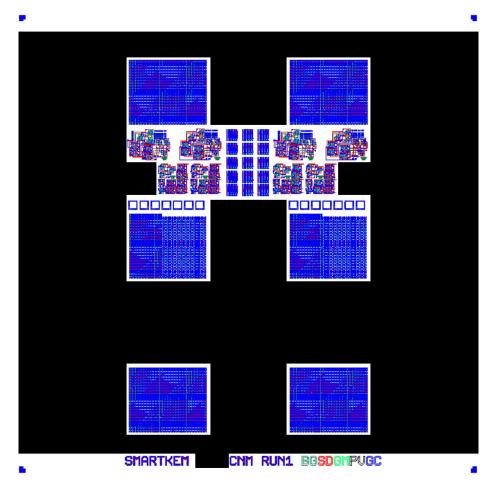

| <b>Figure 26</b> . Run layout with the 9 transistor array and two analog parts. Black areas are other systems from external designers                    |

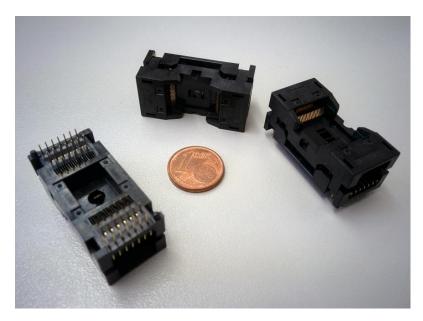

| Figure 27. Photo of the different parts of the prototyped layout 53                                                                                      |

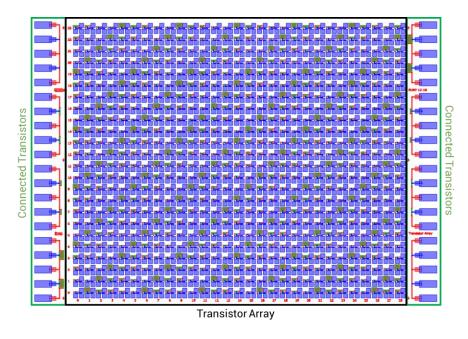

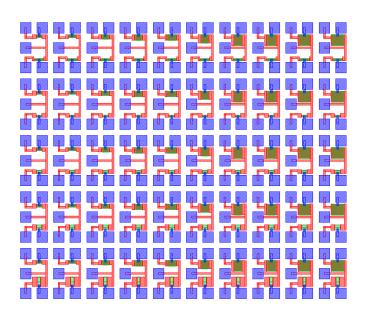

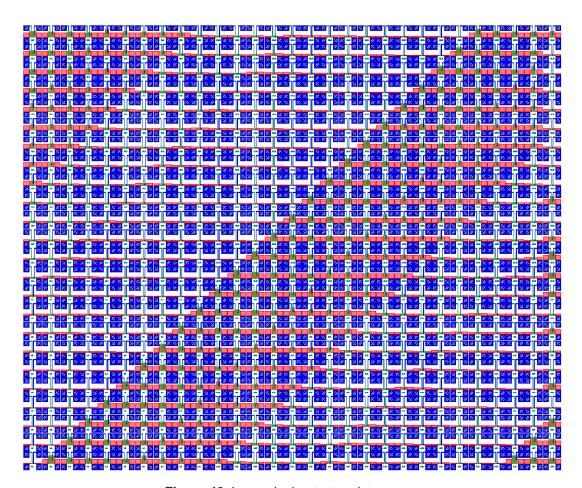

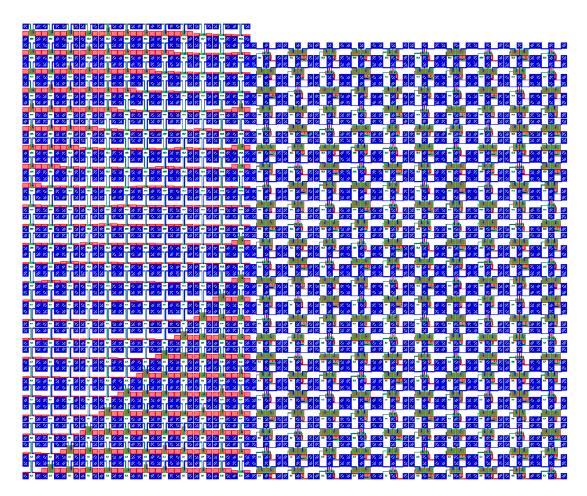

| Figure 28. Transistor array design                                                                                                                       |

| Figure 29. TSOP-4P Socket compared with 1 cent of €                                                                                                      |

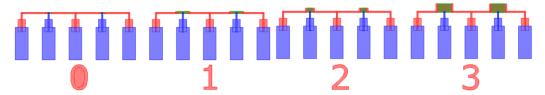

| Figure 30. Transistors with pads design for external interconnection 54                                                                                  |

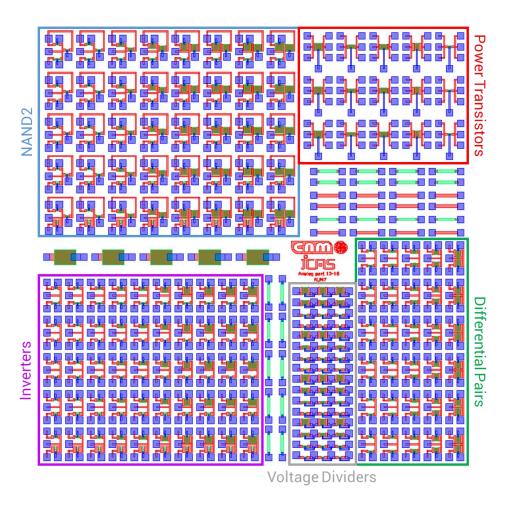

| Figure 31. Transistor array55                                                                                                                            |

| Figure 32. Array pattern sequence                                                                                                                        |

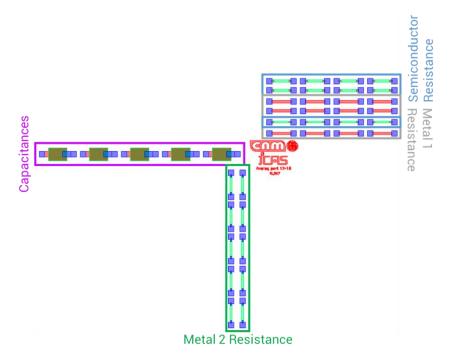

| Figure 33. Analog layout design                                                                                                                          |

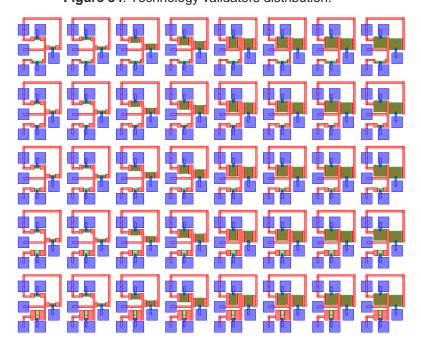

| Figure 34. Technology validators distribution                                                                                                            |

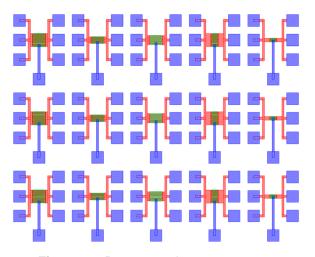

| Figure 35. NAND-2 array57                                                                                                                                |

| Figure 36. Inverter array59                                                                                                                              |

| Figure 37. Voltage reference array                                                                                                                       |

| Figure 38. Differential pair array                                                                                                                       |

| Figure 39. Power transistors array                                                                                                                       |

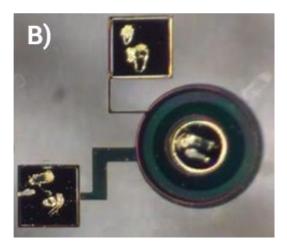

| Figure 40. A) OTFT architecture and B) stack of materials                                                                                                |

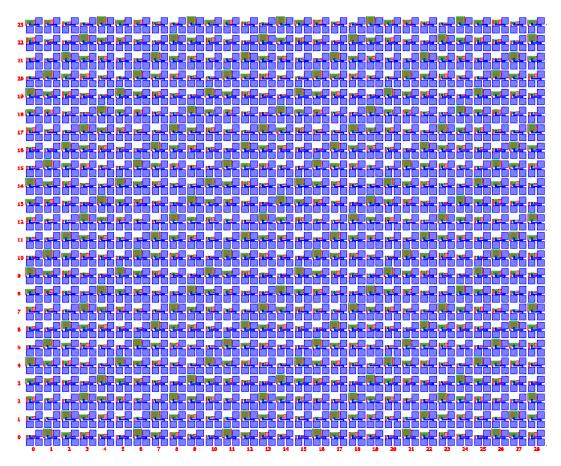

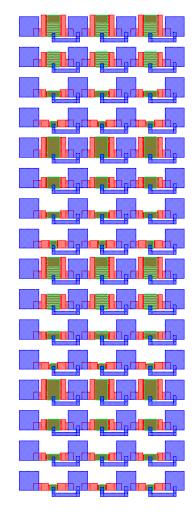

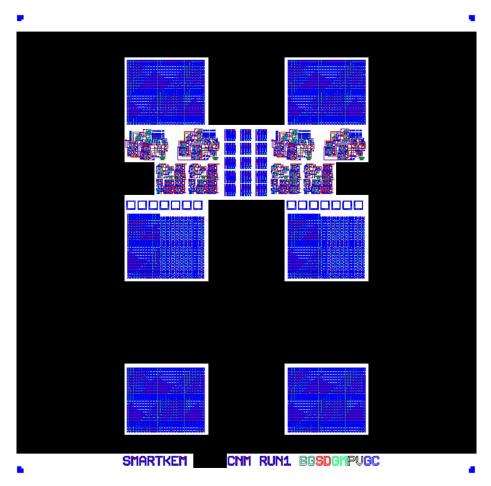

| Figure 41. Run layout with 4 large dual gate OTFT in the sides complemented with the two central arrays with individual transistors and NAND             |

| gates. DRC structures and technology validators are incorporated together with dummy hybridization pads and circuits for testing                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 42. Large dual gate transistor array 66                                                                                                                                                                     |

| Figure 43. Central array with the dual gate transistors on the right and the NAND gates on the left                                                                                                                |

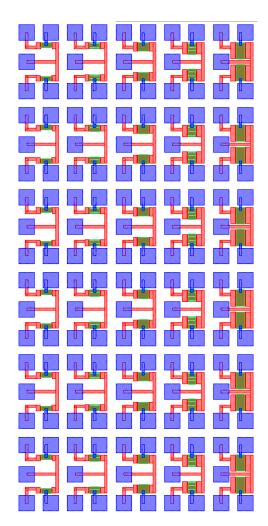

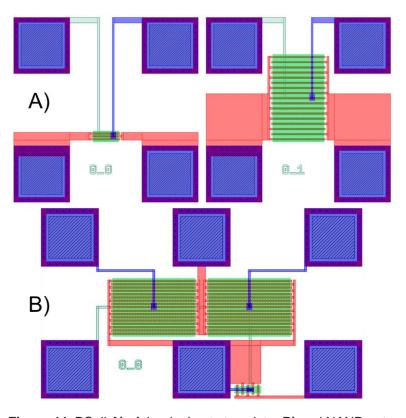

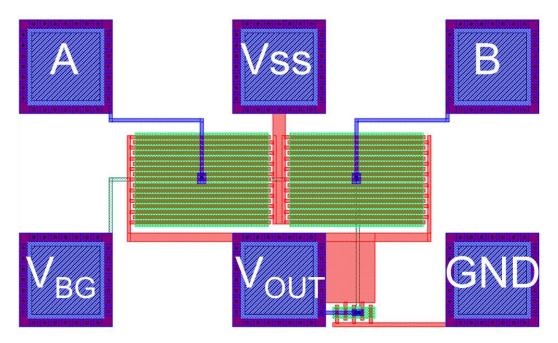

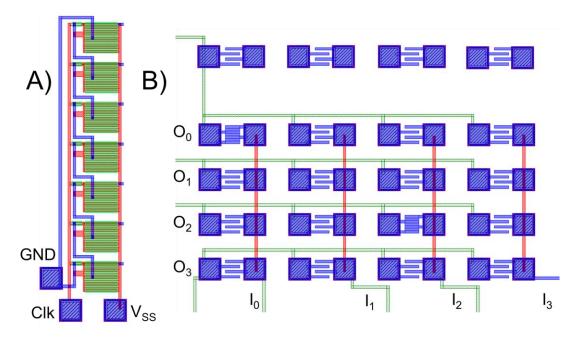

| Figure 44. PCell A) of the dual gate transistor B) and NAND gate 69                                                                                                                                                |

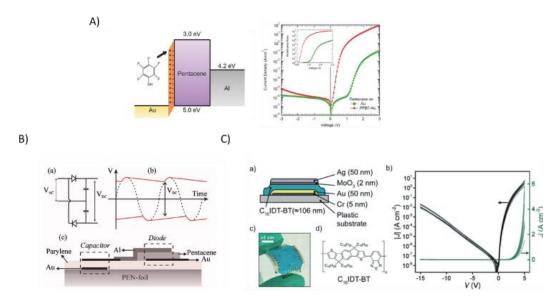

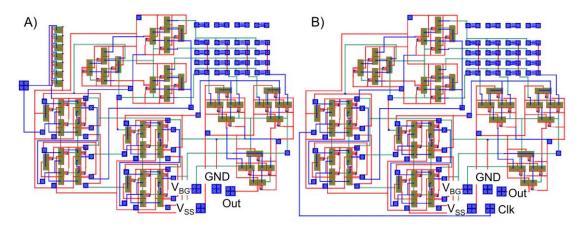

| Figure 45. A) RFID tag with ring oscillator, B) RFID tag without internal clock.                                                                                                                                   |

| Figure 46. Subcircuits designed for testing                                                                                                                                                                        |

| Figure 47. DRC structures and technology validators                                                                                                                                                                |

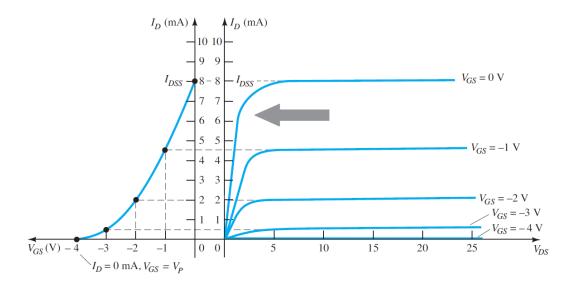

| Figure 48. Transfer and output curves of a Field Effect Transistor (FET) [15].                                                                                                                                     |

| Figure 49. Automatic characterization system schema                                                                                                                                                                |

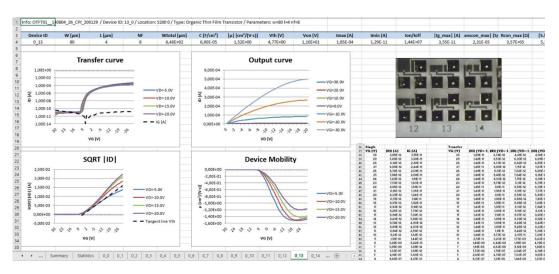

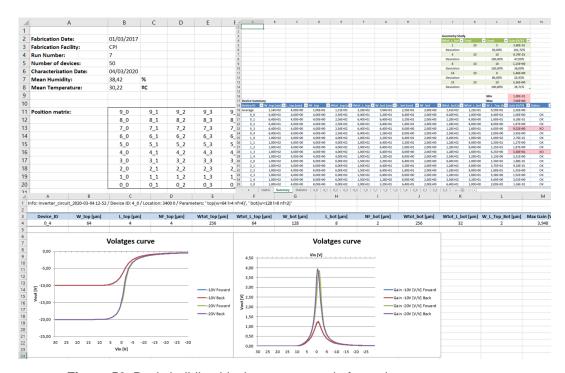

| <b>Figure 50</b> . Report example of individual transistor with graphics, images and data obtained                                                                                                                 |

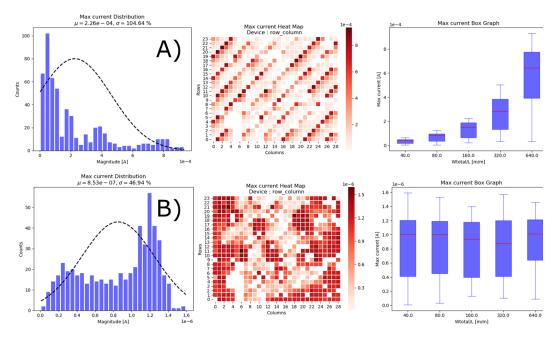

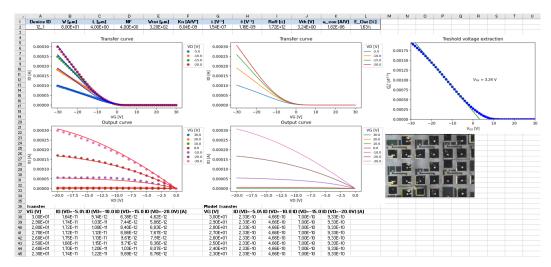

| Figure 51. A) Raw maximum current distribution row and B) Normalized by size of each device maximum current row                                                                                                    |

| Figure 52. Basic building block report example for an inverter array 80                                                                                                                                            |

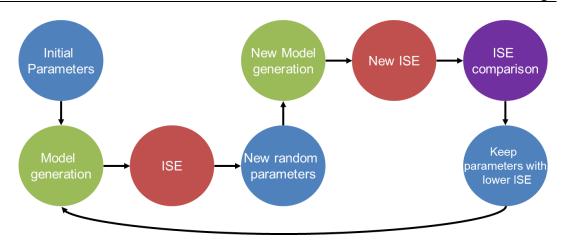

| Figure 53. Flow chart parameters optimization                                                                                                                                                                      |

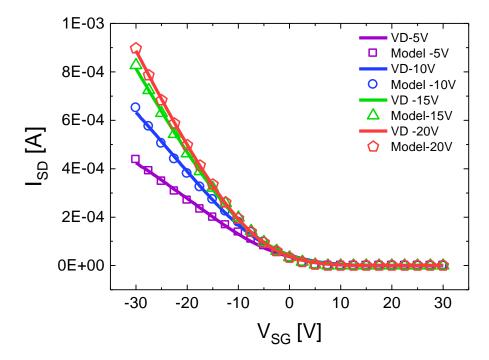

| Figure 54. Transfer curves of an OTFT for different drain potentials from experimental data (lines) and model (symbols)                                                                                            |

| Figure 55. Example of device sheet for the model report with the model parameters, the curves used for the calculation and the theoretical result 82                                                               |

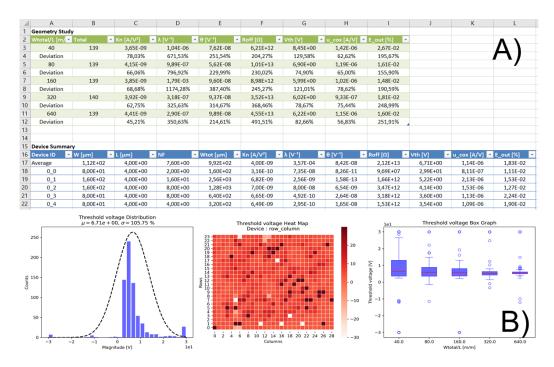

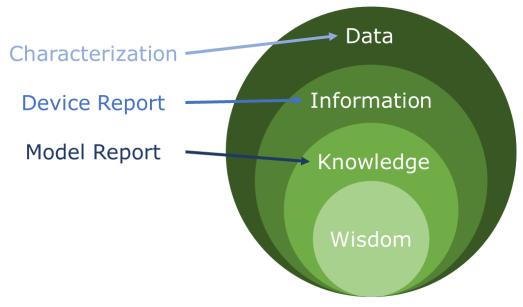

| <b>Figure 56</b> . <b>A)</b> Geometry study with device relevant parameters table and <b>B)</b> example of parameter dispersion in gaussian distribution, heat map position and size classification with box chart |

| Figure 57. Data, information, knowledge, wisdom hierarchy and their correspondence with the automated work                                                                                                         |

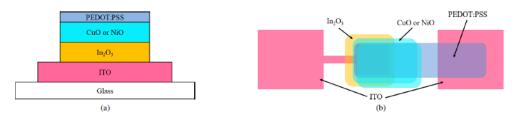

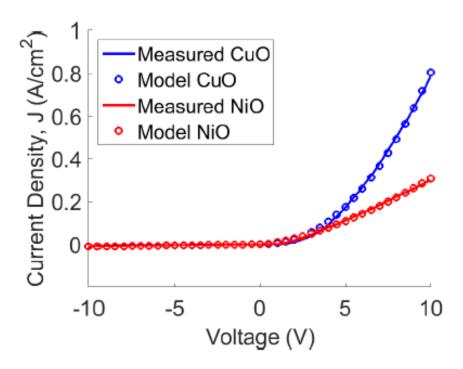

| Figure 58. A) Top and B) cross section view of a pn-diode based on oxide semiconductors [16]                                                                                                                       |

| Figure 59. Comparison between the measured and simulated diode curve.                                                                                                                                              |

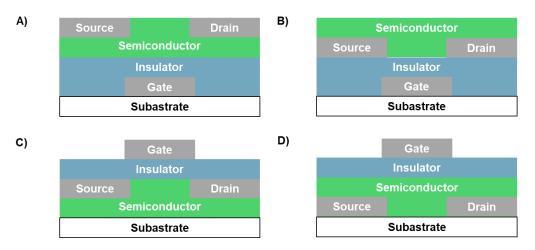

| Figure 60. A) Bottom Gate Top Contact, B) Bottom Gate Bottom Contact, C) Top Gate Top Contact and D) Top Gate-Bottom Contact                                                                                       |

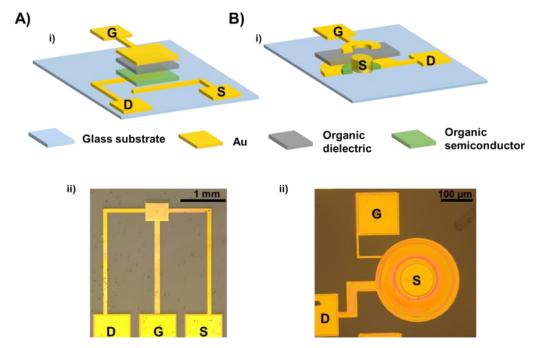

| Figure 61. A) Single gate and B) Corbino OTFT87                                                                                                                                                                    |

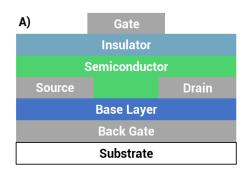

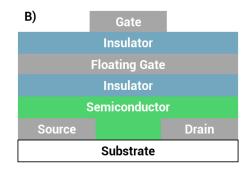

| Figure 62. A) Dual gate and B) floating gate OTFT stack                                                                                                                                                            |

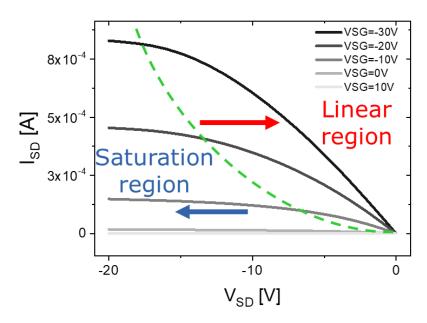

| <b>Figure 63</b> . Regions of the Shichman-Hodges Model applied to output curve of an OTFT90                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

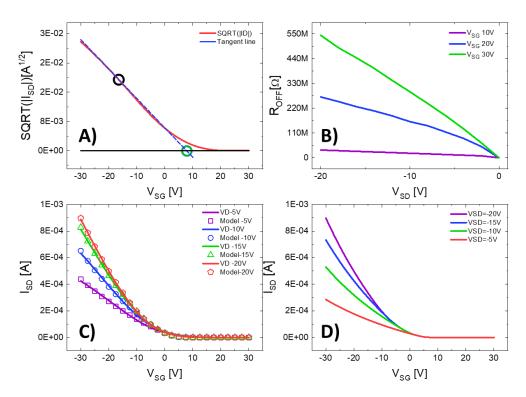

| <b>Figure 64</b> . <b>A)</b> Mobility and threshold voltage extraction <b>B)</b> off resistance depending on drain and gate potentials <b>C)</b> transfer curves with the parameter extraction model <b>D)</b> simulation in Cadence of the Verilog-A model                                             |

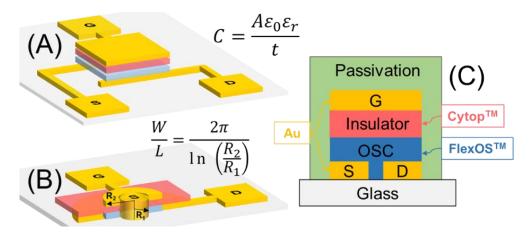

| Figure 65. Architecture of the A) Interdigitated OTFT, and B) Corbino OTFT.  C) OTFT Stack materials, common to both architectures                                                                                                                                                                      |

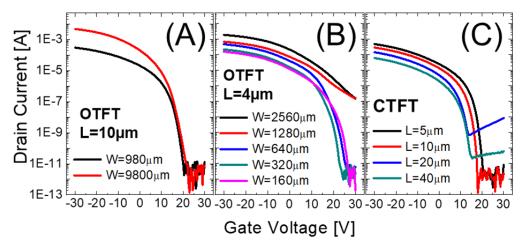

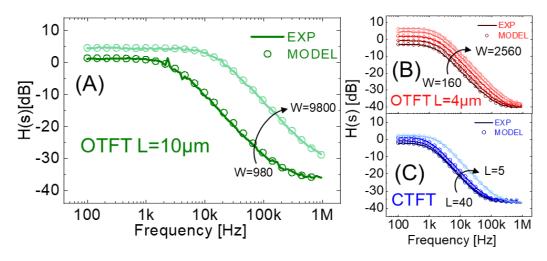

| <b>Figure 66</b> . Drain Current–Gate Voltage characteristics measured on Interdigitated OTFT with <b>A)</b> L = 10 $\mu$ m, <b>B)</b> L = 4 $\mu$ m and <b>C)</b> Corbino OTFT 93                                                                                                                      |

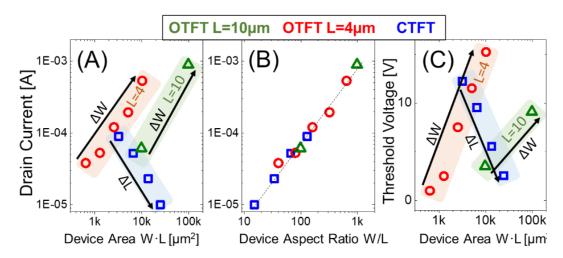

| <b>Figure 67.</b> $I_D$ as a function of <b>A)</b> the device area for OTFT and CTFT and <b>B)</b> as a function of the aspect ratio W/L. <b>C)</b> $V_T$ as a function of device area 94                                                                                                               |

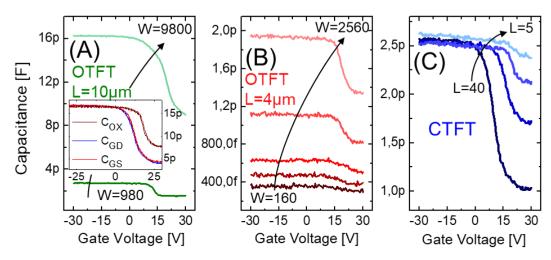

| <b>Figure 68.</b> C-V characteristic of the Gate stack for the interdigitated OTFT with <b>A)</b> L=10 $\mu$ m, <b>B)</b> with L=4 $\mu$ m, and for <b>C)</b> Corbino OTFT. The inset in <b>A)</b> shows the area dependence of the three measured capacitances                                         |

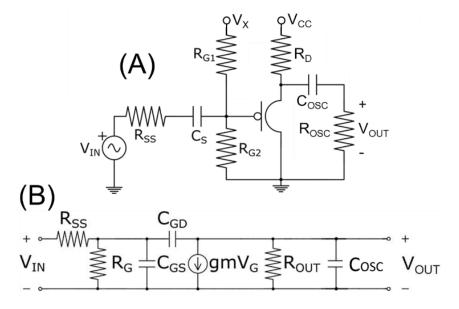

| <b>Figure 69. A)</b> Common Source (CS) amplifier implemented to evaluate the OTFT performance in the frequency domain, and <b>B)</b> small signal model for mid and high frequency regims. $R_G=R_{G1}//R_{G2}$ and $R_{OUT}=r_0//R_D//R_{OSC}$                                                        |

| Figure 70. A) Experimental (lines) and fitted (circles) frequency response for the Interdigitated OTFT with L = 10 $\mu$ m, B) Interdigitated OTFT with L = 4 $\mu$ m and C) Corbino OTFT.                                                                                                              |

| <b>Figure 71. A)</b> Analytically calculated Gate-Drain capacitance (squares), measured from the C-V curves (circles) and obtained from the data fitting (triangles). <b>B)</b> $r_0$ (empty squares) and $g_m$ (circles) obtained from the fitting 97                                                  |

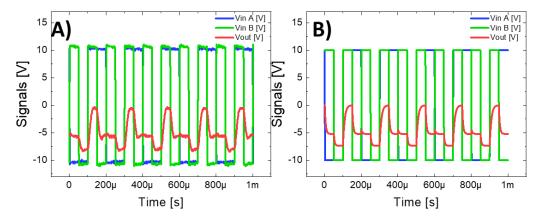

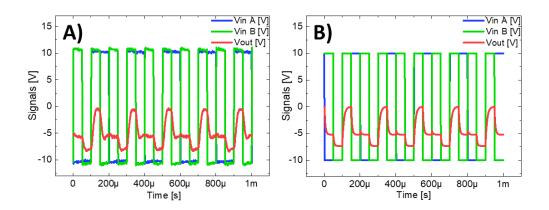

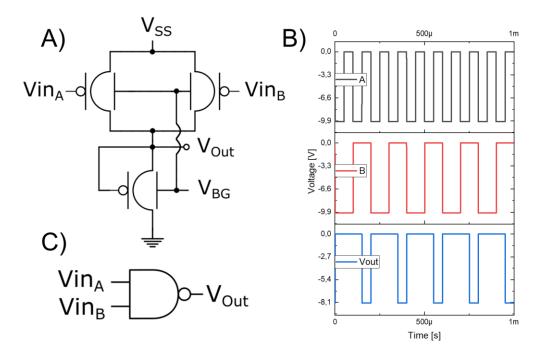

| Figure 72. Input and output signals of a NAND2 gate at 10kHz A) experimental data B) circuit simulation by using our AC signal model                                                                                                                                                                    |

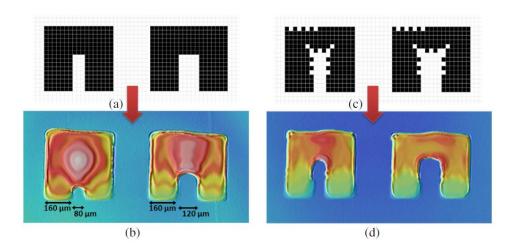

| <b>Figure 73. A)</b> Non-compensated notch pattern; <b>B)</b> 3D image of the deposited non-compensated pattern; <b>C)</b> PSC compensated notch pattern; and <b>D)</b> 3D image for PSC compensated notch rule [52]                                                                                    |

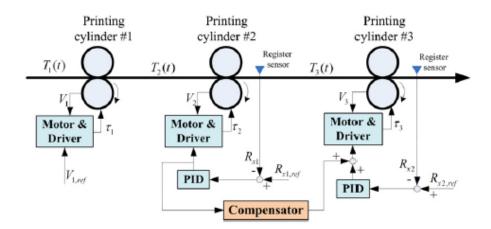

| Figure 74. Schematic of the three-layer direct gravure printing system [56].                                                                                                                                                                                                                            |

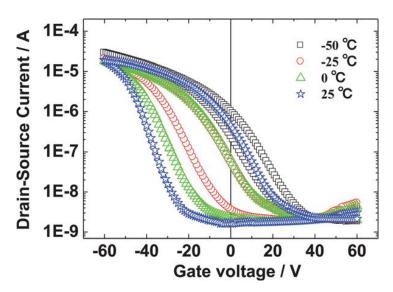

| Figure 75. Transfer characteristics of the OTFT device with PMLG as the ferroelectric layer at different temperatures [59]                                                                                                                                                                              |

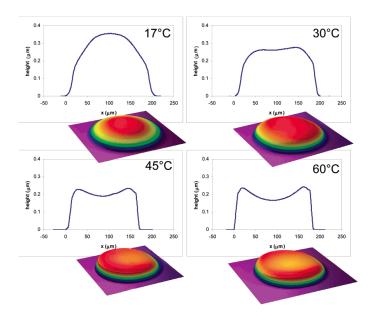

| <b>Figure 76.</b> Cross section and 3D projection from an optical profilometer of single drops printed at the noted temperatures [63]                                                                                                                                                                   |

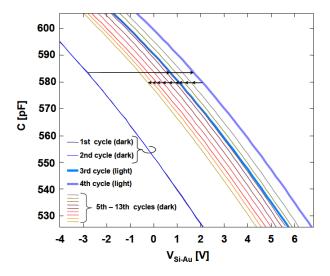

| <b>Figure 77.</b> C-Vs with negligible changes under dark 1 <sup>st</sup> and 2 <sup>nd</sup> cycle. Strong variation occurs, if the C-Vs are performed under illumination 3 <sup>rd</sup> and 4 <sup>th</sup> cycles, and progressively move to negative voltages when in dark again 5-13 cycles. [68] |

| Figure 78. RLC series description in Verilog-A                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

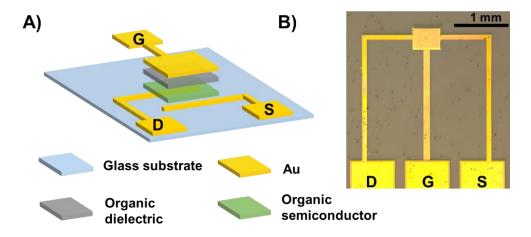

| Figure 79. A) 3D scheme of the Interdigitated geometry and B) its optical image. D, G and S refer to Drain, Gate and Source electrodes, respectively. 113                                                                                                                                                                                                                                                                                    |

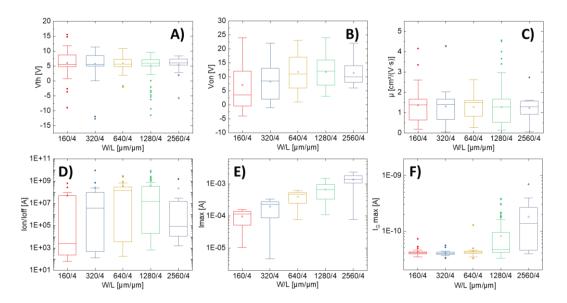

| <b>Figure 80</b> . Parameters distribution of different dimensions devices <b>A</b> ! Threshold voltage, <b>B</b> ) On voltage, <b>C</b> ) mobility <b>D</b> ) lon/loff, <b>E</b> ) Maximum drain current and <b>F</b> ) Maximum gate current. The central mark represents the median box limits indicate the 25 <sup>th</sup> and 75 <sup>th</sup> percentiles, and whiskers extend to the 5 <sup>th</sup> and 9 <sup>th</sup> percentiles. |

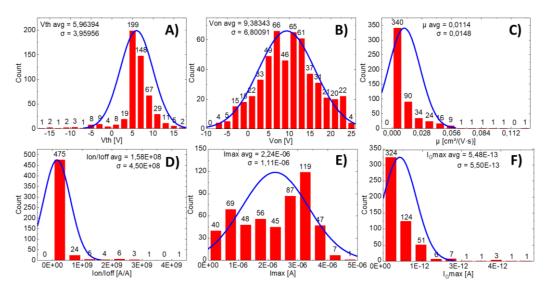

| <b>Figure 81</b> . Parameters distribution of normalized device <b>A)</b> Threshold voltage, <b>B)</b> On voltage, <b>C)</b> mobility <b>D)</b> lon/loff, <b>E)</b> Maximum drain current and <b>F</b> ) Maximum gate current                                                                                                                                                                                                                |

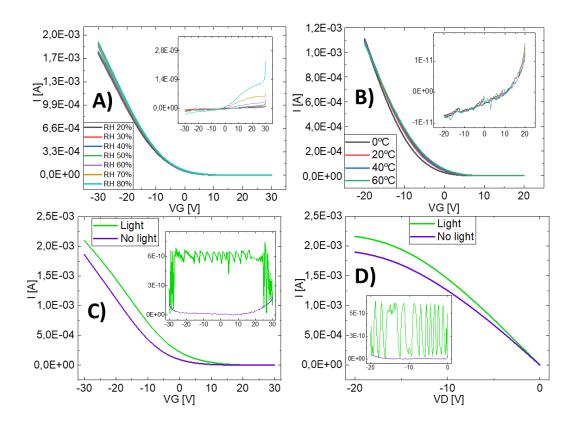

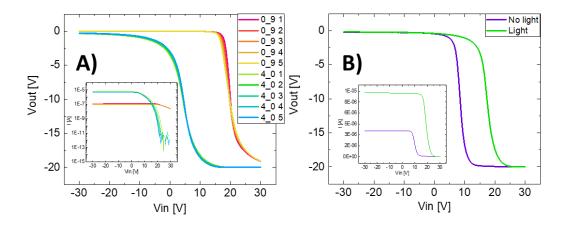

| <b>Figure 82</b> . <b>A)</b> Relative humidity comparison $V_D = -20$ V, <b>B)</b> Temperature measurement comparison VD = -15 V, <b>C)</b> Transfer curve comparison under light or no light $V_D = -20$ V and <b>D)</b> Output curve comparison under light or no light $V_C = -30$ V, all measures of the same device dimensions with $L = 4$ $\mu$ m and total W = 2560 $\mu$ m.                                                         |

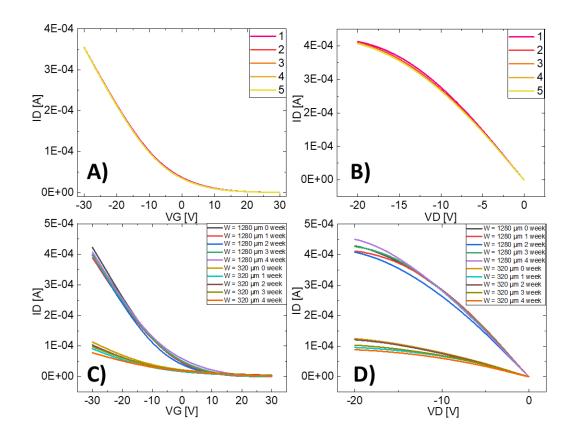

| Figure 83. A) Repetitive Transfer curve W = 1280 $\mu$ m and V <sub>D</sub> = -15 V, B) Repetitive Output curve W = 1280 $\mu$ m and V <sub>G</sub> = -30 V, C) Historic Transfer curve V <sub>D</sub> = -20 V and D) Historical output curve V <sub>G</sub> = -30 V                                                                                                                                                                         |

| <b>Figure 84</b> . <b>A)</b> Inverter repetitive measure comparison with an inset of the current behaviour and <b>B)</b> Light influence on an inverter circuit with an inset of the current behaviour with a size ratio of 5,4                                                                                                                                                                                                              |

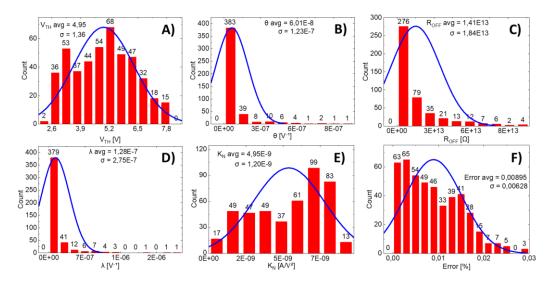

| <b>Figure 85</b> . Parameters distribution of modelled device <b>A)</b> Threshold voltage <b>B)</b> theta, <b>C)</b> off resistance <b>D)</b> lambda, <b>E)</b> Kn as the product of the device capacitance with the mobility and <b>F)</b> Relative error in respect of the experimenta data.                                                                                                                                               |

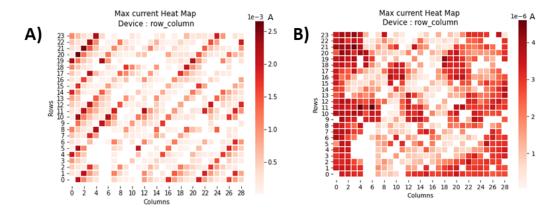

| Figure 86. A) Spatial distribution of max current and B) normalized spatial distribution of max current                                                                                                                                                                                                                                                                                                                                      |

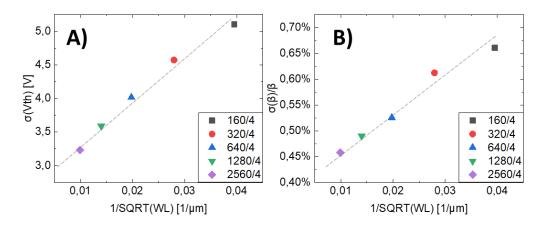

| Figure 87. A) Threshold voltage deviation and B) current factor deviation versus the square root of the inverse transistor area                                                                                                                                                                                                                                                                                                              |

| Figure 88. Input and output signals of a NAND2 gate at 10kHz A) experimental data B) circuit simulation by using our AC signal model                                                                                                                                                                                                                                                                                                         |

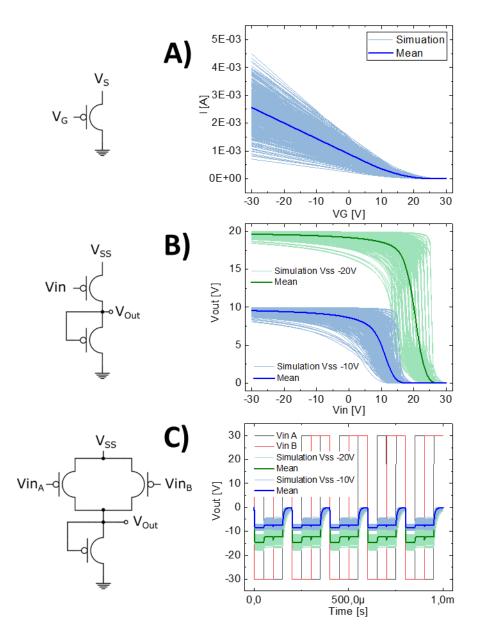

| <b>Figure 89</b> . Circuit schematics and 500 Monte Carlo simulations for OTFT <b>A)</b> inverter circuit <b>B)</b> , and NAND gate <b>C)</b> .                                                                                                                                                                                                                                                                                              |

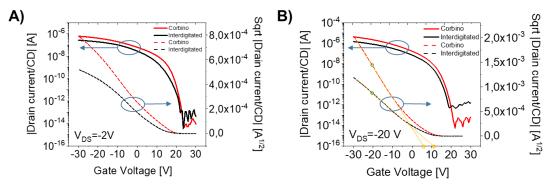

| Figure 90. Square root and logarithmic scale transfer curves of both geometries types for the two behaviour of the transistors: A) lineal region, B) saturation region including the threshold voltage extraction procedure representation.                                                                                                                                                                                                  |

| <b>Figure 91</b> . <b>A)</b> i) 3D scheme of the Interdigitated geometry and ii) its optical image; <b>B)</b> 3D scheme of the Corbino geometry and ii) its optical image. D, G and S refer to drain, gate and source electrodes, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

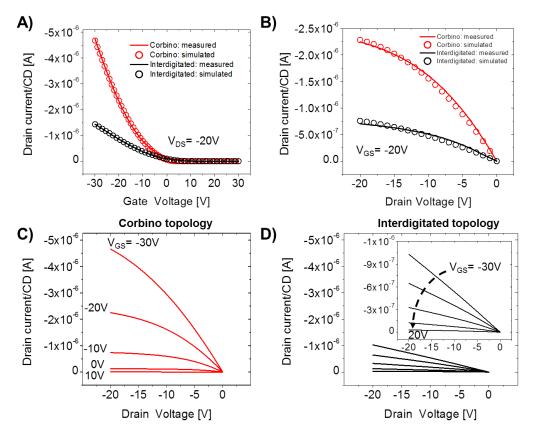

| <b>Figure 92</b> . Experimental transfer <b>A)</b> and output <b>B)</b> characteristics for Corbino and interdigitated geometries normalized to Channel Dimension (CD) for $V_{DS} = -20$ V and $V_{GS} = -20$ V, respectively. The circular symbol refers to the theoretical transfer and output characteristics simulated by using a MOSFET level 3. <b>C</b> Experimental output characteristics of Corbino geometry devices. <b>D</b> Experimental output characteristics of interdigitated geometry devices where gate voltage (V <sub>GS</sub> ) was swept by $-10$ V from $-30$ V to $20$ V. The output graph for interdigitated geometry is rescaled in the inset graph for better comparison. The channel length is 4 μm and 20 μm for interdigitated and the Corbino devices respectively. Both have almost the same W/L ratio |

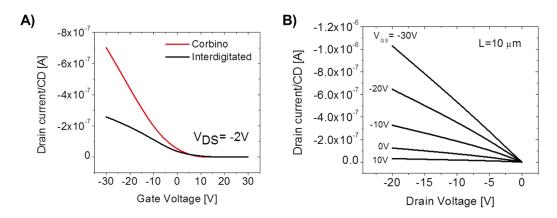

| Figure 93. A) Experimental transfer characteristics for Corbino and interdigitated geometries normalized to Channel Dimension (CD) for $V_{DS}$ = -2 V B) Experimental output characteristics of interdigitated geometry devices where gate voltage ( $V_{GS}$ ) were swept by -10 V from -30 V to 10 V. The channel length is 10 $\mu$ m.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

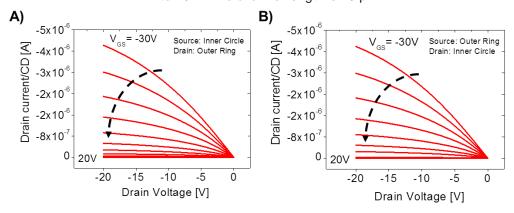

| <b>Figure 94.</b> Output characteristics of the Corbino TFT for the two drain-bias conditions: <b>A)</b> inner circle as source and outer ring as drain, <b>B)</b> inner circle as drain and outer ring as source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>Figure 95</b> . Electrical parameters such as <b>A)</b> threshold voltage, <b>B)</b> effective hole mobility and <b>C)</b> $I_{ON}/I_{OFF}$ ratio for Corbino and interdigitated geometries. The central mark represents the median, box limits indicate the 25 <sup>th</sup> and 75 <sup>th</sup> percentiles, and whiskers extend to the 5 <sup>th</sup> and 9 <sup>th</sup> percentiles. <b>D)</b> Differential output conductance as a function of drain voltage at $V_{GS} = -30 \text{ V}$                                                                                                                                                                                                                                                                                                                                      |

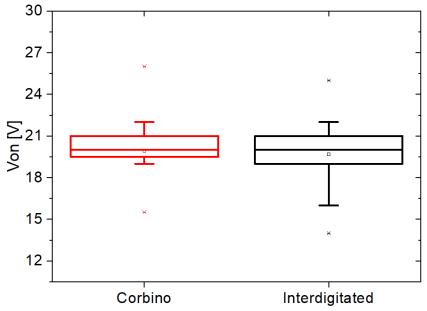

| <b>Figure 96</b> . Turn on voltage of both geometries from the curve transfer curve with $V_{DS}$ = -20 V. Central mark the median, box limits indicates the 25th and 75th percentiles, whiskers extend to 5th and 9th percentiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>Figure 97. A)</b> Inverter circuits by using different combinations of transistor geometries: <b>B)</b> Voltage transfer characteristics (VTC); <b>C)</b> and gain. <b>D)</b> VTC for Inv A geometry with a ratio 8:1; and <b>E)</b> the respective gain. "F" and "B" denote forward and backward sweeps, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

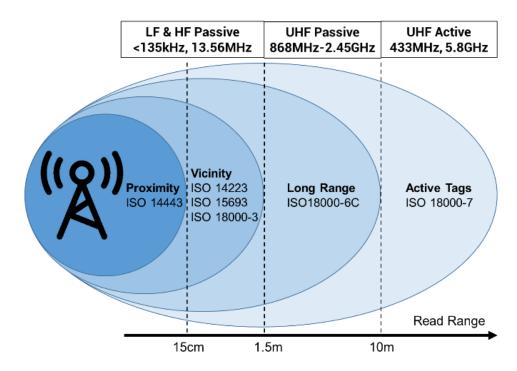

| Figure 98. RFID protocols classification with reading distance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 99. Implementation of the 12-bit code generator as ROM memory [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 100. Flexible point-of-care system with reading/feeding by NFC and presentation of results on electrochromic display [11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

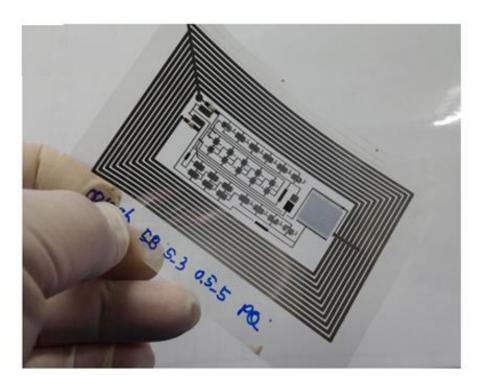

| Figure 101. Some examples of NFC tags reported by IMEC [12] 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

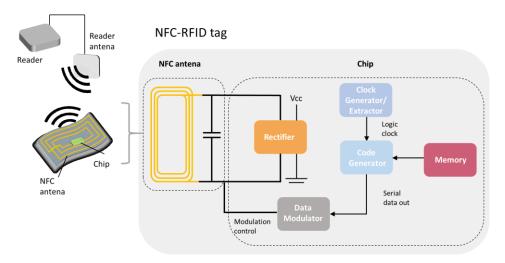

| Figure 102 Basic blocs of a passive RFID tag and their workflow 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

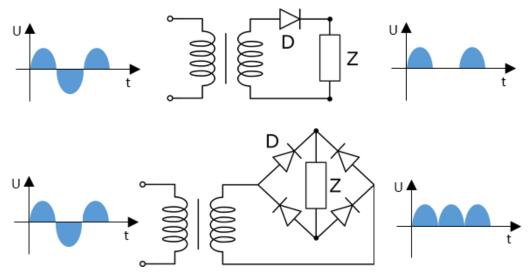

| Figure 103. A) Half-wave rectifier B) Full wave rectifier                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 104. Different configuration of organic and flexible diodes [16] 152                                                                                                               |

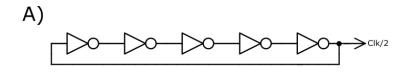

| Figure 105. Different architectures for clock signal generation, A) ring oscillator, B) frequency divider                                                                                 |

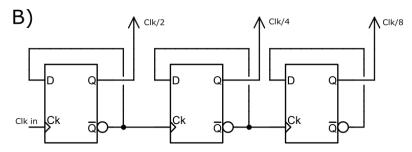

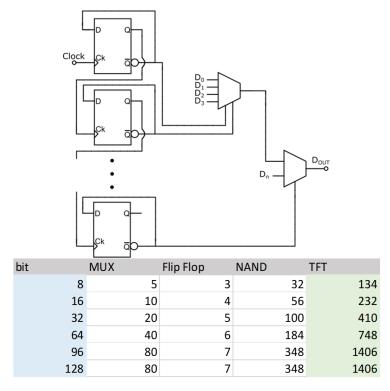

| Figure 106. PISO code generator and a table of the transistor scaling with the bits                                                                                                       |

| Figure 107. Counter and multiplexer architecture for the code generator                                                                                                                   |

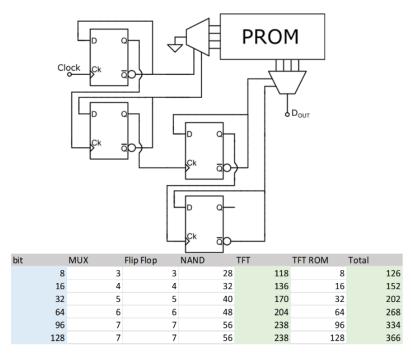

| Figure 108. Counter and PROM architecture for the code generator 155                                                                                                                      |

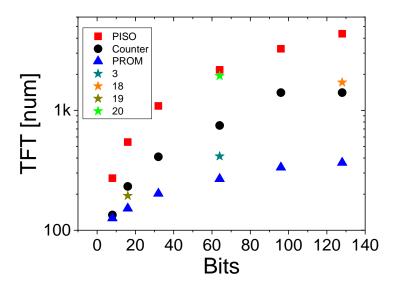

| Figure 109. Benchmark of the architectures                                                                                                                                                |

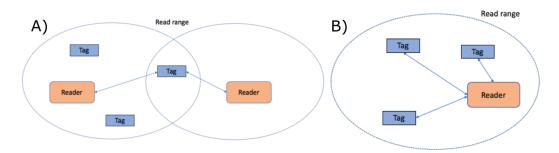

| Figure 110. A) Reader collision B) Tag collision [22]                                                                                                                                     |

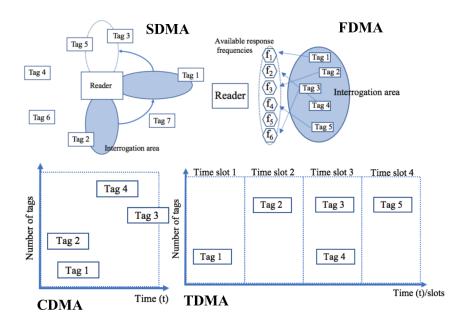

| Figure 111. Four types of tag anticollision, SDMA, FDMA, CDMA and TDMA157                                                                                                                 |

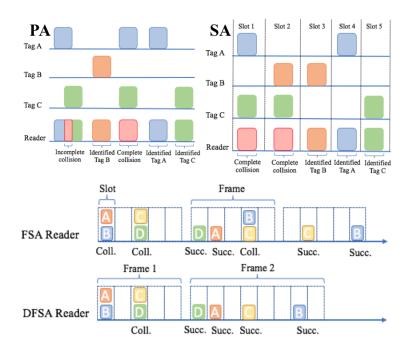

| Figure 112. Different aloha protocols represented on how they work. Table with comparison of characteristics of the protocols                                                             |

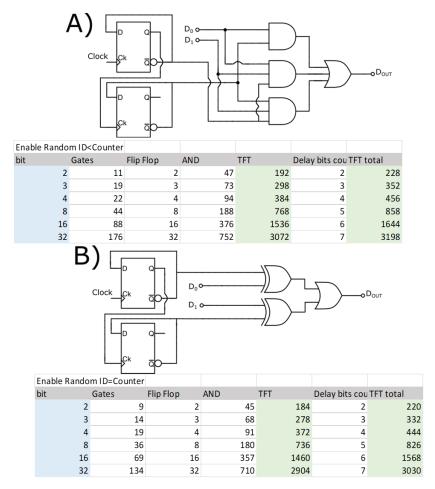

| <b>Figure 113. A)</b> Delay generator comparator for tag ID < than counter B) Delay generator comparator for tag ID = than counter                                                        |

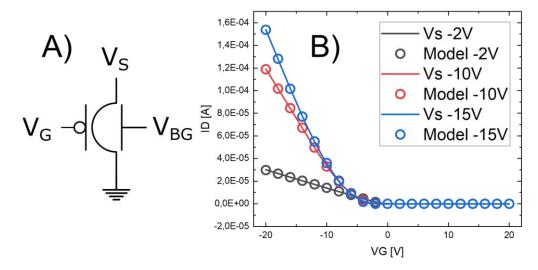

| <b>Figure 114. A)</b> Dual gate OTFT schematic, <b>B)</b> Experimental (line) vs mode (dots) transfer curve, back gate biased at -2 V                                                     |

| <b>Figure 115. A)</b> NAND Gate with 2 inputs with common back gate, <b>B</b> ) simulations results of NAND gate for a back gate of -2 V and Vss of -10 V and <b>C</b> ) NAND gate symbol |

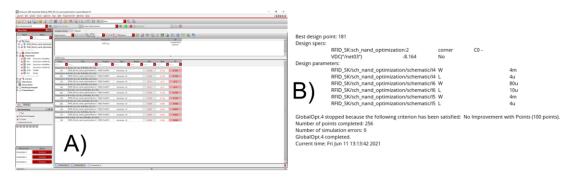

| Figure 116. A) Results of the global optimization of device geometries and B) work report                                                                                                 |

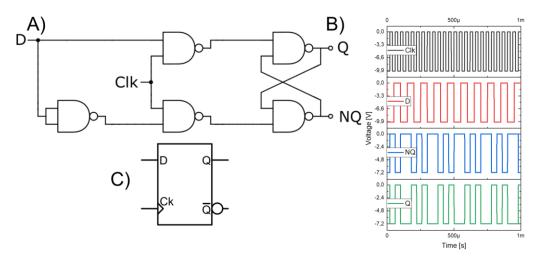

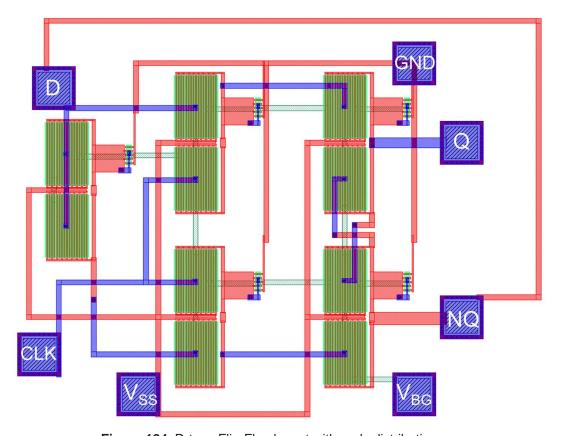

| Figure 117. A) Flip-Flop type D with NAND gates, B) circuit simulation results and C) circuit symbol                                                                                      |

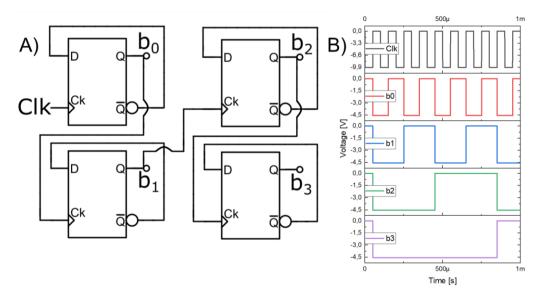

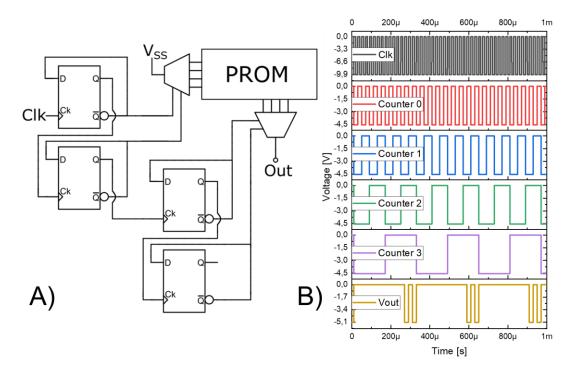

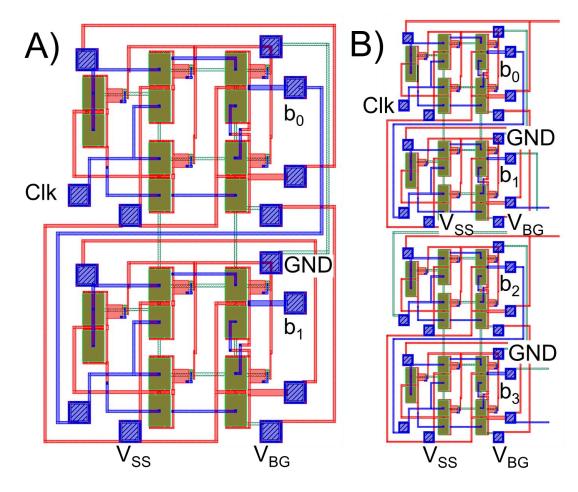

| Figure 118. A) 4-bit counter based on D type Flip-Flops and B) circuit simulation results                                                                                                 |

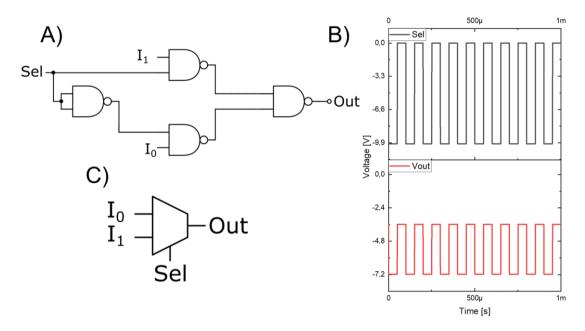

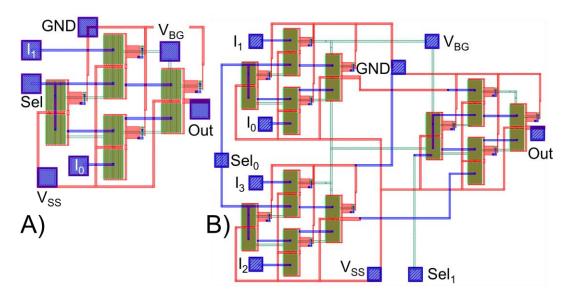

| Figure 119. A) Two input multiplexer based on NAND gates, B) circuit simulation results and C) circuit symbol                                                                             |

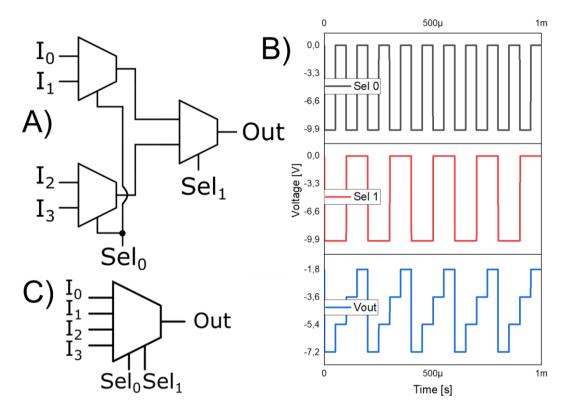

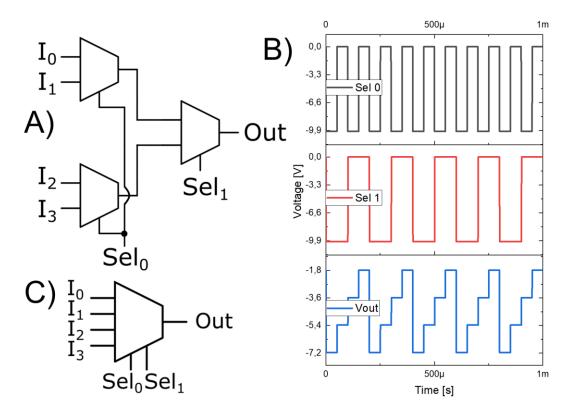

| <b>Figure 120. A)</b> Four input multiplexer based on two input multiplexers, <b>B</b> ) circuit simulation results and <b>C)</b> circuit symbol                                          |

| <b>Figure 121. A)</b> Four output demultiplexer based on two output demultiplexers, <b>B)</b> circuit simulation results and <b>C)</b> circuit symbol                                     |

| Figure 122. A) Final schematic of 16 bits RFID and B) Simulation of the final system                                                                                                      |

| Figure 123. NAND gate layout with pads distribution                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 124. D-type Flip-Flop layout with pads distribution                                                                                                                                                                                                                            |

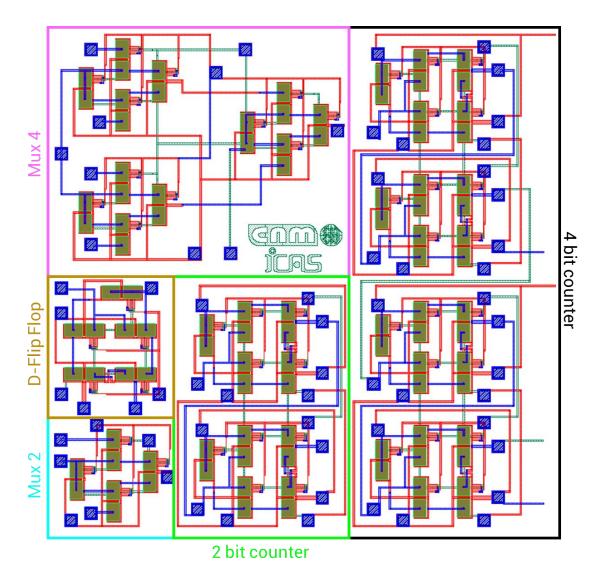

| Figure 125. A) 2-bit counter layout and B) 4-bit counter layout 167                                                                                                                                                                                                                   |

| Figure 126. A) 2-input multiplexer layout and B) 4-input multiplexer layout                                                                                                                                                                                                           |

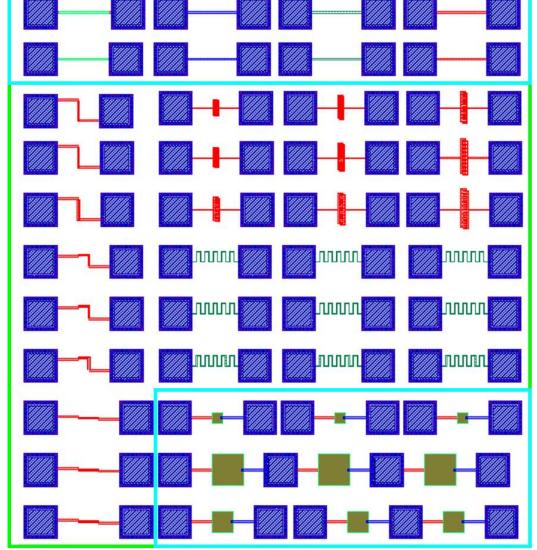

| Figure 127. A) 7 stage ring oscillator and B) Inkjet PROM                                                                                                                                                                                                                             |

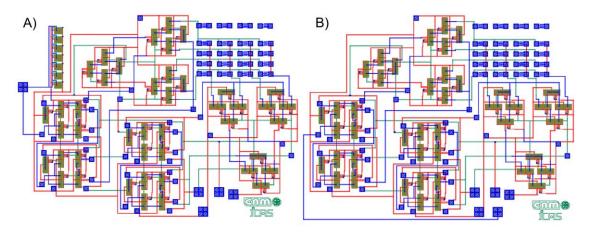

| Figure 128. A) 16-bit RFID system layout with internal clock and B) 16 bit RFID system layout with external clock                                                                                                                                                                     |

| <b>Figure 129.</b> Run layout with 4 large dual gate OTFT in the sides complemented with the two central arrays with individual transistors and NANE gates. DRC structures and technology validators are incorporated together with dummy hybridization pads and circuits for testing |

# **List of Tables**

| Table 1. Organic Circuits and Systems simulated and fabricated                                                      |

|---------------------------------------------------------------------------------------------------------------------|

| Table 2. PDKs developed for organic and printed electronics         31                                              |

| Table 3. Compact models for organic devices.    36                                                                  |

| Table 4. Transistors with pads dimensions.    54                                                                    |

| Table 5. Array transistor dimensions.    56                                                                         |

| Table 6. NAND-2 load transistor dimensions.    58                                                                   |

| Table 7. NAND-2 input transistors dimensions.    58                                                                 |

| Table 8. Inverter input transistors dimensions.    59                                                               |

| Table 9. Inverter load transistors dimensions.    60                                                                |

| Table 10. Voltage reference transistors dimensions.    61                                                           |

| Table 11. Differential pair transistor dimensions.    61                                                            |

| Table 12. Power transistor dimensions.    63                                                                        |

| Table 13. Large array of dual gate transistors dimensions.    66                                                    |

| Table 14. NAND-2 input dual gate transistors dimensions.    68                                                      |

| Table 15. NAND-2 load dual gate transistors dimensions.    69                                                       |

| Table 16. Extracted PN-Diode parameters                                                                             |

| Table 17. Comparison of different topologies of OTFT design styles for basic           nverters with key parameters |

### **Glossary**

AC Alternating Current

**ALU** Arithmetic Logic Unit

AMS Analog and Mixed Signal

**BB** Black Box

**BGBC** Bottom Gate Bottom Contact

**BGTC** Bottom Gate Top Contact

**CANCER** Computer Analysis of Nonlinear Circuits, Excluding Radiation

**CD** Channel Dimension

**CDMA** Code Division Multiple Access

**CMOS** Complementary Metal Oxide Semiconductor

**CNM** Centro Nacional de Microelectrónica

**CRC** Cyclic Redundancy Check

**CS** Common Source

**CSIC** Consejo Superior de Investigaciones Científicas

**CTFT** Corbino Organic Thin Film Transistor

**CuO** Copper Oxide

**C-V** Capacitance Voltage

**DC** Direct Current

**DFSA** Dynamic Frame Slotted Aloha

**DIKW** Data, Information, Knowledge and Wisdom

**DOD** Drop On Demand

**DOS** Density Of States

**DRC** Design Rules Check

**EDA** Electronic Design Automation

**EGOTFT** Electrolyte Gated OTFT

**ERC** Electrical Rule Check

**FDMA** Frequency Division Multiple Access

**FET** Field-Effect Transistor

**FSA** Frame Slotted Aloha

**GB** Gray Box

**GPIB** General-Purpose Instrumentation Bus

**HF** High Frequency

IC Integrated Circuit

ICAS Circuitos Integrados y Sistemas

**ID** Identification

IEC International Electrotechnical Commission

**IEEE** Institute of Electrical and Electronics Engineers

**IMB** Institut de Microelectrònica de Barcelona

**IoT** Internet of Things

**ISE** Integral Square Error

**ISO** International Organization for Standardization

ITO Indium Tin Oxide

I-V Current Voltage

KIT Karlsruher Institut für Technologie

KIT Karlsruher Institut für Technologie

**LED** Light Emitting Diode

**LF** Low Frequency

LSB Less Significant Bit

**LVS** Layout Versus Schematic

MAPE Mean Absolute Percentage Error

MASE Mean Absolute Scaled Error

MIS Metal-Insulator-Semiconductor

MNR Meyer Neldel Rule

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MS Metal-Semiconductor

MSE Mean Squared Error

MTR Multiple Trapping and Release

**NFC** Near Field Communication

NiO Nickel Oxide

NTU Nanyang Technological University

**OE** Organic Electronics

**OGI** Organic Gate Insulator

**OLED** Organic Light-Emitting Diode

**OPDK** Organic Process Design Kit

**OPV** Organic Photovoltaics

**OSC** Organic Semiconductor

**OTFT** Organic Thin Film Transistor

P&R Place and Route

PA Pure Aloha

**PCell** Parametric Cell

**PDK** Process Design Kit

PE Printed Electronics

**PEX** Parasitic parameter Extraction

PISO Parallel Input and Serial Output

**POC** Point-Of-Care

**PROM** Programmable Read Only Memory

**RFID** Radio Frequency Identification

**RH** Relative Humidity

**RLC** Resistance, Inductance and Capacitance

**RMSE** Root Mean Square Error

**ROM** Read Only Memory

**RSD** Relative Standard Deviation

**RTL** Register-Transfer Level

SA Slotted Aloha

**SAM** Self-Assembled Monolayer

**SDMA** Space Division Multiple Access

**SGT** Source Gated Transistors

**SMAPE** Symmetric Mean Absolute Percentage Error

**SMU** Source Measure Unit

**SPI** Standard Commands for Programmable Instruments

**SPICE** Simulation Program with Integrated Circuits Emphasis

**SRL** Sputter Resistant Layer

**TDMA** Time Division Multiple Access

**TFT** Thin Film Transistor

**TGBC** Top Gate Bottom Contact

**TGTC** Top Gate Top Contact

**UHF** Ultra High Frequency

**UOTFT** Universal Organic Thin Film Transistor

**UV** Ultraviolet

VRH Variable Range Hopping

VTC Voltage Transfer Characteristics

**WB** White Box

### List of symbols

A Area

*b*<sub>0</sub> Bit at LSB position

C Capacitance

$C_{GD}$  Gate drain capacitance

C<sub>GS</sub> Gate source capacitance

C<sub>ins</sub> Insulator capacitance

$C_{OX}$  Gate capacitance

E<sub>C</sub> Conduction band

*E*<sub>D</sub> Electron donor

*E<sub>F</sub>* Fermi level

$E_V$  Valence band

*g*<sub>DS</sub> Output Conductance

$g_m$  Transconductance

GND Ground

*I*<sub>0</sub> Input at LSB position

$I_D$  Drain current

ION/IOFF On/off current ration

I<sub>SD</sub> Source drain current

$J_D$  Current density

*J*<sub>S</sub> Saturation current density

L Channel length

*n* Free electron concentration

*NF* Number of fingers

*n<sub>i</sub>* Intrinsic carrier concentration

O<sub>0</sub> Output at LSB position

p Free hole concentration

*r*<sub>0</sub> Output resistance

R<sub>1</sub> Interior Corbino radius

R<sub>2</sub> Exterior Corbino radius

*R*<sub>D</sub> Drain resistance

R<sub>OFF</sub> Off resistance

R<sub>OSC</sub> Semiconductor resistance

*R*<sub>OUT</sub> Output resistance

R<sub>S</sub> Source resistance

SS Subthreshold slope

*t*<sub>ins</sub> Insulator thickness

$V_{BG}$  Back gate voltage

$V_D$  Drain voltage

*V*<sub>G</sub> Gate voltage

$V_{IN}$  Input voltage

*V<sub>OUT</sub>* Output voltage

$V_{SD}$  Source drain voltage

$V_{SG}$  Source gate voltage

$V_{SS}$  Supply voltage

$V_T$  Threshold voltage

$V_{TH}$  Thermal voltage

W Channel width

$\Delta L$  Channel length reduction

$\varepsilon_0$  Vacuum permittivity

$\varepsilon_R$  Relative permittivity or dielectric constant

$\eta$  Diode emission coefficient

λ Channel length modulation

$\mu$  Device mobility

$\mu_{\it eff}$  Device effective mobility

$\mu_{lin}$  Device linear mobility

$\mu_{sat}$  Device saturation mobility

$\phi$  Surface inversion potential

# Dissertation Summary

The competition in the electronics field had led the industry to achieve high level of optimization in device manufacturing and performance, with extreme device density for offering products with a reduced cost. Regards the optimization work in all the different areas, the silicon electronics devices still require of expensive fabrication techniques and materials. This situation has limited the development of very cheap electronic solutions and large area electronics devices.

# 1.1 Objectives of the thesis

Currently, Organic Electronics (OE) manufacturing technologies still lack standardized procedures, despite the fact that the Institute of Electrical and Electronics Engineers (IEEE) and International Electrotechnical Commission (IEC) are promoting the development of methodologies for this technology. This absence of standardization is also present in the design flow step, where different Electronic Design Automation (EDA) tools and models have worked successfully following the same methodology as in silicon-based technology.

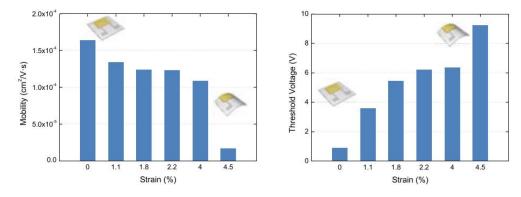

EDA tools have been the base for the current microelectronic industry since they have allowed the design of more and more complex systems that include a massive number of devices, in a reduced design time. The methodology of EDA tools can be implemented independently of the manufacturing technology used, and thus, for this reason, EDA tools have been widely standardized. Process Design Kits (PDK) are developed for connecting the EDA tools with the fabrication techniques using a set of data files, libraries, scripts, and rule sets containing the

specific information of the fabrication and technology used. Based on this, the PDKs provides inputs for supporting the different layers of the EDA software.

The main objectives of this thesis are the modelling and layout design of organic devices for an automatic PDK generation. Focusing to develop a reliable automatized system and a robust model for circuit design that allows a continuous evolution of the models with a minimum effort, different sub-objectives had been identified and defined:

- Elaboration of automatic methodologies and tools for the characterization of electronic devices with the extraction of key parameters for the generation of compact models for circuit simulation. Moreover, automatic methods for layout design should be included.

- Study of the parameter variability and degradation of the Organic Thin Film Transistors (OTFT) and other electronic devices for compact model support. These devices parameters have not been well studied in this type of devices and variability, degradation over time and variation respect to environmental conditions (light, temperature or humidity) need to be investigated.

- Development of an industrial compact model for the OTFT device with Alternating Current (AC) and Direct Current (DC) behaviour including parameter variability and the and non-idealities presented by the devices.

- Implementation of alternative design strategies for the realization of reliable circuits with devices of high variability.

- Design of systems based on organic electronics for the realization of analog and digital circuits with the models and design strategies developed.

# 1.2 List of publications

During the elaboration of this thesis different publications in journals, conferences and collaborations had been done:

- **A. Arnal**, L. Terés, and E. Ramon, "Organic and printed process design kits: review, analysis and comparison," *Flex. Print. Electron.*, vol. 6, no. 3, p. 33001, 2021, doi: 10.1088/2058-8585/ac1d39.

- A. Arnal, A. Crespo-Yepes, E. Ramon, L. Terés, R. Rodríguez, and M. Nafría, "DC characterization and fast small-signal parameter extraction of organic thin film transistors with different geometries," *IEEE Electron Device Lett.*, vol. 41, no. 10, pp. 1–1, 2020, doi: 10.1109/led.2020.3021236.

- A. Arnal, C. Martínez-Domingo, S. Ogier, L. Terés, and E. Ramon, "Monotype Organic Dual Threshold Voltage Using Different OTFT Geometries," *Crystals*, vol. 9, no. 7, p. 333, 2019, doi: 10.3390/cryst9070333.

- A. Arnal, L. Terés, and E. Ramon, "An organic process design kit, from characterization to modelling and simulation," Proc. 2020 IEEE 8th Electron. Syst. Technol. Conf. ESTC 2020, 2020, doi: 10.1109/ESTC48849.2020.9229883.

- G. C. Marques, A. M. Sukuramsyah, A. Arnal, S. Bolat, A. Aribia, X. Feng,S. A. Singaraju, E. Ramon, Y. Romanyuk, M. Tahoori and J. Aghassi-Hagmann "Fabrication and Modeling of pn-Diodes Based on Inkjet Printed Oxide Semiconductors," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 187–190, 2020, doi: 10.1109/LED.2019.2956346.

- G. C. Marques, A. Birla, A. Arnal, S. Dehm, E. Ramon, M. B. Tahoori and J. Aghassi-Hagmann, "Printed Logic Gates Based on Enhancement- And Depletion-Mode Electrolyte-Gated Transistors," *IEEE Trans. Electron Devices*, vol. 67, no. 8, pp. 3146–3151, 2020, doi: 10.1109/TED.2020.3002208.

#### 1.3 Thesis outline

Following the objectives that steered the course of this thesis, the dissertation is organized in seven different chapters summarized below.

- Dissertation Summary: provides a brief introduction of the organization, scientific contributions, work done and the different activities and rewards connected with this thesis.

- 2. State of the Art: is devoted to introduce the basics of the organic electronics field involving the materials, fabrication techniques and main applications. Moreover, this chapter also provides a background to the automation system basics combined with processes design kit needs.

- 3. Layout Design: focused on the automation of the layout step based on Parametric Cells (PCells) and the different EDA tools for layout verification and the development of a layout means different technology validators and test structures implemented in two different layout editors and manufacturers.

- 4. Device Modelling: the chapter involves the basis of characterization and modelling techniques used and how this is implemented in the developed automatic characterization system and the automatic modelling procedure with the organic devices. The methodology involves the DC and AC parameter extraction and is resumed in automatic generated reports.

- 5. Device Simulation: Ambient and variability parameters are extracted and based on the industrial model generated devices and circuits are simulated under different circumstances. The model is used together with robust design techniques for circuit optimization.

- 6. Radio Frequency Identification (RFID) System Design: using an improved technology in the organic electronic field, an RFID system for very cheap applications is simulated and designed under the guidelines of the work done.

- **7. Conclusions**: summarizes the work done in this thesis, provides some insights how the field is evolving and indicates future work to be done.

#### 1.4 Thesis Framework

The main part of this thesis has been carried out in the facilities of the Institut de Microelectrònica de Barcelona (IMB-CNM) from Consejo Superior de Investigaciones Científicas (CSIC) in the group of Integrated Circuits and Systems (ICAS) leaded by Dr. Lluís Terés.

The researcher has been working in the following industrial and research projects at Spanish and International level during his PhD period:

- "SensiFlexTag: Plataforma avanzada para aplicaciones loT con printed electronics para soluciones de trazabilidad, monitorización y localización de personas o productos en entorno de riesgo", Ministerio de Ciencia, Innovación y Universidades (RTC-2017-6679-7). 01/01/2019-31/12/2020.

- "Manufacturable Extended Gate Array Sensors (MEGA Sensors)", Innovate UK (87711-543770), Technology transfer contract with Neudrive Ltd (UK). 01/05/2017-30/04/2018.

- "SmartBallot", Ministerio de Industria, Energía y Turismo (TSI-100103-2015-041), Technology transfer contract with Scytl Secure Electronic Voting S.A. 01/07/2015-31/12/2017.

- "SMART PRINTED PAPER: Printed Electronics para nuevas funcionalidades en papel", Ministerio de Economía y Competitividad (RTC-2014-2619-7), 01/02/2014-31/12/2016.

- "Desarrollo de una etiqueta Near Field Communication (NFC/RFID) flexible con electrónica orgánica (Flex-NFC)", CDTI (IDI-20210365), 01/07/2020-30/06/2022.

- "Disposable Paper Electronic Devices for Sustainable Eco-friendly Platforms (EcoTronic)", Ministerio de Ciencia, Innovación y

Universidades, RETOS de Investigación (RTI2018-102070-B-C21), 01/01/2019-31/12/2021.

"Consultancy Contract with Smartkem Ltd for the development of a roadmap for a Full-Custom Digital Design Strategy", Technical viability study, 01/05/2021-10/09/2021.

During the development of this doctorate, the student has taught two practical courses directly related to the topics of this thesis:

- Training for Glade Layout, in August 2020 for 10 hours.

- Python aplicado para instrumentación de Laboratorio, in May 2021 for 7 hours.

During the research, he participated as organizer in two different congresses:

- 1st Workshop Red-RISCV, at Escola Enginyeria of UAB on the 5<sup>th</sup> and 6<sup>th</sup> of February 2020.

- 5<sup>th</sup> Scientific Meeting of PhD Students (JPhD2020), at UAB Campus on the 17<sup>th</sup> and 18<sup>th</sup> of September 2020.

And have attended and participated in three different conferences for the research spread:

- XXXIII DCIS Lyon, France, 14th-16th November 2018. With the work "A short review of Organic Process Design Kits, from modelling to circuits and systems" had been present in poster session.

- LOPEC 2019 Munich, Germany, 20<sup>th</sup> and 21<sup>st</sup> of March 2019. With the work "*Review of Organic Process Design Kits, from modelling to circuits and systems*" had been present in poster session.

- ESTC 2020 virtual conference, 15<sup>th</sup> to 18<sup>th</sup> September 2020. With the work "An Organic Process Design Kit, from characterization to modelling and simulation" had been present in an oral session.

An award had been received from part of the thesis results:

DC Characterization and Fast Small-Signal Parameter Extraction of Organic Thin Film Transistors With Different Geometries for the best publication in impact journal of 2019-2020 by Microelectronics and Electronic Systems Department of the UAB.

Additionally, four different final degree thesis had been supervised and a website had been made showing part of the results obtained in this work related to a tool development where is offered as a service: <a href="http://pueg.imb-cnm.csic.es/opdk.html">http://pueg.imb-cnm.csic.es/opdk.html</a>.

During the duration of this thesis, a stage of 3 months (May-July 2019) at the Institute of Nanotechnology of the Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany, was done. During the stage he was working in the group

"Low Power Electronics with advanced Materials" leaded by Jasmin Aghassi-Hagmann under the direct supervision of Mr. Gabriel Cadilha Marques. Where he collaborated with the elaboration of two publications related to modelling, and circuit design in the printed electronic field.

# State of the art