**ADVERTIMENT.** L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús estableties per la següent llicència Creative Commons:  [http://cat.creativecommons.org/?page\\_id=184](http://cat.creativecommons.org/?page_id=184)

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons:  <http://es.creativecommons.org/blog/licencias/>

**WARNING.** The access to the contents of this doctoral thesis is limited to the acceptance of the use conditions set by the following Creative Commons license:  <https://creativecommons.org/licenses/?lang=en>

Universitat Autònoma de Barcelona

Departament d'Enginyeria de la Informació i de les

Comunicacions

**HIGH THROUGHPUT IMAGE/VIDEO CODEC

WITH NVIDIA GPUS**

SUBMITTED TO UNIVERSITAT AUTÒNOMA DE BARCELONA

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE

DEGREE OF DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

by Carlos de Cea Domínguez

Bellaterra, Oct 2021

Supervised by:

Dr. Francesc Aulí Llínas

Dr. Joan Bartrina Rapesta

© Copyright 2021 by Carlos de Cea Domínguez

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Bellaterra, Oct 2021

---

Dr. Francesc Aulí Llìnas and Dr. Joan Bartrina

Rapesta

(Supervisors)

*Committee:*

Dr. Victor Sanchez

Dr. Miguel Hernandez

Dr. Daniel Hernandez

Dr. Javier Melenchón Maldonado (substitute)

Dr. Marc Vivet (substitute)

Dr. Ian Blanes (substitute)

*“A mis padres y hermanos.

A los amigos que me han

acompañado en este viaje.”*

# Abstract

The increasing number of image and video content, and the adoption of 8K resolution and high dynamic range technologies, demand faster and more efficient digital coding solutions to store and transfer these data. State-of-the-art solutions like HEVC or JPEG2000 are widely adopted but their computational requirements pose a challenge even for current hardware. For environments like digital cinema or medical image, specific FPGA boards are used to accelerate image processing without affecting image quality. In the last years, a massive parallel hardware have started to gain attraction: Graphical Processing Units (GPUs).

GPUs are massive parallel architectures originally suited for videogames or 3D simulations. In the recent years, their adoption as general purpose devices have allowed to use them as accelerators for a myriad of applications. Algorithms properly adapted to run on GPUs get significant throughput improvements when compared to their CPU implementation. This research focuses on creating an end-to-end codec based on the JPEG2000 standard tailored for GPUs.

This thesis proposes five main contributions, all of which have been published in relevant conferences or journals. The first one focuses on the first end-to-end GPU codec version, which can code and decode gray-scale images. The second version includes the implementation of the video engine within the codec, which can process up to two frames simultaneously. The third contribution consists of an in-depth analysis of the end-to-end codec with multiple throughput improvements and the addition of a multi-frame processing approach, which allows to process multiple frames simultaneously when coding video. The fourth contribution proposes the implementation of an improvement to the core coding engine, tested on a CPU version of the end-to-end codec. The last contribution details an in-depth analysis of the improvement presented in the previous paper but implemented in the end-to-end GPU codec, including results with improvements of more than  $10\times$  the performance of the best JPEG2000 commercial implementation when processing 4K RGB video.

# Acknowledgements

Una tesis doctoral es un viaje en el que encuentras múltiples obstáculos y diferentes sendas hasta conseguir el ansiado título. Como guías he tenido a mis supervisores, Francesc, Juan Carlos y Joan que me han acompañado y aconsejado a cada paso que he dado. Sin vosotros es evidente que no estaría donde estoy ni habría conseguido todo lo que hemos logrado en tan poco tiempo. Este logro es de todos. Gracias por vuestra inmensa paciencia, vuestro conocimiento y apoyo.

En la facultad, además de a mis supervisores, tuve la fortuna de conocer a gente muy capaz que me acompañó en el viaje. Sin ánimo de ser excluyente, debo dar las gracias a mis dos compañeras de despacho por haber hecho más ameno este trayecto, a Pablo por haber contribuido a introducirme en mi línea de investigación, a mi compañero de facultad, Iván, por todos esos almuerzos donde intercambiábamos opiniones y a todos los profesores asociados con los que compartí docencia estos años.

Saliendo ya del ámbito académico, quiero remarcar la importancia que ha tenido mi familia. Gracias a mis padres y hermanos, que aun en la distancia, siempre se han preocupado e interesado por cómo iba avanzando en este viaje. Os he sentido igual de cerca sin importar los kilómetros que nos han separado. Habéis sido el refugio al que acudir siempre que lo he necesitado.

Acompañándome a cada paso que daba en mi estancia en Barcelona estabais vosotros, Aitor y Daniel. Habéis sido los mejores amigos que podía pedir, consiguiendo que mi vida en Cataluña fuera mucho más familiar, agradable y divertida. Sin nuestras tardes de viernes y nuestras escapadas, los días habrían pesado muchísimo. Puedo decir sin temor a equivocarme que, de no ser por los dos, no creo que hubiera sido capaz de llevar tan bien mi estancia allí. Gracias por conseguir que tres años se sintieran como tres meses.

Tampoco me olvido de todos aquellos amigos que tengo lejos tanto en León como en muchas otras partes de España. Ciento es que durante la tesis los momentos de reunión han escaseado, y aun así habéis permanecido atentos y dispuestos a ayudar en lo que buenamente pudierais. Especialmente gracias a vosotros, Sandra y Diego, por vuestro apoyo incondicional este año. Sois muchos, nombrarlos a todos me es imposible. ¡Vosotros sabéis quienes sois!

Por último, y no menos importante, daros las gracias a vosotros, Javier, Agustín, Roger y Miguel, que me acompañasteis virtualmente durante todos estos años, siempre poniendo esa guinda de diversión y esparcimiento tan necesaria, sobre todo durante los últimos meses que estuve en Barcelona mientras duró el confinamiento sanitario estricto.

# Contents

|                                                                                                     |            |

|-----------------------------------------------------------------------------------------------------|------------|

| <b>Abstract</b>                                                                                     | <b>iii</b> |

| <b>Acknowledgements</b>                                                                             | <b>v</b>   |

| <b>1</b> <b>Introduction</b>                                                                        | <b>1</b>   |

| 1.1 Thesis contributions . . . . .                                                                  | 4          |

| 1.2 Organization . . . . .                                                                          | 6          |

| <b>2</b> <b>High Throughput Image Codec for High-Resolution Satellite Images</b>                    | <b>9</b>   |

| <b>3</b> <b>GPU architecture for wavelet-based video coding acceleration</b>                        | <b>15</b>  |

| <b>4</b> <b>GPU Oriented Architecture for an End-to-End Image Video Codec<br/>Based on JPEG2000</b> | <b>27</b>  |

| <b>5</b> <b>Complexity Scalable Bitplane Image Coding with Parallel Coefficient Processing</b>      | <b>43</b>  |

| <b>6</b> <b>Real-time 16K Video Coding on a GPU with Complexity Scalable<br/>BPC-PaCo</b>           | <b>51</b>  |

| <b>7</b> <b>Conclusions</b>                                                                         | <b>67</b>  |

| 7.1 Summary . . . . .                                                                               | 67         |

| 7.2 Future research lines . . . . .                                                                 | 68         |

| <b>A</b> <b>List of Publications</b>                                                                | <b>71</b>  |

# Chapter 1

## Introduction

Digital image and video coding is used nowadays in a myriad of fields and disciplines. The amount of images and videos grow day after day and its storage and processing is getting more challenging as quality, resolutions and samples bit-depths increase. In order to process all these data and store it appropriately, usage of image and video coding techniques are a must. There are three main expert groups that define image and video compression standards that conform the state-of-the-art in terms of digital image encoding/decoding: the consultative committee for space data systems (CCSDS), the moving pictures expert group (MPEG) and the joint photographic expert group (JPEG). The CCSDS [1] coding standards, including CCSDS121 [2], CCSDS122 [3] and CCSDS123 [4] are mainly employed on-board satellites to compress/decompress data obtained on embedded boards, hence its lower computational complexity and feature set. For digital processing in environments with less computational restrictions, HEVC [5] and JPEG2000 [6] are the ones employed for most professional and user-based tasks. Both standards include advanced features like quality scalability, interactive transmission or error resilience. However, both of them, specially JPEG2000, are very demanding computationally, and scenarios like digital cinema or medical usage require specific hardware like Floating Point Gate Arrays (FPGAs) [7, 8, 9, 10] to process data in real-time at high quality. With the increasing demand on higher resolutions and the inclusion of High Dynamic Range (HDR) technologies, the importance of getting faster compression tools to store and transfer

these data is growing more than ever.

The aforementioned standards, HEVC and JPEG2000, were designed based on the mainstream hardware to process data available to the date: Central Processing Units (CPUs). CPUs follow the multiple-instructions multiple-data paradigm (MIMD), which in short means that they are designed to have few but very powerful processing threads. Images, and videos, are data structures consisting of, commonly, thousands of data points which may undergo a series of transformations while they are processed. In the last decade, Graphical Processing Units (GPUs) have become more popular to accelerate applications, specially due to their computational power, with  $10\times$  more TFlops when compared to CPUs, and their affordable price. Furthermore, many supercomputers are including Nvidia GPUs, hence becoming more relevant in scientific researches and simulations [11].

GPUs are hardware devices which were initially designed to aid with graphical applications or videogames. Currently, they are used as well as general purpose devices to accelerate certain parts of a workload. GPUs are based on the single-instruction multiple-data (SIMD) paradigm, which, contrary to the MIMD one, means that the device is designed to process, typically, thousands of data points simultaneously using thousands of threads in a synchronous fashion. GPUs are composed of, typically, multiple streaming multiprocessors (SMs), each of one is responsible of running multiple 32-wide vector instructions in parallel. These groups of 32-threads are referred to as warps, and warps are grouped in thread blocks, which are independent execution units running on an SM. Thread blocks within an SM can be running kernels (i.e. functions) from the same or different applications. Nvidia GPUs make use of the so-called streams to manage the execution of these independent kernels. Using multiple streams can be beneficial to balance the resource usage and throughput of the GPU.

Comparing each architecture, CPU threads pose a lower latency and higher computational power than those of a GPU. However, having more threads to process data simultaneously can be beneficial, specially for data loads that require simple operations per data point. Algorithms which expose a huge amount of data points with no dependencies among them are perfect scenarios for these kind of devices.

Nonetheless, inherently sequential algorithms conform a difficult task for GPUs. In this situation, either the algorithm is slightly modified to run on GPUs without removing the causality among data points, or the algorithm is re-engineered to decrease (or remove) the dependencies. The drawback on the first approach is that throughput increases are usually not that impressive, but compliance with the original implementation is maintained. The second option usually achieves high boosts in throughput, although as a consequence the new application may lose compliance with the original implementation. Applications which can take advantage of this type of parallelism can get huge throughput improvements if the algorithms are properly adapted. Fields like Bioinformatics can get boosts of up to  $20\times$  more performance when adapting its algorithms to run over GPUs [12].

Of the aforementioned codecs, JPEG2000 is the one used in very high-quality demanding environments due to its coding methodology and its excellent resilience to image artifacts. In the last decade, there have been multiple attempts to port JPEG2000 to GPUs without losing its compliance in an effort to increase throughput. The core coding aspect within this standard is composed of four main parts: a color transform (CT), a discrete wavelet transform (DWT), a bitplane coding engine (BPC) and a codestream reorganizer (CR). Of those four, the third one is the heaviest in terms of computational complexity, and it is the only one which exhibits strong dependencies among samples. Thus, unless causality between data samples is broken, the throughput improvements are minimal when porting the algorithm to a SIMD-based architecture. The different attempts to port the algorithm to GPUs, either implementing a full end-to-end codec or just the BPC stage [13, 14, 15, 16, 17, 18, 19, 20, 21], did not achieve competitive throughput, getting lower results than current JPEG2000 CPU implementations like Kakadu [22] running on current hardware. There are other approaches that follow a different line, using GPUs implementations like Comprimato [23] to aid in the coding process, although their performance is limited by the sample inter-dependencies. Finally, the last approach consists on redesigning the algorithm, which achieves better results but the compliance with the traditional implementation is lost [24, 25].

This thesis researches on how to create an efficiently end-to-end image and video

| <i>Title</i>                                                                           | <i>Year</i> | <i>Description</i>                                                                                                                                                                            | <i>Conf. / Journal</i>                 | <i>Core / Quartile</i> | <i>Imp. Factor</i> |

|----------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|--------------------|

| <i>High throughput image codec for high-resolution satellite images</i>                | 2018        | First end-to-end version which codes and decodes images                                                                                                                                       | IGARSS2018                             | C                      | N/A                |

| <i>GPU architecture for wavelet-based video coding acceleration</i>                    | 2020        | First end-to-end version with support to code/decode video with up to two streams                                                                                                             | ParCo2019                              | N/A                    | N/A                |

| <i>GPU-oriented architecture for an end-to-end image/video codec based on JPEG2000</i> | 2020        | Multi-stream image/video coding/decoding software with in-depth analysis on the GPU resources usage, different amount of streams and a final comparison with other state-of-the-art solutions | IEEE Access                            | Q1                     | 3.367              |

| <i>Complexity scalable bitplane image coding with parallel coefficient processing</i>  | 2020        | New feature to improve throughput of the BPC-PaCo kernel on the CPU version of the codec with slight coding performance penalizations                                                         | IEEE Signal Processing Letters         | Q1                     | 3.109              |

| <i>Real-time 16K Video Coding on a GPU with Complexity Scalable BPC-PaCo</i>           | 2021        | Complexity scalable implementation on the GPU codec with in-depth analysis on the throughput improvements and coding performance                                                              | Signal Processing: Image Communication | Q2                     | 3.256              |

Table 1.1: List of publications presented during the Ph.D. and included in the proceedings afterwards.

codec to maximize the throughput while keeping coding performance on par with the original implementation. The proposed solution is based on JPEG2000, it runs entirely on Nvidia GPUs without sacrificing any existing feature, and with increases of over  $10\times$  the throughput over the best commercial JPEG2000 implementation.

## 1.1 Thesis contributions

This thesis continues the line of research started about ten years ago that aims to develop new coding techniques for image/video compression tailored for the fine-grain parallelism of GPUs. It started with the development of coding techniques meant to break the causality of classical coding strategies [26, 27, 28]. Those results lead to the development of a lightweight arithmetic coder that allowed fine-grain parallelism [29, 30]. After that, the research focused on designing and building the different stages of a wavelet-based coding pipeline. The first stage was to develop the DWT [31, 32], which achieved highly competitive performance thanks to a novel register-based strategy. Secondly, an algorithm for the BPC with fine-grain parallelism was presented and evaluated in terms of coding performance in [33, 34]. Then, the GPU implementation of [33, 34] was introduced in [35]. The coding technique used in [33, 34, 35] is referred to as BPC-PaCo. These contributions define the isolated parts of an end-to-end GPU-based codec. This thesis starts when those contributions are published.

The first end-to-end version included the two GPU kernels, DWT and BPC-PaCo, with further adaptations to communicate them, and a new GPU kernel called code-stream reorganization, which reorganizes the data from BPC-PaCo into a compressed data structure ready to be written to the disk. Apart from the new kernel, the challenge of this version was designing an infrastructure capable of taking care of memory transfers between kernels efficiently. Managing memory allocations can be expensive, so it is preallocated taking in consideration the amount of data needed per kernel, which depends on the input data size. The codec makes use as well of Nvidia libraries to implement some primitives within the CR kernel. It also included the first I/O algorithms to read and write images with the minimal impact on the overall performance. This version of the codec can code/decode gray-scale 8-bits images. It was presented at IGARSS2018 [36] and published in the proceedings afterwards.

After the first end-to-end version, the codec was improved by adding video processing, while also including color processing. For this version, the GPU can process two frames simultaneously from a single video feed. It can handle multiple CPU threads to manage two GPU streams simultaneously. Memory preallocation and assignation is carefully handled per stream. The I/O processing is improved, with capability to read information from the disk and send the data to the GPU asynchronously while other frames are being processed. This version yields 4K real-time throughput performance in a Nvidia GTX 1080 Ti GPU. It was presented at ParCo2019 [37] and published in the proceedings afterwards.

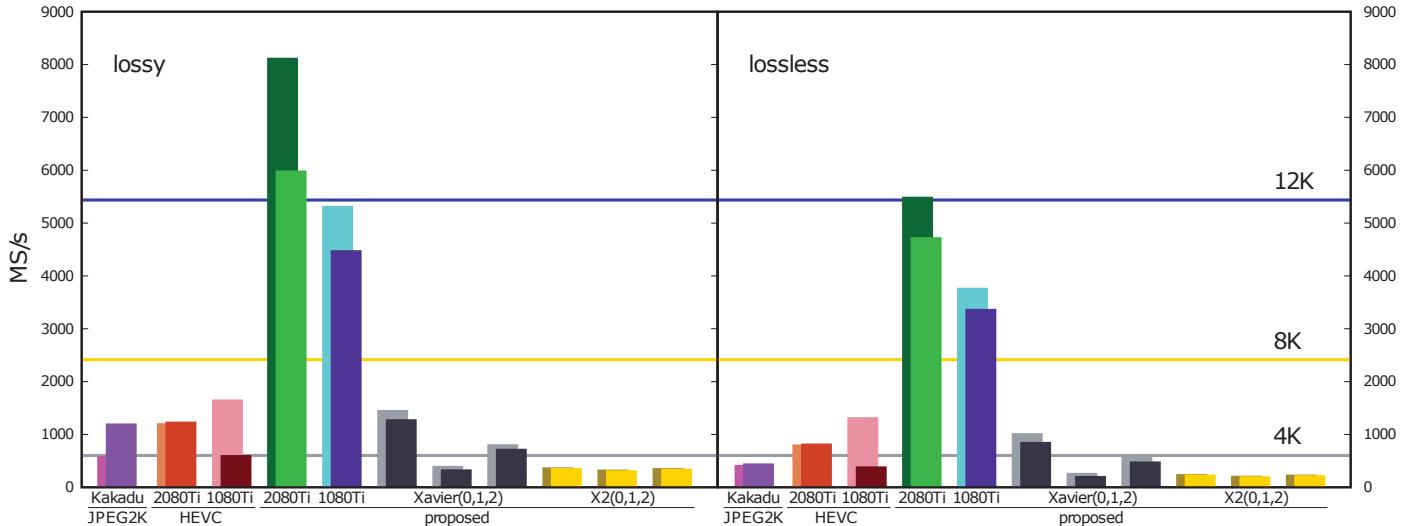

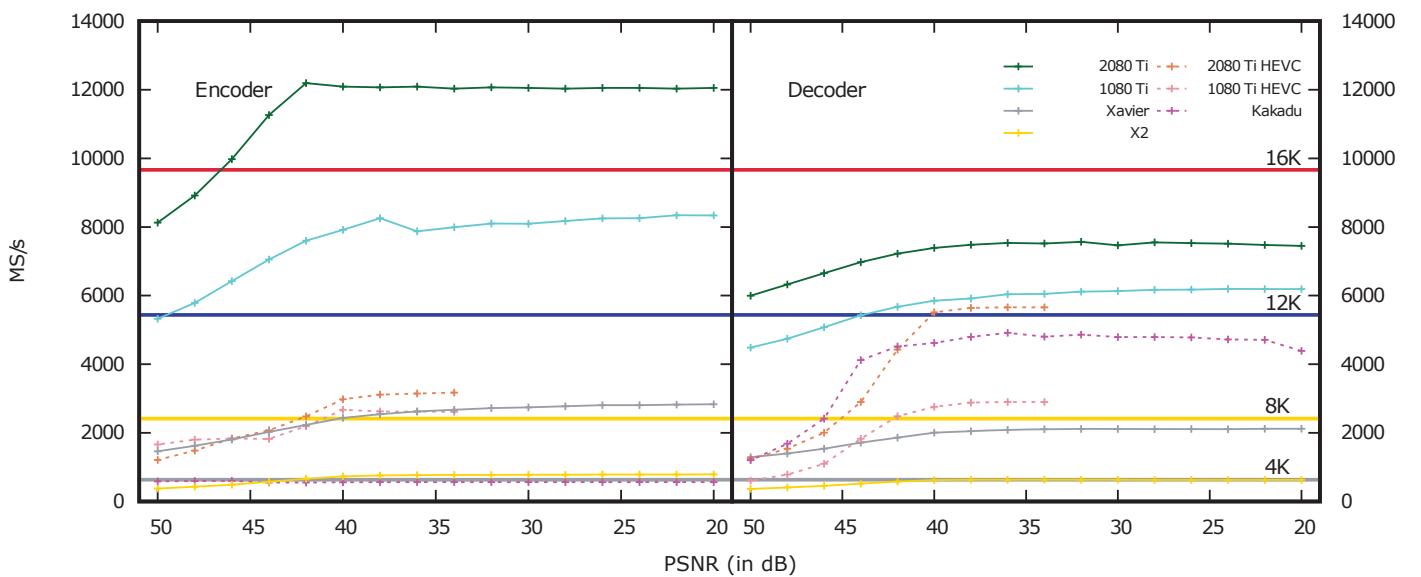

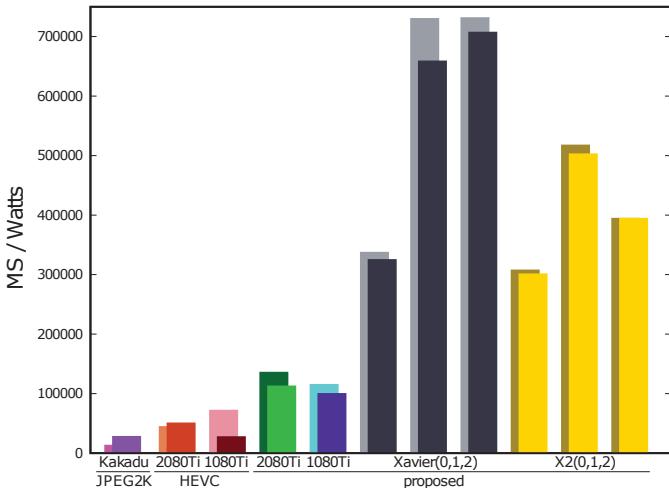

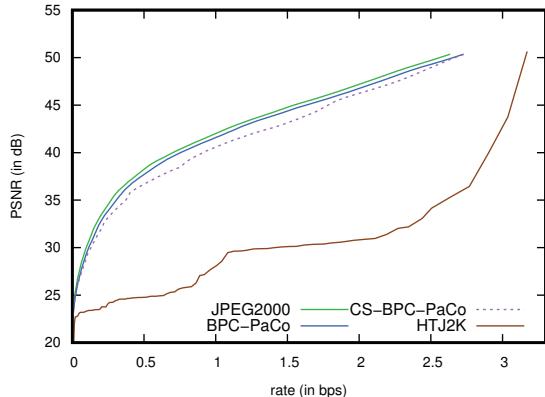

The third implementation includes multi-stream capabilities and multiple throughput improvements across the coding pipeline, including all the kernels and the I/O functions. It details each kernel from a GPU perspective, including memory transfers from the device memory to the individual registers, bandwidth values, device occupancy, etc. It also compares the proposed codec against state-of-the-art solutions like JPEG2000 Kakadu [22] or Nvidia HEVC NVENC [38]. It gets better throughput results than existing JPEG2000 compliant GPU implementations, which run slower than Kakadu. It is published in the IEEE Access on 2020 [24].

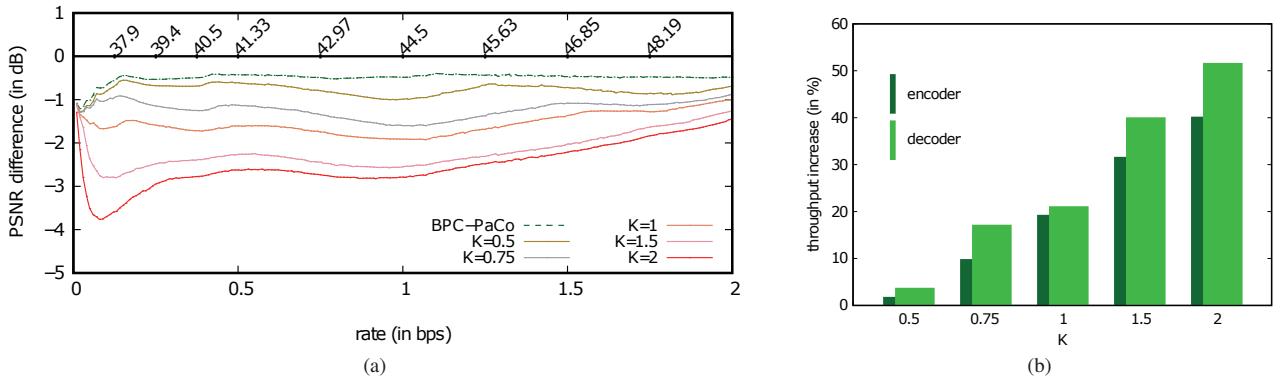

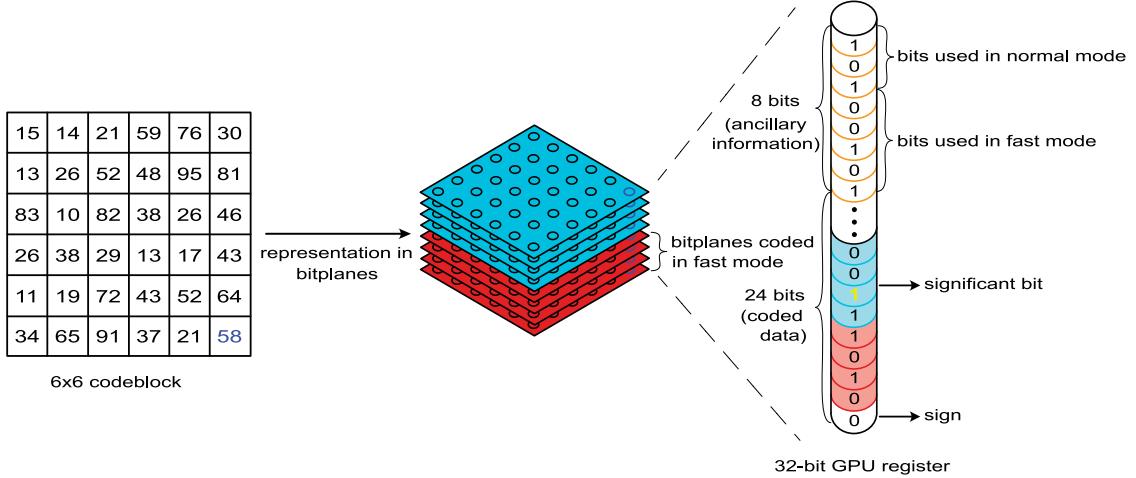

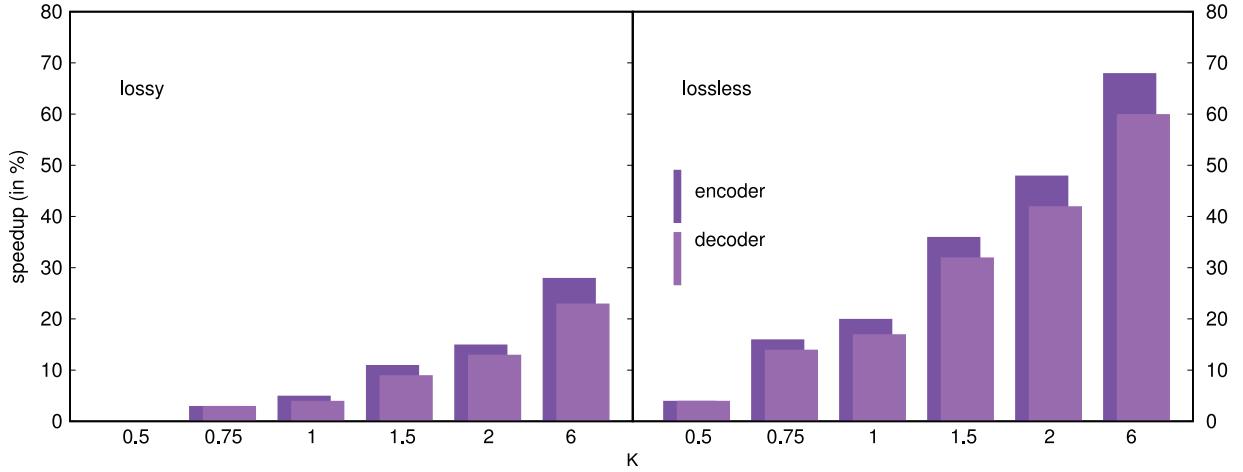

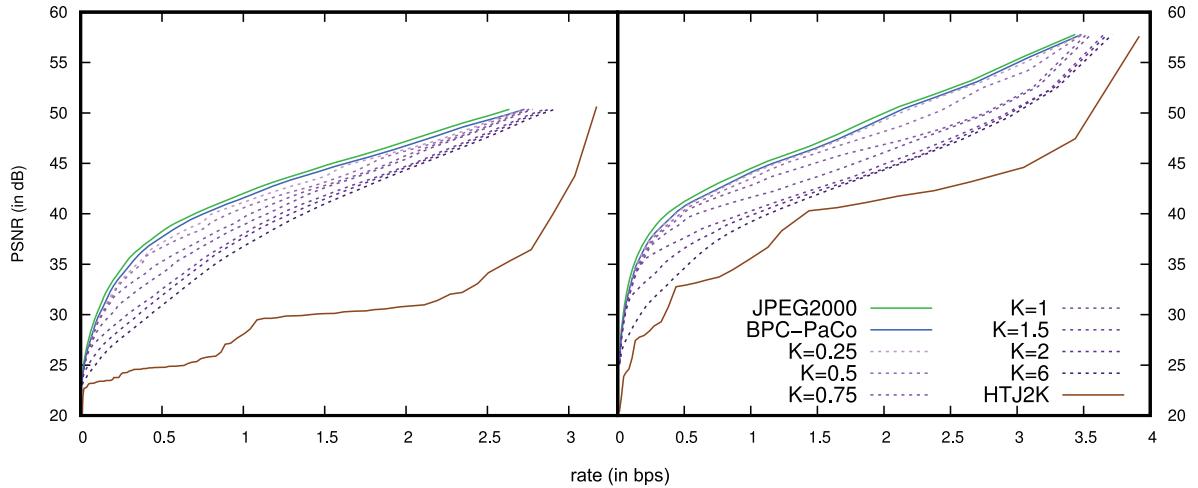

For the fourth publication, the BPC-PaCo algorithm receives a new feature called Complexity Scalability, getting renamed to CS BPC-PaCo. Traditional BPC-PaCo

takes about 86% of the execution time of the entire coding pipeline. CS BPC-PaCo is aimed to improve coding throughput by using a  $K$  factor that works as a trade-off between coding performance and coding throughput. This version is implemented in Java, running on an Intel CPU to test its viability and efficiency. The results showed double digit throughput increments with a coding performance penalty of about 10% with the highest factor. These results were sent to the journal IEEE Signal and Processing Letters, getting published on 2020 [39].

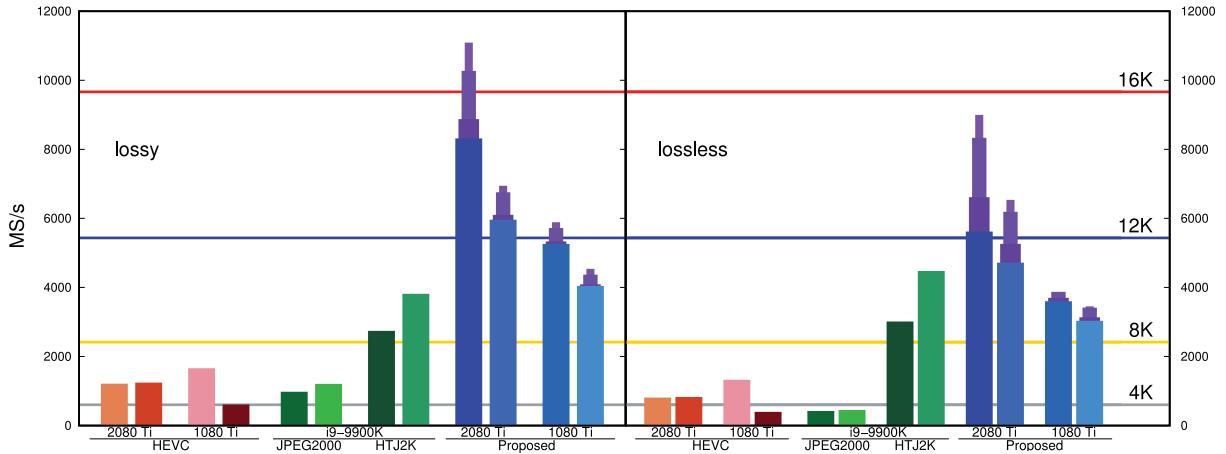

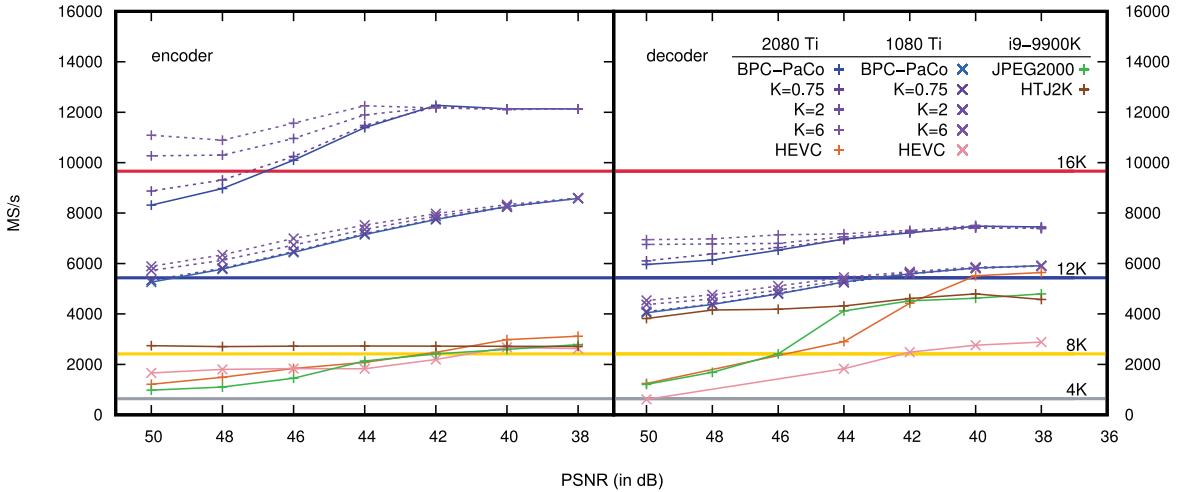

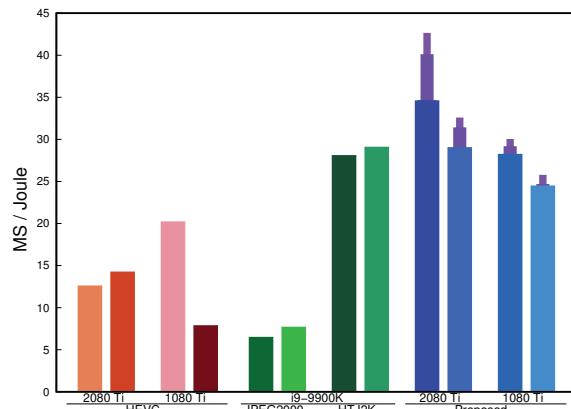

The final publication details the implementation of CS BPC-PaCo in the GPU end-to-end codec. It includes an exhaustive and detailed analysis from both kernel and codec perspective, thoroughly analyzing the impact in memory transfers, instructions per cycle, registers and bandwidth with different  $K$  factors, effectively explaining the achieved improvements. Results show that the codec achieves 16K coding throughput in real-time at 50 dB of PSNR when coding a 2 minute long 4K RGB 8 bps in the Nvidia RTX 2080 Ti, faster than the new JPEG2000 standard part "High-Throughput JPEG2000" codec running on a i9-9900K Intel CPU. It was sent to the journal Signal Processing: Image Communication and published on 2021 [40].

## 1.2 Organization

Each of the following chapters correspond to each of the published papers unedited and in order of publication:

Chapter 2: High Throughput Image Codec For High-Resolution Satellite Images

- Includes the research published in [36].

Chapter 3: GPU architecture for wavelet-based video coding acceleration - Includes the research published in [37].

Chapter 4: GPU-Oriented Architecture for an End-to-End Image/Video Codec Based on JPEG2000 - Includes the research published in [24].

Chapter 5: Complexity Scalable Bitplane Image Coding With Parallel Coefficient Processing - Implementation of the new CS BPC-PaCo published in [39].

Chapter 6: Real-time 16K video coding on a GPU with Complexity Scalable BPC-PaCo - Includes the GPU implementation of the new CS BPC-PaCo published

in [40].

Chapter 7: Conclusions. It includes the final thoughts of the thesis and future lines of research.

## Chapter 2

# High Throughput Image Codec for High-Resolution Satellite Images

# HIGH THROUGHPUT IMAGE CODEC FOR HIGH-RESOLUTION SATELLITE IMAGES

*Carlos de Cea-Dominguez<sup>†</sup>, P. Enfedaque<sup>\*</sup>, Juan C. Moure<sup>‡</sup>, Joan Bartrina-Rapesta<sup>†</sup>, Francesc Auli-Llinas<sup>†</sup>*

<sup>†</sup> Department of Information and Communications Engineering

<sup>‡</sup> Department of Computer Architecture and Operating Systems

<sup>† ‡</sup> Universitat Autònoma de Barcelona, Spain

<sup>\*</sup> Computational Research Division, Lawrence Berkeley National Laboratory

## ABSTRACT

The growth in the use of satellite images has generated the need for their fast compression, processing, and distribution. JPEG2000 is a widespread standard for the compression and transmission of such images once they are in the ground. Despite its advanced features and excellent coding performance, JPEG2000 demands significant computational resources. This paper introduces a wavelet-based codec that uses the JPEG2000 framework, but replaces its most computationally demanding coding stage by a highly parallel engine. When executed in Graphics Processing Units to code high-resolution satellite images, the proposed codec achieves speed-ups of up to 8 $\times$  when compared to the fastest implementation of JPEG2000 executed in a multi-core platform.

**Index Terms**— High throughput image coding, bitplane image coding, JPEG2000.

## 1. INTRODUCTION

Satellite images are nowadays employed in myriad fields such as management of natural resources, study of climate change, weather forecast, or map making, among others. These images are captured by missions formed by a (constellation of) Earth Observation satellite(s) like the LandSat, GeoEye, Sentinel, or SEOSat. The huge amount of data acquired by these satellites pose several challenges. The first is to download the images to the ground with minimum loss in quality. To do so, compression standards such as those proposed by the Consultative Committee for Space Data Systems are commonly employed. Once the data are on the ground, other compression standards with more advanced features are used to store and transmit these images. JPEG2000 (ISO/IEC 15444) is a widespread choice to do so.

Despite its excellent capabilities, the bitplane coding engine of JPEG2000, called tier-1 coding [1], is highly demanding in terms of computational resources. Its algorithm scans the wavelet-transformed coefficients of the image numerous

times, producing a stream of bits with interesting features such as quality progression, possibility of partial transmission, or error resilience [1]. This comes at the expense of long execution times and complex software/hardware implementations.

The image coding community have studied ways to increase the throughput of JPEG2000 implementations for almost ten years. A promising alternative is to use the highly parallel architectures of Graphics Processing Units (GPUs). Modern GPUs are mostly based on the Single Instruction Multiple Data (SIMD) paradigm. Its main idea is to execute a flow of instructions on multiple pieces of data in a lock-step synchronous way. To effectively apply such vector instructions on an algorithm there must be as few dependencies among the data as possible. The main difficulty to implement JPEG2000 in GPUs is that the tier-1 coding stage employs an inherently sequential algorithm. It scans the coefficients one-by-one, producing a result for each that can not be obtained without all the previous. This causality renders parallelism at the bitplane coding engine a very challenging task. Even though there are some works in the literature with this purpose [2–4], some centered on satellite imagery only [5], none of them is able to exploit the full potential of GPUs.

Aware of this issue, the Joint Photographic Experts Group (JPEG) launched in June 2017 a call for proposals [6] aimed to develop an alternate coding engine to increase the throughput of the standard while sacrificing as few as possible of its features. This initiative is currently under development. In the same line of this call for proposals but well before it was launched, we started a line of research whose purpose is to devise a bitplane coding engine that can exploit the fine-grain parallelism of GPUs while maintaining the same features as those of JPEG2000. First, we studied stationary probability models [7, 8] for the coding of coefficients that did not require previously coded data and/or adaptive algorithms like those employed in the standard. Then, we proposed an arithmetic coder that produces fixed-length codewords [9], allowing their interleaving in a single stream instead of producing a single codeword like the MQ coder of JPEG2000. These two techniques were combined in [10] to devise a bitplane cod-

---

This work has been partially supported by the Spanish Government (MINECO), by FEDER, and by the Catalan Government, under Grants TIN2015-71126-R, TIN2014-53234-C2-1-R, and 2014SGR-691.

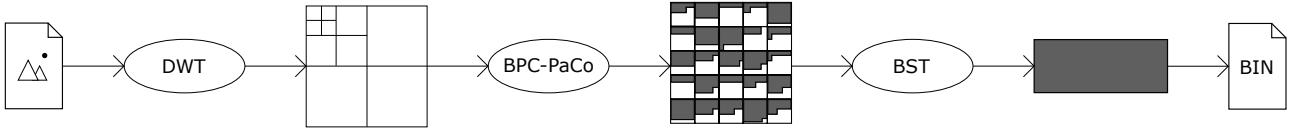

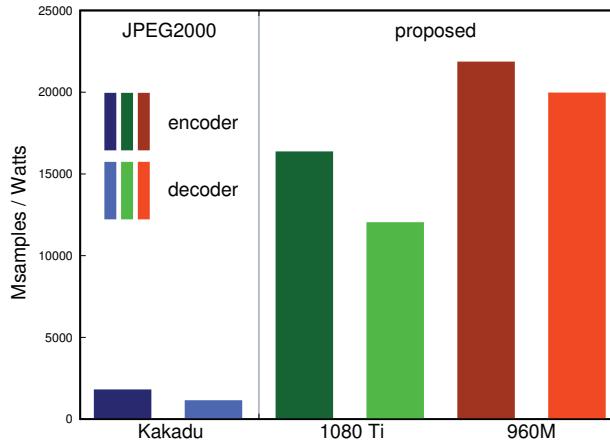

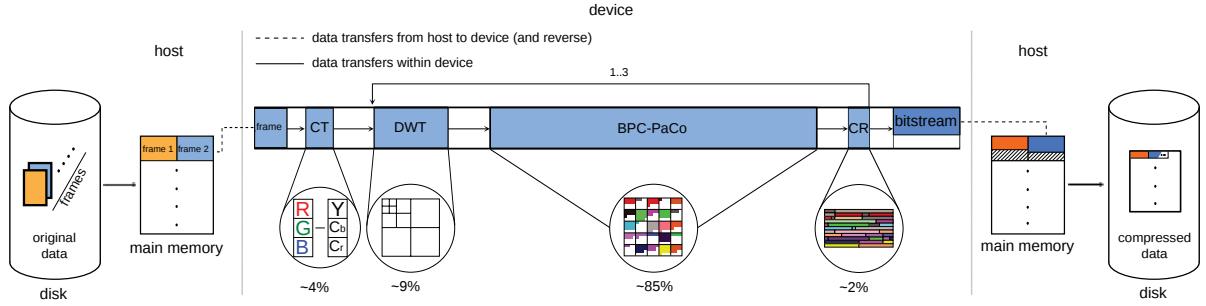

**Fig. 1:** Pipeline of the proposed codec.

ing strategy with parallel coefficient processing (BPC-PaCo), the first coding engine that breaks the dependencies among coefficients. Its implementation in a GPU [11] indicates that it can effectively exploit the parallelism of SIMD architectures, which results in high speed-up factors with respect to the fastest implementations of JPEG2000, either executed in multi-core Central Processing Units (CPUs) or in GPUs.

Our previous work is solely centered on the bitplane coding stage. As explained below, wavelet-based image codecs (including JPEG2000) are commonly structured in three coding stages: wavelet transform, bitplane coding, and bitstream re-organization. This paper introduces an end-to-end codec based on BPC-PaCo. It employs the framework of JPEG2000 and provides the same features of the standard. When employed to code high-resolution satellite images in consumer-grade GPUs from Nvidia, it achieves speed-ups of up  $8\times$  as compared to the fastest implementations of JPEG2000.

The rest of the paper is structured as follows. Section 2 explains the basics of SIMD architectures and JPEG2000. Section 3 describes the proposed end-to-end codec in detail. Section 4 provides experimental results achieved when coding high-resolution images captured by the GeoEye satellite. The last section summarizes this work.

## 2. BACKGROUND

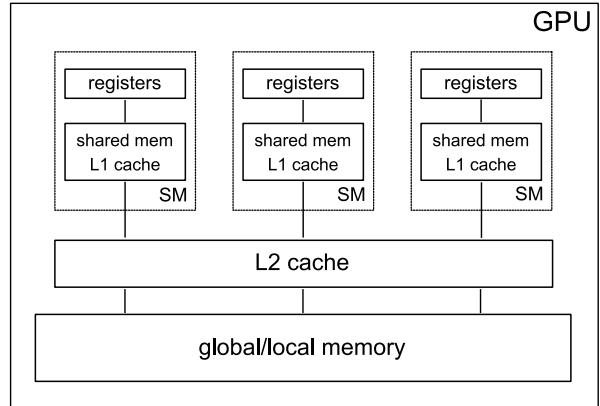

Nvidia GPUs are hardware devices with tens of individual compute units called streaming multiprocessors (SM). Each SM can execute multiple 32-wide SIMD (or also called vector) instructions simultaneously. GPUs from Nvidia employ the CUDA programming model, which defines a computation structure composed by (potentially) thousands of threads grouped into warps and thread blocks. While the hardware device executes 32-wide SIMD instructions, a software CUDA thread is the virtualization of one of the lanes of the SIMD instruction. A warp is the group of 32 consecutive CUDA threads executing vector instructions and advancing their execution in a lock-step synchronous fashion. A CUDA program should reduce control flow divergence (i.e., conditional instructions) among warps since that results in the sequential execution of the divergent paths, which increases the amount of instructions executed. A thread block is a group of warps, each one assigned to run until completion in a specific SM. Warps in a thread block are executed asynchronously and can cooperate via on-chip fast memories, using explicit synchronizing barrier instructions when required.

The CUDA memory model is hierarchically organized as follows: there is a space of local memory private to each

thread, a shared memory private to each thread block, and a global memory public to all threads in the device. From a microarchitecture point of view, the local memory reserved per thread is located either in the registers or the off-chip memory, depending on the available resources. GPUs have two levels of cache as well.

As previously stated, the proposed image codec is structured in three coding stages. The discrete wavelet transform (DWT) is employed in the first stage to decorrelate the spatial redundancy of the image. After that, the image is conceptually partitioned in small sets of wavelet coefficients called codeblocks. Bitplane coding is applied in each codeblock independently. The main idea behind this technique is to code the wavelet-transformed coefficients bitplane by bitplane. A bitplane is defined as the collection of bits in the same position of the binary representation of the magnitude of all coefficients. The bits emitted by the coding engine are fed to an arithmetic coder that employs a probability model to compress them. The last stage of the codec truncates and reorders the bitstreams generated for each codeblock to produce the final codestream.

## 3. PROPOSED CODEC

The proposed codec is implemented in CUDA. Its coding pipeline is depicted in Fig. 1. The encoder (decoder) reads the image (compressed file) from the hard disk to the CPU memory and then moves the data to the main memory of the GPU. The three stages communicate using this main memory. The final stage moves the compressed data (decompressed image) from the GPU to the CPU memory and writes it back to disk. Each coding stage is implemented to exploit the high amount of fine-grain parallelism required for the effective utilization of the GPU’s resources. The algorithm employed to apply the DWT already exhibits fine-grain parallelism and its implementation in GPUs has been widely studied in the literature [12–14]. Herein, we employ the work that we proposed in [13] since, to the best of our knowledge, it is the fastest implementation of the DWT for CUDA. BPC-PaCo has been adapted from our previous work [11]. The third stage of the coding pipeline is called bitstream tightening (BST) and is introduced in this paper.

### 3.1. Discrete wavelet transform

The GPU-adapted DWT implementation employed herein uses a register-based approach [13]. This allows data reuse

and data sharing, taking advantage of the fine-grain parallelism and data access locality of the algorithm. The DWT is applied via the lifting scheme, which processes, alternatively in the vertical or horizontal axis, odd and even image samples by using its adjacent values. The image is divided into tiles, which are processed by independent warps to provide the coarse-grained parallelism needed to populate the SMs of the GPU. With an appropriate tile size, the coefficients of each tile can be completely stored in the local registers of each thread and processed sequentially in both axes without saving the intermediate information. This halves the memory access operations, significantly increasing the throughput of the algorithm.

### 3.2. Bitplane coding with parallel coefficient processing

The wavelet coefficients are conceptually partitioned in codeblocks, typically containing  $32 \times 32$  or  $64 \times 64$  coefficients, that do not have dependencies among them. The processing of codeblocks in parallel typically requires coarse-grained, control-divergent strategies that are employed in many implementations of the original JPEG2000 standard. To solely use this kind of parallelism does not suit well the architecture of GPUs. As previously stated, BPC-PaCo is devised to promote fine-grain parallelism within the codeblock. Briefly described, BPC-PaCo further partitions the codeblock in 32 stripes of coefficients that can be coded by the threads in a warp. The scanning order, context formation, probability model, coding passes, and arithmetic coder are redefined to permit such a parallel processing. In particular, each stripe employs an arithmetic coder and the codewords produced in each stripe are collaboratively interleaved in the bitstream by all the threads in the warp. This permits the use of coarse- and fine-grain parallelism, since both the codeblocks and the coefficients within them are coded in parallel.

### 3.3. Bitstream tightening

The bitstreams produced by BPC-PaCo for each codeblock have different sizes depending on the data coded. As a consequence, they are scattered throughout the entire output buffer. The BST stage must tighten the information generated by BPC-PaCo reorganizing them into a compact codestream that can then be written to a file. Also, it adds some auxiliary information (i.e., headers) to be able to identify the codeblock data within the final file in addition to general image information.

The first step of the proposed BST algorithm is the generation of a vector of integers that contains the size of the bitstreams generated for consecutive codeblocks. This vector is then employed to generate a new vector that contains aggregate bitstream sizes, which represent the offset of the bitstream with respect to the start position. The vector of offsets is used as a memory map in the data reorganizing process. The vector of offsets is generated via the parallel prefix

sum algorithm [15] using the state-of-the-art implementation in the open-source CUB framework.

To perform efficient memory accesses, the workload is distributed among threads promoting that adjacent threads access adjacent data. To do so, the threads are assigned to consecutive positions in the output codestream. Each thread performs a binary search in the vector of offsets to compute the position of the input value corresponding to the assigned output position. A lookup table is added to accelerate the binary search operation: a direct access to the LUT provides a bounded search interval that reduces the average number of search iterations. This auxiliary LUT accelerates the performance of the BST algorithm by  $2 \times$ .

The decoder reverses the operations that are carried out in the encoder. With regard to the BST stage, the vector containing the sizes of the bitstreams is in the auxiliary information of the compressed file, so only the vector offset needs to be recomputed.

## 4. EXPERIMENTAL RESULTS

The proposed codec is compared with Kakadu v7.8. Kakadu is the fastest implementation of JPEG2000. It is programmed in C++ and is heavily optimized via assembly instructions. It supports multithread parallelism when executed in multi-core CPUs. Kakadu is executed in a platform that has a total of 32 Intel Xeon cores running at 2.2 GHz. Our implementation is executed in the consumer-grade GPUs reported in Table 1. The GTX 1080 Ti is a high-end desktop GPU whereas the GTX 960M is a low-end GPU for laptops. The tests report the execution time employed for each implementation without considering the time needed to write the final file to the disk, since that significantly varies depending on the hard disk. The tests employ 3 images captured by the GeoEye satellite. The images are  $10240 \times 10240$ , gray-scale, and have a bit-depth of 8 bits per sample.

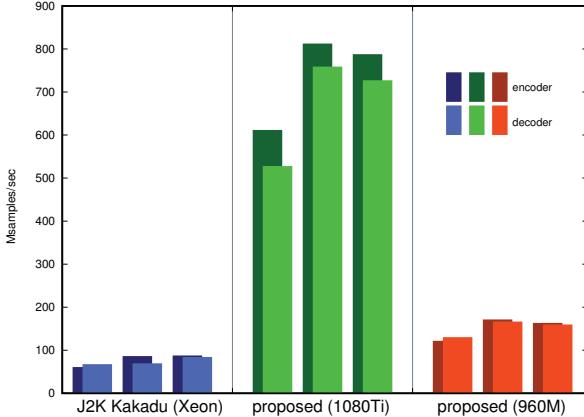

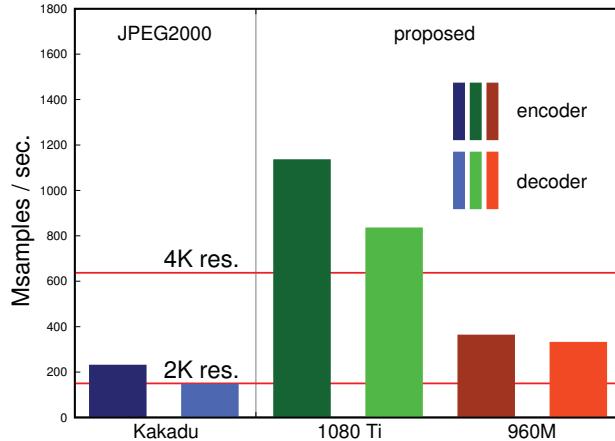

The results achieved are depicted in Fig. 2. The vertical axis is the performance achieved, reported in Msamples per second. Each pair of columns is the encoding and decoding of an image. The results indicate that the proposed codec is approximately  $8 \times$  faster than Kakadu when executed in the GTX 1080 Ti and approximately  $2 \times$  faster than Kakadu when executed in the GTX 960M. As seen in Table 1, the GTX 1080 Ti has six times more cores and memory bandwidth than the GTX 960M, though in the results of Fig. 2 the GTX 1080 is only  $4 \times$  faster than the GTX 960M. This is due to the processes involved in the codec, though further analysis is required.

From a power efficiency point of view, the consumption used by Kakadu with the Intel Xeon platform is up to 380W, whereas the GTX 1080 Ti and GTX 960M consume up to 250W and 60W, respectively. This indicates that the proposed codec achieves a much higher throughput than Kakadu while consuming significantly less power, making it suitable for mobile solutions.

| device      | #SMs | cores $\times$ SM | #cores | clock freq. | mem. bandwidth |

|-------------|------|-------------------|--------|-------------|----------------|

| GTX 1080 Ti | 28   | 128               | 3584   | 1582 MHz    | 484 GB/s       |

| GTX 960M    | 5    | 128               | 640    | 1176 MHz    | 80 GB/s        |

**Table 1:** Features of the GPUs employed.

**Fig. 2:** Results achieved when coding three high-resolution images captured by the GeoEye satellite.

## 5. CONCLUSIONS

The current image compression standards employed for the compression of satellite imagery are mainly devised to exploit the large-degree of parallelism provided in CPUs. This paper introduces an end-to-end codec that employs the framework of JPEG2000 but that provides –in all stages of the coding pipeline– a fine-degree of parallelism. This can be effectively exploited when executed in architectures that highly rely on SIMD parallelism such as those found in Nvidia GPUs. Experimental results coding large-resolution satellite images indicates that the proposed codec is 8 $\times$  faster than the most efficient implementations of JPEG2000 while significantly reducing the power consumption. None of the advanced features of JPEG2000 are sacrificed in the proposed codec, so it is ideal for scenarios that deal with massive datasets, such as in the compression and transmission of satellite imagery. Future work will explore the adaptation of the proposed codec for the coding of other types of images and video.

## 6. REFERENCES

[1] D. S. Taubman and M. W. Marcellin, *JPEG2000 Image compression fundamentals, standards and practice*. Norwell, Massachusetts 02061 USA: Kluwer Academic Publishers, 2002.

[2] J. Matela, V. Rusnak, and P. Holub, “Efficient JPEG2000 EBCOT context modeling for massively parallel architectures,” in *Proc. IEEE Data Compression Conference*, Mar. 2011, pp. 423–432.

[3] M. Ciznicki, M. Kierzynka, P. Kopta, K. Kurowski, and P. Gepnerb, “Benchmarking JPEG 2000 implementations on modern CPU and GPU architectures,” *ELSEVIER Journal of Computational Science*, vol. 5, no. 2, pp. 90–98, Mar. 2014.

[4] Comprimato. (2014, Apr.) Comprimato JPEG2000@GPU. [Online]. Available: <http://www.comprimato.com>

[5] M. Ciznicki, K. Kurowski, and A. Plaza, “Graphics processing unit implementation of JPEG2000 for hyperspectral image compression,” *SPIE Journal of Applied Remote Sensing*, vol. 6, pp. 1–14, Jan. 2012.

[6] *High Throughput JPEG 2000 (HTJ2K): Call for Proposals*, ISO/IEC Std., 2017, document ISO/IEC JTC 1/SC29/WG1 N76037.

[7] F. Auli-Llinas, “Stationary probability model for bitplane image coding through local average of wavelet coefficients,” *IEEE Trans. Image Process.*, vol. 20, no. 8, pp. 2153–2165, Aug. 2011.

[8] F. Auli-Llinas and M. W. Marcellin, “Stationary probability model for microscopic parallelism in JPEG2000,” *IEEE Trans. Multimedia*, vol. 16, no. 4, pp. 960–970, Jun. 2014.

[9] F. Auli-Llinas, “Context-adaptive binary arithmetic coding with fixed-length codewords,” *IEEE Trans. Multimedia*, vol. 17, no. 8, pp. 1385–1390, Aug. 2015.

[10] F. Auli-Llinas, P. Enfedaque, J. C. Moure, and V. Sanchez, “Bitplane image coding with parallel coefficient processing,” *IEEE Trans. Image Process.*, vol. 25, no. 1, pp. 209–219, Jan. 2016.

[11] P. Enfedaque, F. Auli-Llinas, and J. C. Moure, “GPU implementation of bitplane coding with parallel coefficient processing for high performance image compression,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 28, no. 8, pp. 2272–2284, Aug. 2017.

[12] W. J. van der Laan, A. C. Jalba, and J. B. Roerdink, “Accelerating wavelet lifting on graphics hardware using CUDA,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 22, no. 1, pp. 132–146, Jan. 2011.

[13] P. Enfedaque, F. Auli-Llinas, and J. C. Moure, “Implementation of the DWT in a GPU through a register-based strategy,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 26, no. 12, pp. 3394–3406, Dec. 2015.

[14] T. M. Quan and W.-K. Jeong, “A fast discrete wavelet transform using hybrid parallelism on GPUs,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 27, no. 11, pp. 3088–3100, Nov. 2017.

[15] D. Merrill and M. Garland. (2016) Single-pass parallel prefix scan with decoupled look-back. [Online]. Available: <http://research.nvidia.com/sites/default/files/pubs/2016-03\Single-pass-Parallel-Prefix/nvr-2016-002.pdf>

# Chapter 3

## GPU architecture for wavelet-based video coding acceleration

# GPU architecture for wavelet-based video coding acceleration

Carlos DE CEA-DOMINGUEZ <sup>a,1</sup>, Juan C. MOURE <sup>b</sup>, Joan BARTRINA-RAPESTA <sup>a</sup>

and Francesc AULÍ-LLINÀS <sup>a</sup>

<sup>a</sup>*Department of Information and Communications Engineering,

Universitat Autònoma de Barcelona, Spain*

<sup>b</sup>*Department of Computer Architecture and Operating Systems,

Universitat Autònoma de Barcelona, Spain*

**Abstract.** The real time coding of high resolution JPEG2000 video requires specialized hardware architectures like Field-Programmable Gate Arrays (FPGAs). Commonly, implementations of JPEG2000 in other architectures such as Graphics Processing Units (GPUs) do not attain sufficient throughput because the algorithms employed in the standard are inherently sequential, which prevents the use of fine-grain parallelism needed to achieve the full GPU performance. This paper presents an architecture for an end-to-end wavelet-based video codec that uses the framework of JPEG2000 but introduces distinct modifications that enable the use of fine-grain parallelism for its acceleration in GPUs. The proposed codec partly employs our previous research on the parallelization of two stages of the JPEG2000 coding process. The proposed solution achieves real-time processing of 4K video in commodity GPUs, with much better power-efficiency ratios compared to server-grade Central Processing Unit (CPU) systems running the standard JPEG2000 codec.

**Keywords.** Wavelet-based video coding, high-throughput video coding, JPEG2000, GPU, CUDA.

## 1. Introduction

High definition video with resolutions ranging from 2K to 4K is nowadays common in devices such as TVs, digital cinema projectors, and mobiles. Among others, the JPEG2000 standard (ISO/IEC 15444) is employed for such video content in fields like TV production or digital cinema. This standard provides excellent coding performance and advanced features, such as quality progression, partial transmission, or error resilience [1]. Nonetheless, the algorithms employed to achieve them are very demanding computationally. They transform, code, and reorganize the data in three main stages that require multiple scans and coding operations. This results in long execution times and complex implementations. In the case of digital cinema, for instance, field-programmable gate arrays are required to achieve real-time decoding of 2K and 4K video.

---

<sup>1</sup>This work has been partially supported by the Spanish Ministry of Economy and Competitiveness and the European Regional Development Fund under Grants TIN2015-71126-R, TIN2017-84553-C2-1-R and RTI2018-095287-B-I00 (MINECO/FEDER, UE), and by the Catalan Government under Grants 2017SGR-463 and 2017SGR-313.

The first stage of most wavelet-based image/video codecs (including JPEG2000) reduces the image redundancy through the discrete wavelet transform (DWT). The operations performed by the DWT can be parallelized, so DWT implementations for parallel architectures have been widely studied in the literature [2–4]. The second stage employs bitplane coding together with arithmetic coding to reduce the statistical redundancy of wavelet coefficients. This stage scans the coefficients one-by-one, producing a result for each that can not be obtained without all the previous. This causality renders parallelism at the bitplane coding engine a very challenging task. Even though there are some works in the literature with this purpose [5–12], none of them is able to exploit the full potential of GPUs. The third stage of the pipeline reorganizes the data and forms the compressed file.

Aware of the high complexity of JPEG2000, the Joint Photographic Experts Group launched in June 2017 a call for proposals [13] aimed to develop an alternate algorithm for the bitplane and arithmetic coding stage that increases the throughput of the codec. This JPEG2000 part is described in [14, 15]. It increases performance about  $10\times$  though penalizes coding performance about 10%. Also, it sacrifices quality scalability, which may become an issue in image/video transmission scenarios.

In the same line of work but well before this call for proposals, we started a line of research whose final goal is to devise an end-to-end image/video codec that can exploit the fine-grain parallelism of GPUs while maintaining the same features of JPEG2000. For the bitplane and arithmetic coding engine, we introduced a bitplane coding strategy with parallel coefficient processing (BPC-PaCo) that does not hold dependencies among coefficients, allowing efficient implementations in GPUs [16–19]. This engine can effectively exploit the parallelism of SIMD architectures, which results in high speedup factors and lower power consumption with respect to the fastest implementations of JPEG2000, either executed in multi-core CPUs or in GPUs. Evidently, BPC-PaCo is not compliant with the standard, but it does *not* sacrifice quality scalability and it penalizes coding performance only about 2%. For the DWT, we also proposed an efficient architecture in [2] that achieves high performance in GPUs.

The first implementation of the end-to-end codec for GPUs was presented in [20]. Nonetheless, that implementation is only able to process individual high-resolution images. This paper presents a vastly improved implementation that processes video sequences in real-time thanks to the introduction of stream management with multiple CPU threads, a double-buffer strategy, and event handling to synchronize GPU and CPU operations. Experimental results achieved with consumer-grade GPUs suggest that the proposed codec achieves a throughput that allows encoding and decoding 4K video in real-time and yields highly better power consumption ratios than JPEG2000 codecs executed in CPUs.

The rest of the paper is structured as follows. Section 2 explains the basics of the Nvidia GPU architecture. Section 3 briefly describes the different parts of the JPEG2000 standard. Section 4 describes the proposed end-to-end codec in detail. Section 5 provides experimental results achieved when coding high resolution video in two GPUs and compares our results with Kakadu [21], one of the best multi-thread JPEG2000 implementations. The last section concludes summarizing this work.

## 2. Overview of Nvidia GPUs

Nvidia GPUs are hardware devices with tens of individual computing units called streaming multiprocessor (SMs). These SMs can work independently, allowing the GPU to process different sequences of operations, called streams, in parallel. This permits the execution of multiple algorithms in an interleaved fashion, which increases the opportunities for parallelism and thereby the throughput achieved. The SMs execute multiple 32-wide SIMD instructions (i.e., vector instructions) simultaneously.

GPUs from Nvidia employ the CUDA programming model, which defines a computation structure composed by (potentially) hundreds of thousands of threads grouped into warps (each with 32-threads), with each warp assigned to a thread block [22]. While the hardware device executes 32-wide SIMD instructions, a software CUDA thread is the virtualization of one of the lanes of the instruction. From the first CUDA-compatible architecture (v1.0) up to Pascal (v6.2), warps execute instructions in a lock-step synchronous fashion, featuring an implicit synchronization at the end of any divergence [23]. From Volta (v7.0) onward, the implicit synchronization is not included at the end of the branching instructions, and must be coded explicitly if needed [24]. Warps in a thread block are executed asynchronously and can cooperate via on-chip fast memories, using explicit synchronizing barrier instructions when required.

The CUDA memory model is hierarchically organized as follows: there is a space of local memory private to each thread, a shared memory private to each thread block, and a global memory public to all threads in the kernel application. From a microarchitecture point of view, the local memory reserved per thread is located either in the registers or the off-chip memory, depending on the available resources. In the proposed implementation, the host memory (CPU RAM) and the device memory (GPU VRAM) are accessed as different, non-unified memory regions, explicitly managing the moment and the amount of data which are copied between them.

## 3. Overview of JPEG2000

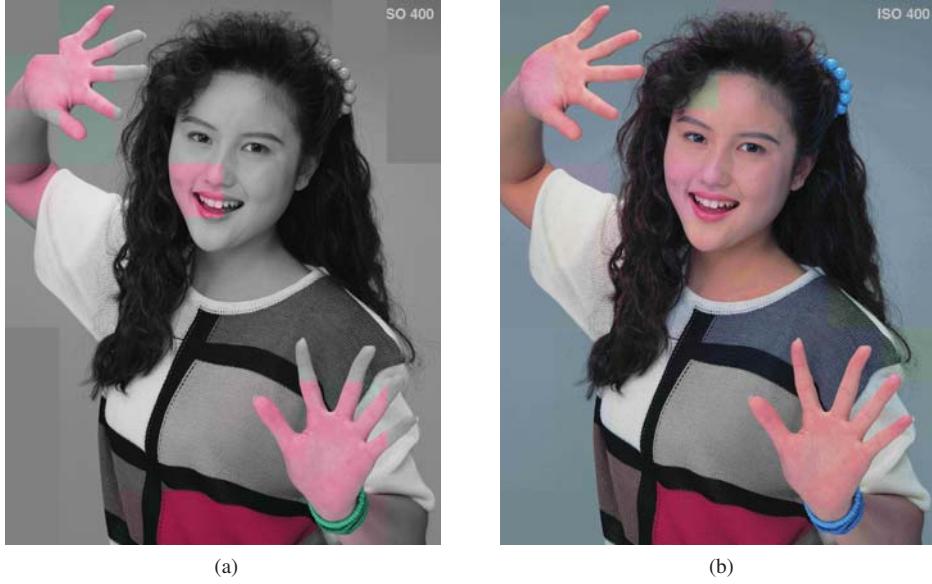

Our GPU codec carries out the same steps as JPEG2000, so they are briefly described below. Depending on the encoding mode employed, either lossy or lossless, the operations involved may be irreversible or reversible, respectively. Irreversible operations improve the compression ratio though they sacrifice image quality slightly.

The first stage of the coding pipeline is the DWT. Our implementation uses a lifting scheme approach [25] due to its low computational complexity. It applies a series of arithmetic operations first row by row and then column by column. The DWT outputs four different subbands, with three of them including smaller detail images and the fourth including the original image at lower resolution and higher energy. These operations are carried out (typically) 5 times within the fourth subband, with each iteration in a lower resolution subband. For lossy compression, the operations employ floating-point arithmetic, so the resulting data are converted to integers before the next stage. This conversion is performed via deadzone quantization [1].

The second stage applies bitplane coding with arithmetic coding. The wavelet coefficients are conceptually partitioned in small sets of typically  $64 \times 64$  wavelet coefficients, called codeblocks. The strategy adopted to process each codeblock consists in coding

the most relevant information first. The data are divided in bitplanes, with each bitplane containing the set of bits from the same binary position of the unsigned binary representation of each coefficient. Encoding begins from the most significant bitplane (i.e., the one with the highest magnitude within the codeblock) to the lowest one. In JPEG2000, each bitplane is scanned in three coding passes. The first pass is called Significance Propagation Pass. This pass only processes the bits of those coefficients that have at least one significant neighbor. A coefficient is called significant from that bitplane that holds the first non-zero bit to the lowest. The second coding pass is called Magnitude Refinement Pass. It visits the coefficients that are significant in higher bitplanes. The Cleanup Pass processes the coefficients not visited in the previous passes. This coding strategy aims to code the information which holds more information first, effectively reducing distortion [26]. Each bit emitted by the bitplane coder is fed to the arithmetic coder along with its contextual information. The context considers the number of neighbors that are significant, employed to determine a probability for the processed bit. This probability is employed by the arithmetic coder to generate the final bitstream.

The compressed data of codeblocks can be truncated to fit a target bitrate. The method to carry out this optimization process is not defined in the standard, so each implementation may adopt its own solution. The final stage reorganizes the data and adds ancillary information needed by the decoder to decode the original image. The decoder carries out the same steps of the encoder in reverse order.

#### 4. Proposed Codec

The proposed codec is implemented in CUDA. CUDA is employed instead of OpenCL because it provides the latest improvements in the newest architectures. JPEG2000 exposes fine-grain parallelism in all coding stages except for the bitplane coder. Except from the bitplane and arithmetic coder, our proposal produces the same output as JPEG2000 in each stage employing a parallel architecture that extracts most of the GPU performance. BPC-PaCo is employed in the bitplane coding engine [18, 19]. As previously stated, this engine is not compliant with the standard though it preserves the same features and allows parallelism at a fine-grain level.

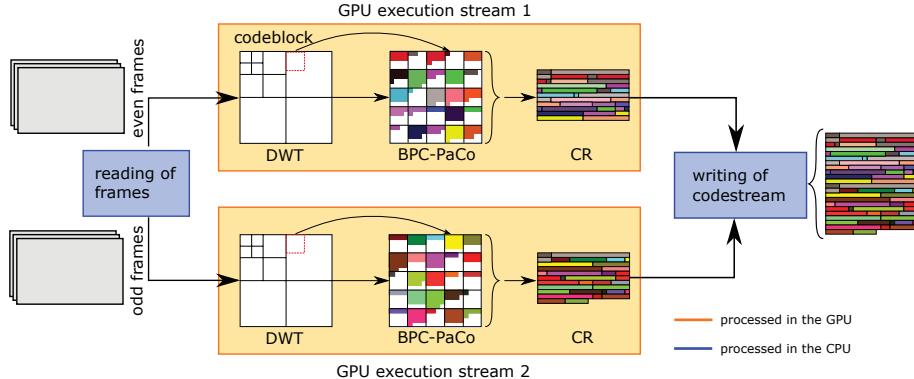

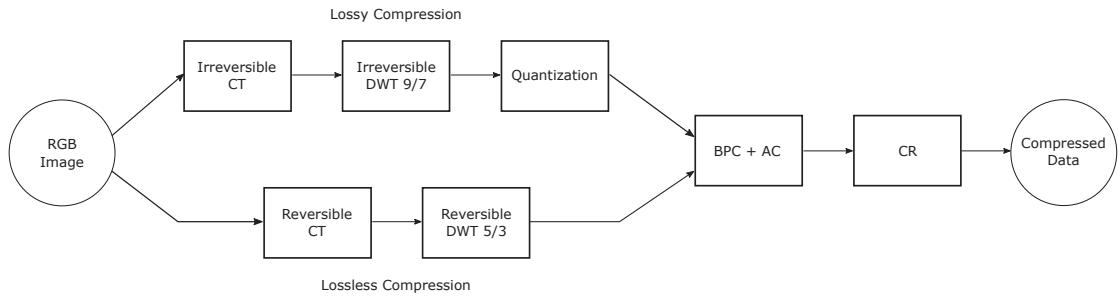

Algorithm 1 describes the main steps of the proposed codec. Fig. 1 also illustrates its main stages. First, the required memory to process the entire video is allocated in the host CPU RAM (lines 1-2) and in the GPU DRAM, which are respectively referred to as  $M^H$  and  $M^D$ . Next, two CPU threads are created, denoted by  $t_1$  and  $t_2$  in Algorithm 1, to manage the input/output from/to the hard disk (lines 3-6 and 10-13, respectively). The codec utilizes a double-buffer strategy per stream. This double-buffer is employed for both reading the raw data and writing the compressed file, so four buffers are allocated for each stream. These buffers are referred to as  $M^H[i]$  and  $M^D[i]$  for the input, and  $M^H[o]$  and  $M^D[o]$  for the output, with  $\{i, o\} \in \{1..2\}$ . When reading, the data from one buffer are processed while the other is filled. For writing, the compressed data are transferred to the host from one GPU buffer while the other is already empty and can be filled with compressed data from the frame that is being processed. This buffer structure enables the parallelization of the processing task in two streams, removes the risk of a system memory overflow and increases the utilization of the system resources. Both threads are constantly checking the buffers to start data transfers as soon as possible.

**Figure 1.** Illustration of the steps performed by the proposed video codec using two streams of execution.

**Algorithm 1.** Main routine of the codec

```

1: CPUMemoryAllocation()

2: GPUGlobalMemoryAllocation()

3: for each empty  $M^H[i]$  do

4:    $M^H[i] \leftarrow \text{HDRead}()$

5:    $M^D[i] \leftarrow M^H[i]$

6: end for

7:  $D \leftarrow \text{DWT\_Q}(M^D[i])$

8:  $\{B_l\} \leftarrow \text{BPC\_AC}(D)$

9:  $M^D[o] \leftarrow \text{CR}(\{B_l\})$

10: for each filled  $M^D[o]$  do

11:    $M^H[o] \leftarrow M^D[o]$

12:    $\text{HDWrite}(M^H[o])$

13: end for

```

From lines 7 to 9 in Algorithm 1 the GPU functions, or kernels, to code a frame are called. The compression of each frame is carried out with three kernels. Two GPU streams, denoted by  $S_{1,2}$ , are employed to process a maximum of two frames simultaneously. Typically, each kernel transfers the data to be processed from the global memory  $M^D[i]$  to the local memory  $R$  to accelerate memory accesses. The kernel  $\text{DWT\_Q}(\cdot)$  receives the original frame data as input and generates quantized wavelet coefficients that are the input of  $\text{BPC\_AC}(\cdot)$ .

$\text{BPC\_AC}(\cdot)$  generates a bitstream per codeblock, referred to as  $B_l$ , with  $l \in \{1.. \hat{L}\}$ ,  $\hat{L}$  being the number of codeblocks in each frame. This set of bitstreams is reorganized in the last kernel  $\text{CR}(\cdot)$ , which also adds ancillary information for decoding. This kernel does not transfer the compressed data to local registers since it only needs to reorganize the data in global memory.

As illustrated in Fig. 1, the use of two GPU streams allows the processing of two frames in parallel, increasing the throughput of the codec. Evidently, the three stages of the coding pipeline are carried out sequentially in each stream. Once a frame is coded, the resulting data are sent asynchronously to the host memory and the stream begins processing the next frame immediately. The three kernels are devised and implemented to extract fine-grain parallelism in the GPU. The proposed GPU-oriented architecture is able to process either high-resolution images or video in real time. Next, a brief description of each kernel is provided.

#### 4.1. Discrete wavelet transform

The adopted DWT implementation [2] in our codec employs a register-based acceleration strategy [27] that transfers data from the global memory  $M^D[i]$  to local registers, avoiding the use of shared memory. Threads communicate among them via shuffle instructions. This strategy allows data reuse and sharing, taking advantage of the fine-grain parallelism and data access locality of the algorithm. First, the image is conceptually divided in blocks that are independently processed by warps. This permits coarse-grain parallelism, populating more SMs of the GPU. The blocks take into account data dependencies of the transform, so they include some samples from adjacent blocks forming a halo. The halo is needed to obtain the same result as if the DWT was applied to the whole image at once. Within each block, the DWT is applied via the lifting scheme, which alternatively processes in the vertical and horizontal axis odd and even samples. If the compression mode is lossy, quantization is applied after the DWT since the next kernel requires integers.

#### 4.2. Bitplane coding with parallel coefficient processing

The coefficients resulting from the  $\text{DWT.Q}(\cdot)$  are conceptually partitioned in small sets called codeblocks. Typically, each codeblock contains  $64 \times 64$  coefficients. They are transferred to the local memory to speed up the processing, like in the previous kernel. Codeblocks do not hold dependencies among them, so they are processed independently. The processing of codeblocks in parallel requires coarse-grain, control-divergent strategies that are employed in many implementations of the original JPEG2000 standard. In addition to this parallelism, the coding engine BPC-PaCo employed in this stage extracts fine-grain parallelism in the coding of the codeblock.

BPC-PaCo is based on bitplane coding, like JPEG2000. A particular feature of BPC-PaCo is that it conceptually divides the codeblock in 32 columns holding two coefficients each. Each codeblock is processed by a warp, and each 2-coefficient column is processed by a thread of the warp. Each thread carries out a modified version of significance coding that does not require cleanup, and the magnitude refinement pass. To employ only 2 coding passes instead of 3 like in JPEG2000 significantly increases the throughput [19]. Each emitted bit is coded via context-based arithmetic coding. To form the context of the coefficient, threads need to cooperate among them so that each coefficient can obtain information of all its adjacent neighbors. Again, this cooperation is performed via shuffle instructions. BPC-PaCo utilizes 32 arithmetic coders so that each thread in the warp can code all bits that it emits. The codewords generated by the arithmetic coders are interleaved in an optimal fashion in the final bitstream generated for the codeblock. The result of kernel  $\text{BPC.AC}(\cdot)$  is the set  $\{B_l\}$  that contains a bitstream per codeblock, with  $l \in \{1.. \hat{L}\}$  and  $\hat{L}$  being the number of codeblocks per component. The probability model employed by the arithmetic coders is static, i.e., it employs pre-defined probabilities that are computed via a training set of images. This coding strategy permits the use of coarse- and fine-grain parallelism, since both the codeblocks and the coefficients within them are coded in parallel.

|                    | <i>SMs</i> | <i>cores</i><br>$\times SM$ | <i>clock</i><br><i>frequency</i> | <i>memory</i><br><i>bandwidth</i> | <i>peak FP32</i><br><i>throughput</i> | <i>TDP</i> | <i>memory</i><br><i>size</i> |

|--------------------|------------|-----------------------------|----------------------------------|-----------------------------------|---------------------------------------|------------|------------------------------|

| <i>GTX 1080 Ti</i> | 28         | 128                         | 1923 MHz                         | 484 GB/s                          | 13.78 TFlops                          | 250 W      | 11 GB                        |

| <i>GTX 960M</i>    | 5          | 128                         | 1176 MHz                         | 80 GB/s                           | 1.5 TFlops                            | 60 W       | 2 GB                         |

**Table 1.** Features of the GPUs employed.

#### 4.3. Codestream reorganization (CR)

The bitstreams produced for each codeblock have different size depending on the data coded, as depicted in Fig. 1. This results in data scattered in the output buffer of the global memory. The final stage of the coding process reorganizes these data putting them in a compact structure that can be transferred to the main memory of the host  $M^H[\phi]$  and then written to the disk. This stage also includes auxiliary information in the final codestream for decoding.

When a warp compresses a codeblock, the lengths of the bitstreams are stored in a vector of integers  $L = \{L_1, L_2, \dots, L_{\hat{L}}\}$ . Then an aggregated list of lengths, i.e.,  $L' = \{0, L_1, L_1 + L_2, \dots, L_1 + \dots + L_{\hat{L}}\}$  is generated via the Device Scan primitive from the Nvidia CUB framework [28]. To accelerate the access to this list, a fast lookup table, denoted by  $LUT_{L'}$  is created. This LUT is generated applying a binary search over  $L'$  in which each position represents some positions of the original map. Our experience indicates that speedups about  $2\times$  are achieved by using such a strategy. Kernel  $CR(\cdot)$  then uses this LUT so that each thread transfers 2 bytes of the codeblock's data to the final output buffer.

## 5. Experimental Results

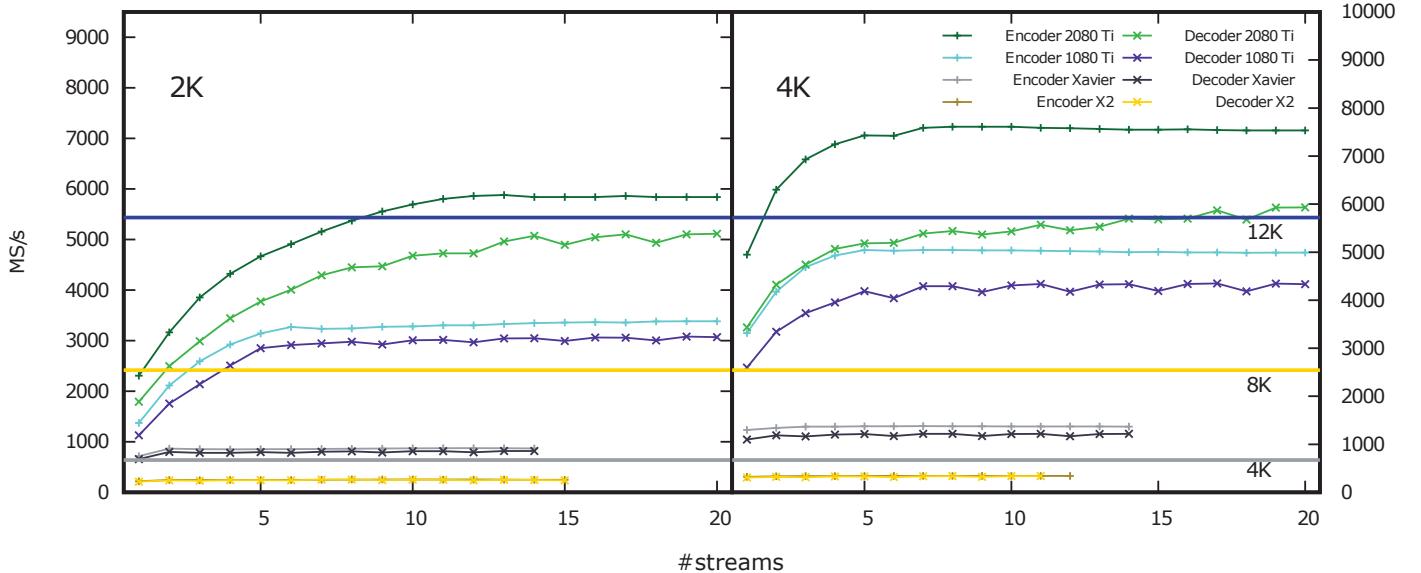

The throughput achieved by the proposed codec is compared with Kakadu v7.A.2 [21] in the experiments below. Kakadu is among the fastest implementations of JPEG2000, with multi-thread support for multi-core CPUs. It is programmed in C++ and is heavily optimized via assembly instructions. In the tests below, Kakadu is executed in a platform that has 4 AMD Opteron 6376 CPUs running at 2.3 GHz, employing a total of 32 threads of execution. Results from other JPEG2000 implementations in GPUs [11, 12] are not included herein because their throughput is similar or inferior to that of Kakadu, with the exception of Comprimate [10], which does not offer any option to test its implementation. Our codec is executed in the consumer-grade GPUs reported in Table 1, namely, the high-end GTX 1080 Ti for desktops, and the low-end GTX 960M for laptops. The tests code a video sequence of 948 frames of size  $2048 \times 832$ , gray-scale, and bit-depth of 8 bits per sample. The results shown below do not consider the I/O time needed to read/write the files from/to the disk since that may affect execution times significantly depending on the device employed. In all implementations, data are read from the host memory, where they are preloaded before starting the execution.

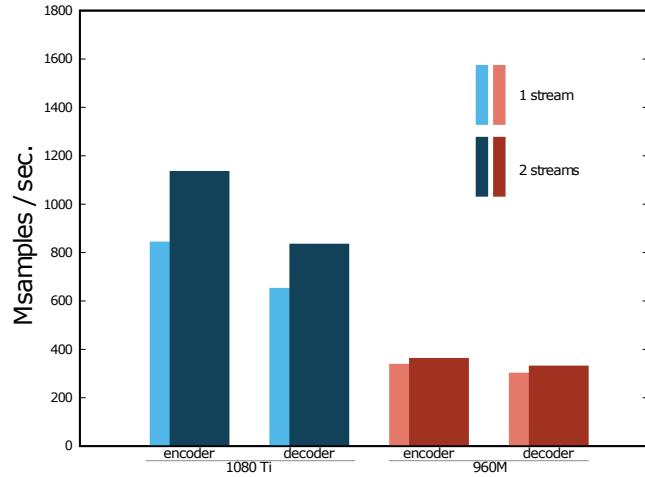

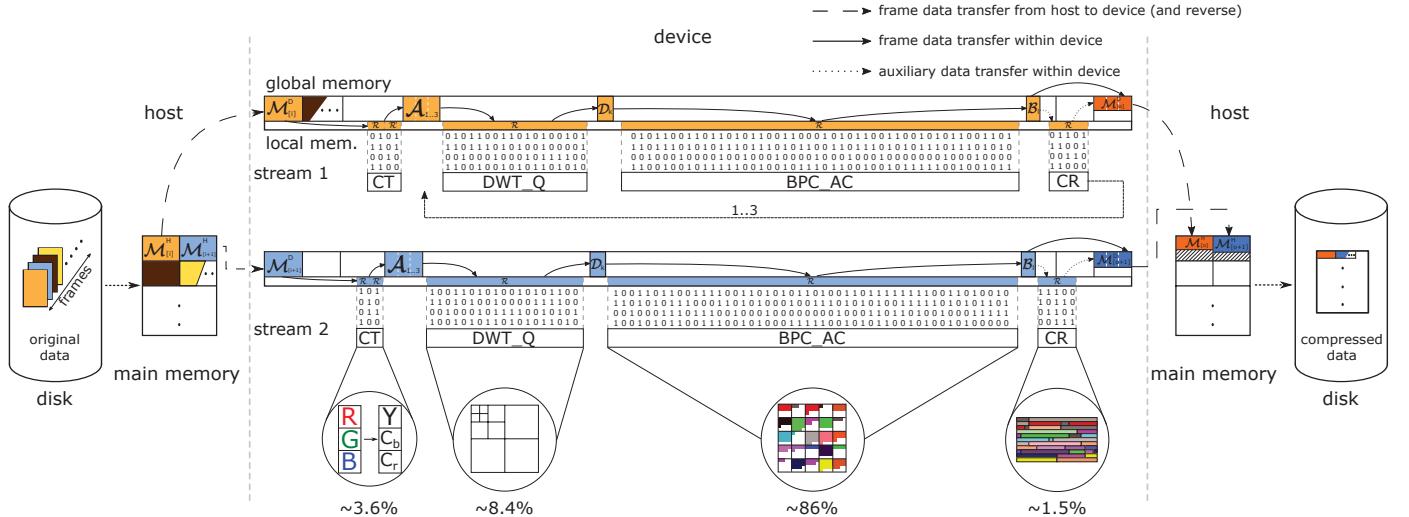

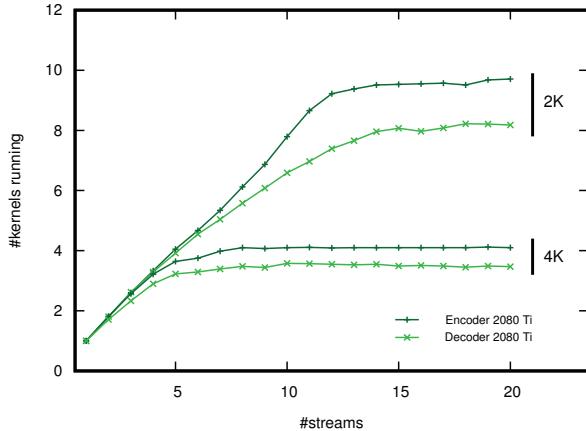

The first test evaluates the throughput achieved by our codec when using 1 or 2 GPU streams. The results are depicted in Fig. 2. The vertical axis reports the throughput achieved, in Mega samples per second (Msamples/sec.). The results for 1 and 2 streams are depicted for each GPU and for the encoding and decoding process. Using 2 streams provides a performance increase about 26% (7%) in the encoding process and 22% (9%)

**Figure 2.** Evaluation of the throughput achieved when using 1 and 2 execution streams.

**Figure 3.** Evaluation of the throughput achieved by the proposed codec and Kakadu.

in the decoding process for the 1080 Ti (960M) GPU. The performance gain depends on the peak throughput of each GPU. The 1080 Ti has ample resources to process more than one frame whereas the 960M almost saturates its resources when coding a single frame (i.e., 1 stream).

The second test evaluates the throughput of the proposed codec running 2 streams and Kakadu. Fig. 3 depicts the obtained results. The proposed codec executed in the 1080 Ti yields a throughput about 5× higher than that of Kakadu. For the 960M, the throughput achieved is about 2× higher than that of Kakadu. Nonetheless, we recall that Kakadu is executed in an expensive multi-CPU platform, whereas the proposed codec employs commodity GPUs. Fig. 3 also depicts the throughput needed to process digital cinema video at resolutions of 2K and 4K in real time (straight horizontal lines). The results suggest that the proposed codec running in the 1080 Ti (960M) can process 4K

**Figure 4.** Evaluation of the power efficiency achieved by the proposed codec and Kakadu.

(2K) video in real time.

The third test evaluates power consumption. Fig. 4 depicts the results yield by Kakadu and our codec. In this case, the vertical axis reports Msamples processed per Watt consumed. Kakadu employs four high-end AMD Opteron processors, each with a thermal design power (TDP) of 115W, whereas the 1080 Ti and 960M GPUs have a TDP of 250W and 60W, respectively. The low power consumption of the 960M makes it the most efficient, being approximately 12 $\times$  more power efficient than Kakadu for encoding and about 17 $\times$  for decoding. The proposed codec executed in the 1080 Ti is less power-hungry than Kakadu too, with increases in efficiency about 9 $\times$  and 10 $\times$  for the encoder and decoder, respectively.

## 6. Conclusions

The JPEG2000 standard is mainly devised to exploit the coarse-grain parallelism provided in CPUs. When employed to code high-resolution video in scenarios such as TV production or digital cinema, implementations need specialized hardware or expensive computer platforms to meet real-time requirements. So far, implementations for cheaper devices such as GPUs are not able to achieve high throughput because the innermost algorithms of the coding system do not exhibit enough fine-grain parallelism. This paper introduces a fully parallel end-to-end codec that employs the framework of JPEG2000 but that provides –in all stages of the coding pipeline– distinct modifications that permits the use of fine-grain parallelism. This can be effectively exploited when executed in architectures that highly rely on SIMD parallelism such as those found in Nvidia GPUs. Experimental results coding high-resolution video indicates that the proposed codec is 5 $\times$  faster than the most efficient implementations of JPEG2000 while reducing the power consumption more than 10 $\times$ . None of the advanced features of JPEG2000 are sacrificed in the proposed codec, so it is ideal for scenarios that deal with massive data sets and/or power constraints.

## References

- [1] D. S. Taubman and M. W. Marcellin, *JPEG2000 Image compression fundamentals, standards and practice*. Norwell, Massachusetts 02061 USA: Kluwer Academic Publishers, 2002.

- [2] P. Enfedaque, F. Auli-Llinas, and J. C. Moure, “Implementation of the DWT in a GPU through a register-based strategy,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 26, no. 12, pp. 3394–3406, Dec. 2015.

- [3] T. M. Quan and W.-K. Jeong, “A fast discrete wavelet transform using hybrid parallelism on GPUs,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 27, no. 11, pp. 3088–3100, Nov. 2017.

- [4] W. J. van der Laan, A. C. Jalba, and J. B. Roerdink, “Accelerating wavelet lifting on graphics hardware using CUDA,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 22, no. 1, pp. 132–146, Jan. 2011.

- [5] S. Datla and N. S. Gidjala, “Parallelizing motion JPEG 2000 with CUDA,” in *Proc. IEEE International Conference on Computer and Electrical Engineering*, Dec. 2009, pp. 630–634.

- [6] R. Le, I. R. Bahar, and J. L. Mundy, “A novel parallel tier-1 coder for JPEG2000 using GPUs,” in *Proc. IEEE Symposium on Application Specific Processors*, Jun. 2011, pp. 129–136.

- [7] J. Matela, V. Rusnak, and P. Holub, “Efficient JPEG2000 EBCOT context modeling for massively parallel architectures,” in *Proc. IEEE Data Compression Conference*, Mar. 2011, pp. 423–432.

- [8] M. Ciznicki, K. Kurowski, and A. Plaza, “Graphics processing unit implementation of JPEG2000 for hyperspectral image compression,” *SPIE Journal of Applied Remote Sensing*, vol. 6, pp. 1–14, Jan. 2012.

- [9] M. Ciznicki, M. Kierzynka, P. Kopta, K. Kurowski, and P. Gepnerb, “Benchmarking JPEG 2000 implementations on modern CPU and GPU architectures,” *ELSEVIER Journal of Computational Science*, vol. 5, no. 2, pp. 90–98, Mar. 2014.

- [10] Comprimate. (2014, Apr.) Comprimate. [Online]. Available: <http://www.comprimate.com>

- [11] (2016, Jun.) CUDA JPEG2000 (CUJ2K). [Online]. Available: <http://cuj2k.sourceforge.net>

- [12] (2016, Jun.) GPU JPEG2K. [Online]. Available: <http://apps.man.poznan.pl/trac/jpeg2k/wiki>

- [13] *High Throughput JPEG 2000 (HTJ2K): Call for Proposals*, ISO/IEC Std., 2017, document ISO/IEC JTC 1/SC29/WG1 N76037.

- [14] D. Taubman, A. Naman, and R. Mathew, “FBCOT: a fast block coding option for JPEG 2000,” in *Proc. SPIE Applications of Digital Image Processing*, vol. 10396, Sep. 2017, pp. 1–18.

- [15] D. Taubman, A. Naman, R. Mathew, and M. D. Smith, “High throughput JPEG 2000 (HTJ2K): New algorithms and opportunities,” *SMPTE Motion Imaging Journal*, vol. 127, no. 9, pp. 1–7, Oct. 2018.

- [16] F. Auli-Llinas, “Stationary probability model for bitplane image coding through local average of wavelet coefficients,” *IEEE Trans. Image Process.*, vol. 20, no. 8, pp. 2153–2165, Aug. 2011.

- [17] F. Auli-Llinas and M. W. Marcellin, “Stationary probability model for microscopic parallelism in JPEG2000,” *IEEE Trans. Multimedia*, vol. 16, no. 4, pp. 960–970, Jun. 2014.

- [18] F. Auli-Llinas, P. Enfedaque, J. C. Moure, and V. Sanchez, “Bitplane image coding with parallel coefficient processing,” *IEEE Trans. Image Process.*, vol. 25, no. 1, pp. 209–219, Jan. 2016.

- [19] P. Enfedaque, F. Auli-Llinas, and J. C. Moure, “GPU implementation of bitplane coding with parallel coefficient processing for high performance image compression,” *IEEE Trans. Parallel Distrib. Syst.*, vol. 28, no. 8, pp. 2272–2284, Aug. 2017.

- [20] C. de Cea-Dominguez, P. Enfedaque, J. Moure, J. Bartrina-Rapesta, and F. Auli-Llinas, “High throughput image codec for high-resolution satellite images,” in *Proc. IEEE International Geoscience and Remote Sensing Symposium*, Jul. 2018, pp. 6524–6527.

- [21] D. Taubman. (2018, Dec.) Kakadu software. [Online]. Available: <http://www.kakadusoftware.com>

- [22] “CUDA, C Programming guide,” Tech. Rep., Jan. 2015. [Online]. Available: <http://docs.nvidia.com/cuda/cuda-c-programming-guide>

- [23] Nvidia. (2018, Jan.) Warp level primitives. [Online]. Available: <https://devblogs.nvidia.com/using-cuda-warp-level-primitives/>

- [24] ——. (2019, Jun.) Nvidia Tesla V100 GPU architecture. [Online]. Available: <http://images.nvidia.com/content/volta-architecture/pdf/volta-architecture-whitepaper.pdf>

- [25] W. Sweldens, “The lifting scheme: A construction of second generation wavelets,” *SIAM Journal on Mathematical Analysis*, vol. 29, no. 2, pp. 511–546, 1998.

- [26] F. Auli-Llinas and M. W. Marcellin, “Scanning order strategies for bitplane image coding,” *IEEE Trans. Image Process.*, vol. 21, no. 4, pp. 1920–1933, Apr. 2012.

- [27] A. Chacon, S. Marco-Sola, A. Espinosa, P. Ribeca, and J. C. Moure, “Boosting the FM-index on the GPU: effective techniques to mitigate random memory access,” *IEEE/ACM Trans. Comput. Biol. Bioinformatics*, vol. 12, no. 5, pp. 1048–1059, Sep. 2015.

- [28] Nvidia. (2018, Dec.) CUB framework. [Online]. Available: <https://nvlabs.github.io/cub/>

## Chapter 4

# GPU Oriented Architecture for an End-to-End Image Video Codec Based on JPEG2000

# GPU-oriented architecture for an end-to-end image/video codec based on JPEG2000

CARLOS DE CEA-DOMINGUEZ<sup>1</sup>, JUAN C. MOURE<sup>2</sup>, JOAN BARTRINA-RAPESTA<sup>1</sup>, AND FRANCESC AULÍ-LLINÀS, (Senior Member, IEEE)<sup>1</sup>

<sup>1</sup>Department of Information and Communications Engineering, Universitat Autònoma de Barcelona, Spain (phone: +34 935811861; fax: +34 935813443; e-mail: carlos.decea@uab.cat, joan.bartrina@uab.cat, francesc.auli@uab.cat)

<sup>2</sup>Department of Computer Architecture and Operating Systems, Universitat Autònoma de Barcelona, Spain (e-mail: juancarlos.moure@uab.es)

Corresponding author: Carlos de Cea-Dominguez (e-mail: carlos.decea@uab.cat).

This work has been partially supported by the Spanish Ministry of Economy and Competitiveness and the European Regional Development Fund under Grants TIN2017-84553-C2-1-R and RTI2018-095287-B-I00 (MINECO/FEDER, UE), and by the Catalan Government under Grants 2017SGR-463 and 2017SGR-313. Copyright (c) 2020 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to [pubs-permissions@ieee.org](mailto:pubs-permissions@ieee.org).

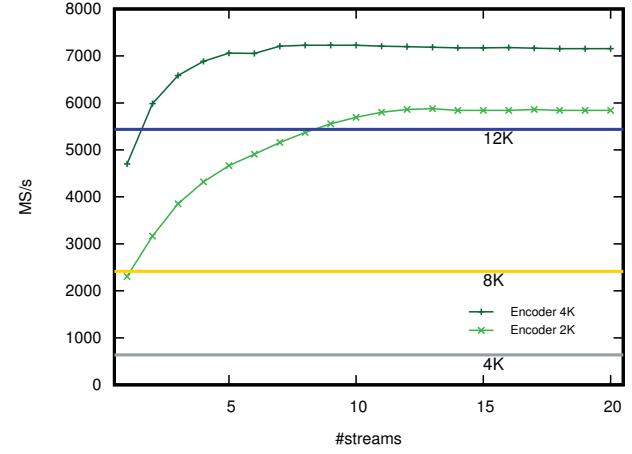

**ABSTRACT** Modern image and video compression standards employ computationally intensive algorithms that provide advanced features to the coding system. Current standards often need to be implemented in hardware or using expensive solutions to meet the real-time requirements of some environments. Contrarily to this trend, this paper proposes an end-to-end codec architecture running on inexpensive Graphics Processing Units (GPUs) that is based on, though not compatible with, the JPEG2000 international standard for image and video compression. When executed in a commodity Nvidia GPU, it achieves real time processing of 12K video. The proposed S/W architecture utilizes four CUDA kernels that minimize memory transfers, use registers instead of shared memory, and employ a double-buffer strategy to optimize the streaming of data. The analysis of throughput indicates that the proposed codec yields results at least 10 $\times$  superior on average to those achieved with JPEG2000 implementations devised for CPUs, and approximately 4 $\times$  superior to those achieved with hardwired solutions of the HEVC/H.265 video compression standard.

**INDEX TERMS** Wavelet-based image coding, high-throughput image coding, JPEG2000, GPU, CUDA.

## I. INTRODUCTION