**ADVERTIMENT.** L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: https://creativecommons.org/licenses/?lang=ca

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: https://creativecommons.org/licenses/? lang=es

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: (c) (1) (a) https://creativecommons.org/licenses/?lang=en

#### Universitat Autònoma de Barcelona

Departament de Microelectrònica i Sistemes Electrònics

# Low-Power High-Resolution $\Delta\Sigma M$ for Next Generation Space Analog-to-Digital Converters

Alejandro Suanes Pérez

Memòria de Tesi presentada per optar al títol de

Doctor en Enginyeria Electrònica i de Telecomunicació

Novembre 2021

Francesc Serra-Graells, Professor Titular del Departament de Microelectrònica i Sistemes Electrònics, Universitat Autònoma de Barcelona, i Michele Dei, Department of Information Engineering, Università di Pisa,

# Certifiquen

que la Memòria de Tesi Low-Power High-Resolution  $\Delta\Sigma M$  for Next Generation Space Analog-to-Digital Converters presentada per Alejandro Suanes Pérez per optar al títol de Doctor en Enginyeria Electrònica i de Telecomunicació s'ha realitzat sota la seva direcció a Institut de Microelectrònica de Barcelona pertanyent al Centro Nacional de Microelectrónica del Consejo Superior de Investigaciones Científicas i ha estat tutoritzada en el Departament de Microelectrònica i Sistemes Electrònics de la Universitat Autònoma de Barcelona (UAB).

| Directors | Francesc Serra-Graells |       |

|-----------|------------------------|-------|

|           | Michele Dei            |       |

|           |                        |       |

|           |                        |       |

|           | a                      | de de |

## Resum

El principal objectiu d'aquesta tesi doctoral és el disseny d'ADCs de baix consum i alta resolució de tipus  $\Delta\Sigma$  per a aplicacions d'espai, tot i que les contribucions són vàlides per a escenaris de sensat de propòsit general on es requereix un gran rang dinàmic. L'estratègia  $\Delta\Sigma$  s'ha escollit com a punt de partida degut al seu alt rendiment i fiabilitat. En particular, les implementacions amb capacitats commutades (SC) són d'especial interès en el treball presentat, les quals es construeixen mitjançant l'ús de nous circuits.

Amb la intenció de definir el procés d'optimització i de facilitar al dissenyador la realització de les tasques tant com sigui possible, s'ha desenvolupat una metodologia de disseny basada en models matemàtics. A més, aquesta metodologia s'han combinat amb tècniques de disseny especials per incrementar la robustesa dels circuits CMOS enfront de la radiació.

Una limitació important en dissenys d'ADCs de baixa freqüència i alta resolució és el soroll *flicker*. Per prevenir la degradació de la resolució causada per aquest efecte, es proposa un mecanisme de cancel·lació de soroll *flicker* mitjançant circuits de capacitats commutades. Aquesta modificació del modulador  $\Delta\Sigma$  ( $\Delta\Sigma$ M), en conjunt amb altres noves tècniques i circuits, permeten obtenir una bona optimització del consum de l'ADC i mantenir les seves prestacions.

L'arquitectura  $\Delta\Sigma$ M Multi-bit proposta s'ha implementat en els tres nodes de tecnologies CMOS 180 nm, 65 nm i 22 nm. El propòsit d'aquest estudi de portabilitat implementacions és descobrir els reptes de disseny que suposa la migració tecnològica, permetent així validar la metodologia de disseny i explorar els potencials beneficis de l'escalat, tant tecnològic com de la tensió d'alimentació.

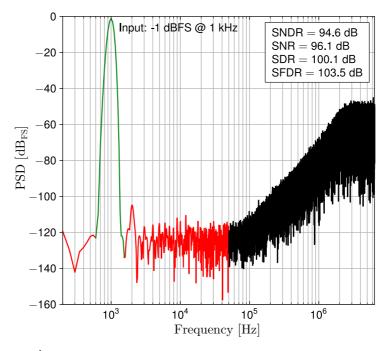

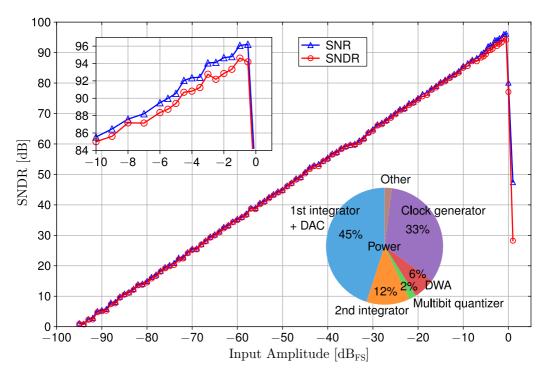

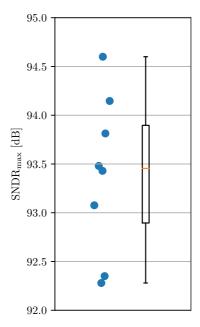

Un  $\Delta\Sigma$ M SC de 0.8mW 50kHz 94.6dB-SNDR lliure de bootstrapping i amb cancel·lació de soroll flicker s'ha fabricat en una tecnologia CMOS de 180 nm i s'ha caracteritzat experimentalment. Les mesures mostren una millora en l'estat de l'art de la FoM en comparació amb convertidors de característiques similars publicats a la literatura. Els resultats també mostren una baixa variabilitat entre diferents mostres, demostrant la robustesa del disseny enfront a la tecnologia. A més, la robustesa d'aquests xips enfront de radiació s'ha comprovat mitjançant un test de dosi total de radiació. Els resultats mostren que l'ADC  $\Delta\Sigma$ M pot suportar com a mínim nivells de radiació adequats per a la majoria de missions espacials.

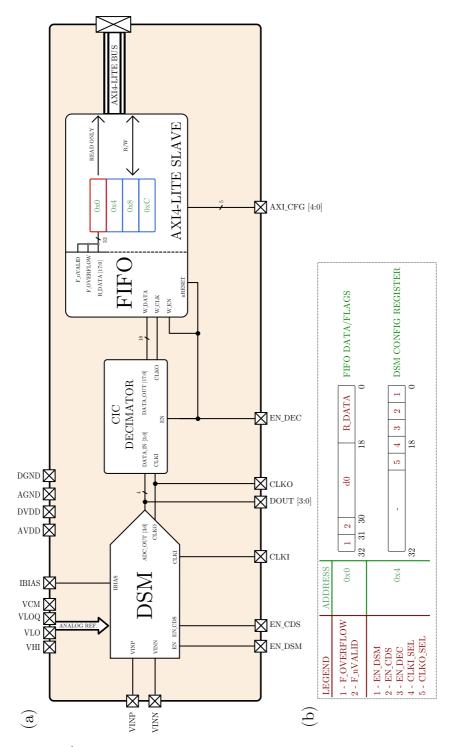

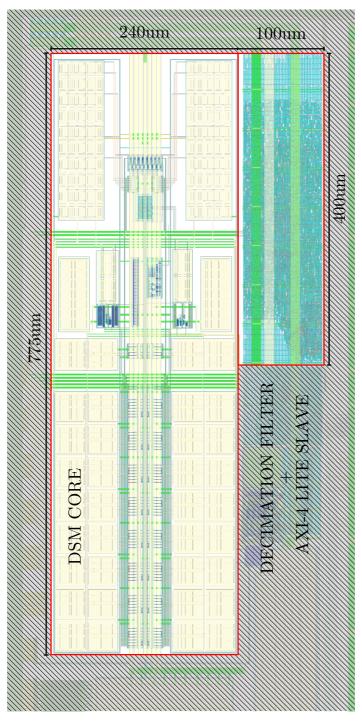

La implementació CMOS de 65 nm del  $\Delta\Sigma$ M incorpora el suport digital compost pel filtre delmador i un perifèric per a comunicacions per bus, i s'ha integrat com un bloc IP per un nucli digital RISC-V. Aquest disseny s'està fabricant en l'actualitat.

Una altra contribució d'aquest treball és el desenvolupament d'una nova arquitectura de  $\Delta\Sigma$ M que incorpora funcions de control de guany automàtic (AGC) fent ús de la tècnica analog floating-point. Un ADC  $\Delta\Sigma$  de tipus Floating Point amb AGC lliure de distorsió i 1.1mW 50kHz 100dB-DR també s'ha fabricat en un node CMOS de 180 nm i s'ha testat experimentalment. Els resultats obtinguts mostren el correcte ús del mecanisme floating-

point, obtenint així una extensió en el rang dinàmic de l'ADC. També s'ha desenvolupat un sistema de test específic per tal de tancar el llaç de control AGC mitjançant processat digital sintetitzat en una plataforma FPGA.

## Resumen

El principal objetivo de esta tesis doctoral es el diseño de ADCs de bajo consumo y alta resolución del tipo  $\Delta\Sigma$  para aplicaciones de espacio, aunque las contribuciones son válidas para cualquier escenario de sensado de propósito general donde se requiera un gran rango dinámico. La estrategia  $\Delta\Sigma$  ha sido escogida como punto de partida debido a su alto rendimiento y fiabilidad. En particular, las implementaciones con capacidades conmutadas (SC) son de especial interés en el trabajo presentado, las cuales se construyen mediante el uso de novedosos circuitos CMOS.

Con la intención de definir el proceso de optimización y facilitar al diseñador la realización de tareas tanto como sea posible, se ha desarrollado una metodología de diseño basada en modelos matemáticos. Además, se ha combinado esta metodología con técnicas de diseño especiales para incrementar la robustez de los circuitos CMOS frente a la radiación.

Una limitación importante en diseños de ADCs de baja frecuencia y alta resolución es el ruido flicker. Para prevenir la degradación de la resolución causada por este efecto, se propone un mecanismo de cancelación de ruido flicker mediante circuitos conmutados. Esta modificación del modulador  $\Delta\Sigma$  ( $\Delta\Sigma$ M), junto a otras nuevas técnicas y circuitos, permiten obtener una buena optimización del consumo del ADC y mantener sus prestaciones.

La arquitectura  $\Delta\Sigma$ M Multi-bit propuesta se ha implementado en los tres nodos de tecnología CMOS 180 nm, 65 nm y 22 nm. El propósito de este estudio de portabilidad es descubrir los retos de diseño que supone la migración tecnológica, permitiendo así validar la metodología de diseño y explorar los beneficios potenciales del escalado tanto tecnológico como de la tensión de alimentación.

Un  $\Delta\Sigma$ M SC de 0.8mW 50kHz 94.6dB-SNDR libre de bootstrapping y con cancelacion de ruido flicker ha sido fabricado en una tecnología CMOS de 180 nm y caracterizado experimentalmente. Las medidas muestran una mejoría en el estado del arte de la FoM en comparación con otros convertidores de características similares publicados en la literatura. Los resultados también muestran una baja variabilidad entre diferentes muestras, demostrando la robustez del diseño frente a tecnología. Además, la robustez de estos chips frente a radiación ha sido comprobada mediante un test de dosis total de radiación. Los resultados muestran que el ADC  $\Delta\Sigma$ M puede soportar como mínimo niveles de radiación adecuados para la mayoría de misiones espaciales.

La implementación CMOS de 65 nm del  $\Delta\Sigma$ M incopora el soporte digital, compuesto por el filtro diezmador y un periférico para comunicaciones por bus, y ha sido integrado como un bloque IP para un núcleo digital RISC-V. Este diseño se está fabricando actualmente.

Otra contribución de este trabajo es el desarrollo de una nueva arquitectura  $\Delta\Sigma M$  que incorpora funciones de control automático de ganancia (AGC) basada en el concepto analog floating-point. Un ADC  $\Delta\Sigma$  de tipo Floating Point con AGC libre de distorsión y 1.1mW 50kHz 100dB-DR también se ha fabricado en un nodo CMOS de 180 nm y testeado experimentalmente. Los resultados obtenidos muestran un correcto uso del mecanismo floating-point, obteniendo así una extensión en el rango dinámico del ADC. También se

ha desarrollado un sistema de test específico con el fin de cerrar el lazo de control AGC mediante procesado digital sintetizado en una plataforma FPGA.

## Abstract

The focus of this PhD thesis is placed in the design of low-power high-resolution  $\Delta\Sigma$ ADCs intended for space applications, but contributions are valid for any general-purpose sensing scenarios where a wide dynamic range is required. The  $\Delta\Sigma$  strategy is chosen because of its high performance and reliability. In particular, switched-capacitor implementations are of interest in this work, which are realized by making use of novel CMOS circuits.

In order to define the optimization process and facilitate the designer's tasks as much as possible, a mathematical framework and methodology is developed. In addition, special design techniques are also combined with this methodology with the intention of increasing the robustness of the CMOS circuits against radiation.

One important limiting factor in low-frequency high-resolution ADCs is flicker-noise. In order to prevent resolution loss caused by this effect, a switched-capacitor flicker-noise cancellation mechanism is proposed. This modification of the  $\Delta\Sigma$ modulator ( $\Delta\Sigma$ M), in conjunction with other novel circuits, allows for a good power optimization of the ADC while keeping its high performance.

The proposed Multi-Bit  $\Delta\Sigma$ M architecture is implemented in the three CMOS technology nodes 180 nm, 65 nm, and 22 nm. The aim of this portability study is to show the design challenges of technology migration, to check the validity of the design methodology, and to explore the potential benefits of both the technology and supply voltage downscaling.

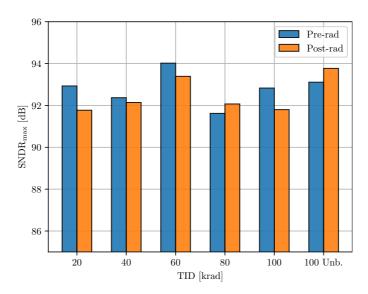

A 0.8mW 50kHz 94.6dB-SNDR bootstrapping-free SC  $\Delta\Sigma$ M ADC with flicker-noise cancellation is fabricated in standard 180 nm CMOS technology and experimentally characterized. The measurements show an improvement of the state-of-the-art FoM compared to other published SC  $\Delta\Sigma$ M realizations. These results also present very low variability between samples, demonstrating the robustness of the design technique versus technology. Furthermore, the robustness against radiation has been also measured via total irradiation dose tests. The results show that the  $\Delta\Sigma$ M ADC can withstand an irradiation dose level rated for most space missions.

The 65 nm CMOS  $\Delta\Sigma$ M design incorporates a digital backend, including the decimation filter and the bus peripheral, and it is integrated as an IP block for a digital RISC-V core. This design is currently under manufacturing.

Another contribution of this work is the development of a new  $\Delta\Sigma M$  architecture incorporating automatic gain control (AGC) capabilities based on the analog floating-point concept. A 1.1mW 50kHz 100dB-DR Floating-Point  $\Delta\Sigma M$  ADC with distortion-less AGC has also been fabricated in standard 180 nm CMOS technology and experimentally tested. The measurement results demonstrate the correct operation of the Floating-Point mechanism, achieving the desired dynamic-range extension. A specific test system is also developed in order to close the AGC loop through digital processing synthesized in a FPGA platform.

## Acknowledgements

I would like to acknowledge my colleges at the Integrated Circuits and systems (ICAS) group for the support I have received while developing all the work presented here and for all the knowledge they have shared with me, which has helped me in becoming a better engineer.

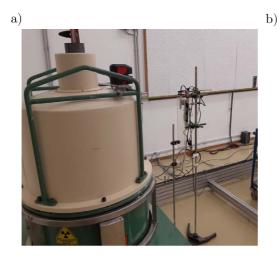

I would also like to thank the European Space Agency (ESA) and the European Space Research and Technology Centre (ESTEC) for the sponsoring this project, including the Co-60 facility team for their help building the irradiation setup and carrying out the irradiation process.

I want to thank my friends for all the good times they have given me; some needed respites during all these years.

Finally, I want to thank my family for always being there, no matter when or where, and expecting nothing in return.

# Contents

| 1        | Intr            | oducti                     | ion                             | 1  |

|----------|-----------------|----------------------------|---------------------------------|----|

|          | 1.1             | Motiv                      | ation                           | 1  |

|          | 1.2             | State-                     | of-Art of High-Resolution ADC   | 2  |

|          |                 | 1.2.1                      | Basic ADC Concepts and Metrics  | 3  |

|          |                 | 1.2.2                      | State-of-Art ADCs               | 9  |

|          | 1.3             | Objec                      | tives and Scope                 | 11 |

| <b>2</b> | $\Delta \Sigma$ | Modu                       | ılation Principles and Modeling | 13 |

|          | 2.1             | $\Delta \Sigma \mathrm{M}$ | Architectures                   | 13 |

|          |                 | 2.1.1                      | First Order $\Delta\Sigma M$    | 13 |

|          |                 | 2.1.2                      | L-Order CIFB $\Delta\Sigma$ M   | 15 |

|          |                 | 2.1.3                      | Feedforward $\Delta\Sigma M$    | 15 |

|          |                 | 2.1.4                      | MASH $\Delta\Sigma$ M           | 16 |

|          |                 | 2.1.5                      | Incremental DSM                 | 18 |

|          |                 | 2.1.6                      | Zoom $\Delta\Sigma$ Ms          | 18 |

|          |                 | 2.1.7                      | Multi-Bit Quantization          | 19 |

|          | 2.2             | SC ve                      | CT Architecture Implementations | 20 |

|   | 2.3             | Model   | ling of SC $\Delta\Sigma$ M                                      | 21 |

|---|-----------------|---------|------------------------------------------------------------------|----|

|   |                 | 2.3.1   | Basic SC Integrator Topology                                     | 22 |

|   |                 | 2.3.2   | Sampling Stage Analysis                                          | 25 |

|   |                 | 2.3.3   | Integration Stage Analysis                                       | 27 |

|   |                 | 2.3.4   | OpAmp Non-Idealities                                             | 30 |

|   |                 | 2.3.5   | Switch Non-Idealities                                            | 32 |

|   |                 | 2.3.6   | Design Equations                                                 | 34 |

| 3 | Mu              | lti-Bit | $\Delta\Sigma { m M}$ with Flicker-Noise Cancellation            | 37 |

|   | 3.1             | Low-F   | Power SC $\Delta\Sigma$ M Architecture                           | 38 |

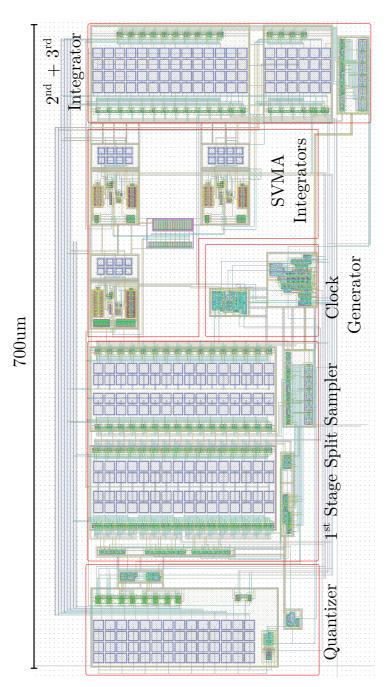

|   | 3.2             | Circui  | t Topology                                                       | 44 |

|   | 3.3             | Built-  | In Flicker Noise Cancellation                                    | 48 |

|   | 3.4             | Low-F   | Power CMOS Circuits                                              | 54 |

|   |                 | 3.4.1   | Clock Generation                                                 | 54 |

|   |                 | 3.4.2   | Class-AB SVMA                                                    | 55 |

|   |                 | 3.4.3   | SC Multi-Bit Quantizer                                           | 58 |

|   | 3.5             | Design  | n Methodology                                                    | 64 |

|   |                 | 3.5.1   | Mitigation Techniques for Radiation Effects                      | 68 |

| 4 | Floa            | ating-I | Point $\Delta\Sigma \mathrm{M}$ with Distortion-Less AGC         | 71 |

|   | 4.1             | Sensir  | ng Scenario                                                      | 71 |

|   | 4.2             | Floati  | ng-Point Architecture                                            | 74 |

|   | 4.3             | SC Ci   | rcuit Implementation                                             | 76 |

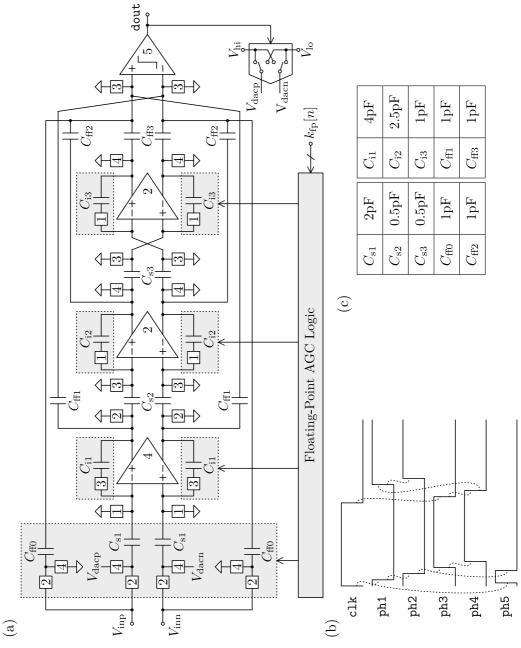

|   |                 | 4.3.1   | Input Scaler and Feedback Updater                                | 79 |

|   |                 | 4.3.2   | Memory Updater                                                   | 83 |

| 5 | $\Delta \Sigma$ | M Re    | alizations in CMOS Technology                                    | 87 |

|   | 5.1             | Multi-  | -bit $\Delta\Sigma$ M CMOS Scalability in 180 nm, 65 nm, & 22 nm | 87 |

|   | 5.2             | IP Fo   | cused Design                                                     | 94 |

|   |       | 5.2.1 Decimation Filter                                            | 94  |

|---|-------|--------------------------------------------------------------------|-----|

|   |       | 5.2.2 AXI-4 Lite Interface                                         | 96  |

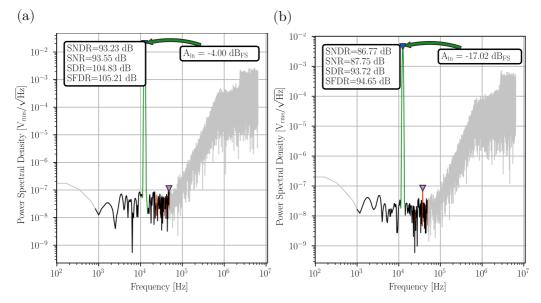

|   | 5.3   | Floating-Point $\Delta\Sigma M$ with Distortion-Less AGC in 180 nm | 97  |

| 6 | Exp   | perimental Results 1                                               | .03 |

|   | 6.1   | Measurement Setup                                                  | .03 |

|   | 6.2   | Multi-bit $\Delta\Sigma$ M Measurement Results                     | .09 |

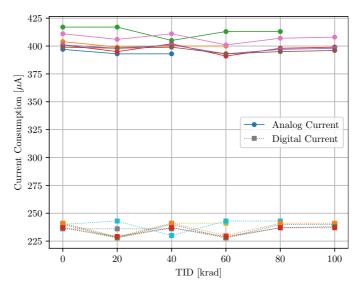

|   |       | 6.2.1 Radiation-Hardness Test Results                              | 13  |

|   | 6.3   | Floating-Point $\Delta\Sigma$ M Measurement Results                | .16 |

| 7 | Cor   | nclusions 1                                                        | 21  |

|   | 7.1   | Contributions                                                      | .21 |

|   | 7.2   | Future Work                                                        | .22 |

| R | efere | ences 1                                                            | 25  |

# List of Figures

| 1.1 | Amplitude transfer function of an ideal uniform quantizer for a 9-level case.                                                                                                                                                 | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Example of an ADC PSD function (a) and a typical SNDR curve (b). Typical ADC parameters are also annotated in the graphs                                                                                                      | 4  |

| 1.3 | Example of oversampling on a harmonic signal with added white noise. The same signal is sampled at Nyquist rate $(OSR=1)$ in blue and oversampled $(OSR=4)$ in green. Red shadowed area is outside the bandwidth of interest. | 7  |

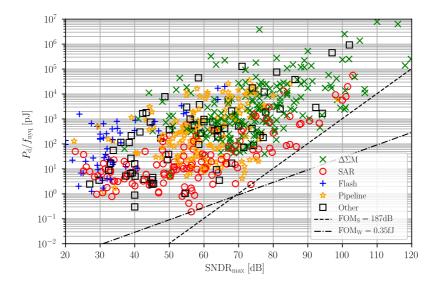

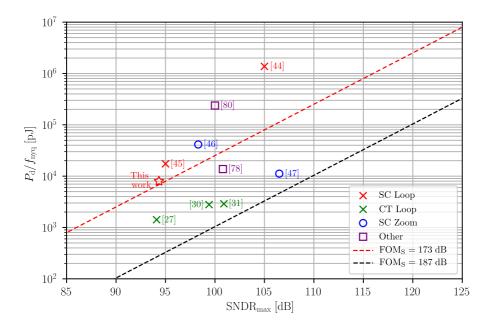

| 1.4 | State-of-art ADC chart. Current FoM limits are shown in dashed lines                                                                                                                                                          | 9  |

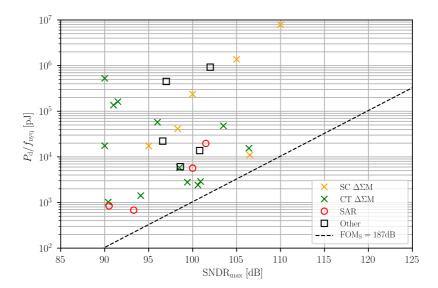

| 1.5 | State-of-art ADC chart showing only high-resolution ADCs (SNDR $\geq$ 90 dB) with general purpose bandwidth (BW $\geq$ 20kHz)                                                                                                 | 10 |

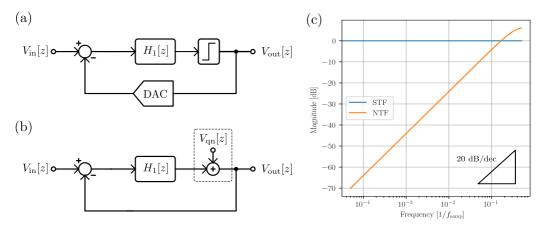

| 2.1 | General case, first-order $\Delta\Sigma M$ architecture (a), linear model (b) and plot of the magnitude of its characteristic transfer functions (c)                                                                          | 14 |

| 2.2 | General CIFB $\Delta\Sigma$ M architecture                                                                                                                                                                                    | 15 |

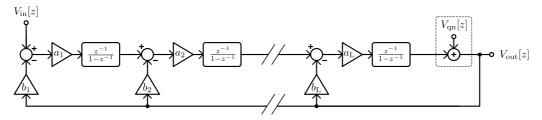

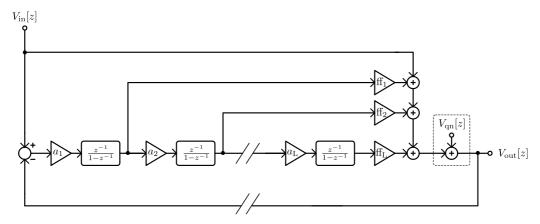

| 2.3 | General feedforward $\Delta\Sigma M$ architecture                                                                                                                                                                             | 16 |

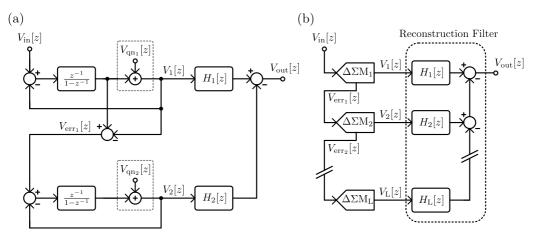

| 2.4 | Two-stage MASH $\Delta\Sigma$ M (a) and general M-stage MASH $\Delta\Sigma$ M architecture (b)                                                                                                                                | 17 |

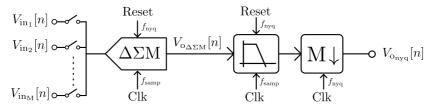

| 2.5 | General architecture of incremental $\Delta\Sigma$ Ms with input multiplexation. ADC memories are reset at Nyquist rate                                                                                                       | 18 |

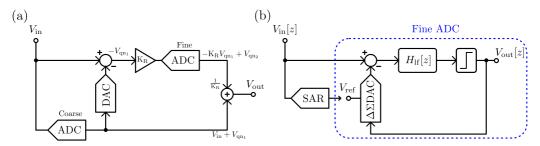

| 2.6  | Classic two-step ADC architecture (a) and zoom $\Delta\Sigma M$ architecture (b), where coarse SAR ADC is used to tune the DAC reference voltage of the fine $\Delta\Sigma M$                                                                                                                                                                         | 19 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

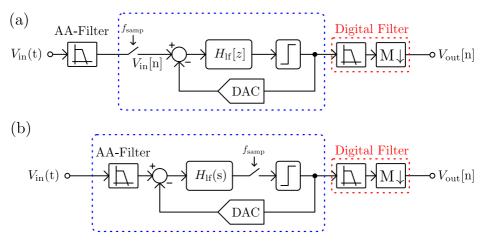

| 2.7  | SC (a) and CT (b) $\Delta\Sigma$ M tipical architectural implementations. The ADC is delimited by the blue line and the digital filter by the red line                                                                                                                                                                                                | 20 |

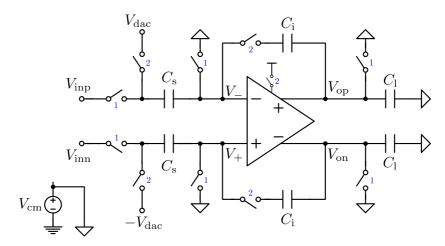

| 2.8  | Fully-differential SC integrator topology. Blue numbers indicate the phase when the switch is closed                                                                                                                                                                                                                                                  | 23 |

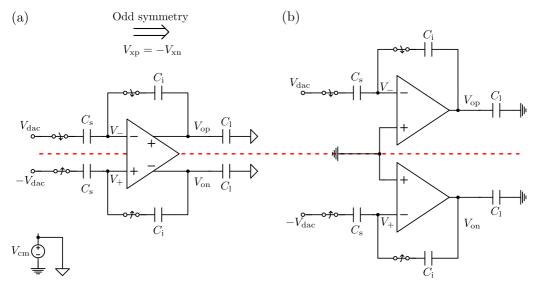

| 2.9  | SC integrator during integration stage (open switches omitted) (a), and equivalent odd-symmetry circuit (b)                                                                                                                                                                                                                                           | 24 |

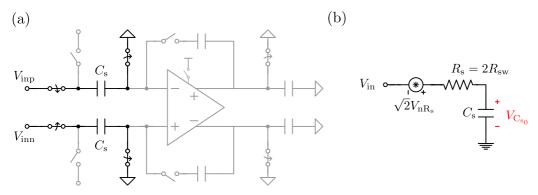

| 2.10 | SC integrator during sampling stage (a), and simplified differential signal model (b)                                                                                                                                                                                                                                                                 | 24 |

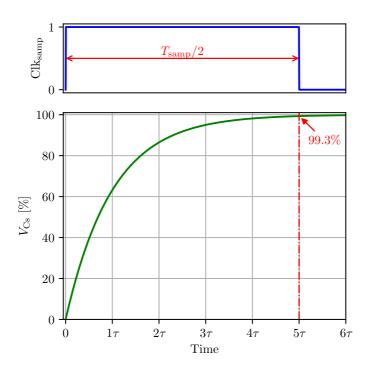

| 2.11 | Typical SC input sampler transient response                                                                                                                                                                                                                                                                                                           | 26 |

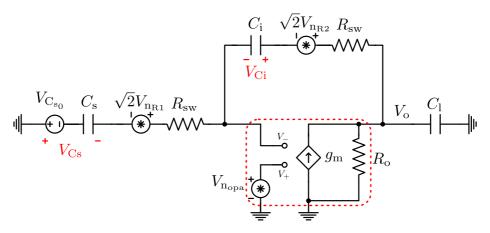

| 2.12 | SC integrator linear model with noise sources                                                                                                                                                                                                                                                                                                         | 27 |

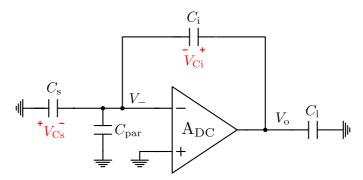

| 2.13 | SC integrator model with finite-gain OpAmp and input parasitic capacitance.                                                                                                                                                                                                                                                                           | 30 |

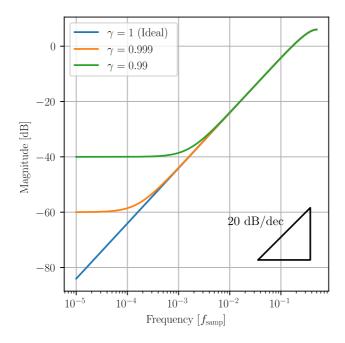

| 2.14 | NTF of a first-order $\Delta\Sigma M$ with a leaky integrator showing the behavior for different $\gamma$ values                                                                                                                                                                                                                                      | 31 |

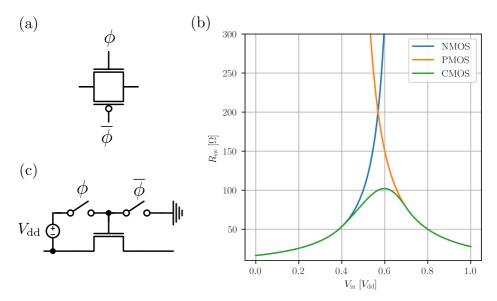

| 2.15 | CMOS switch (a), characteristic CMOS non-linear resistance (b) and bootstrapped switch principle (c)                                                                                                                                                                                                                                                  | 33 |

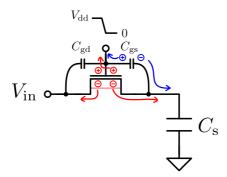

| 2.16 | Charge injection (red) and clock feedthrough (blue) effects in a SC circuit caused by MOS switches.                                                                                                                                                                                                                                                   | 34 |

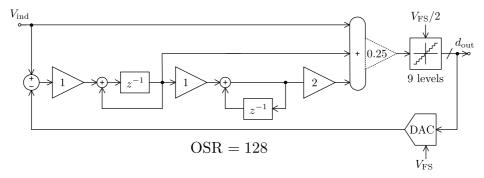

| 3.1  | High-level architecture of the proposed second order feedforward Multi-Bit $\Delta\Sigma M.$                                                                                                                                                                                                                                                          | 37 |

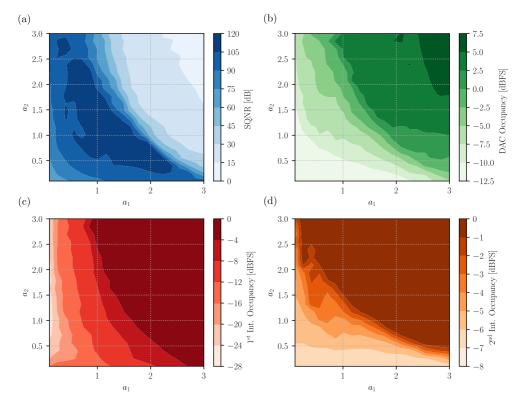

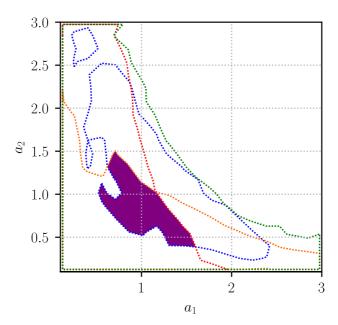

| 3.2  | Example of a 2-D coefficient sweep while evaluating different architectural parameters: SQNR (a), and DAC (b), first integrator (c), and second integrator (d) occupancies respect to the full-scale. In this example, the integrator gain factors are swept while the rest of the parameters are kept to the optimal value found in the global sweep | 39 |

| 3.3  | Optimal coefficient region (in purple) from the simulations at Fig. 3.2 complying with the contraints: SQNR $> 105$ dB, DAC level $< 0$ dBFS, first integrator level $< -8$ dBFS and second integrator level $< -5$ dBFS.                                                                                                                             | 40 |

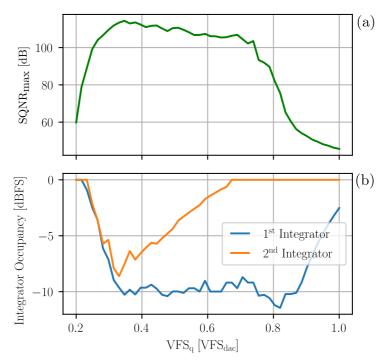

| 3.4  | SQNR (a) and integrator signal level (b) of the Multi-Bit $\Delta\Sigma$ M architecture of Fig. 3.1 as a function of the quantizer full-scale level                                                                                                                                                                                                   | 42 |

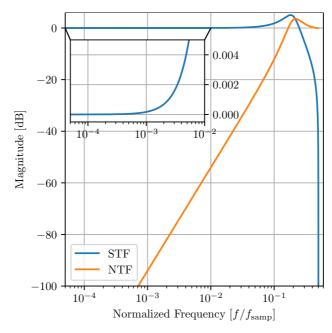

| 3.5  | Characteristic transfer functions of the Multi-Bit $\Delta\Sigma M$ architecture of Fig. 3.1. The zoomed inset shows the STF magnitude at the frequencies of interest                                                                                                                                                                                 | 43 |

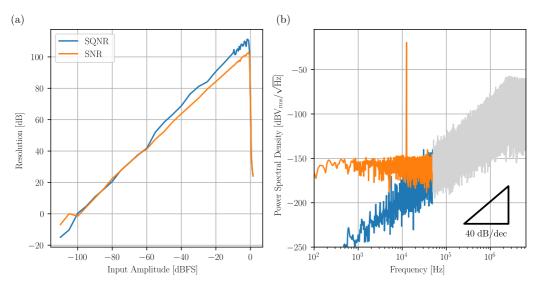

| 3.6  | Simulated Multi-Bit $\Delta\Sigma$ M resolution (a) and PSD at the optimal amplitude point at -1 dBFS (b) with and without kTC noise contribution                                                                                                                          | 44 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

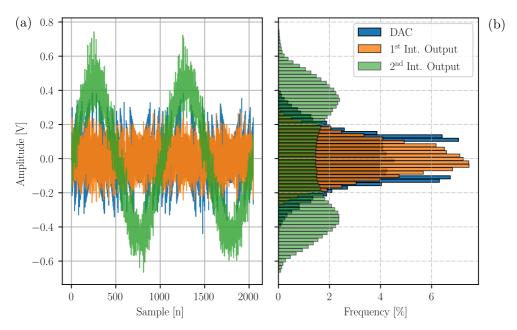

| 3.7  | State-variable dynamics (a) and probability distribution (b) from the Multi-Bit $\Delta\Sigma$ M architecture of Fig. 3.1                                                                                                                                                  | 45 |

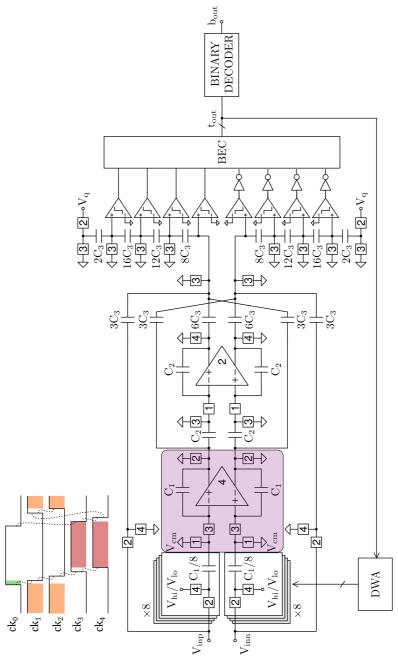

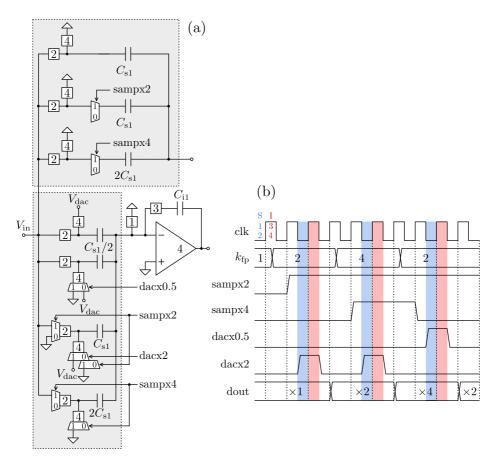

| 3.8  | Circuital implementation of the Multi-Bit second-order $\Delta\Sigma M$ of Fig. 3.1. Numbered boxes represent CMOS switches and their master clock phase. The purple shadowed area will be replaced by the flicker noise cancellation modification proposed in Section 3.3 | 46 |

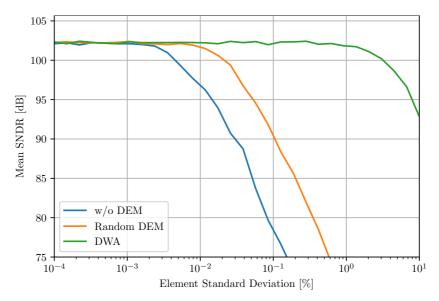

| 3.9  | Effect of DAC mismatch in the overall $\Delta\Sigma M$ SNDR for different DEM implementations                                                                                                                                                                              | 48 |

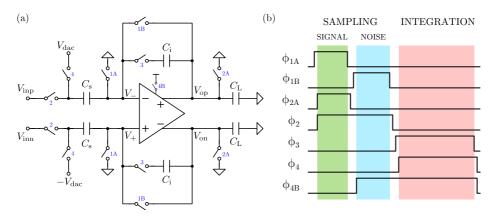

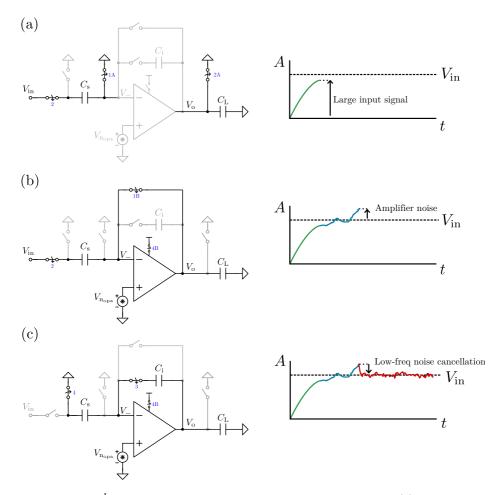

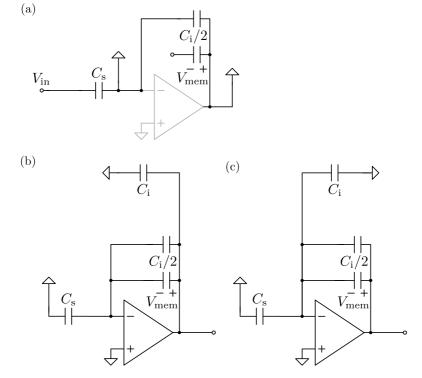

| 3.10 | Fully differential integrator circuit incorporating CDS-based flicker-noise cancellation (a) and control chronogram (b)                                                                                                                                                    | 49 |

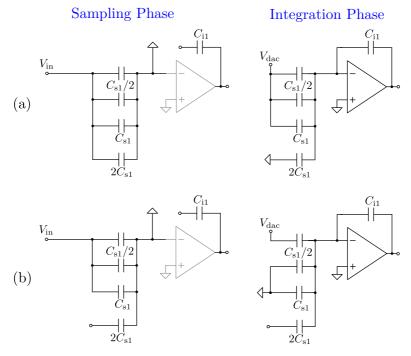

| 3.11 | Flicker-noise cancellation operation: signal sampling (a), noise sampling (b) and integration with noise cancellation (c). $\dots$                                                                                                                                         | 50 |

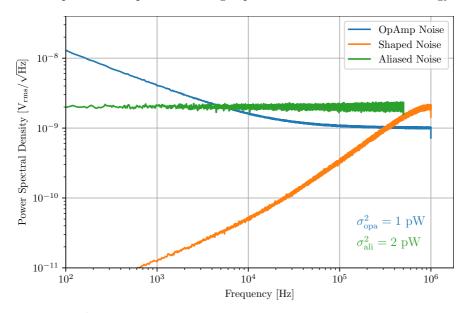

| 3.12 | High-level simulation showing the frequency transformations of the amplifier noise due to the CDS operation. The amplifier power level here is used as an example and does not relate to actual measurements                                                               | 52 |

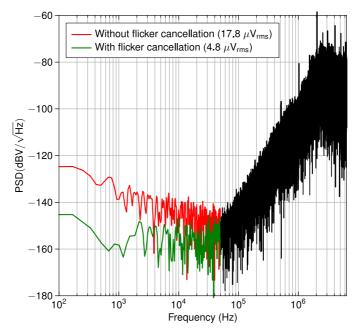

| 3.13 | Electrical noise floor simulation of a specific $\Delta\Sigma M$ implementation from Fig. 3.8 with and without the proposed flicker-noise cancellation mechanism.                                                                                                          | 53 |

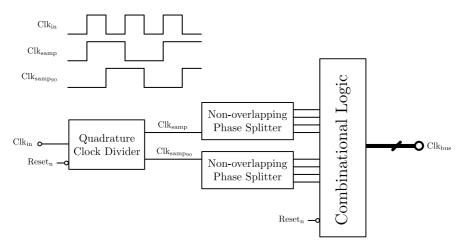

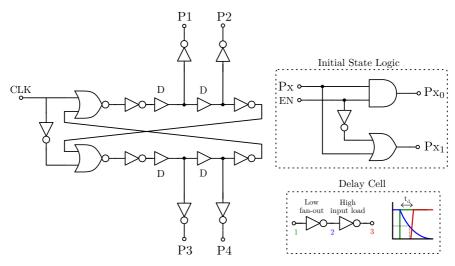

| 3.14 | General schematic of the clock generator module                                                                                                                                                                                                                            | 54 |

| 3.15 | Example of a 4-phase non-overlapping phase splitter                                                                                                                                                                                                                        | 55 |

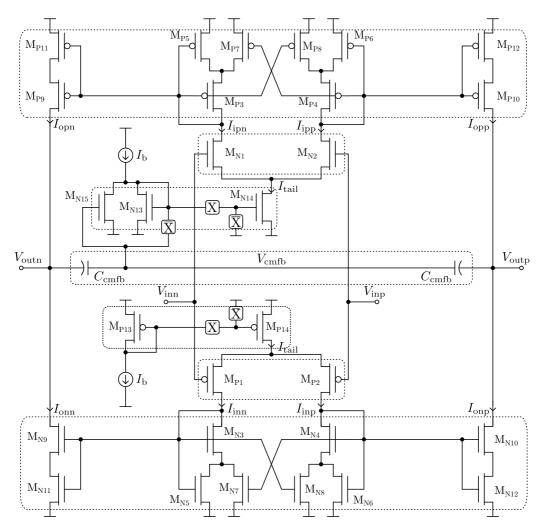

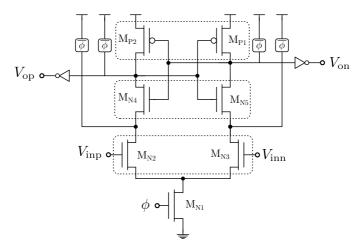

| 3.16 | Type-II SVMA circuit topology used in the OpAmps from Fig. 3.8. Dashed boxes indicate element matching groups                                                                                                                                                              | 56 |

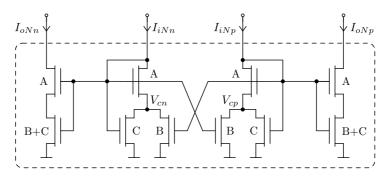

| 3.17 | Type-II variable current mirror from the SVMA in Fig. 3.16                                                                                                                                                                                                                 | 57 |

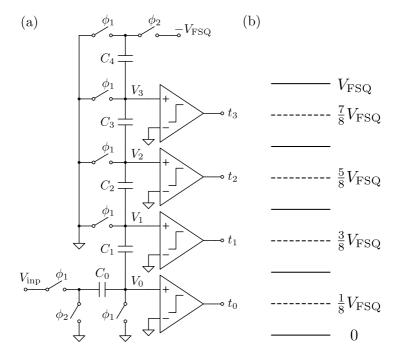

| 3.18 | Single-ended schematic of the SC multi-bit quantizer used in the design of the $\Delta\Sigma M$ in Fig. 3.8a and equivalent quantization levels set by the capacitor ratios (b)                                                                                            | 59 |

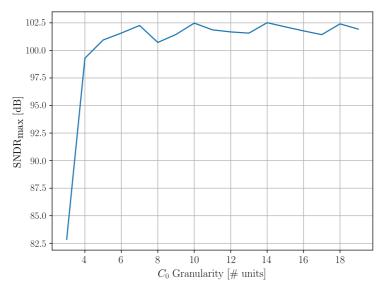

| 3.19 | High-level simulation showing the maximum SNDR versus $C_0$ granularity for the $\Delta\Sigma$ M in Fig. 3.1                                                                                                                                                               | 61 |

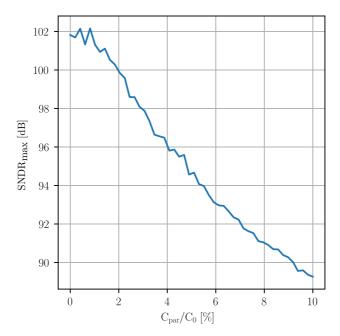

| 3.20 | High-level simulation showing the effects of quantizer parasitic capacitance on the resolution of the $\Delta\Sigma M$ in Fig. 3.8                                                                                                                                         | 62 |

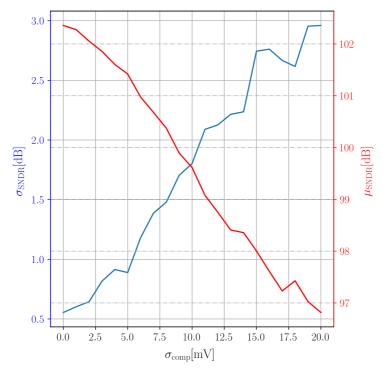

| 3.21 | High-level simulation of the effects of comparator offset in the $\Delta\Sigma M$ from Fig. 3.1. The red and blue axes describe the mean resolution and standard deviation, respectively, given a certain standard deviation for the comparator input offset               | 63 |

| 3.22 | NMOS-input StrongARM comparator circuit topology                                                                                                                                                                                                                           | 63 |

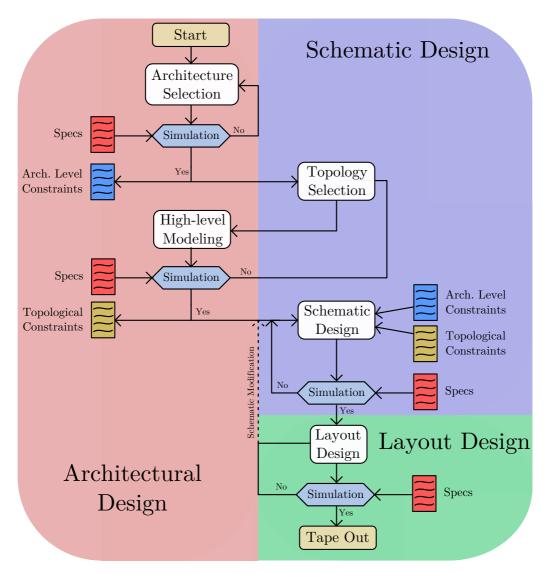

| 3.23 | General top-down design methodology for full-custom analog and mixed-signal ICs                                                                                                                                                               | 65 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.24 | Schematic design methodology for the analog core of the multi-bit SC $\Delta\Sigma$ M proposed in this chapter                                                                                                                                | 67 |

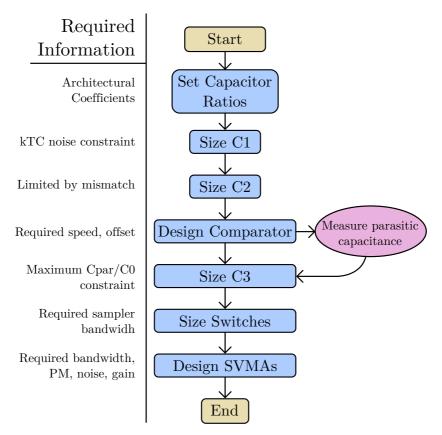

| 3.25 | SVMA design algorithm for power optimization (a) and example of the optimization process (b)                                                                                                                                                  | 68 |

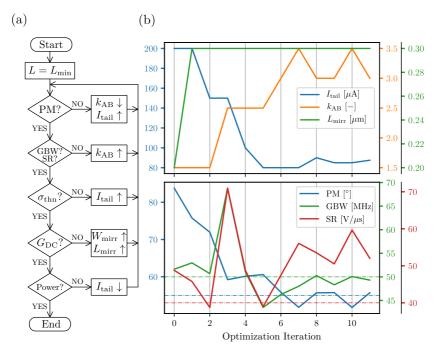

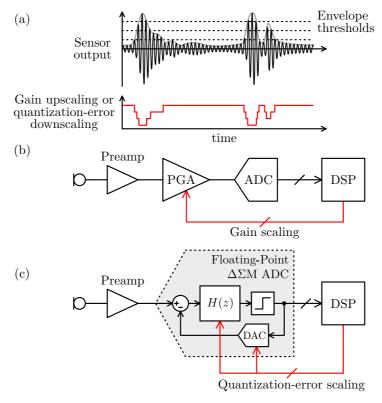

| 4.1  | Example of a high DR signal and the feedback gain calculated by the DSP (a), classic AGC system (b) and proposed $\Delta\Sigma M$ with built-in AGC (c).                                                                                      | 72 |

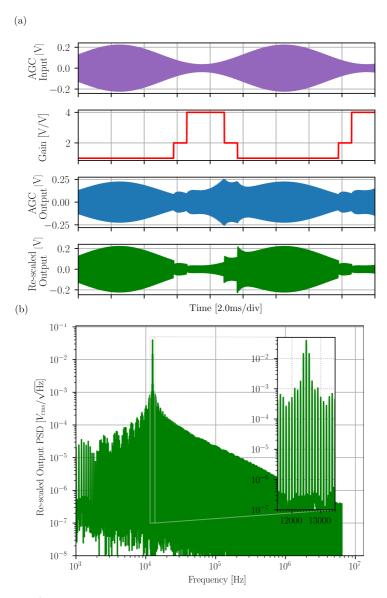

| 4.2  | Simulation example of the classical AGC system of Fig. 4.1b when applied to an AM signal. Time-domain signals (a) and PSD of the reconstructed signal (b)                                                                                     | 73 |

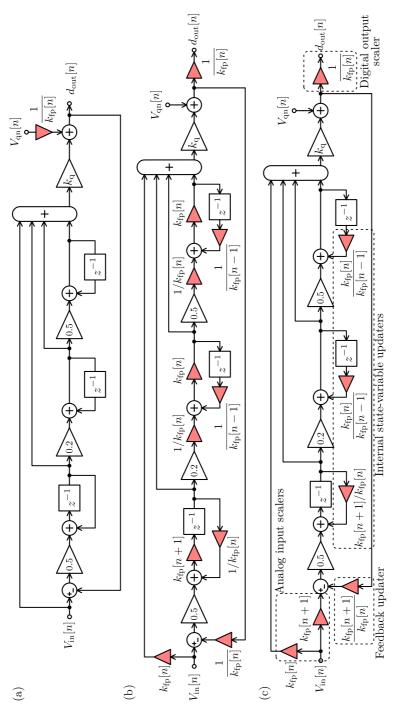

| 4.3  | Linear model of a single-bit third-order $\Delta\Sigma M$ architecture with scalable quantization (a), correction propagation (b) and proposed realization (c).                                                                               | 75 |

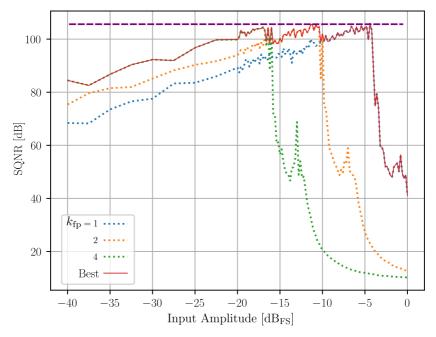

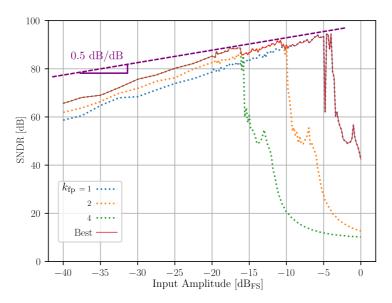

| 4.4  | Simulated SQNR from the architecture in Fig. 4.3 for each $k_{\rm fp}$ scaling factor. The continuous red line shows the best resolution achievable at each input amplitude point with an optimal AGC control                                 | 77 |

| 4.5  | Simplified schematic of the single-bit third-order SC Floating-Point $\Delta\Sigma M$ circuit (a), phase switching scheme (b) and capacitors sizing (c)                                                                                       | 78 |

| 4.6  | Single-ended circuit (a) and operation (b) of the Floating-Point $\Delta\Sigma M$ input scaler and feedback updater. Blue and red shadowed regions show the instants of gain transition during sampling and integration stages, respectively. | 80 |

| 4.7  | Simulated SNR from the architecture in Fig. 4.3, now including kTC noise, for each $k_{\rm fp}$ scaling factor. The continuous red line shows the best resolution achievable at each input amplitude point with an optimal AGC control        | 82 |

| 4.8  | First SC integration operation during $2 \to 4$ (a) and $4 \to 2$ (b) input gain transitions                                                                                                                                                  | 82 |

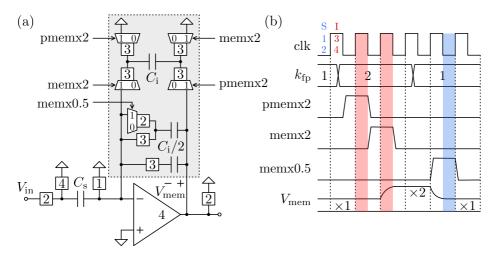

| 4.9  | Single-ended circuit (a) and operation (b) of the Floating-Point $\Delta\Sigma M$ memory updater. Blue and red shadowed regions show the instants of gain transition during sampling and integration stages, respectively                     | 84 |

| 4.10 | SC integrator state during a memory division (a), memory pre-amplification (b) and memory amplification (c)                                                                                                                                   | 84 |

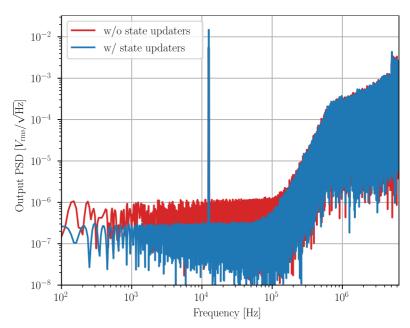

| 4.11 | Simulated PSD showing the AGC transition noise of a re-scaled output signal, with and without the implementation of memory and feedback updater circuits                                                                                      | 85 |

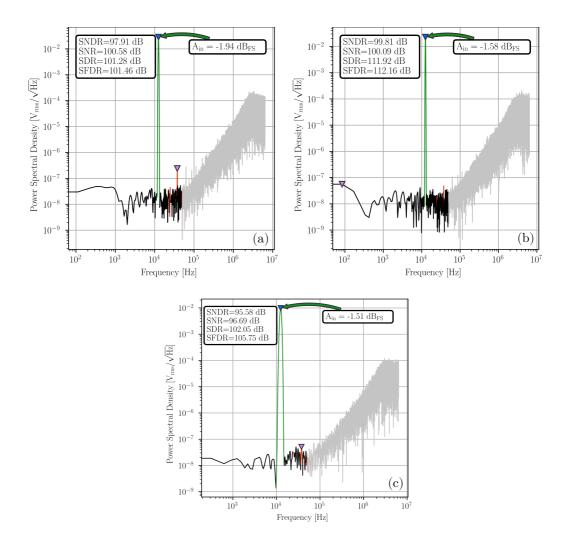

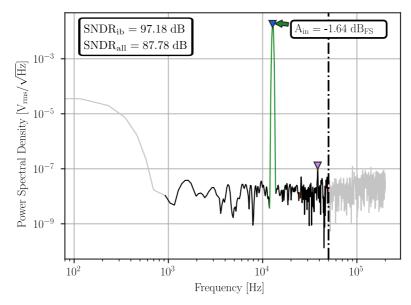

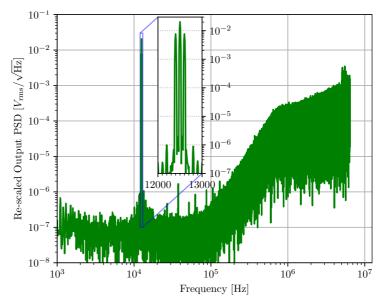

| 5.1  | Fig. 3.8 for 180 nm (a), 65 nm (b), and 22 nm (c) technological nodes, at an input of 12.5 kHz and optimal amplitude for each of the implementations.                                                                                                                                   | 90  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

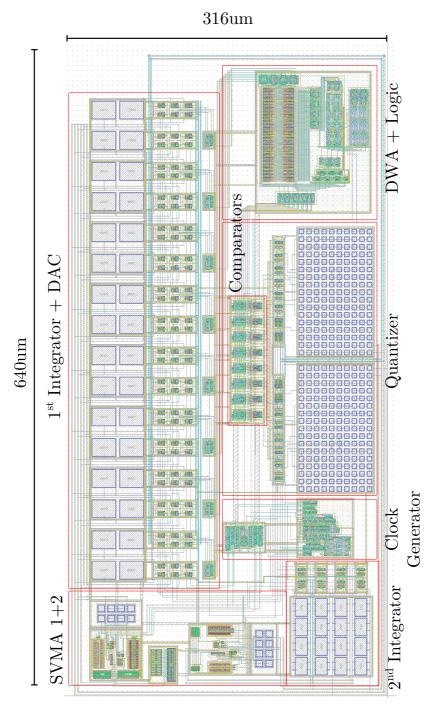

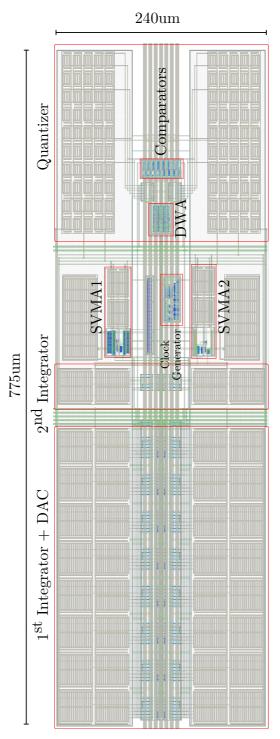

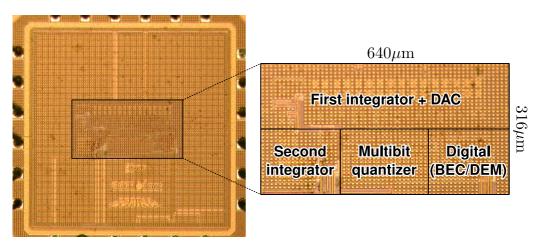

| 5.2  | Layout design of the Multi-bit $\Delta\Sigma M$ in 180 nm CMOS technology. Total design area is 0.202 mm²                                                                                                                                                                               | 91  |

| 5.3  | Layout design of the Multi-bit $\Delta\Sigma M$ in 65 nm CMOS technology. Total design area is $0.186~\rm mm^2$                                                                                                                                                                         | 92  |

| 5.4  | Layout design of the Multi-bit $\Delta\Sigma M$ in 22 nm CMOS technology. Total design area is $0.043~\rm mm^2$                                                                                                                                                                         | 93  |

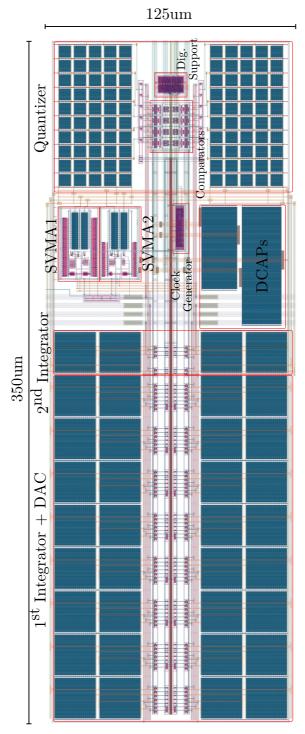

| 5.5  | General structure of the CIC decimation FIR filter                                                                                                                                                                                                                                      | 95  |

| 5.6  | Electrical simulation showing the resolution of the 65 nm $\Delta\Sigma$ M design along with the CIC decimator. Low-frequency windowing effects are not taken into account in the calculations                                                                                          | 96  |

| 5.7  | Top schematic of the $\Delta\Sigma M$ IP design (a) and meaning of the slave register data (b)                                                                                                                                                                                          | 98  |

| 5.8  | Layout design of the Multi-bit $\Delta\Sigma M$ IP, including the decimation filter and the AXI-4 Lite slave peripheral, in 65 nm CMOS technology. Overall IP area is $0.226~\mathrm{mm}^2$                                                                                             | 99  |

| 5.9  | Post-layout simulation results of the Floating-Point $\Delta\Sigma$ M implementation from Fig. 4.5 in 180 nm CMOS technology, showing the PSD and the maximum achievable resolution at $A_{\rm in}=-4$ dBFS with $k_{\rm AGC}=1$ (a) and $A_{\rm in}=-17$ dBFS with $k_{\rm AGC}=4$ (b) | 100 |

| 5.10 | Layout design of the Floating-Point $\Delta\Sigma M$ in 180 nm CMOS technology. Overall area is 0.238 mm²                                                                                                                                                                               | 101 |

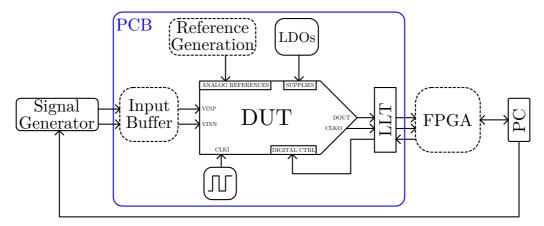

| 6.1  | General scheme of the test setup for the $\Delta\Sigma M$ ADC designs proposed in this PhD thesis                                                                                                                                                                                       | 104 |

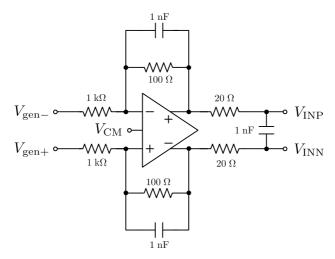

| 6.2  | Fully-differential input buffer schematic from the PCB test setup                                                                                                                                                                                                                       | 105 |

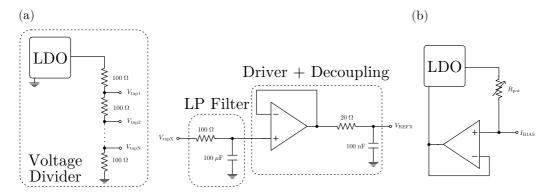

| 6.3  | Voltage reference generator (a) and bias current generator (b) circuits from the PCB test setup.                                                                                                                                                                                        | 105 |

| 6.4  | Main test PCB (a) and individual modules with soldered DUT samples on top (b)                                                                                                                                                                                                           | 107 |

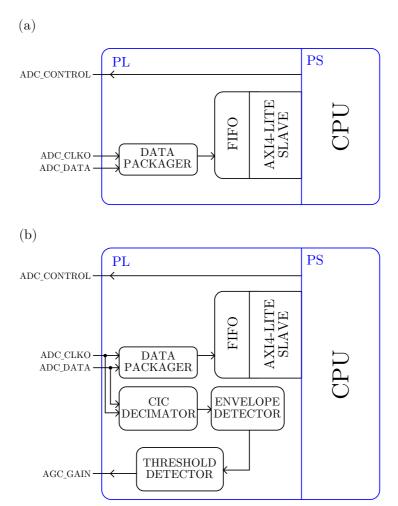

| 6.5  | FPGA design for the Multi-bit $\Delta\Sigma M$ (a) and for the Floating-Point $\Delta\Sigma M$ with distortion-less AGC (b)                                                                                                                                                             | 108 |

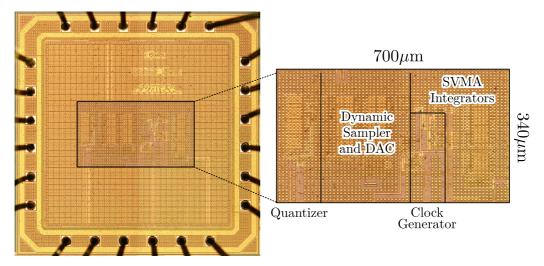

| 6.6  | Multi-bit $\Delta\Sigma \mathrm{M}$ IC fabricated in 180 nm CMOS technology                                                                                                                                                                                                             | 110 |

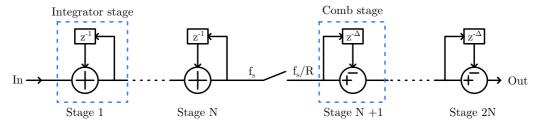

| 6.7  | Measured PSD of the Multi-Bit $\Delta\Sigma$ M from Fig. 6.6                                                                                                                                                                                                                            | 110 |

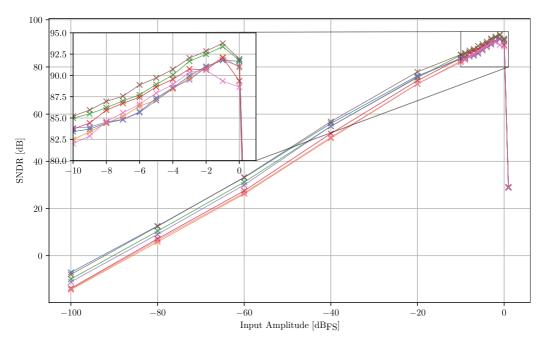

| 6.8  | Measured SNDR curve of the Multi-Bit $\Delta \Sigma M$ from Fig. 6.6 and power distribution                                                                                                                                                                                                                                                                             | 111 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.9  | Maximum SNDR measured from several Multi-bit $\Delta\Sigma M$ IC samples                                                                                                                                                                                                                                                                                                | 111 |

| 6.10 | State-of-art chart showing the Mulyi-Bit $\Delta\Sigma Ms$ from Table 6.1. Absolute general $FoM_S$ in dashed black and absolute SC $FoM_S$ in dashed red                                                                                                                                                                                                               | 113 |

| 6.11 | Test setup positioning in the irradiation room (a) and front view of the setup (b)                                                                                                                                                                                                                                                                                      | 114 |

| 6.12 | Measured current consumption from several Multi-bit $\Delta\Sigma M$ IC samples at the different TID steps                                                                                                                                                                                                                                                              | 115 |

| 6.13 | Measured maximum SNDR from several Multi-bit $\Delta\Sigma$ M IC samples before and after irradiation for different TID                                                                                                                                                                                                                                                 | 115 |

| 6.14 | Measured SNDR curves from several Multi-bit $\Delta\Sigma M$ IC samples after the irradiation process                                                                                                                                                                                                                                                                   | 116 |

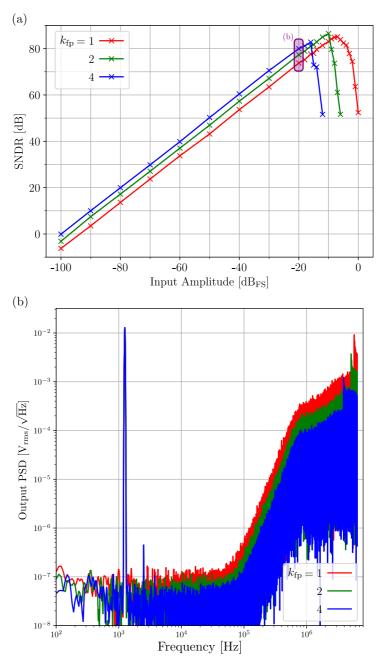

| 6.15 | Floating-Point $\Delta\Sigma {\rm M}$ IC, fabricated in 180 nm CMOS technology                                                                                                                                                                                                                                                                                          | 117 |

| 6.16 | Measured SNDR (a) from the Floating-Point $\Delta\Sigma M$ in Fig. 6.15a and PSD at an input of $-20$ dBFS for each gain factor (b)                                                                                                                                                                                                                                     | 118 |

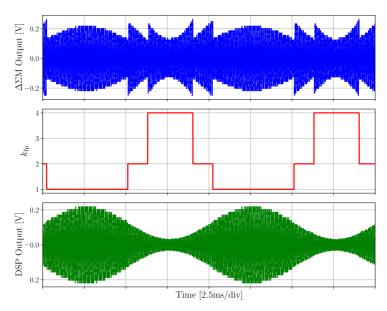

| 6.17 | Measured raw output from the Floating-Point $\Delta\Sigma M$ in Fig. 6.15 (blue), AGC values after closing the control loop (red) and reconstructed output (green) for a 12.5 kHz harmonic input when 75 % modulated in amplitude at 100 Hz. For clarity purposes, the 1-bit raw data is displayed here after being filtered using a 128-point sliding-window averaging | 119 |

| 6.18 | Measured PSD from the raw-data sequence shown in Fig. 6.17                                                                                                                                                                                                                                                                                                              | 119 |

# List of Tables

| 1.1 | Qualitative comparison of the main ADC families                                                                                                                                                          | 11  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Qualitative comparison between SC and CT $\Delta\Sigma$ M architectural implementations                                                                                                                  | 22  |

| 2.2 | SC integrator main design equations                                                                                                                                                                      | 35  |

| 3.1 | Summary of the most important radiation effects in electrical components.                                                                                                                                | 69  |

| 3.2 | Summary of the mitigation actions taken during the full-custom design of the multi-bit SC $\Delta\Sigma$ M in Fig. 3.8                                                                                   | 70  |

| 5.1 | Summary table of the main post-layout simulation results of the Multi-bit $\Delta\Sigma$ M implementation in different technology nodes. †Note: Resolution specifications were different for this design | 88  |

| 5.2 | Post-layout SNDR simulation results of the Multi-bit $\Delta\Sigma$ M implementation for different technology nodes versus process and temperature corners                                               | 89  |

| 5.3 | CIC decimator specifications and design parameters                                                                                                                                                       | 95  |

| 5.4 | Bit width of the registers used in the integration and comb stages of the decimator                                                                                                                      | 96  |

| 5.5 | Summary of the main post-layout specifications for the Floating-Point $\Delta\Sigma M$ implementation from Fig. 4.5 in 180 nm CMOS technology. †Note: This calculation uses DR instead of SNDR           | 100 |

| 6.1 | Comparison of high-resolution (SNDR $_{\rm max} \geq 90 dB$ ) general-purpose (BW $\geq 20 kHz$ ) $\Delta \Sigma Ms$ to the presented Multi-bit SC $\Delta \Sigma M$ realization 112 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2 | TID received by each of the Multi-bit $\Delta\Sigma M$ samples taking part in the irradiation process. †Note: Samples 6 and 7 were unbiased during this process114                   |

| 6.3 | Comparison of different $\Delta\Sigma$ Ms featuring high dynamic-range to the presented Floating-Point $\Delta\Sigma$ M                                                              |

## List of Acronyms

$\Delta\Sigma M$  delta-sigma modulator

ADC analog-to-digital converter

**AFP** Analog Floating Point

AGC automatic gain control

$\mathbf{AM}$  amplitude modulated

AMBA Advanced Microcontroller Bus Architecture

ASIC application specific integrated circuit

**AXI** Advanced eXtensible Interface

**BEC** bubble error correction

CDS correlated double sampling

CIC cascaded integrator-comb

CIFB cascade-of-integrators feed-back

CMFB common-mode feedback

CMOS complementary metal-oxide semiconductor

${f CPU}$  central processing unit

$\mathbf{CT}$  continuous-time

DAC digital-to-analog converter

**DC** direct-current

**DEM** dynamic element matching

**DNL** differential non-linearity

**DR** dynamic range

**DRC** design rule checker

**DSP** digital signal processor

**DT** discrete-time

**DUT** device under test

DWA dynamic weighted averaging algorithm

$\mathbf{EMI}$  electromagnetic interference

**ENOB** effective number of bits

ESA European Space Agency

ESTEC European Space Research and Technology Centre

FIFO first-in, first-out

FIR finite impulse response

FoM figure-of-merit

$\mathbf{FPGA}$  field programmable gate array

FS fullscale

$\mathbf{GBW}$ gain-bandwidth product

**HDL** hardware-description languages

IC integrated circuit

ICT information and communications technology

**IEEE** Institute of Electrical and Electronics Engineers

**INL** integral non-linearity

**IoT** Internet-of-Things

**IP** intelectual property

kTC Jonhson-Nyquist capacitive noise

${f LDO}$  low-dropout regulator

**LLT** logic level translator

LSB least significant bit

LVS layout versus schematic

MASH multi-stage noise-shaping

MBU multiple-bit upset

MCU multiple-cell upset

$\mathbf{MiM}$  metal-insultator-metal

$\mathbf{MoM}$  metal-oxide-metal

MOS metal-oxide semiconductor

MOSFET metal-oxide semiconductor field-effect transistor

NMOS N-channel MOS

NTF noise transfer function

**OpAmp** operational amplifier

**OSR** oversampling-ratio

**OTA** operational transconductance amplifier

PC personal computer

PCB printed circuit board

PGA programmable gain amplifier

PL programmable logic

PMOS P-channel MOS

**PS** processing system

**PSD** power spectral density

PVT process, supply voltage and temperature

RISC reduced instruction set computer

rms root-mean-square

RTL register transfer language

SAR successive approximation register

SC switched-capacitor

**SDR** signal-to-distortion ratio

**SEB** single event burnout

**SEDR** single event dielectric rupture

**SEE** single event effect

**SEFI** single event functional interrupt

**SEGR** single event gate rupture

**SEHE** single event hard error

SEL single event latch-up

**SESB** single event snap-back

**SET** single event transient

**SEU** single event upset

${f SFDR}$  spurious-free dynamic range

${f SNDR}$  signal-to-noise-to-distortion ratio

$\mathbf{SNR}$  signal-to-noise ratio

**SOA** switched-OpAmp

SoC system-on-chip

SQNR signal-to-quantization-noise ratio

SR slew rate

STF signal transfer function

SVMA switched variable-mirror amplifier

TID total ionizing dose

TMR triple modular redundancy

TNID total non-ionizing dose

VLSI very large-scale integration

$\mathbf{VMA}$  variable-mirror amplifier

# Introduction | 1

#### 1.1 Motivation

The current evolution of the information and communications technology (ICT) has led into the convergence of many traditional fields, such as real-time analytics, health monitoring, machine learning, sensory systems, embedded systems, etc..., into complex applications which share data with one another over some kind of network and even the Internet. This is the so called Internet-of-Things (IoT) paradigm, which is currently the focus of the industry and its expanding at a high rate [1]–[3].

This growing market demands sensors with increasingly better performance (e.g. resolution), increased autonomy (i.e. low power consumption), and high-speed capabilities. A key component in any sensory system is the analog-to-digital converter (ADC), since its performance often determines the capabilities of the whole sensory system. In many applications, the ADCs are integrated along with all the analog front-end and digital back-end in the same chip. This is usually known as an application specific integrated circuit (ASIC) [4], [5], and some may even integrate the sensors themselves when possible [6], benefiting from increased compactness and robustness. This is one of the many reasons why developing state-of-the-art ADCs in standard complementary metal-oxide semiconductor (CMOS) technologies is attractive.

The continuous node downscaling in the CMOS technology results in reduced transistor channel length and supply voltage. Despite its inherent benefits, such as lower power consumption and higher speed, it poses increasingly challenging issues in the design of ADCs. This is due to the degradation of the transistor analog performance, increased process mismatch, and reduction of the available voltage range [7].

Currently, the focus research trends and highest state-of-art figures belong to successive approximation register (SAR) ADCs, in the moderate-to-high-resolution range [8]–[18], and continuous-time (CT) delta-sigma modulator ( $\Delta\Sigma$ M) ADCs, in the high-resolution range [19]–[33]. Despite having a lower performance with regard to their CT counterpart, switched-capacitor (SC)  $\Delta\Sigma$ Ms are also attractive because of their high-robustness to technology mismatch and the reduced design complexity [34]–[47]. Many SAR and CT  $\Delta\Sigma$ M designs are also able to achieve such high-performance values because of the

employment of on-line or off-line calibration techniques, at the cost of increased design complexity and manufacturing costs. Since calibration-free circuits are of interest for most remote smart-sensing applications, this is another reason why SC  $\Delta\Sigma$ Ms are an attractive choice.

The general design points of SC  $\Delta\Sigma$ Ms are well understood in the literature [48]. Nonetheless, different designs suffer from peculiar effects that must be carefully considered. For this reason, it is of interest to develop a design methodology in order to ease the design process to the engineer, and even automate some of the design tasks. This methodology should also be valid when migrating the design to different CMOS technology nodes, with special interest on high scalability. Moreover, having a properly described methodology is beneficial regarding the power optimization of the design, allowing for a better performance at a lesser design cost and time.

Another interesting subject is the fact that many sensors used in the industry often generate very weak signals. This is traditionally solved by a signal conditioning stage at the output of the sensor, which amplifies its signal to the appropriate ADC input range. In applications where the sensor signal undergoes large variations of its dynamic range (DR) this is typically handled by automatic gain control (AGC) systems. They make use of a programmable gain amplifier (PGA) at the sensor output controlled by the backend digital signal processor (DSP), which adjusts the PGA gain using feedback, to keep the signal range under control. Classic AGC applications make use of time constants, which adjust the trade-off between AGC sensitivity and response speed [49]. An interesting question arises when considering if this functionality can be incorporated in the ADC architecture itself, and what advantages it can enjoy versus classic AGC implementations.

Placing the focus on space applications, the same can be said about the necessity of ADCs. The space environment, however, is harsh to electronic systems due to the high levels of irradiated particles coming from different sources, the most notable the sun. For this reason, integrated circuits (ICs) intended for space missions require to be properly designed in order to be protected from many radiation effects that would put the application in danger. Incorporating these new design guidelines into the regular IC design flow and carrying out tests to check the effects of radiation on the chips is indeed an interesting topic.

All of the described factors contribute to the motivation of this PhD thesis. The work on the high-resolution ADCs for space missions, in the scope of the project funded by the European Space Agency (ESA)-European Space Research and Technology Centre (ESTEC) under the contract 4000124840/18/NL/MH denominated "Low-power High-resolution Rad-hard ADCs for Space Applications (LOHIRA)", provided the main contributions of this PhD thesis.

#### 1.2 State-of-Art of High-Resolution ADC

In this section, the basic concepts and metrics of ADCs will be explained, in order to provide a basic background and understanding of analog-to-digital conversion. The understanding of these metrics will allow the classification of different ADCs types and architectures

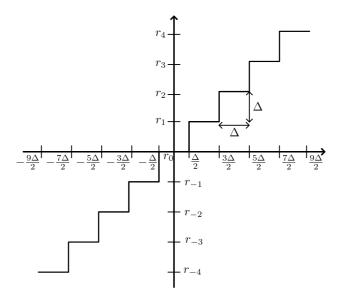

Figure 1.1 Amplitude transfer function of an ideal uniform quantizer for a 9-level case.

based on a single figure-of-merit (FoM). This metric combines several performance and resource parameters into a single number for comparison purposes. Finally, a review of the ADC state-of-art and the most important ADC types is presented to give a good understanding of their strong and weak points and their suited applications.

### 1.2.1 Basic ADC Concepts and Metrics

#### **Quantization Noise and ADC Resolution**

The purpose of an ADC is to digitalize a continuous-time signal in a way so that data can be stored, processed, and communicated using digital systems. To achieve this purpose, the digitalization can be understood as a two-step operation: time-discretization and amplitude-discretization.

The most typical case of amplitude-discretization is uniform quantization [50], in which a set of equally spaced levels are defined. Non-uniform quantizers can also be used and may perform better depending on the application [51]. The transfer function of an ideal uniform quantizer is depicted in Fig. 1.1. The difference in amplitude between these levels is called the quantization step or least significant bit (LSB), and it is given by:

$$\Delta = \frac{\text{FS}}{L - 1} = \frac{\text{FS}}{2^{N} - 1},\tag{1.1}$$

where FS is the quantizer full-scale, or maximum peak-to-peak signal amplitude, L is the number of quantization levels, and N is the number of quantization bits, when the number of levels can be expressed as a power of 2, which is something usual.

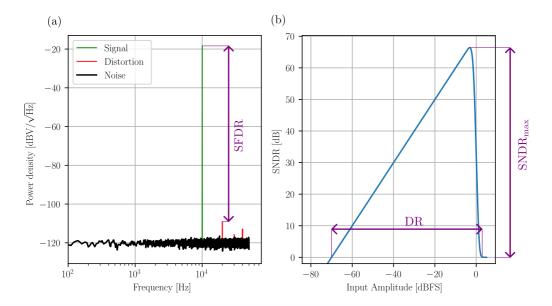

Figure 1.2 Example of an ADC PSD function (a) and a typical SNDR curve (b). Typical ADC parameters are also annotated in the graphs.

In an ideal quantizer, the maximum amplitude error committed by the quantization process is delimited to  $\pm \Delta/2$ . By making a series of assumptions about the input signal that usually hold true for common applications [52], [53], the quantization error, or quantization noise, can be modeled as a white noise process with a total power given by:

$$QN = \frac{\Delta^2}{12}. (1.2)$$

The maximum resolution of an ideal ADC, which basically consists on an ideal sampler and quantizer, is then given by the signal-to-quantization-noise ratio (SQNR), a ratio between the signal power and the quantization noise power. It can be computed using (1.1) and (1.2). The ADC input is assumed to be a pure harmonic signal, so its root-mean-square (rms) value is used to compute the signal power:

$$\begin{split} {\rm SQNR} &= \frac{{\rm FS^2/8}}{{\rm QN}} \approx \frac{3}{2} 2^{2N}, \\ {\rm SQNR} \; [{\rm dB}] &= 6.02 {\rm N} + 1.76 \; [{\rm dB}], \end{split} \label{eq:SQNR} \tag{1.3}$$

where it was assumed  $2^{N} \approx 2^{N} - 1$ , for  $N \gg 1$ . Equation (1.3) states that each additional bit ideally increments the resolution by 6.02 dB.

When considering real ADCs, quantization noise is not the only error source degrading the resolution. Another term, the signal-to-noise ratio (SNR), encompasses all types of noise introduced by the ADC. Since the resolution might be measured at amplitudes other than the ADC full-scale, a more general expression replaces this term by the signal power

at any amplitude, S<sub>in</sub>:

$$SNR = \frac{S_{in}}{QN + \sigma_{p}^{2}},$$

(1.4)

where  $\sigma_n$  is the rms integrated power of all the in-band noise introduced by the ADC, with the exception of quantization noise.

Real ADCs also distort the input due to several non-linear circuital effects. Due to its deterministic nature, distortion is usually considered as a separate term as noise, and thus measured by its own metric, the signal-to-distortion ratio (SDR), defined as:

$$SDR = \frac{S_{in}}{\sigma_d^2},\tag{1.5}$$

where  $\sigma_d$  is the total rms power of the frequency components located at multiples of the input tone, or harmonics.

Another used distortion metric is the spurious-free dynamic range (SFDR), which relates the input signal power to the power of the largest harmonic  $H_{\rm max}$ . This term is defined as:

$$SFDR = \frac{S_{in}}{H_{max}}.$$

(1.6)

A metric taking into account all of the other measurements is the signal-to-noise-to-distortion ratio (SNDR), which includes all kind of error sources affecting the ADC resolution. For this reason, it is the most significant term when describing the effective resolution of an ADC:

$$SNDR = \frac{S_{in}}{QN + \sigma_n^2 + \sigma_d^2}.$$

(1.7)

Another common term is the DR, which describes the range of input power for which the sampled signal is above the error power level:

$$DR = \frac{S_{\text{max}}}{S_{\text{min}}},\tag{1.8}$$

where  $S_{min}$  and  $S_{max}$  are the minimum and maximum input power values for which the SNDR is greater than 0 dB. For an ideal ADC this value is equal to the SQNR, but in real ADCs the DR is usually larger than the SNDR.

Finally, since it is typical to express the resolution as a number of bits, it is possible to obtain a definition similar to (1.3) but using the SNDR instead of the SQNR. This metric is called effective number of bits (ENOB), and it is defined as:

$$ENOB = \frac{SNDR - 1.76}{6.02}.$$

(1.9)

An example of typical ADC measurements is shown in Fig. 1.2. From the power spectral density (PSD) in Fig. 1.2a, the SFDR can be obtained by visual inspection, and the SNR, SDR, and SNDR can be computed by integrating the in-band power of the different elements. The SNDR in Fig. 1.2b is the result of computing the SNDR from the PSD

measurements at different input amplitudes. The maximum SNDR and the DR can be extracted from this graph by visual inspection.

There exist another kind of resolution metrics; static metrics, such as the differential non-linearity (DNL) and integral non-linearity (INL). These metrics aim to describe the resolution of an ADC by looking at deviations in the transfer function from the ideal. However, they cannot be applied to ADCs with memory such as  $\Delta\Sigma$ Ms, since a static transfer function does not exist in this case. Dynamic metrics, such as the ones presented in this section, can be applied to any kind of ADC. Since the focus of this PhD thesis is the  $\Delta\Sigma$ M architecture, static metrics will not be discussed further.

### Oversampling

The Nyquist Theorem states that, in order to be able to recover a signal from its discretetime samples, the sampling frequency must be greater or equal than the Nyquist frequency, which is twice the value of the signal bandwidth [54]:

$$f_{\text{samp}} \ge f_{\text{nyq}} = 2BW.$$

(1.10)

While making  $f_{\text{samp}} = f_{\text{nyq}}$  proves sufficient to avoid aliasing, there are some benefits that can be obtained from using a sampling frequency greater than  $f_{\text{nyq}}$ . This condition is called oversampling, and the oversampling-ratio (OSR) is defined as the ratio between the sampling frequency and the Nyquist frequency:

$$OSR = \frac{f_{samp}}{f_{nvq}}.$$

(1.11)

In (1.2), the quantization noise power was defined to be only dependent on the quantization step value, which in turn depends on the ADC fullscale (FS) and its number of bits/levels. The quantization noise power density, however, is dependent on the sampling frequency because the quantization noise power is equally distributed over all the range of discrete-domain frequencies:

$$QN_{den} = \frac{QN}{f_{samp}/2}.$$

(1.12)

The total in-band noise power can be found by integrating the noise density over the ADC bandwidth. In this case, the noise density is a constant over all the frequency range, so:

$$QN_{ib} = QN_{den} \cdot BW = QN \frac{f_{nyq}}{f_{samp}},$$

$$QN_{ib} = \frac{QN}{OSR}.$$

(1.13)

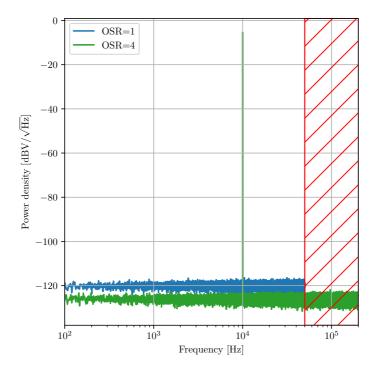

Therefore, the in-band noise power is inversely proportional to the OSR. This is graphically shown in Fig. 1.3, where the same noisy signal is sampled using a different OSR. It can be seen that, for an OSR larger than one, part of the noise power is distributed outside the defined bandwidth, reducing thus the in-band noise. The noise outside the bandwidth can be removed by using adequate digital filtering. This is also true for other noise sources

Figure 1.3 Example of oversampling on a harmonic signal with added white noise. The same signal is sampled at Nyquist rate (OSR=1) in blue and oversampled (OSR=4) in green. Red shadowed area is outside the bandwidth of interest.

that distribute equally over all the spectrum, e.g. Jonhson-Nyquist capacitive (kTC) noise, so they also benefit from oversampling at the cost of increased power consumption.

This mechanism is exploited in depth in some ADC architectures, such as  $\Delta\Sigma$ Ms, which make use of high oversampling ratios in addition to noise shaping transfer functions to reduce the in-band quantization noise even further [55]. Recent SAR ADCs are also incorporating noise shaping techniques to improve resolution, albeit using low OSR values [9], [10], [12], [17], [18]. This kind of ADCs are called "Oversampling ADCs", whereas traditional ones are called "Nyquist-rate ADCs".

### **ADC Figures-of-Merit**

In Section 1.2.1, the most commonly used metrics were defined to help quantify the resolution of an ADC. Two other important ADC parameters are the power consumption,  $P_{\rm d}$ , and the bandwidth, BW, usually expressed as the Nyquist frequency according to (1.10).

There exist many different applications for which uneven ADC requirements are needed. Some applications require extremely high resolution, others might require the sampling of signals with very large frequency and others might require the integration of many ADCs for multi-channeling purposes, requiring thus low power consumption. With this in mind, it is hard to tell if an ADC is better than another because the different performance metrics cannot be compared in a straight forward way. This is the motivation for the use of FoMs; to provide an useful metric to compare different ADCs and to be pushed to the limit by the research efforts [56].

One of the commonly used FoMs is the Walden FoM [57]:

$$FoM_{W} = \frac{P_{d}}{f_{nvo}2^{ENOB}} [J/conv]. \tag{1.14}$$

The three important performance metrics that have been discussed are included in the equation. Therefore, a good summary of the global ADC performance can me inferred from this value. The number given by this FoM represents the energy required to make the conversion per sample and per level, so the lower this number the better the ADC.

By inspecting this FoM, it can be seen that decreasing the power by  $\times 2$  yields the same improvement as increasing the ENOB by +1, or increasing the bandwidth by  $\times 2$ . The relationship between power and speed usually holds in practice, but the relationship between resolution and power starts differing as the resolution increases. For example, for many high-resolution ADCs, kTC noise sets the maximum achievable resolution, and in order to increase the ENOB by 1-bit the power consumption has to be increased by  $\times 4$  [58]. For this reason, the Walden FoM does not provide a fair evaluation of high-resolution ADC. This motivated the creation of the Schreier FoM, which takes all of the above discussion into account by establishing the following definition:

$$FoM_S = SNDR + 10 \log \frac{f_{\text{nyq}}}{2P_{\text{d}}} \text{ [dB]}. \tag{1.15}$$

Figure 1.4 | State-of-art ADC chart. Current FoM limits are shown in dashed lines.

According to this equation, the power has to be increased by  $\times 4$  in order to obtain a +6.02 dB FoM improvement (i.e. 1-bit ENOB increase), so this FoM is more coherent with the practical design issues of high-resolution ADCs.

## 1.2.2 State-of-Art ADCs

As mentioned in Section 1.2.1, FoMs are the metric used to evaluate the ADC performance. There are different types of ADC architectures, each excelling in different areas. The principles of operation of each architecture are always the same, but the research tries to incorporate new or more efficient techniques along with more optimal circuits in order to break the current state-of-the-art FoM limit.

The state-of-art ADCs can be plotted into the graph shown in Fig. 1.4 [59], representing the ADCs published in the IEEE International Solid-State Circuits Conference (ISSCC) and the Symposium on VLSI Technology and Circuits. The chart graphically represents the ADC resolution, in the x-axis, and the energy-per-Nyquist sample, in the y-axis. The current state-of-art FoM is delimited by the dashed lines, which represent the points with a same FoM value. The improvement trend moves perpendicular to the lines. Currently, the Schreier FoM limit is placed at 187dB, whereas the Walden FoM limit is at 0.35fJ/conv.

A distinction is made between the different base ADC architectures [60]. Flash ADCs have fallen behind other architectures, but they still have a place for ultra-high-speed applications [61]–[65]. Pipeline ADCs cover the range of applications requiring high-speed but also higher resolution than the one offered by flash types [66]–[69]. SAR ADCs exhibit the best balance between all the performance metrics [19]–[33], covering a wide

Figure 1.5 | State-of-art ADC chart showing only high-resolution ADCs (SNDR  $\geq$  90 dB) with general purpose bandwidth (BW  $\geq$  20kHz).

range of applications and currently achieving the highest Schreier FoM value [8]. Finally,  $\Delta\Sigma$ Ms cover the very high resolution application range, also achieving high FoM values [21]–[47], [70]–[83]. In addition, there exist additional architectures not shown in the chart individually, such as integrating ADCs, which are very efficient for low-speed applications and can potentially achieve very high resolution. The different characteristics of these ADC families are summarized in Table 1.1.

Out of all the ADCs shown in Fig. 1.4, it can be appreciated that only a small percentage of them are located in the very high resolution region (SNR  $\geq$  90 dB). Furthermore, if only the ADCs with an audio-range or wider bandwidth (i.e. general purpose ADCs) of this region are selected, then the total number of published ADCs is less than thirty, as depicted in Fig. 1.5 [14]–[18], [21]–[33], [43]–[47], [70], [71], [78]–[80]. In addition, the Schreier FoM, although competitive in some designs, does not achieve the best FoM values. The reason for this is that the design of such high resolution ADCs intended for general purpose applications is not trivial, and achieving such performance requires design trade-offs that are not positively accounted for even by the Schreier FoM.

| ADC Type                  | Strength                                      | Weakness                                    | Applications                                             |

|---------------------------|-----------------------------------------------|---------------------------------------------|----------------------------------------------------------|

| Flash                     | Highest speed                                 | Lowest resolution Power hungry Large area   | High-speed instrumentation                               |

| Pipeline                  | High speed<br>Moderate resolution             | Low power efficiency Latency Complex design | High-speed instrumentation                               |

| SAR                       | Best power efficiency<br>Minimalist design    | Moderate speed<br>Requires calibration      | Industrial measurement Data acquisition Audio processing |

| $\Delta\Sigma \mathrm{M}$ | Highest resolution                            | Requires digital support<br>Moderate speed  | Industrial measurement Data acquisition Audio processing |

| Integrating               | Potentially high resolution<br>Low complexity | Slower as resolution increases              | Low-speed industrial measurements                        |

**Table 1.1** | Qualitative comparison of the main ADC families.

# 1.3 Objectives and Scope

Following the motivation factors given in Section 1.1, the working hypotheses that build the basis of this PhD thesis can be summarized in the following statements:

- A high-resolution, low-power, moderate-bandwidth, calibration-free, state-of-the-art ADC can be fabricated in standard CMOS technology.

- It is possible to design state-of-the-art SC  $\Delta\Sigma$ Ms with a competitive FoM not so far behind their CT  $\Delta\Sigma$ Ms counterparts, with the advantages of enjoying increased robustness.

- A design methodology can be derived for the design and optimization of low-power SC ΔΣM ADCs.

- Such ADCs can be made suitable for space applications by the employment of a special design guidelines in order to increase their radiation robustness.

- It is possible to incorporate AGC capabilities into the SC  $\Delta\Sigma$ M architecture by implementing the appropriate ADC modifications.

In order to demonstrate whether these hypotheses are true or not, the research work presented in this PhD thesis can be defined according to the following objectives:

- A mathematical framework derived from circuital analysis in conjunction with high-level modeling and simulation, and a design methodology for the design of low-power SC  $\Delta\Sigma$ M ADCs.

- A state-of-the-art, high-resolution SC  $\Delta\Sigma M$  with a high, experimentally measured Schreier FoM.

- A flicker-noise cancellation mechanism for resolution enhancement in SC circuits.

- State-of-the-art, low-power circuits and techniques from the literature employed in order to improve the ADC performance, such as multi-bit quantization.

- The robustness of the SC  $\Delta\Sigma$ M architecture explored by porting the design into lower CMOS technology nodes, as well as the validation of the design methodology.

- Increase of the radiation-hardness of the ADC by incorporating rad-hard techniques into the design methodology, together with radiation tests in order to validate it.

- A full ADC intelectual property (IP) realization including the hardware implementation of the decimation filter and bus peripheral.

- A new SC  $\Delta\Sigma$ M architecture incorporating AGC capabilities.

As the statements above show, the scope of this PhD thesis focuses on SC  $\Delta\Sigma$ Ms. The contributions from this work attempt to show that SC  $\Delta\Sigma$ Ms are a viable choice when designing high-resolution ADCs and that there are many advantages to be obtained from making this choice. Many applications, such as high-quality audio processing, scientific measurement, space missions, etc... can benefit from the ADCs contributed by this work, and the proposed techniques for SC circuits may open new paths in the high-resolution research field.

# $\Delta\Sigma$ Modulation Principles and Modeling f 2