**ADVERTIMENT.** L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: https://creativecommons.org/licenses/?lang=ca

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: https://creativecommons.org/licenses/? lang=es

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license:

(c) () (o) https://creativecommons.org/licenses/?lang=en

# Characterization of degradation induced by BTI, HCI and OFF-State stress, and of the Resistive Switching phenomenon in FD-SOI Ω-Gate NW-FET devices. Analysis of aging relaxation in ring oscillator circuits fabricated in 28nm technology

Ph.D. Thesis written by Carlos Andrés Valdivieso León

Under the supervision of Dr. Rosana Rodríguez Martínez

Reliability of Electron Devices and Circuits group (REDEC)

Department of Electronic Engineering

Bellaterra (Cerdanyola del Valles), July 2025

The undersigned, Prof. Rosana Rodríguez Martínez, Professor of the Electronic Engineering Department (Engineering School) of the *Universitat Autònoma de Barcelona*,

#### **CERTIFY:**

That the thesis entitled "Characterization of degradation induced by BTI, HCI and OFF-State stress, and of the Resistive Switching phenomenon in FD-SOI Ω-Gate NW-FET devices. Analysis of aging relaxation in ring oscillator circuits fabricated in 28nm technology" has been written by the Ph.D. candidate Carlos Andrés Valdivieso León under her supervision, in fulfilment of the requirements of the PhD programme in Electronic and Telecommunication Engineering.

**Author:** Carlos Andrés Valdivieso León

**Supervisor:** Rosana Rodríguez Martínez

Bellaterra (Barcelona), July 2025.

# **Content**

| Content2                                                                          |      |

|-----------------------------------------------------------------------------------|------|

| Agradecimientos5                                                                  |      |

| Acknowledgement 6                                                                 |      |

| Preface                                                                           |      |

| 1. Introduction9                                                                  |      |

| 1.1 MOSFET device                                                                 | 9    |

| 1.1.1 Operation modes of a MOS capacitor                                          | . 10 |

| 1.1.2 Technology roadmap                                                          | . 11 |

| 1.1.3 Planar FD-SOI transistors                                                   | . 14 |

| 1.2 Variability in MOSFETs devices                                                | . 15 |

| 1.2.1 Time zero variability                                                       | . 16 |

| 1.2.2 Time dependent variability                                                  | . 16 |

| 1.2.2.1 Bias Temperature Instabilities (BTI)                                      | .16  |

| 1.2.2.2 Hot Carrier Injection (HCI)                                               | . 18 |

| 1.2.2.3 Off-state stress degradation (OSS)                                        | . 20 |

| 1.3 Reversible dielectric breakdown                                               | . 23 |

| 1.3.1 Resistive switching phenomenon (RS)                                         | . 24 |

| 1.3.2 Characteristics of resistive switching                                      | . 24 |

| 1.3.3 Resistive Switching commutation mechanisms                                  | . 26 |

| 2. Impact of OFF-State, HCI, and BTI degradation in FD-SOI Ω-Gate N<br>FETs29     | W-   |

| 2.1 Samples description                                                           | . 29 |

| 2.1.1 The 'SNOW' wafer map                                                        | . 30 |

| 2.1.2 Samples structure                                                           | . 31 |

| 2.2 Characterization setup                                                        | . 33 |

| Wafer probe station                                                               | . 34 |

| Semiconductor parameter analyzer                                                  | . 34 |

| 2.2.1 Characterization of transistor parameters                                   | . 35 |

| 2.3 Measurement procedure                                                         | . 35 |

| 2.4 Experimental Results                                                          | . 38 |

| 2.5 Conclusions                                                                   |      |

| 3. First observations of Resistive Switching in FD-SOI $\Omega$ -gate transistors | 49   |

|                                                                                   |      |

| 3.1 Resistive                                                                           | e Switching-like behavior in FD-SOI transistors                | 49             |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------|

| 3.1.1 Dev                                                                               | ice description                                                | 49             |

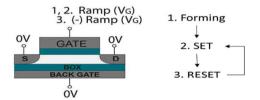

| 3.1.2 Setu                                                                              | p for Resistive Switching experiments                          | 51             |

| 3.1.3 Mea                                                                               | asurement procedure                                            | 51             |

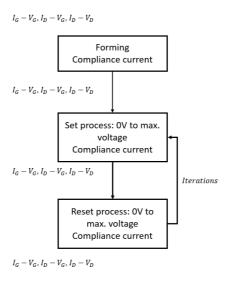

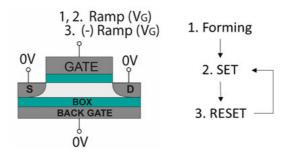

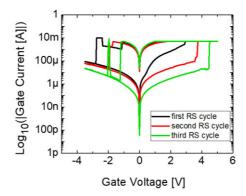

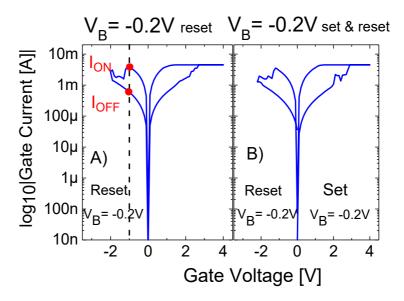

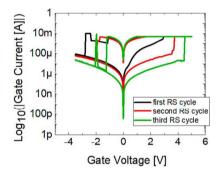

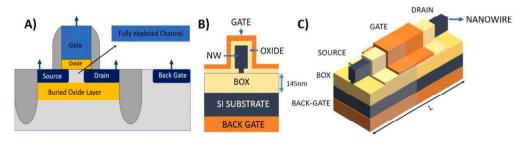

| 3.1.4 Exp                                                                               | erimental Results                                              | 53             |

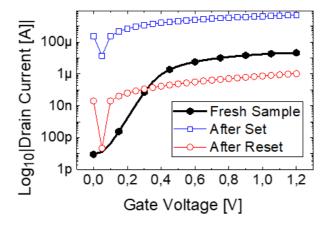

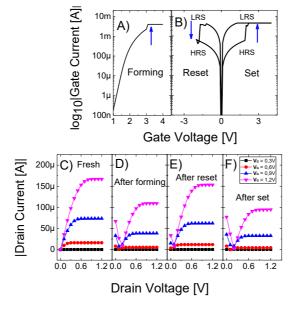

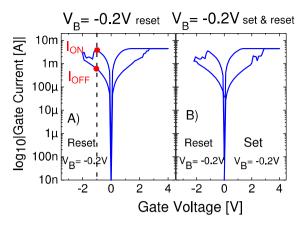

| 3.2 Partial r                                                                           | ecovery of transistor's characteristics during RS              | 55             |

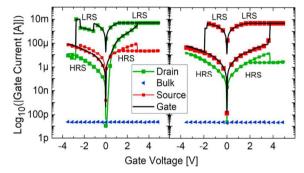

| 3.2.1 Res                                                                               | ults and discussion                                            | 55             |

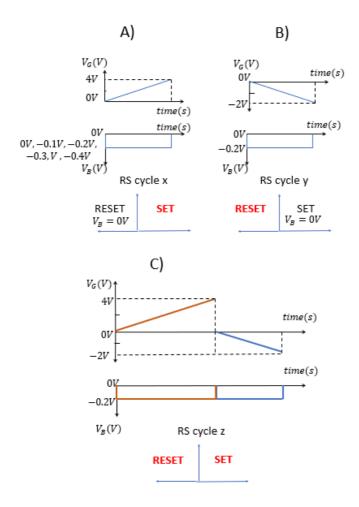

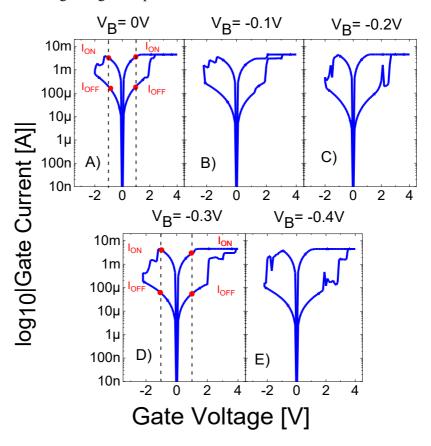

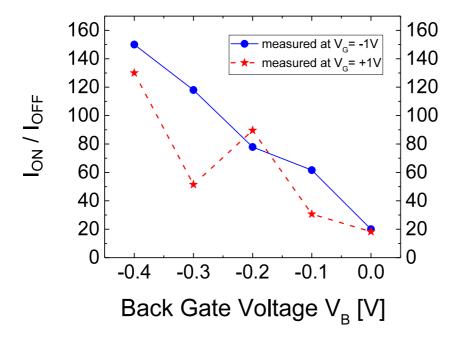

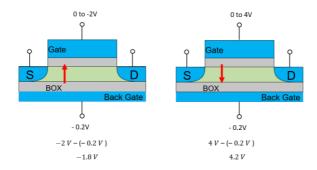

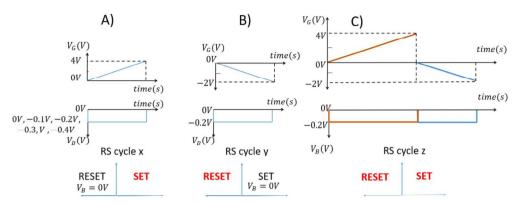

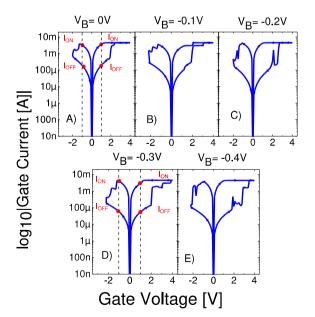

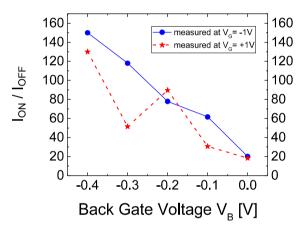

| 3.3 Impact of                                                                           | of the back gate bias on RS                                    | 57             |

| 3.3.1 Res                                                                               | ults and discussion                                            | 57             |

| 3.4 Conclus                                                                             | ions                                                           | 62             |

|                                                                                         |                                                                |                |

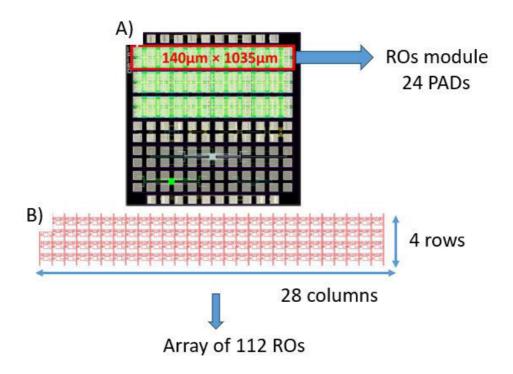

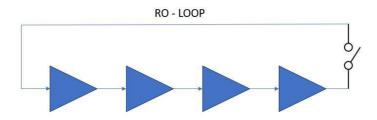

| 4. Aging relaxatio                                                                      | n after TDV in 28nm TSMC array of ring oscillators             | 63             |

| 0 0                                                                                     | n after TDV in 28nm TSMC array of ring oscillators description |                |

| 4.1 Samples                                                                             | •                                                              | 63             |

| 4.1 Samples 4.1.1 Arr                                                                   | description                                                    | 63<br>63       |

| 4.1 Samples 4.1.1 Arr 4.2 Charact                                                       | descriptionay of ring oscillators                              | 63<br>63       |

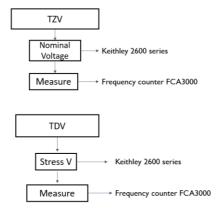

| 4.1 Samples 4.1.1 Arr 4.2 Charact 4.3 Measure                                           | description                                                    | 63<br>63<br>64 |

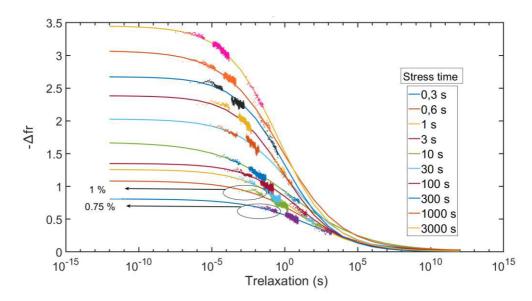

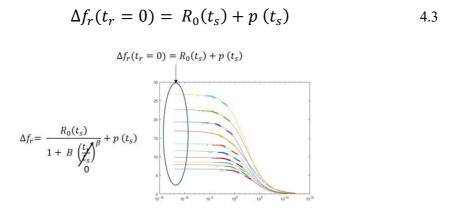

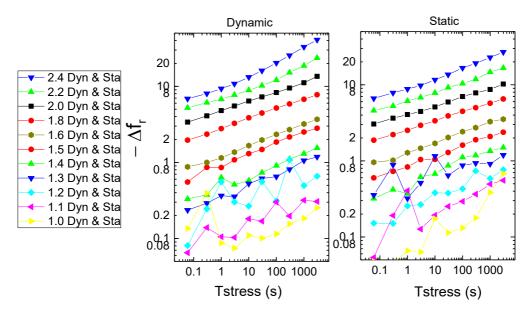

| 4.1 Samples 4.1.1 Arr 4.2 Charact 4.3 Measure 4.4 Results                               | description                                                    | 63<br>64<br>66 |

| 4.1 Samples 4.1.1 Arr 4.2 Charact 4.3 Measure 4.4 Results a 4.5 Conclusion              | description                                                    | 63<br>64<br>66 |

| 4.1 Samples 4.1.1 Arr 4.2 Charact 4.3 Measure 4.4 Results a 4.5 Conclusi Summary and Co | description                                                    | 63<br>64<br>66 |

"Aunque nuestro intelecto siempre quiera claridad y certeza, a nuestra naturaleza, normalmente, le parece fascinante la incertidumbre"

Carl von Clausewitz

# **Agradecimientos**

Durante estos últimos años, mucha gente ha hecho posible la realización de esta tesis doctoral. Es por eso, que me gustaría agradecerle a cada uno de ellos por sus palabras de aliento y guía en momentos de incertidumbre.

En primer lugar, me gustaría dar las gracias a mi tutora, Rosana Rodríguez, por estar siempre disponible para guiarme y resolver mis dudas en toda esta etapa doctoral.

En segundo lugar, quiero agradecer a mis padres José y Carmen, a ellos les debo mucha de mi personalidad, además, por apoyarme en mis decisiones desde que decidí dejar el país para estudiar. A mis hermanos Emilio y Karla por su apoyo fraternal y sincero cuando más lo necesitaba. A Tatiana, mi cuñada, a José Eduardo que con su inocencia llegó a alegrar la familia. A mis tíos Jimmy y Tania por acogerme como uno más en su casa y por sus consejos. A mi abuelita Graciela, que siempre creyó en mí, a mis primos y mis tíos gracias por todo.

También me gustaría agradecer a Albert Crespo, por su guía en las largas horas de laboratorio a Montserrat Nafría, Javier Martín, Emili Salvador y los demás miembros del grupo de investigación Redec, de cual que fui parte durante mi proceso doctoral. Por supuesto quiero agradecer a mis compañeros de departamento (Amir, Danyal, Pau, Jian, Paris, Ferran) por hacer más agradable el proceso del doctorado y por las risas.

Vorrei ringraziare anche il Professore Felice Crupi: è stato lui, insieme alla Professoressa Rosana Rodríguez, a darmi l'opportunità di intraprendere il dottorato. I suoi consigli si rifletteranno nel mio percorso professionale.

Obviamente quisiera agradecer a mis amigos (Carolina, Darly, Camila, Alejandra, Emily, Mariella, Jacqueline, Ignacio, Carlos y Michel) por las risas y hacer más llevadera esta aventura del doctorado.

# Acknowledgement

Over the past few years, many people have contributed to making this doctoral thesis possible. That is why I would like to thank each and every one of them for their words of encouragement and guidance during times of uncertainty.

First and foremost, I would like to thank my supervisor, Rosana Rodríguez, for always being available to guide me and answer my questions throughout this doctoral journey.

Secondly, I want to express my gratitude to my parents, José and Carmen. I owe much of my personality to them, and I'm especially grateful for their support in my decision to leave my country in pursuit of education. To my siblings, Emilio and Karla, thank you for your heartfelt and fraternal support when I needed it the most. To my sister-in-law Tatiana, and to José Eduardo, whose innocence brought joy to our family. To my uncles Jimmy and Tania, for welcoming me into their home and for their wise advice. To my grandmother Graciela, who always believed in me, and to my cousins and extended family, thank you for everything.

I would also like to thank Albert Crespo for his guidance during the long hours in the lab, as well as Montserrat Nafría, Javier Martín, Emili Salvador, and the other members of the Redec research group, of which I was a part throughout my doctoral process. Of course, I want to thank my department colleagues (Amir, Danyal, Pau, Jian, Paris, Ferrán, Álvaro) for making the doctoral journey more enjoyable and for all the laughter we shared.

I would also like to thank Professor Felice Crupi—it was he, along with Professor Rosana Rodríguez, who gave me the opportunity to pursue this PhD. His advice will be reflected in my professional path.

Naturally, I want to thank my friends (Carolina, Darly, Camila, Alejandra, Emily, Mariella, Jacqueline, Ignacio, Carlos, and Michel) for the laughter and for making this doctoral adventure more bearable.

# **Preface**

They have enabled significant improvements in many aspects of our lives, such as communication, transportation, and healthcare. Without the invention of the transistor in 1947 by John Bardeen, Walter Brattain and William Shockley, it would not have been possible to understand microelectronics in the 20<sup>th</sup> and 21<sup>st</sup> centuries, the miniaturization of electronic devices, and, later, the digitalization of society. Not only has the academic field focused its efforts on these achievements, but also the semiconductor industry, which finances research and seeks profitability for its products by maintaining low prices for consumers. Improvements in fabrication techniques have allowed consumer electronics to evolve. As a result, many different devices have emerged, such as computers, smartphones, and supercomputers.

Nowadays, there is a high demand for highly integrated devices that can storage more information with lower power consumption. The technological roadmap evolves with these new devices. As an example, FinFETs, the gate all around transistors (GAA-FETs) and  $\Omega$ -gate nanowire FETs fabricated with high dielectric materials (high-k dielectric).

Defects in transistors, such as interface traps and bulk traps, lead to device variations and impact reliability. They become more pronounced with the reduction in technology size. Variations in intrinsic transistor parameters, such as threshold voltage (Vth) or mobility  $(\mu)$ , both after fabrication and over time during circuit operation, are primary causes of performance deviations that can negatively impact integrated circuit (IC) reducing their intended lifetimes. These deviations must be statistically characterized and modelled.

In this context, it is essential to identify the most significant sources of phenomena affecting modern nanometer-scale MOSFETs. Furthermore, methodologies for experimentally characterizing devices to obtain precise transistor parameters due to degradation must be described.

The work presented in this thesis tries to advance in this way. Thus, an experimental characterization of the main failure mechanisms that take place in fully depleted silicon on insulator (FD-SOI)  $\Omega$ -gate nanowire FETs using high-k dielectric is presented. Aging of these samples due to Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), Off-state stress and dielectric breakdown are studied. The reversibility of the dielectric breakdown also known as resistive switching phenomenon, has also been observed and analyzed in this thesis.

On the other hand, the final goal is to analyze how device degradation affects the circuits performance. In this sense, in this thesis, the degradation of a TSMC array of a high-k ring oscillator is also studied.

In chapter 1, an overview of MOSFETs is provided, discussing their electrical characteristics and reviewing the key milestones in the evolution of electronics in recent years. It will then focus on the topic of variability, with particular attention to the phenomena of time zero variability (TZV) and time dependent variability (TDV), which significantly impact circuit performance and reliability. Then, a detailed explanation of the resistive switching phenomenon is presented.

Chapter 2 will present the samples FD-SOI (Fully Depleted Silicon on Insulator) high-K dielectric transistors used. Then, it will detail the methods used to characterize the aging mechanisms. Besides, the results of the main aging mechanisms will be presented. These mechanisms include BTI degradation, HCI degradation, and Off-state degradation. This chapter will evaluate and compare the degradation mechanisms observed after the stress phases in these samples.

Chapter 3 will address another key topic of this thesis: resistive switching. This phenomenon has been analyzed in the FD-SOI omega gate FETs samples. The chapter will be divided into two parts: first, the recovery of the transistor after the resistive switching phenomenon, and second, the effect of the transistor's back gate on the resistive switching.

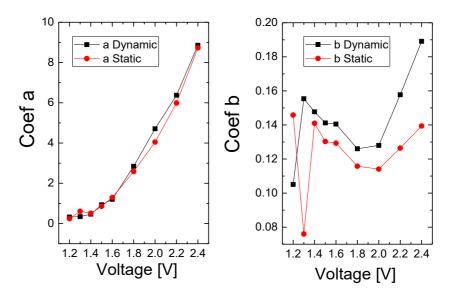

Chapter 4 will focus on the research conducted at the Inter-university Microelectronics Center (IMEC). This work outlines the electrical characterization performed at the circuit level. The samples used in these studies consist of TSMC 28nm high-k ring oscillator arrays. In these samples, both static degradation (BTI) and dynamic degradation (BTI-HCI) will be investigated, and the results will be presented.

Next, the conclusions of this thesis will be summarized. Finally, the annexes of this thesis will be appended.

# 1. Introduction

In this chapter, a brief review of the evolution of micro and nano electronics technology will be presented, with particular emphasis placed on the devices that are used in this thesis. Then, the types of variability will be described including the different failure mechanisms studied in this work. Finally, the resistive switching mechanism will be explained along with its characteristics.

# 1.1 MOSFET device

In this section, an overview of one of the most significant electronic innovations of the 20th century is presented. Subsequent sections will explore the evolution, composition, and electrical characteristics of MOSFETs in detail.

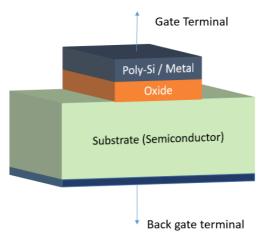

The MOSFET is composed by a MOS structure (Figure 1.1). The top layer is typically a metal, though it can also consist of highly doped polysilicon. Beneath this lies an insulating layer, commonly silicon dioxide (SiO<sub>2</sub>) or a *high-k* dielectric material. The substrate usually consists of silicon and can be doped to create either p-type or n-type devices, depending on the majority carriers present within the substrate.

Figure 1.1: Scheme of a MOS structure

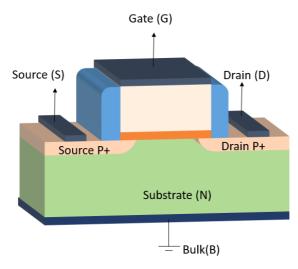

The MOS structure is completed to form a MOSFET by introducing two highly doped regions with impurities opposite to those in the substrate, thus, forming the source and drain regions. The device operates by forming a channel between source and drain contacts by inversion, electrons in the case of a p-type substrate (n-channel MOSFET) as shown in Figure 1.2, or holes in the case of an n-type substrate (p-channel MOSFET). The number of charge carriers in the channel are controlled by the gate terminal.

Figure 1.2: Scheme of an n-type substrate MOSFET device

# 1.1.1 Operation modes of a MOS capacitor

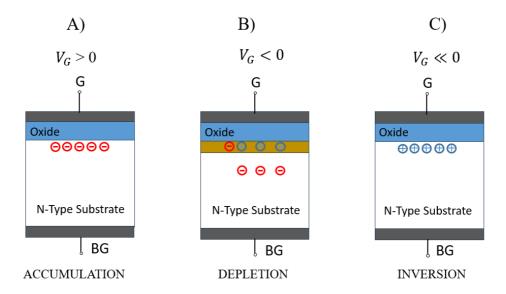

The MOS capacitance has three different modes of operation [1]. They are determined by variations in the gate voltage. These regions are defined based on whether the gate voltage increases or decreases. To explain the different MOS capacitor operation modes, we will consider a device with n-type substrate (Figure 1.2). The first mode of operation is called accumulation. This occurs when a positive voltage is applied to the gate contact  $(V_G>0)$ , so that the positive voltage attracts the electrons towards the interface between oxide and semiconductor. As a result, the majority carriers, electrons in this case, lead to an accumulation of electrons close to the interface (see Figure 1.3 A).

Depletion is the second mode of operation. It occurs when a small negative voltage is applied to the gate terminal ( $V_G$ <0). This negative voltage repels the electrons leaving a depletion region in the substrate region close to the oxide. The total capacitance decreases in comparison to the accumulation region and it leaves a positive charge in the depletion region as depicted in Figure 1.3 B).

The third mode of operation is inversion. This occurs when a voltage much lower than zero ( $V_G << 0$ ) is applied to the gate terminal. The highly negative charge begins to repel electrons, and eventually, minority carriers accumulate at the surface (see Figure 1.3 C). As for the capacitance, it initially decreases in weak inversion but saturates when strong inversion is reached.

Figure 1.3: Operations modes of a MOS capacitor. A) Accumulation. B) Depletion. C) Inversion.

# 1.1.2 Technology roadmap

The continuous advancement of microelectronics, along with the growing demand for more compact devices, has driven a sustained reduction in size, in line with Moore's Law. The evolution of MOSFET technology has progressed from simply reducing transistor dimensions to exploring new architectures designed to mitigate the effects associated with miniaturization: The most common problems associated to scaling include short channel effects as, for example, speed saturation, and channel length modulation [2], [3] between others.

This section presents key milestones in the scaling of MOSFETs:

## Planar MOSFET and CMOS

Planar MOSFETs and CMOS (Complementary MOS) became industry standards for low power applications [4]. One of its key characteristics was its length, approximately  $L = \sim 10 \mu m$ . This period covers from the 1960s to 1980s [5].

# Scaling Era

Moore's Law dominated this period that covers from the 1990s to 2000s, with the number of transistors within an integrated circuit doubling every two years. The achieved dimensions were 0.35 µm of technological node and smaller. In the 1990s the use of technological node started, with the establishment of technology roadmaps such as the National Technology Roadmap for Semiconductors (NTRS), which later evolved into the

International Technology Roadmap for Semiconductors (ITRS)[6] and subsequently the International Roadmap for Devices and Systems (IRDS)[7]. In the 2000s the name of technological node no longer corresponds to the physical channel length, and it became an industry convention.

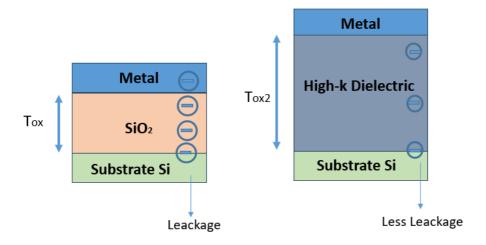

# High-k dielectrics, Strained Silicon

Scaling introduced another problem: the leakage currents through the dielectric. This event consists of electrons that cross the dielectric barrier between gate and substrate most known as *tunnel effect*. This phenomenon can form a current path that accelerates oxide degradation reducing the drain current and increasing the gate current. To mitigate these effects, high permittivity dielectrics or high-k dielectrics were introduced. The main characteristic of these materials is their high dielectric constant K [8]. The metal gate was introduced as well in this period which allow to reduce leakage currents and helped to continue scaling.

In Figure 1.4 the representation of a MOS structure with silicon oxide dielectric and its equivalent with high-k dielectric is depicted. From this figure, it can be extracted the definition of "Equivalent Oxide Thickness" (EOT) [9]. EOT is defined as the thickness of an ideal silicon dioxide layer that would yield the same capacitance per unit area as the high-k dielectric employed in the MOSFET gate stack. In other words, the dielectric material (high-k) exhibits the same electrical behavior as a much thinner silicon dioxide layer as represented in Figure 1.4.

Figure 1.4: LEFT: Schematic representation of a MOS structure with SiO<sub>2</sub> dielectric and RIGHT: its equivalent with high-K dielectric.

#### **FinFETs**

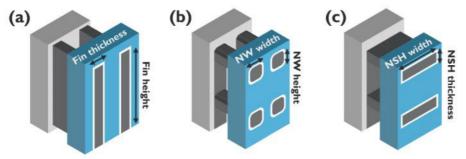

Another key moment (that covers between 2010s to 2020s) was the introduction of 3D transistors or FinFETs. In this case, the gate wrapped all the fin-shaped channel, which improves gate control (see Figure 1.5 a). With the introduction of FinFETs at technological node of 22nm low power performance was achieved jointly by the reduction of leakage currents [10].

#### Gate All Around

As transistors continue to shrink in size, new ways to improve its performance are emerging. Gate-All-Around (GAA) transistors are developed as a technology where the gate fully surrounds a finger structure, which results in enhanced performance and reduced leakage.

The International Roadmap for Devices and Systems (IRDS) [11] identified Gate-All-Around FETs (GAAFETs) as a key successor to FinFETs [12] for advancing future semiconductor nodes. These devices are categorized into vertical and lateral designs. Both lateral and vertical GAAFETs utilize structures such as *nanowires* (NW) and *nanosheets* (NSH) [13] for channel configurations (Figure 1.5 b and c respectively). They demonstrate significant potential for scaling below a technological node of 10 nm due to their enhanced control over short-channel effects and improved performance such as: power consumption (no p-n leakage currents), higher drive currents ( $I_{ON}$ ) faster switching speeds and low variability.

To optimize area and increase current drive lateral GAAFETs are arranged in stacked nanosheets or nanowires, where multiple sheets and wires are inserted. Lateral GAA structures offer improvements over FinFETs such as: full 360° electrostatic control, reduced short channel effects (DIBL, subthreshold leakage) [14]. In these configurations, the channel is completely wrapped by the gate material, as illustrated in Figure 1.5 b and c.

While lateral GAA transistors have already been adopted in advanced manufacturing nodes, vertical GAA architecture remains largely at the research stage and are currently less prevalent due to their higher fabrication complexity and integration challenge [15].

However, GAA transistors also require more complicated fabrication steps compared to  $\Omega$ -gate FETs which will be explained in the next sections. This fabrication complexity is due to gate wrapping and nanosheet/nanowire formation. Regarding gate wrapping, the complexity is due to advanced deposition techniques that technology requires, that is to say, the process to create thin films. Concerning nanosheet/nanowire formation, they require many etching - release processes, i.e. remove – isolate layers of material during fabrication process.

Figure 1.5: 3d schematic view of a lateral a) FinFET, b) NW-FET, c) NSH-FET [15].

On the other hand, cylindrical GAA refers to the vertical nanowire, commonly known as vertical GAA. The cylindrical shape of the channel enhances transistor performance by improving carrier distribution and minimizing corner effects (electric field concentration in sharp corners) [16].

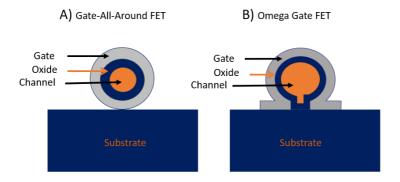

# Nanowire transistors - Omega-Gate

$\Omega$ -gate FETs are named due to the omega shape of the gate. They are considered as an improvement of the gate-all-around transistors [17]. The  $\Omega$ -gate FETs are an alternative to reduce the complicated fabrication processes that GAA requires as commented in the last paragraphs. In this kind of transistor, the gate wraps around the channel. Fig 1.6 shows the differences between GAA FETs and  $\Omega$ -gate FETs.

Figure 1.6: Cross section of a gate all around transistor (A) and  $\Omega$ -gate FET (B).

The  $\Omega$ -gate FET geometry where the gate wraps three sides of the channel provides better control minimizing short channel effects and reducing leakage currents [18]. Compared to planar transistors and FinFETs,  $\Omega$ -gate FETs offer enhanced performance and efficiency, particularly in lower 10nm applications like processors and memory devices. They improve scalability and reduce power consumption [19].

#### 1.1.3 Planar FD-SOI transistors

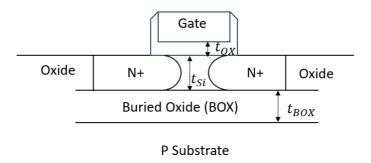

# Silicon on Insulator (SOI)

The use of silicon on insulator transistors was an improvement in terms of scaling and channel control. SOI technology has re-emerged as one of the most promising alternatives for continued scaling in semiconductors below 10nm [20]. This technology uses an insulator layer as can be seen in Figure 1.7, called buried oxide or BOX. This layer separates the active silicon region, reducing parasitic capacitances, enhancing energy efficiency and speed compared to traditional bulk silicon semiconductors [20]. In particular, the SOI technology devices eliminate latch-up. Latch-up is an effect that appears between p-n junctions that cause high current flow between them.

Figure 1.7: Schematic representation of a SOI planar - transistor

SOI technology is classified in two types based on its fabrication:

**Partially depleted silicon on insulator (PD-SOI).** - A partially depleted device is the technology where the silicon layer,  $t_{Si}$  in Figure 1.7, allows the charge accumulation within the channel. This flexibility simplifies the manufacturing process. Contrarily to FD-SOI, body effects are found in this technology.

The body effect refers to the fact that the body region (located between the buried oxide and the dielectric) is electrically floating and capable of accumulating charge. This charge rise can result in an increase in the threshold voltage, with the direction of the shift depending on whether the device is an NMOS or PMOS transistor, respectively. This body effect depends mostly on the biasing conditions of the source, drain, and gate terminals, but not on the substrate, as it is electrically isolated by the buried oxide (BOX) layer.

**Fully depleted silicon on insulator (FD-SOI).** – In this technology the silicon layer,  $t_{Si}$  in the Figure 1.7, is depleted i.e. no charge accumulation occurs within the channel. In a fully depleted device, the influence of the substrate voltage (body) on the threshold voltage  $V_{TH}$  (body effect) is eliminated.

# 1.2 Variability in MOSFETs devices

The variability in transistors refers to the fluctuation in their electrical characteristics. There are two types of variations: Time Zero Variability (TZV) and Time Dependent Variability (TDV), and they will be described in the next paragraphs.

The combined effects of TZV and TDV can critically impact on the functionality of devices and circuits, diminish device and circuit reliability and potentially shortening their operational lifetime. So, their statistical characterization and modeling are necessary.

# 1.2.1 Time zero variability

The variability phenomenon has always been present in semiconductor fabrication. Time Zero Variability (TZV) refers to those device fluctuations due to the manufacturing imperfections in transistor fabrication that cause variability in transistor parameters as technology scales down. TZV is also known as process variation. This could be stochastic or systematic. The stochastic time zero variability refers to the variability that occurs between devices of the same die. The systematic variation is the variation of the devices parameters between die to die, wafer to wafer, or lot to lot [21].

# 1.2.2 Time dependent variability

As its name suggests, time-dependent variability (TDV) refers to the variations that devices parameters experience after a period of use under operation conditions. TDV is also known as 'Aging'. Most important aging mechanisms are Bias Temperature Instabilities (BTI), Hot Carrier Injection (HCI), OFF-State Stress (OSS) and dielectric breakdown. In the next sections, these mechanisms will be developed in depth. It is therefore necessary to characterize aging mechanisms to determine the durability of devices.

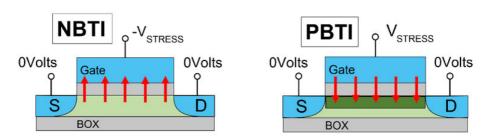

# 1.2.2.1 Bias Temperature Instabilities (BTI)

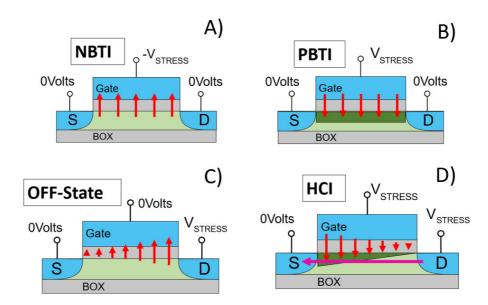

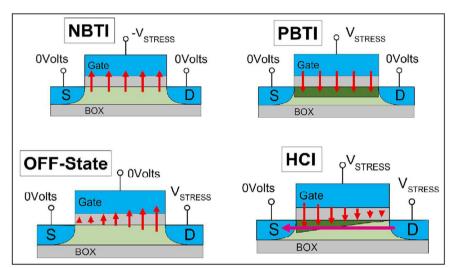

The Bias Temperature Instabilities, known as BTI, is an aging mechanism that is produced when a device is subjected to elevate temperatures and voltages during a limited time. In p-MOSFETs, it is known as *NBTI*. To characterize NBTI, the gate terminal of the transistor is biased with negative voltage. The electric field that the dielectric endures goes from bulk to gate (red arrows in figure 1.8 LEFT). The transistor's other terminals are grounded. Holes (positive charges) are attracted to the gate insulator interface, which causes continuous degradation in transistors' parameters as: threshold voltage ( $V_{th}$ ), transconductance (gm), linear current  $I_{DLIN}$  and saturation current  $I_{DSAT}$  between others [22], [23].

NBTI was observed for the first time in  $SiO_2$  and SiON insulators [24]. Later after the introduction of high-K dielectrics is still an important aging mechanism and reliability

concern. The discovery of this aging mechanism led to the development of models that predict this behavior.

Figure 1.8: Representation of a transistor subjected to NBTI (LEFT) and PBTI (RIGHT). In both cases, the direction of the electric field through the dielectric is represented with red arrows.

In the case of n-MOSFETs, BTI is called *PBTI*, and it is caused when the gate terminal is biased with positive voltages and electrons (negative charges) are attracted to the gate dielectric interface. The electric field is directed towards the bulk (red arrows in figure 1.8 RIGHT). Both NBTI and PBTI illustrate the effects of TDV.

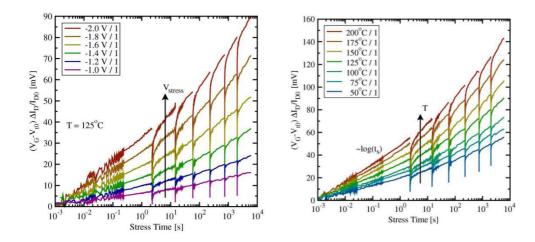

The consequences of P/NBTI are the degradation of transistor's parameters like  $\Delta V_{th}$ , mobility  $\Delta\mu$ , drain current  $I_{DS}$  and carrier propagation delay  $\tau_{PD}$ , between others. These changes are not permanent; rather, they have the potential to be reversed after the transistor bias is stopped (relaxation window), allowing it to recover some of its original performance characteristic [20]. According to the reference, even after a long period of relaxation window it is not enough to reach a total recovery i.e. a  $\Delta V_{th} = 0$ . In [25], a permanent component of relaxation is recognizable after a measurement of 7 decades of relaxation but it is not universal behavior and it will depend on the sample. Defects in materials that cause BTI such as oxygen vacancies and bond breaks in silicon can be activated due to temperature, and voltage. In Figure 1.9 (LEFT) a measurement obtained in [26] shows a voltage dependency of BTI, which means that when stress voltages (from 1.0V to 2.0V) increase, the degradation also increases. In Figure 1.9 (RIGHT) different temperatures tested in a device stressed at the same voltage V = -2V are presented. As observed, for a stress time of 10s, low temperature (50°C in Figure 1.9 RIGHT) reach a maximum of 60mV of degradation of the observed parameter, while 200°C (red lines in Figure 1.9) reach ~140mV of degradation. This tendency shows that at higher temperatures higher is the degradation in BTI.

Figure 1.9. BTI degradation LEFT: for different stress voltages at T= 125°C where degradation depends on stress voltage. RIGHT: for 7 different temperatures at a stress voltage of V= -2V [26].

About the frequency dependency of BTI, many publications show the importance of BTI when the device is subjected to dynamic voltage (AC-BTI) [27], [28], [29]. This aging mechanism is known as the dominant degradation mechanism in computation CMOS logic [30]. Understanding the characteristics of AC-BTI is important, notably its dependence on the duty factor. Specifically, it has been observed that higher duty factors lead to an increased degradation of BTI [30]. Moreover, some publications have shown a strong frequency dependence. For example in [31], the frequency dependence is analyzed using the recently proposed capture/emission time map model. This model explains Bias Temperature Instability (BTI) as a collection of numerous independent reactions reaching good accuracy with experimental data.

# 1.2.2.2 Hot Carrier Injection (HCI)

Hot Carrier Injection (HCI) is another aging phenomenon that was discovered nearly 50 years ago. From the seventies until the 21st century, research focused on understanding the physics of this principal failure mechanism [32]. This effort converged in the development of models that could predict the behavior [33].

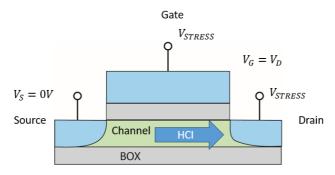

HCI takes place when carriers move in the transistor's channel from source to drain. This mechanism is accelerated by the lateral electric field generated by voltage applied to drain and gate terminals. Some carriers acquire enough energy to penetrate the gate dielectric (impact ionization). These carriers will generate defects that affect the characteristics of the transistor. Figure 1.10 shows the schematics of a transistor under HCI degradation. The blue arrow shows the direction of the lateral electric field and later degradation near the drain side (nonuniform stress).

For long-channel devices ( $L > 0.15\mu m$ ),  $V_G = V_D/2$  is the most harmful condition at room temperature. But for short-channel transistors the higher degradation that happens at room temperature is when  $V_G = V_D$  [34], [35]. Long and short channel transistors are usually stressed under the most harmful conditions. On the one hand, in long-channel devices stressed at  $V_G = V_D/2$  the degradation is less serious due to decreased number and energy of carriers. On the other hand, degradation in short-channel transistors stressed at  $V_G = V_D$  increases [36], which means that for short channel devices HCI is substantially harmful.

Figure 1.10: Schematics of the effect of HCI in the transistor's channel

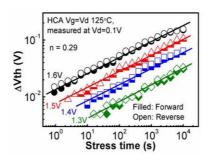

As BTI phenomenon, HCI aging is also voltage dependent. It can generate a shift in transistor's threshold voltage  $V_{TH}$ , and a reduction of the saturation current [37]. In Figure 1.11, voltage dependency is tested. Several biases tested demonstrate that at higher voltage, threshold voltage degradation  $\Delta V_{TH}$  increases [38].

Figure 1.11: Threshold voltage  $V_{TH}$  degradation vs stress time after HCI aging. Different biases tested and measured at  $V_D = 0.1V$  under 125°C of temperature [38].

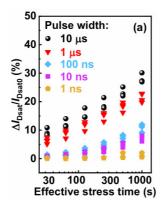

HCI is a phenomenon influenced by temperature; higher temperatures result in more severe degradation than lower temperatures under DC stress conditions. HCI depends on frequency, just as BTI aging mechanism, under dynamic conditions (AC-HCI), the degradation at the same temperature is less severe than for samples subjected to DC conditions. As shown in Figure 1.12, some studies show that HCI degradation depends on pulse width. If the signal has a longer pulse width (pulse region where the maximum degradation condition is satisfied  $V_G = V_D/2$ ), more degradation due to the time of exposure that devices endure under HCI. [39].

Figure 1.12: AC HCI degradation with different pulse widths at temperature of 85° C [39].

# 1.2.2.3 Off-state stress degradation (OSS)

Another aging mechanism that has attracted attention recently is the Off-State Stress (OSS) degradation. While HCI and BTI were extensively studied in an 'on-state' of the transistor [40],[41], 'off-state' has not been deeply studied in the last decades [42]. Certainly, this mechanism was not a big reliability concern in  $SiO_2$  poly devices, but the use of high-k dielectrics increased the risk of OSS due to hole trapping inside high-k defects [42].

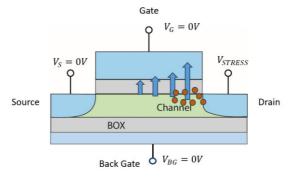

OSS happens when the transistor is in 'off' mode ( $V_G = 0V$ ) (see Figure 1.13), In this state, the source terminal is grounded ( $V_S = 0V$ ), and also the back gate ( $V_{BG} = 0V$ ), while the drain terminal is biased ( $V_D = V_{STRESS}$ ). This bias creates a lateral electric field that can, over the long term, affect the dielectric material. The damage produced by OSS is located in the oxide close to drain terminal (Figure 1.13). Some researchers have shown that during OSS, the subthreshold slope (SS) increases significantly. It is well known that as the gate dielectric thickness ( $T_{OX}$ ) continues to thin, controlling the off-state current becomes more complicated [43].

Figure 1.13: Schematics of a transistor under Off-state degradation.

Normally, the devices during their operation are subjected to different failure mechanisms. Transistors frequently switch between on and off states. When in off state, the drain  $V_D > 0$  V faces high voltage while the gate remains at zero voltage, which can lead to potential degradation [44]. In the opposite order, in the on state (where  $|V_G| > 0$  V and  $V_D = 0$  V), BTI becomes a significant factor. During the switching process, when both  $|V_G|$  and  $|V_D|$  are active, HCI can occur.

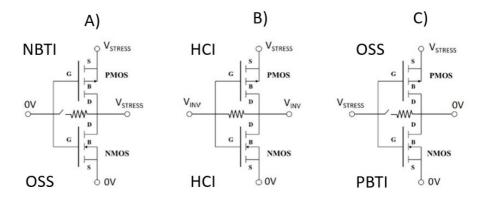

In applications such as CMOS inverters or SRAM cells, degradation during the off state plays a substantial role in devices wear-out and needs careful assessment to maintain circuit reliability. In Figure 1.14, the actuation of three aging mechanisms in an inverter is represented. When a low voltage is applied to the input (0V in case A), a negative drop between gate-source and gate-drain is produced. In consequence, pMOSFET suffers NBTI. The nMOSFET is not conducing but an electric field is produced (1V in output), so the nMOSFET suffers OSS. When the input is switched to '1' (case B), the output voltage shifts from '1' to '0' and in this transition both transistors are subjected to HCI aging with  $V_D = V_G$ . Finally, when a high voltage is applied at the input, the nMOSFET experiences PBTI, while the pMOSFET undergoes OSS. This situation (case C) is the opposite of what occurs in case A.

Figure 1.14: In an inverter, the bias switch between the drain and gate makes the device suffer OSS and BTI, alternatively HCI is suffered.

#### 1.2.2.4 Dielectric breakdown

Dielectric breakdown is a consequence of the device dielectric degradation. Degradation leads to a loss of the fundamental characteristics that define these materials. Breakdown signifies either a complete or partial loss of the isolated properties of the device dielectric [45], [46], [47].

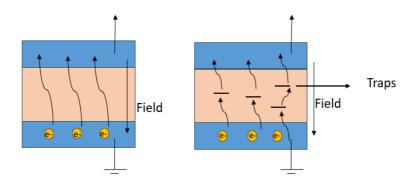

Dielectric degradation can be observed when electric stress is applied to the dielectric. In thin insulators, due to the voltage applied, a tunnel conduction is produced through the dielectric. Progressively this conduction will create defects inside the oxide and the interfaces of the oxide with the electrodes. Electrons may either pass directly through the dielectric (Figure 1.15 LEFT) or be assisted by traps present within the oxide (Figure 1.15 RIGHT). There is a moment when the critical density of defects [48] is reached. In this moment dielectric breakdown happens, according to percolative model [49].

Figure 1.15: LEFT: Schematic representation of the tunnel effect. RIGHT: trapped assisted tunnel effect.

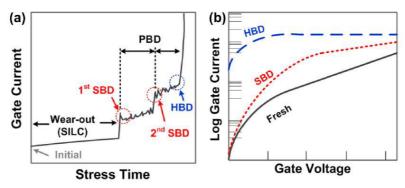

There are different types of dielectric breakdown: *Hard Breakdown* (HBD) occurs when there is an abrupt change in current, resulting in catastrophic damage to the device. *Soft Breakdown* (SBD) involves a rapid increase in current that causes moderate damage to the dielectric, that although not immediately devastating, it can lead to significant issues over time. *Progressive Breakdown* (PBD) manifests as incremental damage, which can silently affect the device's functionality [50].

In Figure 1.16 a), the evolution of the leakage current through the dielectric as degradation increases is illustrated. It begins with the initial stress induced leakage current (SILC). Next, the first soft breakdown (SBD) occurs, followed by a noticeable increase between the first and second SBDs, which can be identified as progressive dielectric breakdown (PDB). Finally, the abrupt change in current at the end is classified as hard breakdown (HBD). This types of breakdown are not a general behavior and depend on the dielectric thickness of the device. In figure 1.16 b) the typical I-V characteristic of the fresh device (black) and after stressed with SBD (red) and HBD (blue).

Figure 1.16: Representation of the gate current increment versus time as the dielectric degradation increases: representation of hard breakdown (HBD), soft breakdown (SBD) and progressive breakdown (PBD) (a) and typical I-V curves of a fresh sample and after a after stress (b) [47].

# 1.3 Reversible dielectric breakdown

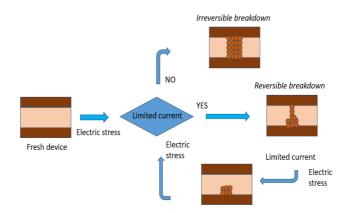

As previously mentioned, dielectric breakdown leads to a gradual loss of the device dielectric isolating properties, which can result in permanent damage. However, with the proper current limitation and devices with determinate materials, it is possible for a device to regain some of its dielectric properties after experiencing a drop in resistance when exposed to controlled electrical conditions again. This phenomenon is referred to as reversible dielectric breakdown and it is directly linked to the resistive switching phenomenon, that will be explained in the following sections. In Figure 1.17, the schematic representation of hard breakdown (HBD), also known as irreversible breakdown, and a reversible breakdown, is illustrated. When a fresh device is subjected to electric stress without current limitations, it experiences an irreversible breakdown. In contrast, if the current is limited, the electrical conductance of the device can be restored by applying determinate voltages. This process can be cycled multiple times, depending on the level of current limits.

Figure 1.17 Schematic representation of irreversible and reversible breakdown.

# 1.3.1 Resistive switching phenomenon (RS)

Resistive switching (RS) is a phenomenon in which a device experiences a non-volatil change in its electrical resistance when a determined voltage is applied. Resistive switching phenomenon was discovered in the 1960s [51]. This study was performed in a Metal-Insulator-Metal MIM structure of  $Al_2 O_3$ . But the phenomenon started to be deeply studied many years later. After, it was demonstrated that RS could define clearly stable resistive states. Memories based on RS are considered as possible substitutes to *flash* memories [52].

Devices that exhibit resistive switching (RS) behavior are commonly referred to as *memristive devices*. Among them, the most prominent and widely utilized is the *memristor*, a component theoretically introduced by Leon Chua in 1971 as the fourth fundamental two-terminal circuit element, alongside the resistor, capacitor, and inductor [53], [54].

Some works about RS in very scaled devices such as Gate All Around (GAA) transistors are found in literature. In [55], [56] RS is observed in vertical GAA nanopillars integrated with RRAM cells, showing good non-volatile memory properties.

In the next sections, the RS characteristics and the different physical mechanisms responsible for RS, will be explained.

# 1.3.2 Characteristics of resistive switching

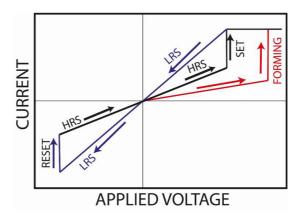

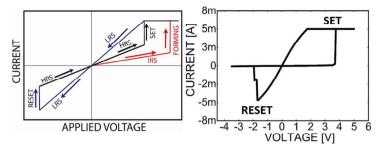

In a device with RS, two different resistance states can be distinguished: low resistance state (LRS) and high resistance state (HRS) (Figure 1.18).

Low Resistance State (LRS) or On-state: It is a high conductivity state. High Resistance State (HRS) or Off-state: It is a low conductivity state. When characterizing a resistive switching (RS) device, three distinct mechanisms emerge:

**Forming:** This is the initial voltage applied to the device or material. This process typically leaves the device in a low-resistance state (LRS) (see Figure 1.18). In some thin oxide materials, performing this step may not be necessary to observe RS.

*Set:* This mechanism refers to the transition from a high-resistance state (HRS) to a low-resistance state (LRS) (Figure 1.18).

**Reset**: This process involves changing from the LRS back to the HRS (Figure 1.18).

Figure 1.18 Representation of an I-V characteristic of a device with RS in which can be recognized forming, set and reset processes.

Usually, during both *forming* and *set* process, a current limit or compliance is applied to prevent hard breakdown (HBD). In contrast, during the *reset* phase, it is not necessary to limit the current, as the energy used is sufficient to change the conductive state [57].

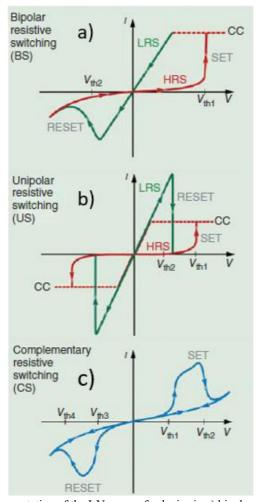

There are three RS modes that depend on the polarity of the *set* and *reset* and the stability of the states:

**Bipolar RS:** In bipolar RS, *reset* and *set* processes happen at different polarities. To observe this kind of RS, the applied polarities could be both when  $V_{set} > 0$  and  $V_{reset} < 0$  or  $V_{reset} > 0$  and  $V_{set} < 0$ . Starting at HRS, a set process can be triggered by  $V_{set} > V_{th1}$  which results in LRS as described in Figure 1.19 a.

Unipolar RS: Reset and set processes happen in the same polarity. It can be distinguished between unipolar positive ( $V_{set}$  and  $V_{reset} > 0$ ) and unipolar negative ( $V_{set}$  and  $V_{reset} < 0$ ) as represented in figure 1.19 b. Starting at HRS, the set process is triggered at  $V_{set} > V_{th1}$ . The current compliance is often limiting LRS which is released in RESET process with  $V_{reset} > V_{th2}$ .

**RS** threshold: Even though it is fundamentally associated with the resistive switching phenomenon, it cannot be strictly categorized as a standard RS mode due to its distinct behavior regarding voltage polarity and the transient nature of its states. Unlike RS, when the voltage is reverted to zero, the resultant resistance state exhibits a volatile nature, leading to inverse switching at a different threshold voltage,  $V_{th1}$  (see Figure 1.19 c). [58].

Figure 1.19. Schematic representation of the I-V curve of a device in a) bipolar resistive switching mode. b) unipolar resistive switching. c) complementary resistive switching [51].

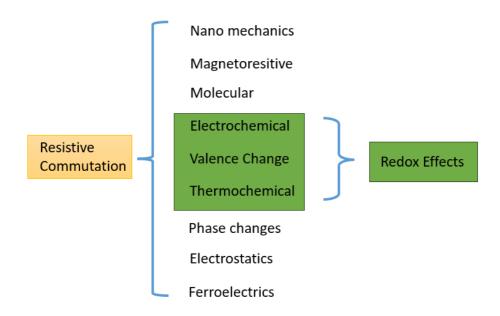

# 1.3.3 Resistive Switching commutation mechanisms

In resistive switching devices, a significant array of processes (Figure 1.20) contributes to the phenomenon of RS. Figure 1.20 illustrates the classification of the different processes that generate the RS phenomenon. They are electrochemical mechanisms (ECM), valence change mechanism (VCM), thermochemical mechanism (TCM), phase changes memories, electrostatics, ferroelectrics, nanomechanics, magneto-resistive and molecular. Among these, we will focus on redox-based mechanisms, which we will see in this thesis.

Figure 1.20 Classification of RS commutation physical mechanisms [59].

The generation and destruction of a conductive filament (CF) within the dielectric are key characteristics of reduction-oxidation (RedOx) mechanisms. RedOx mechanisms are chemical processes that involve the transfer of electrons. Oxygen vacancies or metallic cations can migrate within the dielectric, facilitating the formation and destruction of a conductive filament. This process is influenced by the presence and movement of ions within the dielectric material.

The Mechanisms associated with RedOx processes are:

**Electrochemical Mechanism:** This process is controlled by an electric field and is directly based on the diffusion of a metallic electrode through the oxide, resulting in the formation of a metallic conductive filament (CF).

*Valence Change Mechanism*: As the name suggests, this mechanism involves the generation of oxygen vacancies within the oxide, which create conductive regions inside the dielectric material.

**Thermochemical Mechanism:** This process is governed by thermal effects. The resistive switching (RS) phenomenon occurs due to the melting of the conductive filament (CF). Thermal effects also influence the diffusion of atoms and ions.

# 2. Impact of OFF-State, HCI, and BTI degradation in FD-SOI Ω-Gate NW-FETs

The results of this chapter are reproduced and/or adapted from:

- C. Valdivieso, A. Crespo-Yepes, R. Miranda, D. Bernal, J. Martin-Martinez, R. Rodriguez, M. Nafria, "Comparison of OFF-State, HCI and BTI degradation in FDSOI Ω-gate NW-FETs", Solid-State Electronics, Volume 194, 2022.

- C. Valdivieso, A. Crespo-Yepes, R. Miranda, D. Bernal, J. Martin-Martinez, R. Rodriguez, M. Nafria, "Impact of OFF-State, HCI and BTI degradation in FDSOI Ω-gate NW-FETs", Solid-State Electronics, Volume 203, 2023.

This chapter is structured into three sections. The first section provides a detailed description of the samples selected from the 'Snow' wafer map and the characterization methods employed. In the second section, experimental results will be presented for HCI, BTI, and OSS. Finally, the conclusions of this chapter will be summarized.

As it was presented in Chapter 1, device degradation caused by BTI or HCI is still relevant in deeply scaled CMOS technologies [60], [61], [62], [63], [64], [65]. The measurement of device degradation by subjecting them to elevated temperatures and voltages accelerates the deterioration of circuits that would otherwise last for years. In recent years, there has been a growing interest on understanding the degradation effects caused by OFF-state stress (OSS), a phenomenon that can arise during the operation of electronic devices within circuits [66], [67], [68], [69], [70], [71]. As highlighted in section 1.2.2.3, OSS plays a critical role in determining the reliability and longevity of these devices. In this chapter, the effects of negative/positive BTI and HCI degradations are also experimentally studied and compared to that of the OFF-state stress in FD-SOI  $\Omega$ -gate FETs. The dependence on the stress voltage of the ON and OFF drain current shifts induced by OFF-State stresses is also analyzed. Moreover, the variations of the drain, source, back gate and gate currents during and after the stress are compared, to evaluate in more detail the effects on the device electrical properties of each of the aging mechanisms.

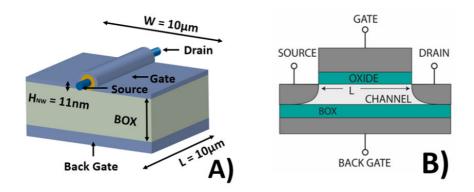

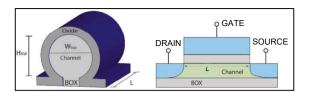

# 2.1 Samples description

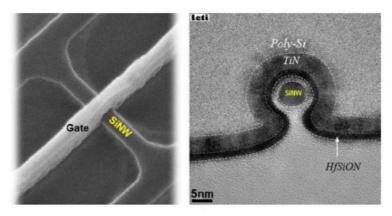

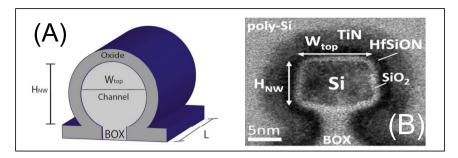

The FD-SOI  $\Omega$ -gate nanowire field-effect transistors (FETs) used in this chapter are illustrated in Figure 2.1. They are a type of Gate-All-Around (GAA) transistor that features an omega-shaped gate that encircles the channel. These devices were fabricated by CEA LETI [72] and utilize a high-k dielectric stack. In Figure 2.1 left, the nanowire (from top) Scanning Electron Microscopy (SEM) image is shown. While, in Figure 2.1 right, the transistor cross-sectional Transmission Electron Microscopy (TEM) image is presented.

Figure 2.1 (Left) scanning electron microscopy (SEM) and (right) cross-sectional transmission electron microscopy (TEM) images of SOI omega-gate nanowire [72].

# 2.1.1 The 'SNOW' wafer map

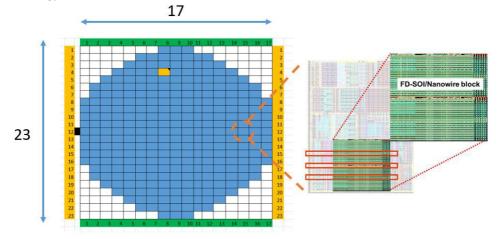

Most of the devices used in this thesis are integrated into a silicon wafer called 'SNOW'. It is organized into a grid of 17 rows and 23 columns, as illustrated in Figure 2.2. This wafer is carefully divided into individual dies. Within each die, lies a specialized block that incorporates advanced FD-SOI (Fully Depleted Silicon-On-Insulator) nanowire technology.

Figure 2.2 'Snow' wafer representation subdivided into individual dies that contains the FD-SOI nanowires transistors.

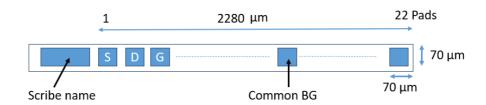

The structure consists of 22 pads, each of them with an area of  $70 \times 70 \mu m^2$ . All 22 pads cover a length of  $2820 \mu m$  (see Figure 2.3) and contain 7 devices. The typical arrangement of these pads follows a specific order: beginning with the source terminal (S), followed by the drain terminal (D), then the gate terminal (G), and finally the back gate terminal of the transistors (BG), which is common for seven devices (see Figure 2.3). The devices distribution is shown in Table 2.1.

Figure 2.3 Pad distribution of 7 devices in 22 pads with common back gate contact for all 7 devices.

| Pad | Connection               | Pad | Connection         |

|-----|--------------------------|-----|--------------------|

| 1   | Source of device 1       | 12  | Drain of device 4  |

| 2   | Drain of device 1        | 13  | Gate of device 4   |

| 3   | Gate of device 1         | 14  | Source of device 5 |

| 4   | Source of device 2       | 15  | Drain of device 5  |

| 5   | Drain of device 2        | 16  | Gate of device 5   |

| 6   | Gate of device 2         | 17  | Source of device 6 |

| 7   | Source of device 3       | 18  | Drain of device 6  |

| 8   | Drain of device 3        | 19  | Gate of device 6   |

| 9   | Gate of device 3         | 20  | Source of device 7 |

| 10  | Common substrate contact | 21  | Drain of device 7  |

| 11  | Source of device 4       | 22  | Gate of device 7   |

Table 2.1 Pad distribution of the devices.

# 2.1.2 Samples structure

In the previous subsection, the 'SNOW' wafer map exhibited a well-organized arrangement of devices in rows. In Table 2.2 the total number of devices used in this chapter is shown, organized by name of scribe, length and width.

| Scribe Name | <b>W</b> (μ <b>m</b> ) | L(µm) Orientation |   | Type (n/p) | # of<br>Samp.<br>used |

|-------------|------------------------|-------------------|---|------------|-----------------------|

| N14         | 0.03                   | 0.01              | 0 | N          | 2                     |

| N14 | 0.03 | 0.02 | 0 | N | 42 |

|-----|------|------|---|---|----|

| N14 | 0.03 | 0.03 | 0 | N | 3  |

| N14 | 0.03 | 0.1  | 0 | N | 2  |

Table 2.2 List of the samples tested in this chapter.

To ensure proper organization of the measurements, each device was marked after the experimentation process. Most of the results used in this chapter are based on one type of device which, after extensive experimentation, was identified as the most suitable for performing the tests conducted. This transistor is designated as its corresponding scribe name, which is **N14**, and it will be described in the next paragraph.

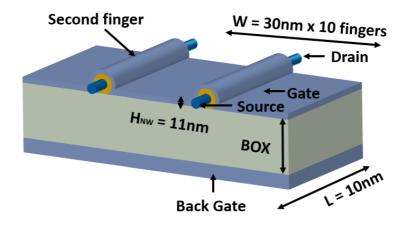

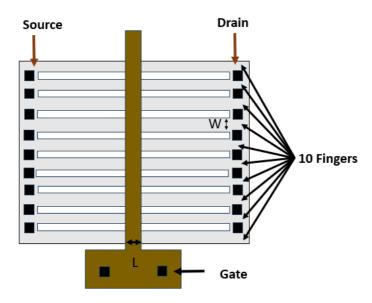

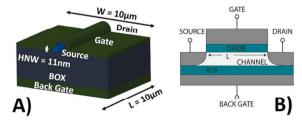

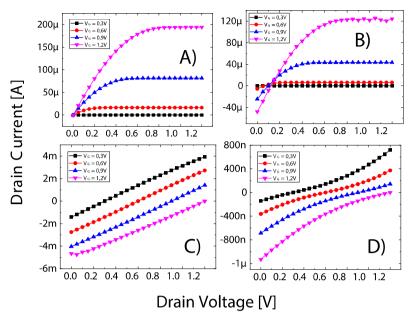

**Device N14:** The structure of the FD-SOI nanowire transistor [72] is represented in Figure 2.4 up. It has a dielectric, which is a combination of HfSiON/TiN with equivalent oxide thickness of EOT = 1.3nm. The device's dimensions are  $W = 300nm \times L = 10,20,30,100 nm$ . The nanowire height is  $H_{NW} = 11nm$ . The device contains a buried oxide layer (BOX) with a thickness of 145nm. The gate terminal is comprised entirely of a poly-silicon layer.

It is a multi-finger design, characterized by multiple fingers that extend from a common junction point as represented in Figure 2.4 down. This device is used to test aging mechanisms such as BTI, HCI, and OSS due to its short channel characteristics. The most N14 devices used in this chapter have the follow dimensions:

- 1)  $W = 30nm \times 10 \text{ fingers}, L = 10nm,$

- 2)  $W = 30nm \times 10 \text{ fingers, } L = 20nm,$

- 3)  $W = 30nm \times 10 \text{ fingers}, L = 30nm.$

Figure 2.4 Up: Example of two finger representation of a multifinger structure of a  $\Omega$ -Gate FD-SOI nanowire transistor (N14 device) Down: top view of a multi-finger (10 fingers) structure W= 30nm x 10 fingers.

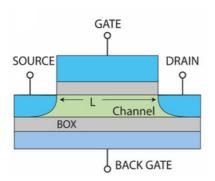

The FD-SOI  $\Omega$ -Gate nanowire can be represented as a planar transistor, as illustrated in Figure 2.5, the channel, where electrons flow from the source to the drain, is enclosed by the gate and dielectric.

Figure 2.5 Planar representation of the FD-SOI  $\Omega$ -Gate transistor N14.

The most used sample in the experiments completed in this chapter are the device with the following dimensions  $W = 30nm \times 10$  fingers and L = 20nm. The multi-finger structure is a characteristic of the GAA nanowires that allows an increase in current drive and optimize area [73]. In Table 2.2 the 'Snow' wafer map shows many more devices, but the choice of this sample was with this channel length the results obtained were better. As a result, the observation of the aging phenomenon characteristics was clearer.

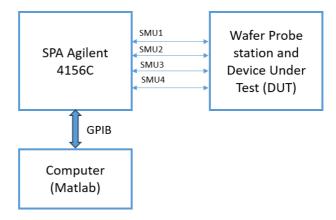

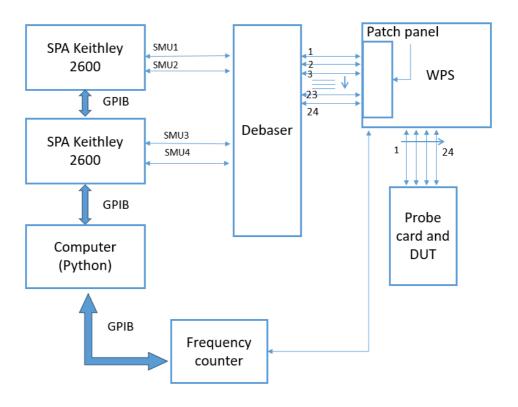

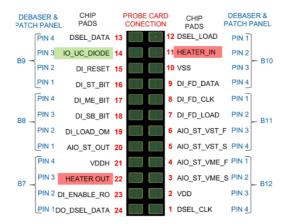

# 2.2 Characterization setup

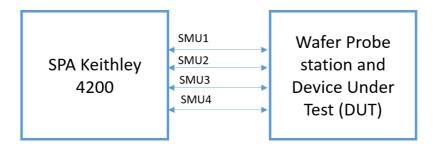

The basic equipment used is composed by a wafer probe station (WPS) and a semiconductor parameter analyzer (SPA) that will be explained in the next paragraphs.

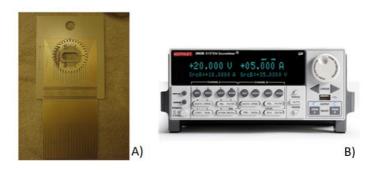

#### Wafer probe station

The experimental process began with the placement of the wafer under study in the chuck of the wafer probe station (WPS). Once positioned, the device under test (DUT) is selected using a microscope. Each of the WPS's positioners has a needle that connects the source monitor units (SMUs) of the SPA, to the four terminals of the transistor: source, drain, bulk, and back gate. The WPS used in the experiments of this thesis is enclosed in a Faraday cage that avoids the effect of external electric fields.

## Semiconductor parameter analyzer

The WPS is connected to a Semiconductor Parameter Analyzer (SPA) that applies voltage/current and measures current/voltage responses of the device. In this chapter the SPA utilized is the Keithley 4200A-SCS that contains 4 source monitor units (SMUs) capable of applying voltage and measure current and vice versa. The SPA is equipped with the Keithley interactive test environment (KITE) software.

#### Characterization setup for aging experiments

In this setup, the SMUs of the SPA are connected to the wafer probe station (WPS), which links the positioners to contact the device under test (DUT). The SPA is controlled through commercial software included in the equipment. Figure 2.6 illustrates the block diagram of the first measurement setup used for aging tests.

Figure 2.6 Block diagram of the first measurement setup used for the aging experiments. SPA connected in transmission and reception with WPS.

#### 2.2.1 Characterization of transistor parameters

The measurement-stress-measurement (MSM) methodology is the most used for assessing the degradation caused by aging mechanisms in transistor parameters. This technique involves first measuring the characteristics of a device before applying stress, secondly, apply the stress, and finally measure again the device characteristics after the stress has been removed.

To enhance the effects observed during the aging process, during the stress  $V_G$  or  $V_D$  values are larger than the nominal voltage operation of the technology. This is called accelerated stress conditions. An additional parameter that can be adjusted is the duration of stress, which can be increased exponentially, for instance 1s, 10s, 100s, 1000s based on the requirements of the research. During both the pre-stress and post-stress periods, the characteristics of the transistor are compared to assess the device's degradation.

Following the MSM method, characterization procedure for the aging measurements presented in this chapter involved the following steps:

- 1) Characterizing the parameters of the transistor in a 'fresh' sample.

- 2) Performing a stress test to analyze HCI, BTI, or OSS, applying stress voltages of different durations.

- 3) After each stress test, the transistor's characteristics were assessed to measure the degradation associated with the aging mechanism.

# 2.3 Measurement procedure

In Figure 2.7 an example of the methodology followed in this thesis is shown. First, a measurement of the transistor characteristics  $I_G - V_G$ ,  $I_D - V_G$ ,  $I_D - V_D$  when the transistor is 'fresh' that is before stress application. Second, stress voltages are applied to the device. Finally, a post stress characterization of the device characteristics  $I_G - V_G$ ,  $I_D - V_G$ ,  $I_D - V_D$  that measures the effects of degradation. The second and third steps can be repeated successively to analyze the effect of the application of several stress intervals.

Figure 2.7 Example of the methodology sequence used in most of the experiments performed in this thesis.

Nevertheless, the MSM technique suffers from drawbacks, including the loss of precise data. This loss is particularly evident when stress is released, and some failure mechanisms show recovery during this period.

In the next paragraphs, the different stress voltage configurations will be shown. They will be presented according to the aging mechanism being tested.

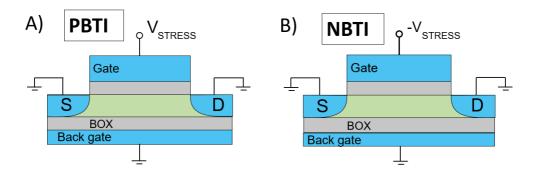

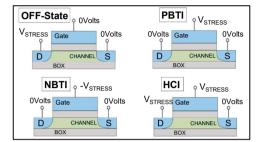

### **Negative/Positive Bias temperature instabilities:**

In the characterization of Bias Temperature Instability (BTI), we systematically analyzed both negative and positive biasing conditions. To study PBTI, a stress voltage of 2.4 volts (negative for the case of NBTI) was applied to the gate terminal, while the source, drain, and back gate terminals were maintained at ground potential. This experimental setup is depicted in Figure 2.8, which illustrates the configuration of the terminals during the testing process.

Figure 2.8 Biasing configuration to perform experiments of A) PBTI and B) NBTI.

#### **Hot Carrier Injection HCI:**

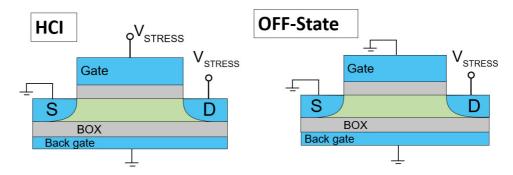

In the context of Hot Carrier Injection (HCI), we focused on the most detrimental stress scenario for short-channel devices, specifically where the gate voltage  $V_G$  equals the drain voltage  $V_D$  (i.e.  $V_G = V_D$ ). In this situation, a stress voltage of 2.4V was applied at the same time to both the gate and drain terminals, as depicted in Figure 2.9 left. Meanwhile, the source terminal and the back gate were kept grounded to ensure a controlled environment for the stress testing. This configuration allows for a comprehensive analysis of the device's performance and reliability under more degraded conditions.

## Off-state stress (OSS):

During the OFF-state tests, stress voltage was applied specifically to the drain terminal  $V_D$ , with all other electrodes maintained at ground potential to ensure accurate measurements, as depicted in Figure 2.9 right. The stress voltage was systematically varied within the range of 1.7 V to 2.5 V to thoroughly investigate how the different voltage levels influenced the degradation occurring in the OFF state. This approach allowed for a comprehensive analysis of voltage dependence on the performance of the device.

Figure 2.9 Biasing configuration to perform experiments of LEFT) HCI. RIGHT) OFF-state stress.

This setup focused on device-level characterization. The device under test (DUT) features four terminals, thereby requiring the utilization of four Source Measure Units (SMUs) to independently bias and measure each terminal.

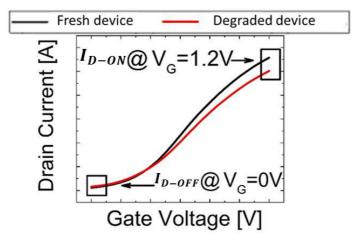

Within the MSM technique, one method for assessing the degradation of the subthreshold slope (SS) is to compare the  $I_D - V_G$  characteristics at  $V_G = 0V(I_{D-OFF})$  and  $V_G = 1.2V(I_{D-ON})$ .

The characteristics  $I_{D-ON}$  and  $I_{D-OFF}$  will be useful to measure degradation caused by aging. They are illustrated in Figure 2.10.  $I_{D-ON}$  is the drain current when the gate voltage is 1.2V 'on-state' and  $I_{D-OFF}$  is the drain current when the gate voltage is 0V 'off-state' as represented inside the black boxes in Figure 2.10. In this figure, the fresh  $I_D - V_G$  of a device is represented in black and the  $I_D - V_G$  characteristic of a degraded device in

red. The difference between  $I_{D-ON}$  and the  $I_{D-OFF}$  of the fresh device and the degraded device, is a measure of degradation.

This method is particularly important in situations where significant distortion in the  $I_D$  –  $V_G$  characteristics makes the threshold voltage and mobility unreliable parameters for assessing device degradation.

Figure 2.10 Representation of  $I_{D-ON}$  and  $I_{D-OFF}$  in a  $I_D-V_G$  characteristic of the transistor. Black fresh device and red degraded device are represented.

## 2.4 Experimental Results

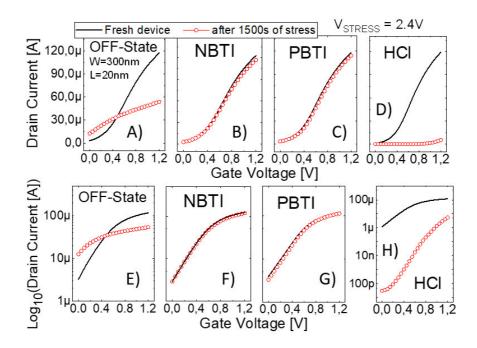

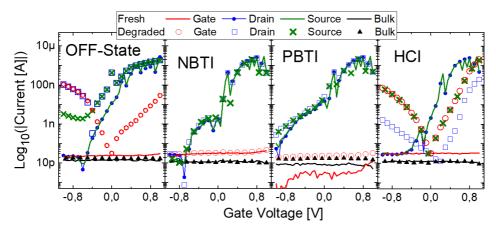

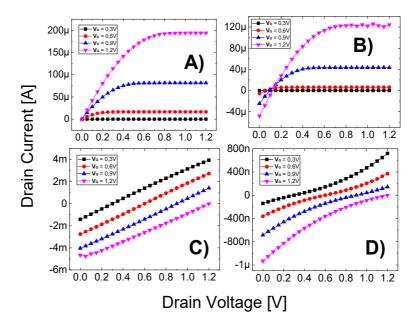

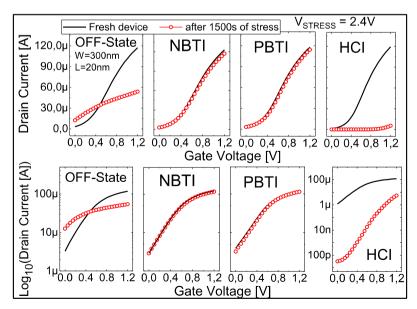

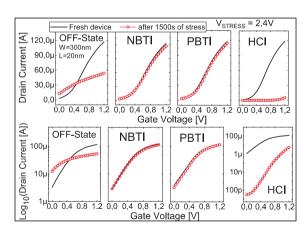

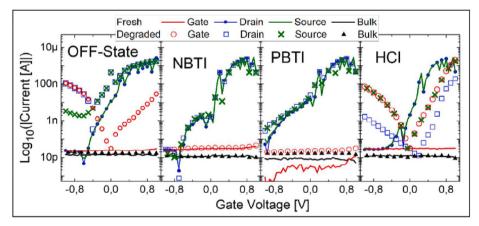

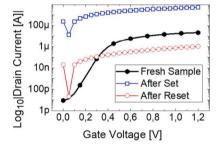

This section presents the experimental results derived from the characterization setup depicted in Figure 2.6. First, a comparison of the principal aging mechanisms is presented in Figure 2.11. The  $I_D - V_G$  characteristics of the fresh device (before stress) are represented with black line, while the  $I_D - V_G$  characteristics after 1500 seconds of stress are represented with red circles.

These characteristics were obtained at  $V_{DS} = 50mV$ . This figure presents the results of experiments conducted on devices with a width of W = 300nm and a length of L = 20nm. Represented from left to right: OFF-state stress (OSS), NBTI, PBTI and HCI stresses at 2.4 V in linear scale (top) and log scale (bottom).

Figure 2.11  $I_D - V_G$  curves ( $V_{DS} = 50 \text{ mV}$ ) of the fresh device (black line) and after 1500 s of 2.4 V stress (red circles). Linear (top) and logarithmic (bottom) plots are shown.

For the fresh devices (black line in Figure 2.11), short channel effects (SCE) are evidenced by the large drain current  $(I_D)$  in the subthreshold region and the small threshold voltage ( $\sim 0.25V$ ) as depicted in Figure 2.11 A) and E). Regarding the PBTI and NBTI stresses, no significant changes on the  $I_D - V_G$  curves can be appreciated after the stress beyond a small reduction of  $I_{D-ON}$  (i.e., current at  $V_G = 1.2V$ ).

However, for HCI and OFF-State tests, the consequences of the stress are clearly observed. For HCI stress, there is a large increase of the threshold voltage ( $\sim 1 V$ ) and the mobility is strongly reduced as depicted in Figure 2.11 D) and H). Therefore, the damage that  $I_{D-ON}$  experiences ( $\sim 90\%$  reduction) is very detrimental (the largest, when compared to the other stress cases).

For OSS note that, though the  $I_D - V_G$  characteristic is largely modified (Figure 2.11 A in red dots), the  $I_{D-ON}$  decrease is smaller (~50%). However, in this case the subthreshold current increases significantly and the  $I_D - V_G$  characteristic is completely distorted as depicted in Figure 2.11 A) and E), being not possible to clearly identify the subthreshold region.  $I_D$  exhibits an almost linear dependence on  $V_G$  for large stress voltages, what means a large degradation of the device performance.

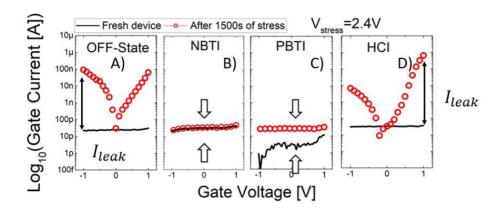

In Figure 2.12, a comparison of the  $I_G - V_G$  characteristics is presented. These characteristics were obtained immediately after acquiring the  $I_D - V_G$  curve. The analysis displays a logarithmic scale for the OFF-state stress (OSS), Negative Bias Temperature

Instability (NBTI), Positive Bias Temperature Instability (PBTI), and Hot Carrier Injection (HCI), arranged from left to right. As shown in Figure 2.12, the fresh devices are represented in black, while the stressed devices are marked with red circles.

As previously mentioned, both the OSS and HCI are particularly damaging to the dielectric's isolation properties (see Figure 2.12 A and D). This is evident from the significant leakage associated with these two mechanisms. In the OFF-state graphic shown in Figure 2.12 A), the leakage current is approximately  $\sim 0.1 \mu A$  at -1V. In contrast, it appears that the dielectric is not significantly affected by NBTI and PBTI, as depicted in Figure 2.12 B) and C).

Figure 2.12  $I_G - V_G$  curves of the fresh device (black line) and after 1500 s of 2.4 V stress (red circles). For A) OSS. B) NBTI. C) PBTI. D) HCI

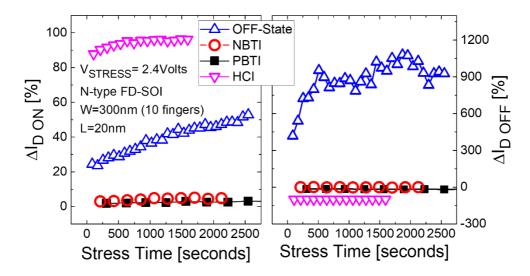

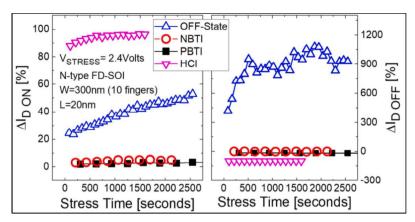

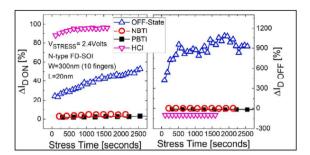

A more detailed comparison of the impact of the different kinds of stresses on the device properties has been made. Figure 2.13 shows the relative  $I_{D-ON}$  and  $I_{D-OFF}$  reduction suffered after OFF-State (blue triangles), PBTI (black squares), NBTI (red circles) and HCI (pink triangles) stresses as a function of stress time. As observed in Figure 2.13, negative and positive BTI produce the smallest variations on  $I_{D-ON}$  (<7% after 2000 s).

On the other hand, HCI provokes the largest reduction of  $I_{D-ON}$ , mostly induced within the first 100s of the stress (pink triangles in Figure 2.13 left), indicating that, in this technology, HCI is extremely harmful. Finally, for the OFF-State stress,  $I_{D-ON}$  shift suffers a fast increase at the beginning of the stress and then evolves smoothly with the stress time from ~20% (after the first inspection at 80 s) to ~50% after 2500 s (blue triangles in Figure 2.13 left), also exhibiting a saturation effect for larger stress times. Concerning  $I_{D-OFF}$ , there is no change for N/PBTI and it largely decreases for the HCI stresses (~100%) in comparison with the  $I_{D-ON}$ , but a huge increase is observed for the OFF-State case (~1000%, i.e., 10 times with respect the fresh  $I_{D-OFF}$  blue triangles in Figure 2.13 right).

Figure 2.13 Absolute value of the relative  $I_{D-ON}$  (left) and  $I_{D-OFF}$  (right) variations for an OFF-State (blue triangles), PBTI (black squares), NBTI (red circles) and HCI (pink triangles) stress at 2.4 V, as a function of the stress time.

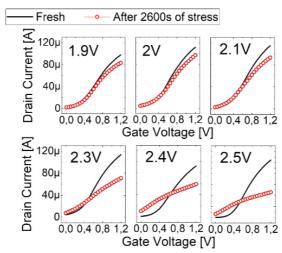

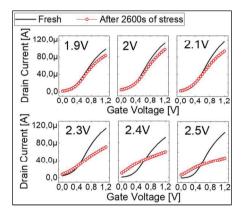

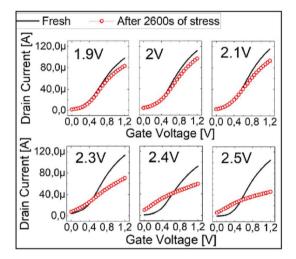

To get more insight into the OFF-state stress (OSS) aging mechanism, its voltage and time dependences have been evaluated. Figure 2.14 shows some examples of the  $I_D - V_G$  curves measured after 2600 s of stress for 1.9V, 2V, 2.1V, 2.3V, 2.4V and 2.5V together with the fresh  $I_D - V_G$  curves. Note that, for all the stress voltages,  $I_{D-ON}$  decreases with respect to the fresh value, measuring larger reductions for larger stress voltages.

On the other hand,  $I_{D-OFF}$  and the subthreshold slope (SS) increases with stress voltage, though the observed  $I_{D-OFF}$  degradation is very small for the lowest stress voltages (1.9 V to 2.1 V). These changes are critical for the largest stress voltages (>2.3 V), since the combination of both degradations,  $I_{D-ON}$  decrease and  $I_{D-OFF}$  increase, extremely distorts the  $I_D - V_G$  characteristic, as previously highlighted in Figure 2.14.

Figure 2.14  $I_D - V_G$  curves ( $V_{DS}$ =50mV) value of the fresh device (black line) and after 2600s of OSS (red circles) at 1.9 V, 2 V, 2.1 V, 2.3 V, 2.4 V, 2.5 V.

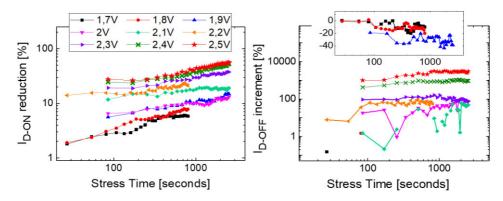

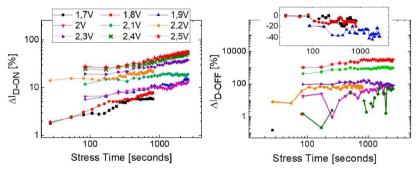

In Chapter 1, the temporal evolution of degradation resulting from various aging mechanisms affecting transistors was introduced. This degradation is typically characterized by a steady decline in key parameters of the transistor. A power law model is often adhered to, indicating that when these changes are plotted on a double logarithmic graph, a straight line is formed by the data points. This characteristic is illustrated in Figure 2.15, where the predictable nature of degradation over time is demonstrated.

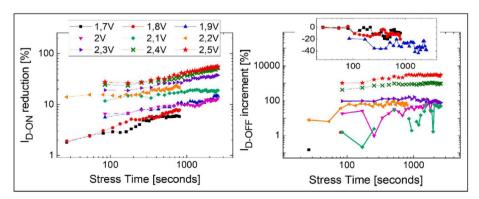

The temporal evolution of  $I_{D-ON}$  and  $I_{D-OFF}$  variations as parameters to quantify degradation, together with the voltage dependences, for the case of the OSS degradation are analyzed in Figure 2.15. For  $I_{D-ON}$  (left), as expected, the larger the stress conditions (voltage and time), the larger the  $I_{D-ON}$  degradation, reaching a 60% reduction after 2600 s at 2.5 V.

On the other hand, for  $I_{D-OFF}$  (right), only for large enough stress voltages (~2V), an increase of this parameter is observed following the power law. For the lowest stress voltages such as 1,7V, 1,8V and 1,9V  $I_{D-OFF}$  decreases with stress time, as can be seen in the subfigure of Figure 2.15 (right), reaching a ~40% reduction for 1.9 V at the end of the test. However,  $I_{D-OFF}$  is 30 times the fresh value, for the stress at 2.5 V. All these results indicate that the OFF-state stress modifies the subthreshold and ON operation regions of the device, by increasing the leakage current through the channel and reducing the ON current  $I_{D-ON}$ , largely affecting the device performance, as observed in Figure 2.15.

Figure 2.15. Relative  $I_{D-ON}$  reduction (left) and  $I_{D-OFF}$  increment (right) as a function of the stress time for OFF-State stresses at  $V_D$  ranging from 1.7V to 2.5V.

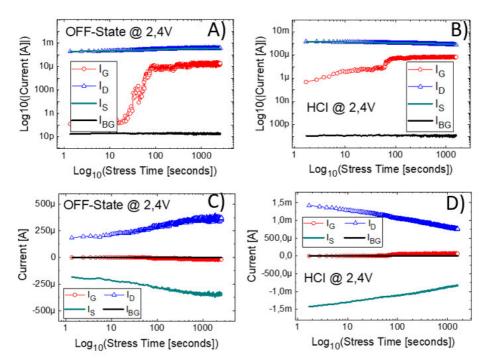

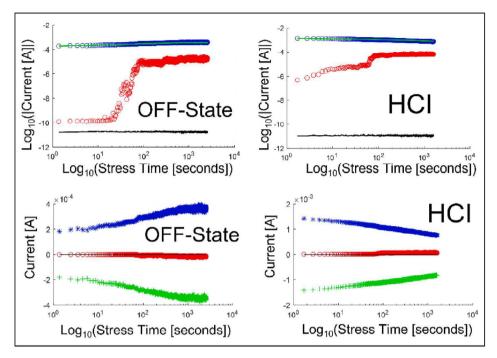

For a better understanding of the effects of each of the aging mechanisms, the currents through the four terminals of the device (gate, drain, source and back gate) during HCI and OSS stresses have been analyzed. Figure 2.16 depicts the  $I_D(\text{blue})$ ,  $I_G(\text{red})$ ,  $I_S(\text{green})$  and  $I_{BG}(\text{black})$  currents measured during the stress phase of the MSM tests at 2,4V in logarithmic scale for the current and for the time on top of the figure, and linear/logarithmic plot on the bottom.

$I_{BG}$  current shows no relevant change during the test, that means that the buried oxide (BOX) damage can be neglected. For the case of drain terminal current  $I_D$  and source terminal current  $I_S$ , which have the same magnitude but opposite sign, are larger in the case of the HCI stresses. Moreover, the temporal trend of the currents (see Figure 2.16) for the two stresses is opposite: whereas they smoothly increase in Figure 2.16 A and C (in absolute value) with time for the OFF-state stress, they decrease for the HCI case (Figure 2.16 B and D). Surprisingly, when compared to the fresh device, there is a large increase of the gate current after both kinds of tests. Though at the end of both tests the magnitude of  $I_G$  is similar, the temporal evolution differs. For the OSS,  $I_G$  remains small until the stress time is large enough (approximately 20 s in the example shown), and then it increases smoothly until a relatively constant value.

In the case of the HCI tests (see Figure 2.16 B and D), however, a large increase is observed at very short stress times and evolves with a similar trend as in the case of the OFF-state until the final value. Despite the different temporal trends, the increase of  $I_G$  suggests a significant degradation of the gate dielectric in the two cases.

Figure 2.16.  $I_D$  (blue),  $I_G$  (red),  $I_S$  (green) and  $I_{BG}$  (black) currents registered during the stress phase of the OFF-State (left A and C) and HCI (right B and D) tests at 2.4 V. Top figures show the absolute value of the currents in a log scale; bottom figures those currents in linear scale (with their sign).

To understand better the electric fields and currents that operate within the transistor, particularly in relation to aging mechanisms during the stress biasing phase, a detailed schematic of these various fields is presented in Figure 2.17. During negative/positive bias temperature instability N/PBTI stress tests, a uniform distribution of the electric field within the device is exhibited along the channel (see Figure 2.17 A and B), indicating a consistent interaction across its length.

In contrast, noticeable asymmetry in the electric field is observed during the OFF-state (OSS) and hot carrier injection (HCI) tests as represented in red arrows in Figure 2.17 C and D). Furthermore, an inversion channel is established during positive bias temperature instability (PBTI) and HCI testing depicted in green in Figure 2.17 B and D, allowing for a distinct current flow that alters the behavior of the device. It is important to note that substantial ON currents can be cross through the channel during HCI stress testing represented in a purple arrow from drain terminal to source terminal.

Although no channel has been created during the OSS stresses, large leakage current between drain and source are measured due to the lateral electric field applied, which is represented with red arrows in Figure 2.17.

Figure 2.17. Schematic representation of the sign and magnitude of the electric field applied to the dielectric. The inversion channel created during PBTI and HCI tests is depicted in green. The large channel current that can flow during the HCI stresses is represented by the purple arrow from drain to source.