This is the **published version** of the bachelor thesis:

Cano Carabaca, Santi; Paco Sánchez, Pedro Antonio de, dir. Diseño, construcción y medida de un amplificador de bajo ruido con tecnología SiGe. 2022. 93 pag. (956 Grau en Enginyeria de Sistemes de Telecomunicació)

This version is available at https://ddd.uab.cat/record/266885

under the terms of the [G] BY-SA license

## UAB

Trabajo de Fin de Grado

GRADO EN INGENIERÍA DE SISTEMAS DE TELECOMUNICACIÓN

## Diseño, Construcción y Medida de un Amplificador de Bajo Ruido con Tecnología SiGe

Santi Cano Carabaca

DIRECTOR: Pedro de Paco

DEPARTAMENTO DE TELECOMUNICACIÓN Y INGENIERÍA DE SISTEMAS

UNIVERSIDAD AUTÓNOMA DE BARCELONA

Bellaterra, Julio 4, 2022

## Abstract

This work explains the process that has been followed to design, build and measure a low noise amplifier that offers a gain of 35 dB and a minimum noise figure at a working frequency of 7.5 GHz.

The first step in the design of any amplifier is the study of the characteristics of the transistor. In this work, SiGe technology will be chosen due to its low consumption. Then the electrical model of the adaptation and polarization networks will be made using Aglient's ADS program and then its Momentum tool will be used to calculate the electromagnetic fields generated by the copper tracks. In this way, the simulation results can be better approximated to the real behavior of the device. However, we will see that to achieve that 35dB of gain it is not enough to just use one stage, so the design of a 3-stage low noise amplifier will also be explained.

Finally, the construction process of the 1-stage and 3-stage designs and the steps to follow to correctly measure the resulting amplifiers will be explained.

## Resumen

En este trabajo se explica el proceso que se ha seguido para diseñar, construir y medir un amplificador de bajo ruido que ofrezca una ganancia de 35 dB y una figura de ruido mínima a una frecuencia de trabajo de 7,5 GHz .

El primer paso en el diseño de cualquier amplificador es el estudio de las características del transistor. En este trabajo se optará por usar tecnología SiGe debido a su bajo consumo. Luego se realizará el modelo eléctrico de las redes de adaptación y de polarización mediante el programa ADS de Aglient y a continuación se utilizará su herramienta Momentum para calcular los campos electromagnéticos generados por las pistas de cobre. De esta forma, se podrán aproximar mejor los resultados de la simulación al comportamiento real del dispositivo. Sin embargo, veremos que para conseguir esos 35dB de ganancia no es suficiente con solo usar una etapa, por lo que también se explicará el diseño de un amplificador de bajo ruido de 3 etapas.

Finalmente, se explicará el proceso de construcción de los diseños de 1 y de 3 etapas y los pasos a seguir para medir correctamente los amplificadores resultantes.

# Índice general

| <b>A</b> l | bstra | ct                                                             | 1  |

|------------|-------|----------------------------------------------------------------|----|

| R          | esum  | en                                                             | 11 |

| Li         | stado | o de Figuras                                                   | IX |

| Li         | stado | o de Tablas                                                    | х  |

| 1.         | Intr  | roducción                                                      | 1  |

|            | 1.1.  | Motivación y Objetivos                                         | 1  |

| 2.         | Car   | acterísticas de los transistores                               | 3  |

|            | 2.1.  | Característica I-V: Punto de polarización                      | 4  |

|            |       | 2.1.1. Elección del punto de polarización óptimo               | 6  |

|            |       | 2.1.2. Influencia de la frecuencia en el punto de polarización | 9  |

|            | 2.2.  | Parámetros de Scattering                                       | 10 |

|            | 2.3.  | Figura de ruido mínima y ganancia máxima                       | 13 |

|            | 2.4.  | Frecuencia de corte                                            | 15 |

|            | 2.5.  | Estabilidad                                                    | 15 |

|            | 2.6.  | Círculos de ganancia y figura de ruido                         | 18 |

|            |       | 2.6.1. Análisis teórico de los círculos de ganancia            | 18 |

|            |       | 2.6.2. Análisis teórico de los círculos de figura de ruido     | 20 |

|            |       | 2.6.3. Simulación de los círculos de ganancia y ruido          | 21 |

|            | 2.7.  | DC-Block Y DC-Feed                                             | 23 |

Índice general IV

| 3.        | Diseño del LNA de 1 etapa |         |                                                                                  |    |  |  |  |

|-----------|---------------------------|---------|----------------------------------------------------------------------------------|----|--|--|--|

|           | 3.1.                      | Model   | o eléctrico ideal                                                                | 25 |  |  |  |

|           | 3.2.                      | Model   | o eléctrico real                                                                 | 28 |  |  |  |

|           |                           | 3.2.1.  | Elección del sustrato                                                            | 29 |  |  |  |

|           |                           | 3.2.2.  | Capacidades y resistencias reales                                                | 29 |  |  |  |

|           |                           | 3.2.3.  | Redes de polarización                                                            | 31 |  |  |  |

|           |                           | 3.2.4.  | Redes de adaptación y estabilización                                             | 33 |  |  |  |

|           | 3.3.                      | Model   | o electromagnético: Diseño del Layout                                            | 36 |  |  |  |

|           |                           | 3.3.1.  | Layout de la red de polarización                                                 | 37 |  |  |  |

|           |                           | 3.3.2.  | Layout de la red de adaptación                                                   | 39 |  |  |  |

|           |                           | 3.3.3.  | Layout de la unión de ambas redes                                                | 40 |  |  |  |

|           |                           | 3.3.4.  | Cavidades resonantes: la "carcasa" del amplificador $\ \ldots \ \ldots \ \ldots$ | 43 |  |  |  |

|           |                           | 3.3.5.  | Punto de compresión                                                              | 46 |  |  |  |

| 4.        | Con                       | strucc  | ión y resultados del LNA de 1 etapa                                              | 48 |  |  |  |

|           | 4.1.                      | Constr  | rucción del LNA de 1 etapa                                                       | 48 |  |  |  |

|           | 4.2.                      | Medid   | a de los parámetros S con el VNA                                                 | 50 |  |  |  |

|           |                           | 4.2.1.  | Calibración con el CALKIT                                                        | 50 |  |  |  |

|           |                           | 4.2.2.  | Resultados y comparación con la hipótesis                                        | 51 |  |  |  |

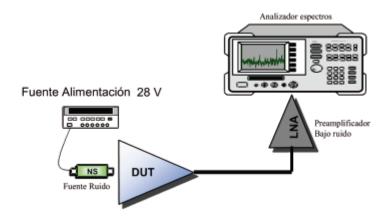

|           | 4.3.                      | Medid   | a del factor de ruido con el Analizador de Espectros                             | 55 |  |  |  |

|           |                           | 4.3.1.  | Método del Factor Y                                                              | 55 |  |  |  |

|           |                           | 4.3.2.  | Montaje y configuración del "Setup" para la medición del ruido                   | 56 |  |  |  |

|           |                           | 4.3.3.  | Resultados y comparación con la hipótesis                                        | 57 |  |  |  |

| <b>5.</b> | Dise                      | eño del | l LNA de 3 etapas                                                                | 60 |  |  |  |

|           | 5.1.                      | Model   | o eléctrico real                                                                 | 60 |  |  |  |

|           |                           | 5.1.1.  | Enlaces interetapas                                                              | 61 |  |  |  |

|           |                           | 5.1.2.  | Gain Flatness                                                                    | 61 |  |  |  |

|           |                           | 5.1.3.  | Amplificador LNA de 2 etapas                                                     | 62 |  |  |  |

|           |                           | 5.1.4.  | Amplificador LNA de 3 etapas                                                     | 63 |  |  |  |

Índice general V

|    | 5.2.  | Modelo  | electromagnético                                                                 | 64  |

|----|-------|---------|----------------------------------------------------------------------------------|-----|

|    |       | 5.2.1.  | Redes de adaptación                                                              | 64  |

|    |       | 5.2.2.  | Redes de polarización                                                            | 66  |

|    | 5.3.  | Depend  | lencia entre las distintas etapas de un amplificador y sus respectivas ganancias | 67  |

| 6. | Con   | clusion | es                                                                               | 71  |

|    | 6.1.  | Futuras | s líneas de investigación                                                        | 72  |

| Bi | bliog | rafía   |                                                                                  | I   |

| Α. | Cód   | igo Ma  | tlab                                                                             | III |

|    | A.1.  | Función | n Automatic_Measurement                                                          | III |

|    | A.2.  | Función | n SParametersPlot                                                                | V   |

|    | A.3.  | Función | a EtapasSeparadas                                                                | VII |

# Índice de figuras

| 2.1.  | Modelo no lineal PSPICE                                                                                | 5  |

|-------|--------------------------------------------------------------------------------------------------------|----|

| 2.2.  | Característica I-V Transistor BFR840L3RHESD                                                            | 5  |

| 2.3.  | DC current gain $h_{FE}=f(I_C), V_{CE}=1.8V$ BFR840L3RHESD transistor                                  | 6  |

| 2.4.  | Circuito PSPICE con los parameter sweep de $V_{CE}$ y $I_{C}$ transistor BFR840L3RHESD                 | 7  |

| 2.5.  | Cómo cambiar el tipo de barrido de linear a single point                                               | 7  |

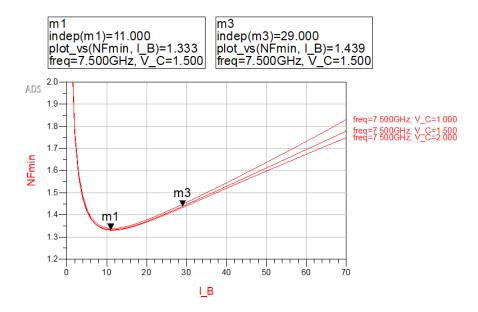

| 2.6.  | Dependencia de la figura de ruido respecto de $I_B$ en $\mu A$ y $V_{CE}$ en V                         | 8  |

| 2.7.  | Dependencia de la ganancia respecto de $I_B$ en $\mu A$ y $V_{CE}$ en V                                | 8  |

| 2.8.  | Dependencia de la figura de ruido respecto de $I_B$ en $\mu A$ y $V_{CE}$ en V y múltiples frecuencias | 9  |

| 2.9.  | Dependencia de la ganancia respecto de $I_B,V_{CE}$ y múltiples frecuencias                            | 9  |

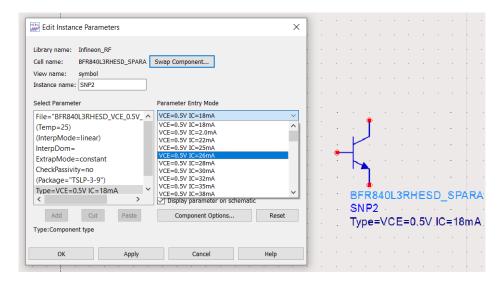

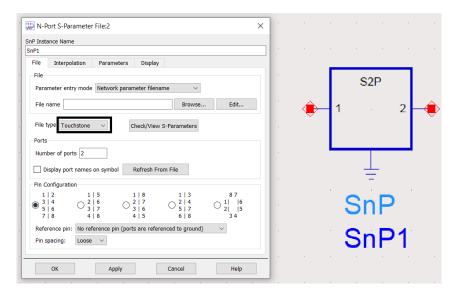

| 2.10. | Diferentes combinaciones $V_{CE}-I_C$ para el transistor SPARA                                         | 11 |

| 2.11. | Cómo seleccionar un archivo Touchstone haciendo uso del N-Port S-Parameter File                        | 11 |

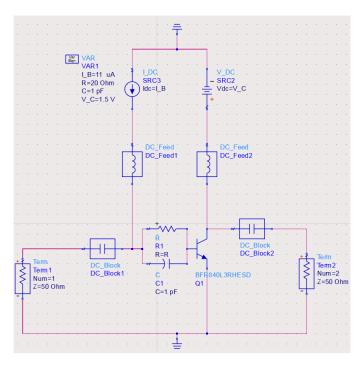

| 2.12. | Modelo no lineal PSPICE. Se ha incluido el $S$ -parameters                                             | 12 |

| 2.13. | Parámetros de Scattering del transistor BFR840L3RHESD. $V_{CE}=1,5V,~I_{C}=4mA$ y $I_{B}=11\mu A$      | 12 |

| 2.14. | Figura de ruido mínima y ganancia máxima con transistor BFR840L3RHESD                                  | 13 |

| 2.15. | Figura de ruido mínima y ganancia máxima con transistor BFR840L3RHESD SPARA                            | 14 |

| 2.16. | Factor de Rollett y $\mu-test$ transistor BFR840L3RHESD y BFR840L3RHESD SPARA                          | 16 |

| 2.17. | Círculos de estabilidad de fuente y de carga para transistor BFR840L3RHESD $$ .                        | 17 |

| 2.18. | Círculos de estabilidad de fuente y de carga para transistor BFR840L3RHESD SPARA                       | 17 |

| 2.19. | Red de dos puertas genérica con impedancia de fuente v carga arbitraria                                | 18 |

Listado de figuras

| 2.20. | Circuito general de un amplificador de una etapa                                                                                                                                                                                          | 20 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.21. | A la izquierda (a) círculos de ganancia de fuente y de figura de ruido. A la derecha (b) círculos de ganancia de carga y ganancia de potencia                                                                                             | 22 |

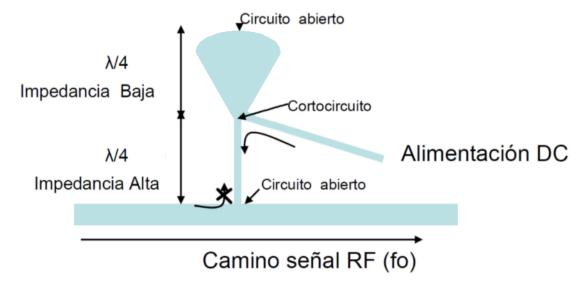

| 2.22. | DC-Feed con dos líneas de transmisión de $\lambda/4$ acabadas en forma de stub radial.                                                                                                                                                    | 23 |

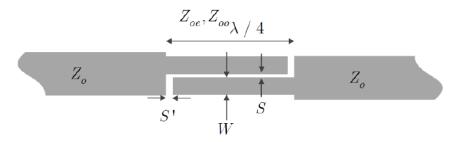

| 2.23. | Circuito de líneas acopladas con función DC-Block                                                                                                                                                                                         | 24 |

| 3.1.  | Modelo eléctrico de un amplificador de 1 etapa desadaptado                                                                                                                                                                                | 25 |

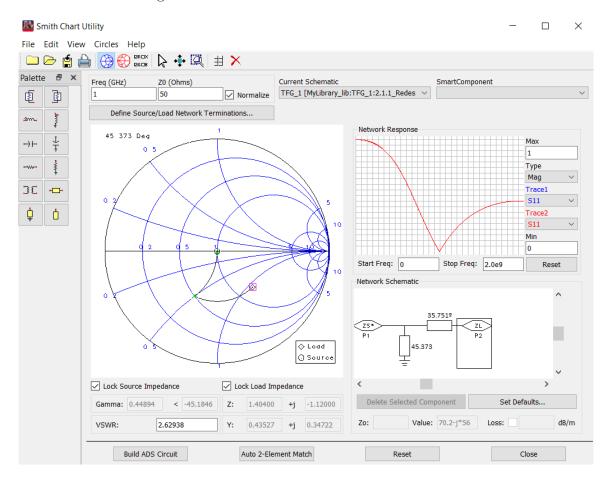

| 3.2.  | Herramienta Smith Chart para le red de adaptación de la entrada. Seleccionar el pin de la impedancia de carga y introducir el valor de impedancia <b>conjugada</b> que se quiere adaptar. En la impedancia de fuente se tienen $50\Omega$ | 26 |

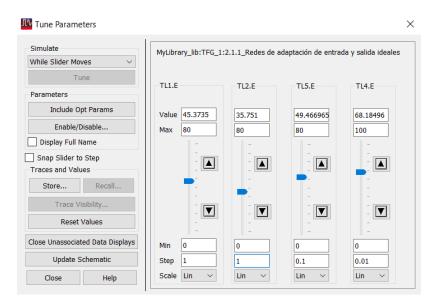

| 3.3.  | Herramienta de tunning con 4 barridos en longitud eléctrica (uno por cada elemento distribuido)                                                                                                                                           | 27 |

| 3.4.  | Matching Networks de entrada y de salida para la primera etapa de un modelo ideal                                                                                                                                                         | 27 |

| 3.5.  | Círculos de ganancia y figura de ruido adaptados                                                                                                                                                                                          | 28 |

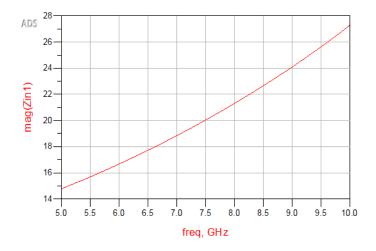

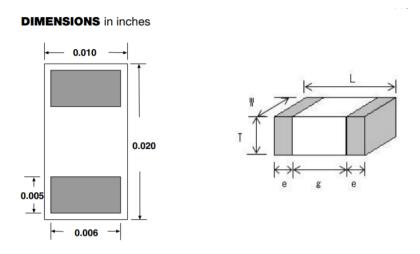

| 3.6.  | Representación de la capacitancia y del parámetro $S_{21}$ de la capacidad GRM0225C1CR70WA03 de Murata                                                                                                                                    | 30 |

| 3.7.  | Representación de la impedancia en función de la frecuencia para la resistencia SCPX_0705_D_19950814 de $10\Omega$                                                                                                                        | 30 |

| 3.8.  | Los parámetros $S(1,3)$ y $S(2,3)$ muestran el aislamiento de la entrada respecto de la alimentación y de la alimentación respecto del transistor respectivamente                                                                         | 31 |

| 3.9.  | Aislamiento de la red de polarización de entrada                                                                                                                                                                                          | 32 |

| 3.10. | Representación del modelo eléctrico de la red de polarización de entrada                                                                                                                                                                  | 32 |

| 3.11. | Redes de adaptación y estabilización para 1 etapa                                                                                                                                                                                         | 33 |

| 3.12. | Modelo eléctrico del amplificador de 1 etapa real $\dots \dots \dots \dots \dots \dots$                                                                                                                                                   | 34 |

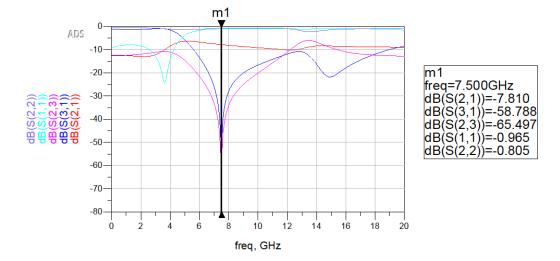

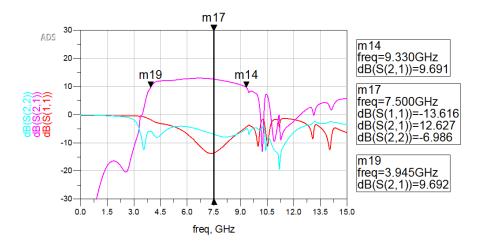

| 3.13. | Parámetros S del amplificador de 1 etapa real                                                                                                                                                                                             | 34 |

| 3.14. | Parámetros S del amplificador de 1 etapa real sin focos de inestabilidad $\dots$                                                                                                                                                          | 35 |

| 3.15. | Mejoras en el ancho de banda y en el aislamiento                                                                                                                                                                                          | 35 |

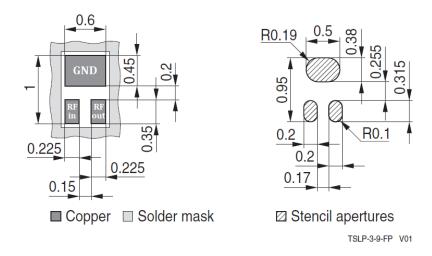

| 3.16. | Dimensiones del transistor BFR840L3RHESD [10] $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                                                                       | 37 |

| 3.17. | Ejemplo de la representación de las dimensiones de una resistencia (izquierda) y de una capacidad (derecha) en un Data Sheet                                                                                                              | 38 |

| 3.18. | Layout de la red de polarización de entrada                                                                                                                                                                                               | 38 |

Listado de figuras

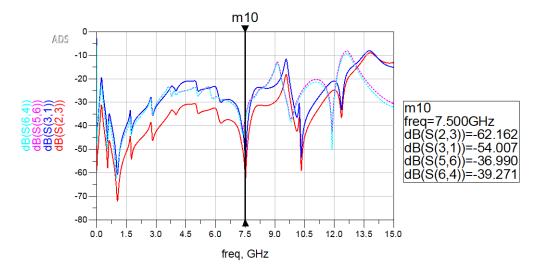

| 3.19. | Aislamiento de las simulaciones electromagnética (línea discontinua) y eléctrica (línea continua)                                                                                                             | 39 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.20. | Layout de las redes de adaptación                                                                                                                                                                             | 40 |

| 3.21. | Comparativa de los parámetros S y del ancho de banda del modelo eléctrico (línea continua) respecto del electromagnético (línea discontinua) de las redes de adaptación junto con el transistor y los DC-Feed | 40 |

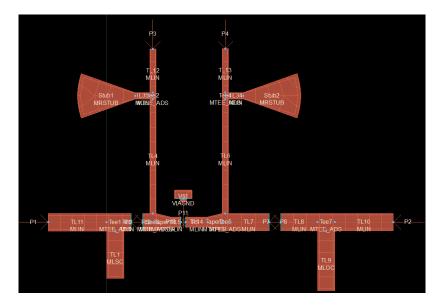

| 3.22. | Layout del amplificador de 1 etapa real                                                                                                                                                                       | 41 |

| 3.23. | Comparativa de los parámetros S y del ancho de banda del modelo eléctrico (línea continua) respecto del electromagnético (línea discontinua) del amplificador real de 1ª etapa                                | 41 |

| 3.24. | Layout del amplificador real de 1 etapa con agujeros y planos de masa añadidos .                                                                                                                              | 42 |

| 3.25. | Simulación de los parámetros de Scattering del modelo de prueba del amplificador                                                                                                                              | 42 |

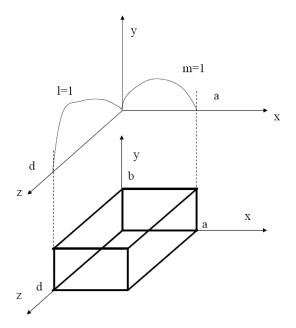

| 3.26. | Cavidad rectangular y diagrama de onda estacionaria en su interior                                                                                                                                            | 43 |

| 3.27. | Amplificador real de 1 etapa a construir                                                                                                                                                                      | 45 |

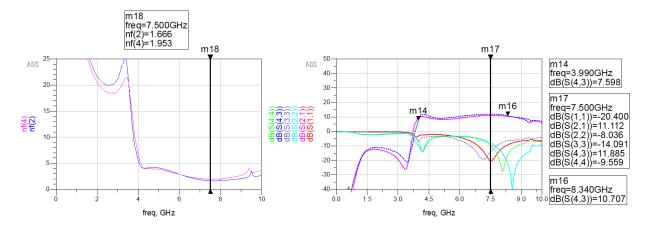

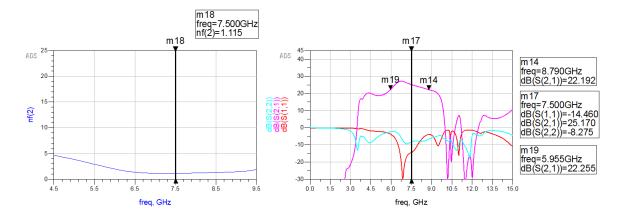

| 3.28. | Simulación eléctrica (línea continua) y electromagnética (línea discontinua) con el modelo SPARA del transistor                                                                                               | 45 |

| 3.29. | Simulación eléctrica (línea continua) y electromagnética (línea discontinua) con el modelo no lineal del transistor                                                                                           | 46 |

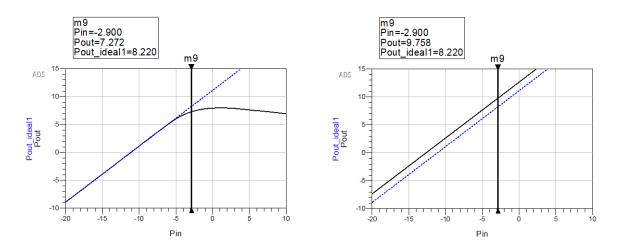

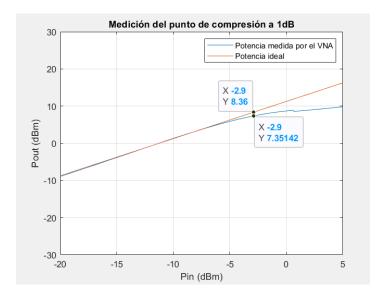

| 3.30. | Punto de compresión a 1 dB del amplificador simulado con el modelo no lineal del transistor (izquierda) y con el modelo SPARA del mismo (derecha)                                                             | 46 |

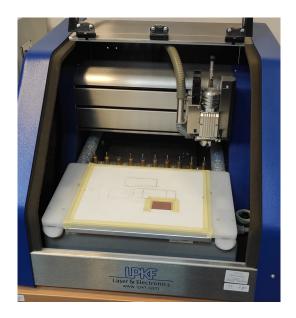

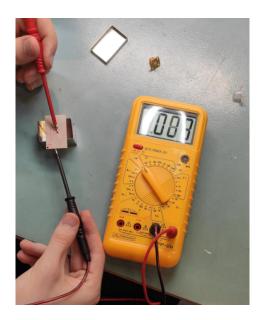

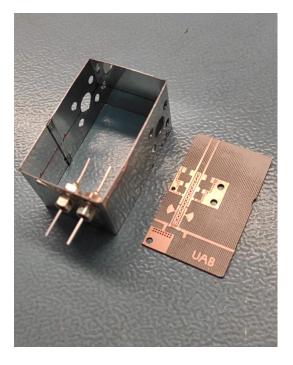

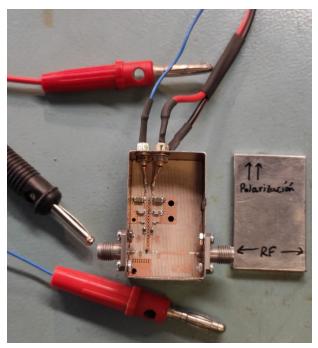

| 4.1.  | Construcción de las pistas con la fresadora (izquierda) y comprobación de circulación de corriente a través de los agujeros (derecha)                                                                         | 49 |

| 4.2.  | Proceso de construcción del amplificador                                                                                                                                                                      | 49 |

| 4.3.  | Proceso de calibración con el kit de calibración OSLT. En la imagen también se muestra el CALKIT eléctrico                                                                                                    | 51 |

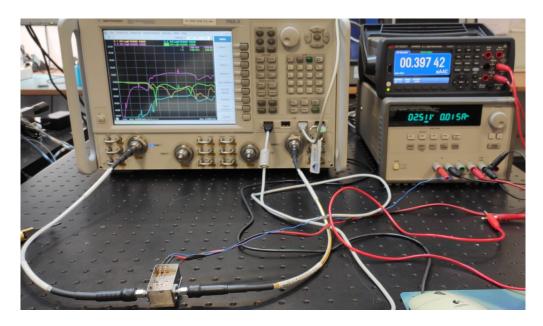

| 4.4.  | Montaje previo a la medición de los parámetros $S$ del amplificador $\ldots \ldots$                                                                                                                           | 52 |

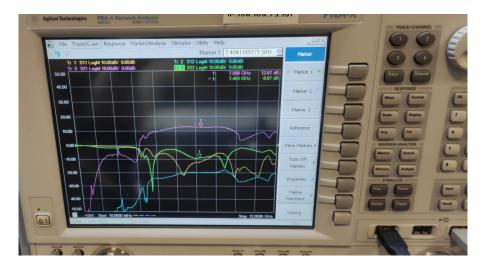

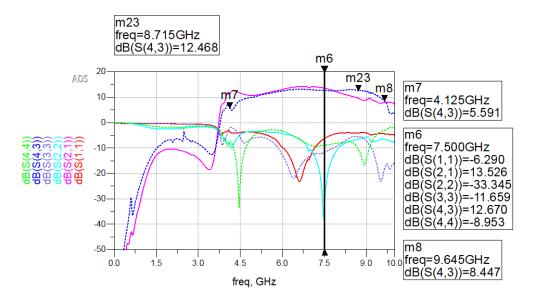

| 4.5.  | Resultados para el punto de polarización en el que mejor trabaja el amplificador: $V_C=2.5~{ m V}~{ m y}~V_B=0.85~{ m V}~{ m .}$                                                                              | 52 |

| 4.6.  | Comparación de los resultados obtenidos a través del VNA (línea continua) con la simulación electromagnética de la figura 3.28                                                                                | 53 |

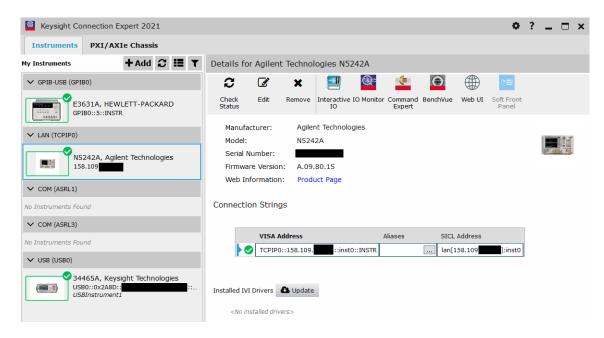

| 4.7.  | Dispositivos conectados al ordenador del laboratorio según el programa Keysight  Connection Expert                                                                                                            | 54 |

| 4.8.  | Medición en el VNA del punto de compresión a 1 dB                                                                                                                                                             | 55 |

Listado de figuras

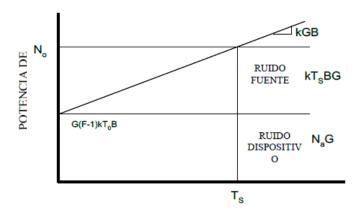

| 4.9.  | Relación lineal entre las potencias de ruido a la entrada y a la salida. [20] $$                                                                                                            | 55 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.10. | Setup para medir la figura de ruido con el método del factor Y [20]                                                                                                                         | 57 |

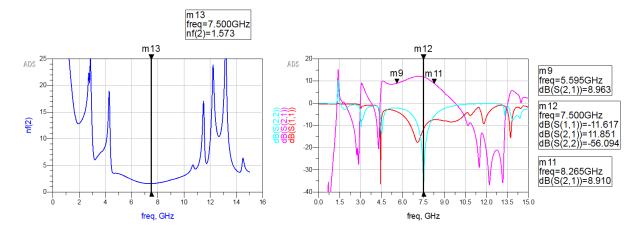

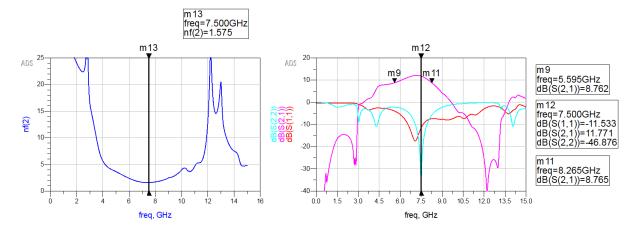

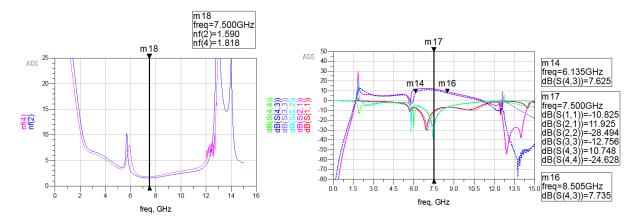

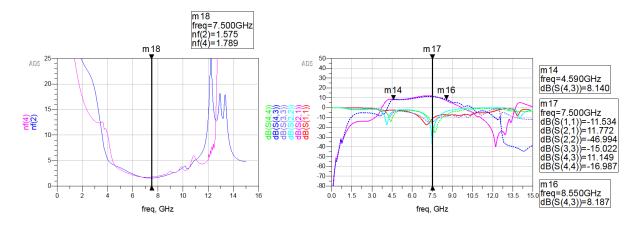

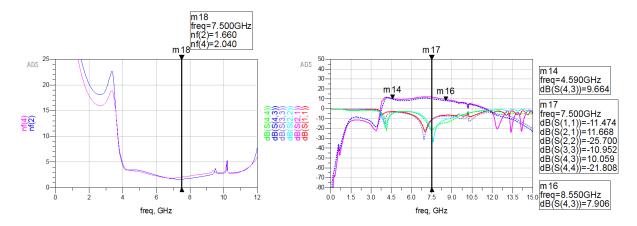

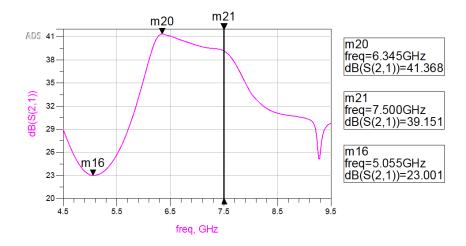

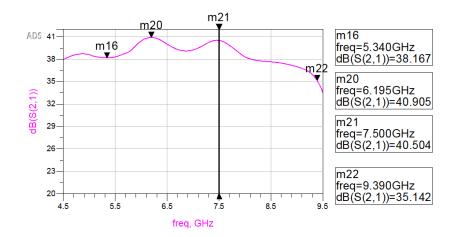

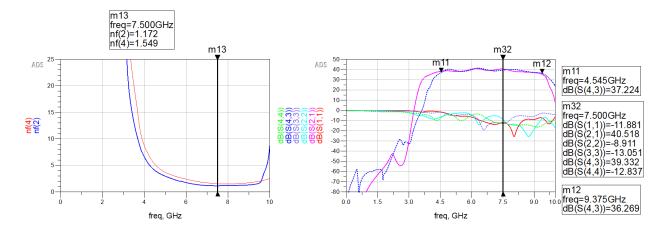

| 5.1.  | Gain flatness del LNA con las 3 etapas idénticas                                                                                                                                            | 62 |

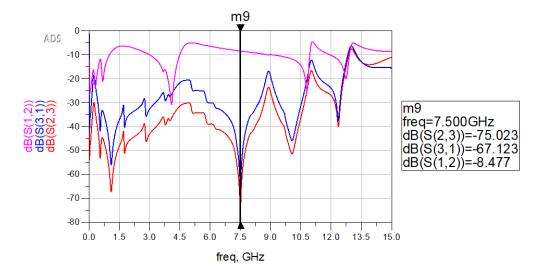

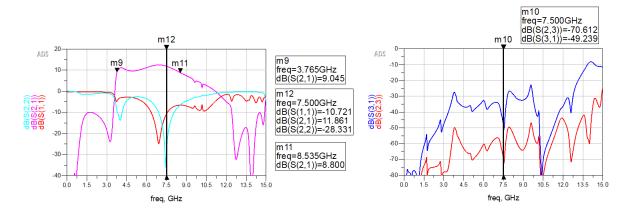

| 5.2.  | Parámetros S del modelo eléctrico de únicamente la segunda etapa. No se ha enlazado todavía la primera etapa                                                                                | 62 |

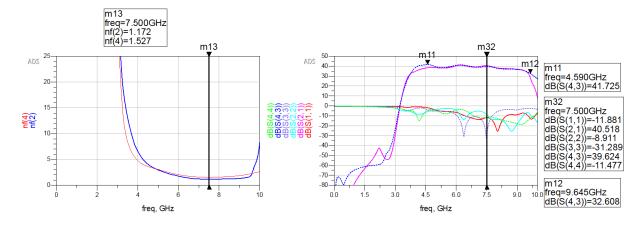

| 5.3.  | Figura de ruido y parámetros S del modelo eléctrico de la primera y segunda etapa enlazadas                                                                                                 | 63 |

| 5.4.  | Parámetros S del modelo eléctrico de únicamente la tercera etapa. No se han enlazado todavía las dos etapas anteriores                                                                      | 63 |

| 5.5.  | Figura de ruido y parámetros S del modelo eléctrico del LAN de 3 etapa enlazadas                                                                                                            | 64 |

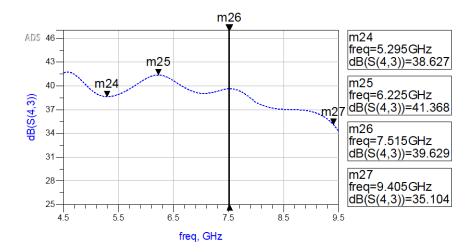

| 5.6.  | Gain flatness del LNA de 3 etapas de distintas adaptaciones                                                                                                                                 | 64 |

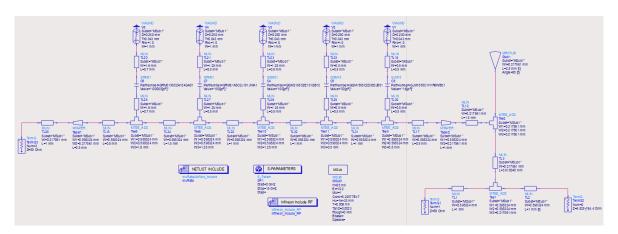

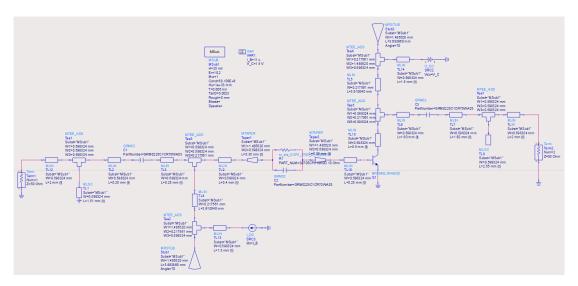

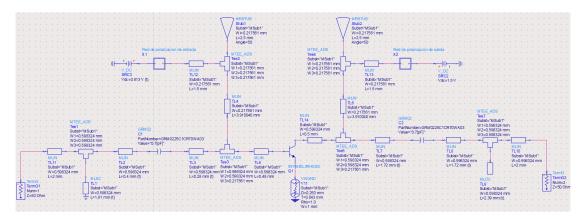

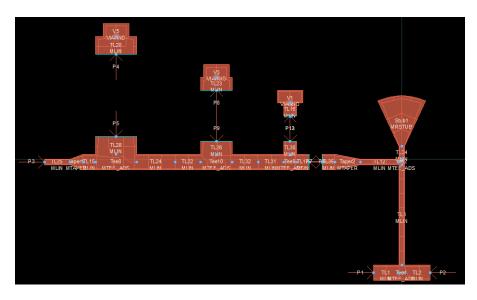

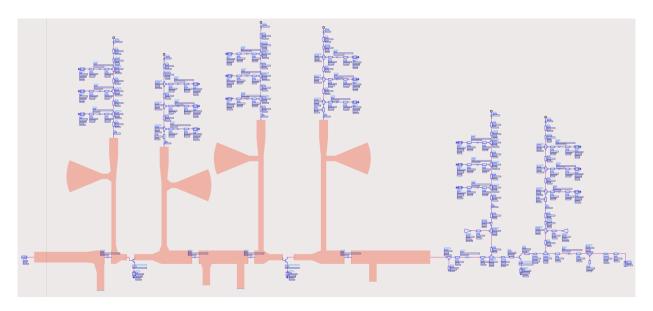

| 5.7.  | Representación de una parte del proceso de simulación electromagnética paso por paso                                                                                                        | 65 |

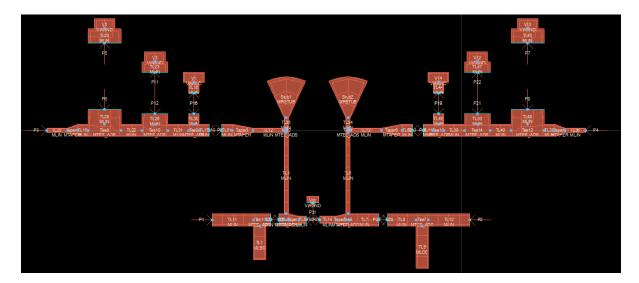

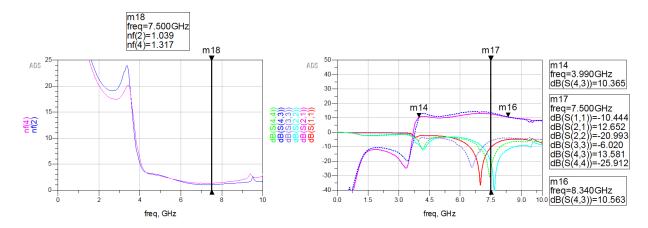

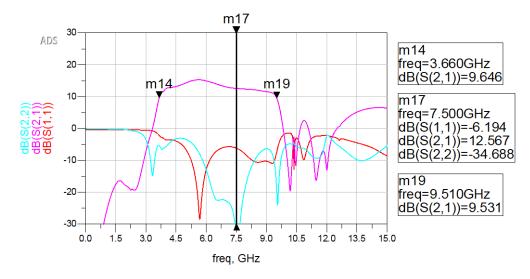

| 5.8.  | Simulación eléctrica (línea continua) y electromagnética (línea discontinua) de la red de adaptación del LNA de 3 etapas                                                                    | 65 |

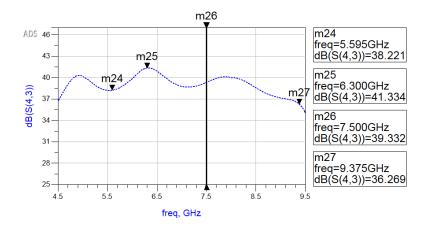

| 5.9.  | Gain flatness del modelo electromagnético de la red de adaptación del LNA de 3 etapas                                                                                                       | 66 |

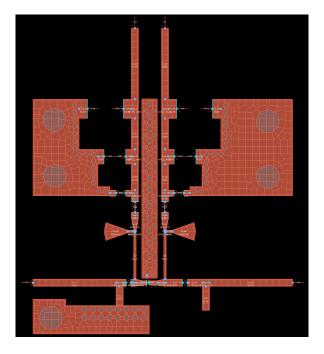

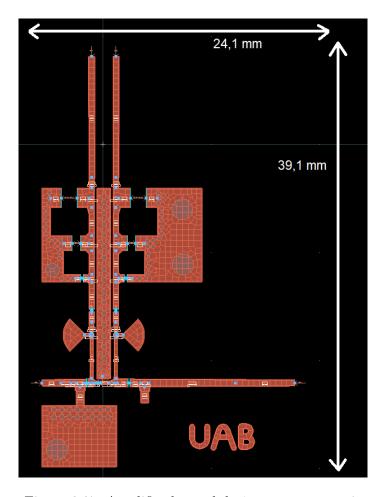

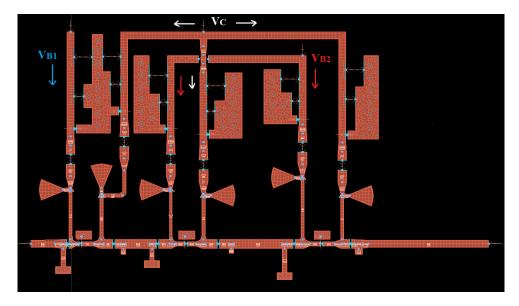

| 5.10. | Layout del LNA de 3 etapas                                                                                                                                                                  | 66 |

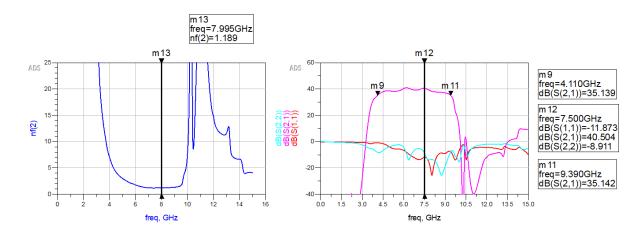

| 5.11. | Figura de ruido y parámetros S de la simulación electromagnética (línea discontinua) del LNA de 3 etapas                                                                                    | 67 |

| 5.12. | Gain Flatness del LNA de 3 etapas                                                                                                                                                           | 67 |

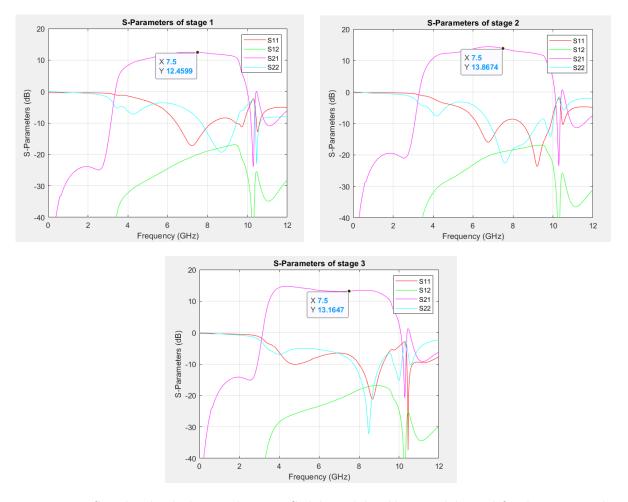

| 5.13. | Simulación de los parámetros S del modelo eléctrico del amplificador para cada etapa por separado                                                                                           | 68 |

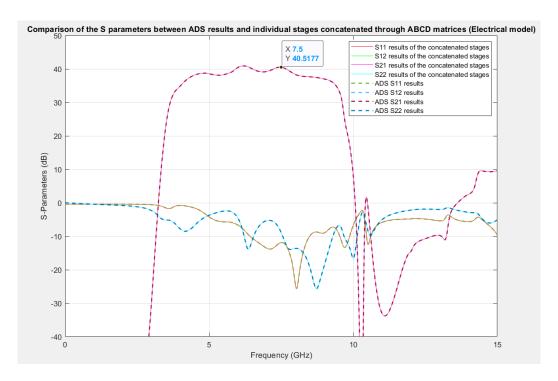

| 5.14. | Comparación de los parámetros S entre la simulación eléctrica del amplificador de 3 etapas y la concatenación de los 3 amplificadores de 1 etapa concatenados mediante matrices ABCD        | 69 |

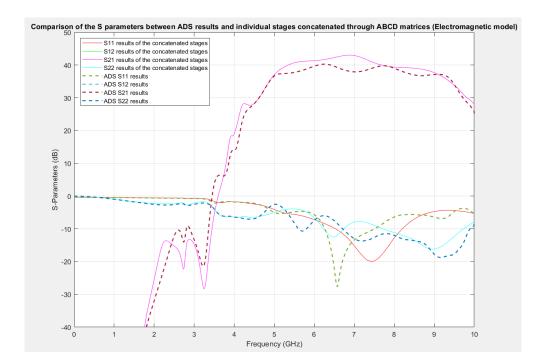

| 5.15. | Comparación de los parámetros S entre la simulación electromagnética del amplificador de 3 etapas y la concatenación de los 3 amplificadores de 1 etapa concatenados mediante matrices ABCD | 70 |

## Índice de tablas

| 2.1. | Distintos proyecto de LNAs                                                                                                                 | 3  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2. | Características AC, $V_{CE}=1,8V,f=5,5GHz$ transistor BFR840L3RHESD                                                                        | 6  |

| 2.3. | Resultados de las simulaciones de los parámetros de scattering a una frecuencia de 7,5 GHz para cada transistor                            | 13 |

| 2.4. | Ganancia y figura de ruido a una frecuencia de 7,5 GHz para cada transistor $$ . $$ .                                                      | 14 |

| 2.5. | Círculos de ganancia y ruido desadaptados                                                                                                  | 22 |

| 3.1. | Círculos de ganancia y de ruido adaptados                                                                                                  | 28 |

| 3.2. | Propiedades del Sustrato Rogers AD1000                                                                                                     | 29 |

| 4.1. | Medidas de la Figura de ruido para una polarización de $V_{CE}=2.5V,V_{B}=0.85V$ y una corriente de colector de 12 mA (en máxima ganancia) | 58 |

| 4.2. | Medidas de la Figura de ruido para distintas polarizaciones a 7 GHz                                                                        | 58 |

## Capítulo 1

## Introducción

En un sistema de telecomunicaciones las antenas se rigen por el principio de reciprocidad, es decir que la directividad, la impedancia, el ancho de haz etc., son iguales en transmisión y en recepción. No obstante, no hay que confundir el transmisor y el receptor con la antena transmisora y la receptora.

Por un lado, el transmisor debe encargarse de entregar a la antena transmisora una señal conocida modulada y codificada, que ha pasado por un amplificador de potencia para aumentar su energía y propagarla por el espacio en una o varias direcciones.

Por otro lado, el receptor debe captar la señal de potencia entregada por la antena receptora, que ha sido atenuada y se le ha superpuesto ruido (reduciendo su SNR) y posibles interferencias durante su viaje a través de distintos medios. En este punto las señales recibidas son demasiado pequeñas para ser demoduladas. Por ejemplo, la potencia de las señales Wi-Fi recibidas suelen ser de entre -50 dBm y -75 dBm, mientras que las señales de GPS pueden llegar hasta los -125 dBm en recepción. La solución es añadir un amplificador después de la antena receptora para que amplifique la señal. Sin embargo, hay que tener en cuenta que para demodular y decodificar correctamente la señal recibida debemos tener una SNR grande para que la *Bit Error Rate* (BER) sea baja. Esto se consigue usando un amplificador que aumente la magnitud de la señal aportando el menor ruido posible. En otras palabras, hay que usar un amplificador de bajo ruido o LNA.

Este trabajo se centrará en el diseño, la construcción y la medición del LNA que compone una pequeña parte de todo este sistema de recepción tan complejo.

#### 1.1. Motivación y Objetivos

A finales del siglo XX y principios del siglo XXI, la demanda de productos de comunicación inalámbrica relacionados con la telefonía móvil y la conexión a Internet ha crecido vertiginosamente, hasta tal punto de pasar del 2G al 5G en menos de 30 años. Como ya se ha comentado, el

primer elemento de la mayoría de receptores de los sistemas de comunicaciones es el amplificador de bajo ruido o LNA, que recibe y amplifica la señal débil y corrompida por el ruido de la antena agregando la menor cantidad de ruido posible.

El principal elemento a tener en cuenta en un LNA es la figura de ruido (NF), que es la cantidad de ruido intrínseco que añade el LNA. Un buen LNA tiene un NF bajo, de entre 1 y 3 dB, aunque en algunos casos puede llegar a los 5dB. Además, el LNA debe tener suficiente ganancia para aumentar la señal al nivel de potencia deseado. La ganancia y la figura de ruido no suelen llevarse bien, ya que cuando mejoras una, sueles empeorar la otra, por lo que los ingenieros de microondas suelen jugar con este trade-off.

Debido a la creciente demanda de amplificadores de bajo ruido, el objetivo principal de este trabajo es explicar el proceso de diseño, construcción y medición de un LNA que trabaje una frecuencia central de 7,5GHz y ofrezca una figura de ruido de entre 1 y 3 dB con una ganancia de 35 dB. Para ello, el trabajo se resume en 7 capítulos:

- En el capítulo 2 se hace un estudio de cuál de los 4 transistores que funcionan con tecnología SiGe es el que ofrece un mejor comportamiento para el tipo de amplificador que queremos diseñar. También se realiza una breve explicación de los parámetros S, la figura de ruido y la ganancia y sus respectivos círculos, la estabilidad y la importancia de los DC-Block y DC-Feed en un amplificador.

- En el capítulo 3 se explica todo el proceso del diseño de un amplificador de una etapa. Esto se hace así porque para comprender el funcionamiento de un amplificador de tres etapas, primero debemos comprender su modelo más sencillo. Para el diseño veremos las diferencias entre el modelo eléctrico ideal, el modelo eléctrico real y el modelo electromagnético y estudiaremos las 3 partes principales del amplificador: la red de adaptación, la red de polarización y la red de estabilización.

- En el capítulo 4 procedemos a construir un amplificador de 1 etapa con los resultados de las simulaciones electromagnéticas del capítulo anterior. Veremos todos los problemas que pueden llegar a surgir durante un proceso de montaje y la importancia que tiene comprender este proceso para diseñar un modelo que luego sea fabricable. Finalmente, en el proceso de medición se explicará la importancia de calibrar el VNA antes de medir y un método muy útil para realizar varias mediciones automáticamente.

- En el capitulo 5 se realiza el diseño del amplificador de 3 etapas. No se hace una explicación tan detallada de los apartados ya vistos en el capítulo 3, pero sí se mencionan aspectos que no se tienen en cuenta en una etapa, como los enlaces interetapa, la uniformidad en ganancia, la dependencia entre las distintas etapas...

- En el capítulo 6 se construye el amplificador de 3 etapas y se destaca la complejidad del montaje y la precisión necesaria de este para que todo funcione correctamente.

- En el capítulo 7 se encuentran las conclusiones obtenidas al final del trabajo.

## Capítulo 2

## Características de los transistores

Si bien los amplificadores de AsGa tiene un comportamiento óptimo en Ganancia y ruido, presentan um mayor consumo de corriente. La misión de este proyecto es validar si se puede construir un amplificador comparable en prestaciones a un amplificador de AsGa pero con un consumo menor. Para conseguir este objetivo se propone el uso de transistores de SiGe.

De momento el objetivo de este proyecto se basa en aprender el proceso de diseño y fabricación de un LNA a temperatura ambiente, pero en un futuro, el siguiente paso sería diseñarlo para temperaturas criogénicas. En la siguiente tabla se muestran distintos tipos de LNAs diseñados a temperaturas muy frías:

| Referencia | Tecnología                                   | Frecuencia | $G_{max}$ | NF   | $P_{dc}$ | FOM                 |

|------------|----------------------------------------------|------------|-----------|------|----------|---------------------|

| Referencia | rechologia                                   | (GHz)      | (dB)      | (dB) | (mW)     | $(\mathrm{GHz/mW})$ |

| [1]        | 100 nm InP HEMT                              | 4-12       | 37        | 6    | 15       | 4.52                |

| [2]        | $130~\mathrm{nm}~\mathrm{InP}~\mathrm{HEMT}$ | 0.5-13     | 38.1      | 4.4  | 15       | 7.2                 |

| [3]        | InP HEMT                                     | 4-12       | 34        | 5    | 9        | 6.04                |

| [4]        | $200~\mathrm{nm}$ InP HEMT                   | 4-12       | 27        | 13   | 5.7      | 2.91                |

| [5]        | 100 nm GaAs mHEMT                            | 4-12       | 31        | 5.3  | 8        | 5.85                |

| [6]        | $130~\mathrm{nm}$ SiGe HBT                   | 8-12       | 15        | 21   | 8.2      | 2.6                 |

| [7]        | SiGe HBT                                     | 0.5-4      | 25        | 9    | 8.3      | 1.17                |

| [8]        | SiGe HBT                                     | 4-8        | 26        | 8    | 0.58     | 22.4                |

| [9]        | SiGe NPN                                     | 3-14       | 32.4      | 11.4 | 5.8      | 5.39                |

Tabla 2.1: Distintos proyecto de LNAs

donde la figura de mérito o FOM no es más que una cifra que determina la magnitud de la calidad, desempeño, efectividad o eficiencia de un trabajo y en amplificadores de bajo ruido se

define como:

$$FOM = \frac{S_{21,mag} \cdot Bandwidth[GHz]}{(NF_{mag} - 1) \cdot P_{DC}[mW]}$$

(2.1)

En este capítulo se realizará un estudio de 4 modelos de transistores de SiGe diferentes y se seleccionará aquel que mejor se adapte a las necesidades del amplificador.

- Transistor BFR840L3RHESD de Infineon, cuyo Data Sheet podemos encontrar en [10]

- Transistor BFP720 de Infineon, cuyo Data Sheet podemos encontrar en [11]

- Transistor BFU725F de NXP (mismo que BFP740 de Infineon), cuyo Data Sheet podemos encontrar en [12]

- Transistor BFU730LX de NXP (mismo que BFR843EL3 de Infineon), cuyo Data Sheet podemos encontrar en [13]

Es importante comprobar que las especificaciones de los Data Sheet de cada transistor se adaptan a los modelos eléctricos de los fabricantes.

#### 2.1. Característica I-V: Punto de polarización

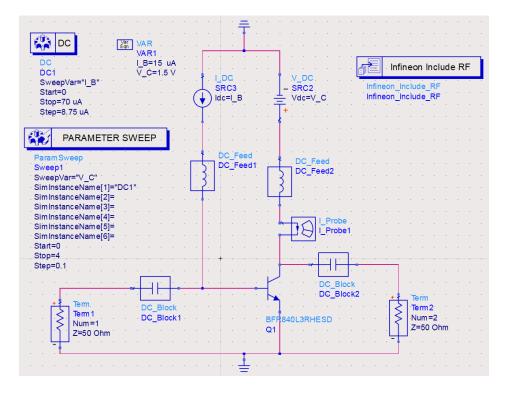

En este apartado estudiaremos la característica I-V de cada transistor. Un transistor que funciona en la región activa se dice que está polarizado y esto es muy útil para aplicaciones de amplificación. En ADS se puede representar la característica I-V para ver a partir de qué tensión de colector-emisor  $V_{CE}$  y de qué corriente de base  $I_B$  se consigue que el transistor pase de la región de saturación a la región activa. Para hacer la simulación del punto de polarización se puede usar la función BJT Curve Tracer con una corriente de base de 0 a  $70\mu A$  y una tensión colector-emisor de 0 a 3V o equivalentemente usando un DC simulation que muestree la corriente de base y un parameter sweep que barra la tensión  $V_{CE}$ :

Figura 2.1: Modelo no lineal PSPICE

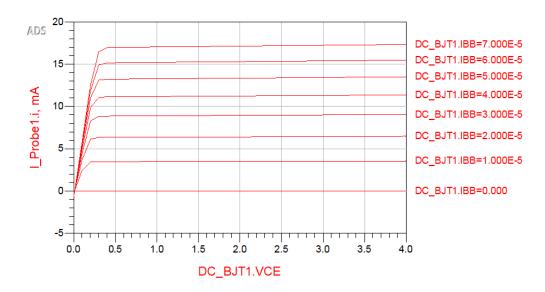

Figura 2.2: Característica I-V Transistor BFR840L3RHESD

Notar que aunque se aumente  $V_{CE}$  a un valor mayor del máximo permitido por los Data Sheet, no se contempla el punto de ruptura porque la aproximación del modelo eléctrico de Infineon se ha optimizado para potencias bajas.

Si se realizar la misma simulación para los 4 transistores se observa que tienen una característica I-V muy parecida, pero no idéntica. Esto se debe a que los packages de cada transistor son diferentes y provocan que en continua haya una mínima variación en el punto de polarización.

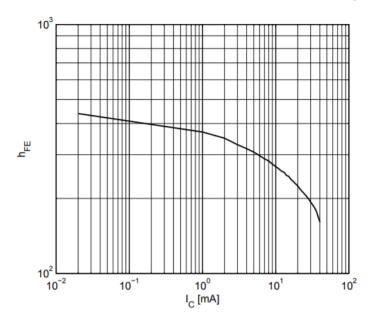

Por otro lado, de la figura 2.2 se puede obtener  $\beta$  o ganancia de corriente DC  $(h_{FE})$ , que es

la relación entre la corriente de colector  $I_C$  y la corriente de base  $I_B$ , es decir, cuántas veces es mayor la primera que la segunda.

$$\beta = h_{FE} = \frac{I_C}{I_B} \tag{2.2}$$

Esta relación disminuye a medida que  $I_C$  aumenta, tal y como vemos en [10, fig. 4]:

Figura 2.3: DC current gain  $h_{FE}=f(I_C), V_{CE}=1,8V$  BFR840L3RHESD transistor

#### 2.1.1. Elección del punto de polarización óptimo

En este apartado se va a determinar qué alimentación,  $V_{CE}$  y  $I_B$  debe trabajar el transistor elegido para obtener una figura de ruido mínima y una ganancia elevada.

Como se ve en [10], el fabricante proporciona distintos valores ganancias y figuras de ruido en función de la frecuencia. Dado que el transistor funcionará a una frecuencia de 7,5 GHz se tomará como referencia la tabla de 5,5 GHz del Data Sheet.

| Parameter            | Symbol       | Values | Unit                   | Test Condition |

|----------------------|--------------|--------|------------------------|----------------|

| Maximum power gain   | $G_{ms}$     | 22     | dB                     | $I_C = 10mA$   |

| Transducer gain      | $ S_{21} ^2$ | 19     | uБ                     | $I_C = 10mA$   |

| Minimum noise figure | $NF_{min}$   | 0,65   | $\mathrm{d}\mathrm{B}$ | $I_C = 5mA$    |

| Associated gain      | $G_{ass}$    | 16,5   | uD                     | $I_C = 5mA$    |

Tabla 2.2: Características AC,  $V_{CE}=1,8V,\,f=5,5GHz$  transistor BFR840L3RHESD

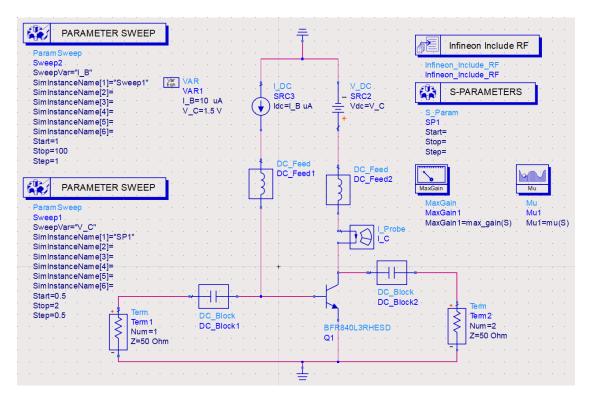

A continuación se demuestra que los valores dados por el Data Sheet se parecen en el simulador. Para empezar se añaden dos parameter sweep a nuestro modelo PSPICE: uno que barra un rango de corrientes  $I_B$  y otro que barra un rango de tensiones  $V_{CE}$ .

Figura 2.4: Circuito PSPICE con los parameter sweep de  $V_{CE}$  y  $I_C$  transistor BFR840L3RHESD

Además, hay que enfocar el análisis para una única frecuencia; en este caso para f=7,5 GHz. Para hacerlo hay que ir a la función S-parameters y cambiar el tipo de barrido a single point

Figura 2.5: Cómo cambiar el tipo de barrido de linear a single point

Una vez simulado observar que la tensión  $V_{CE}$  no tiene mucha influencia en la figura de ruido

y la ganancia. Sin embargo, cuando la corriente de base  $I_B$  es muy pequeña se genera mucho ruido y poca ganancia, mientras que cuando  $I_B$  es grande sucede lo contrario.

Los markers 1 y 3 indican la mínima y máxima figura de ruido respectivamente, correspondientes a los markers 2 y 4 que indican la ganancia mínima y máxima respectivamente.

Figura 2.6: Dependencia de la figura de ruido respecto de  $I_B$  en  $\mu A$  y  $V_{CE}$  en V

Figura 2.7: Dependencia de la ganancia respecto de  $I_B$  en  $\mu A$  y  $V_{CE}$  en V

Notar que hay una figura de ruido mínima para una corriente de base  $I_B=11\mu A$  que, haciendo uso de la expresión 2.2, corresponde a una corriente de colector  $I_C=4mA$ . De igual forma, se encuentra la ganancia máxima en  $I_B=29\mu A$  que corresponde a una  $I_C\approx 9mA$ . Las diferencias respecto del Data Sheet se deben a que se ha usado una frecuencia distinta.

#### 2.1.2. Influencia de la frecuencia en el punto de polarización

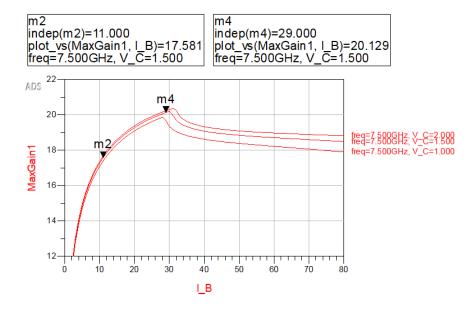

También es interesante analizar la figura de ruido y la ganancia en función de la frecuencia:

Figura 2.8: Dependencia de la figura de ruido respecto de  $I_B$  en  $\mu A$  y  $V_{CE}$  en V y múltiples frecuencias

Figura 2.9: Dependencia de la ganancia respecto de  $I_B,\,V_{CE}$  y múltiples frecuencias

Como cabía esperar, tanto la figura de ruido como la ganancia dependen de la frecuencia y a medida que esta aumenta, también lo hace la figura de ruido y la ganancia disminuye. En otras palabras, el aumento de la frecuencia siempre será un mal condicionante para la figura de ruido y la ganancia.

#### 2.2. Parámetros de Scattering

Los parámetros de scattering se utilizan, normalmente en frecuencias altas, para definir el comportamiento de redes eléctricas lineales en régimen permanente de pequeñas señales. Los amplificadores de bajo ruido trabajan con señales de potencia bajas y por tanto tendrán un comportamiento lineal. Si se trabajara con amplificadores de potencia habría que tener en cuenta las no-linealidades. Clasificamos los parámetros S (teniendo en cuenta que las redes de entrada y salida están adaptadas) según:

- S(1,1): Es el coeficiente de reflexión a la entrada

- $\, \bullet \,$  S(1,2): Es la potencia de la señal que entra por la entrada y sale por la salida

- S(2,1): Es la potencia de señal que entra por la salida y sale por la entrada. Si el sistema es recíproco  $S_{21} = S_{12}$

- S(2,2): Es el coeficiente de reflexión a la salida. Si el sistema es simétrico  $S_{22}=S_{11}$

Hay tres formas de calcular los parámetros de Scattering gracias a las librerías de Infineon y ADS.

- 1. La primera consiste en realizar un modelo no lineal PSPICE que se utiliza para representar el dispositivo. Este es el caso ideal, sin embargo, los modelos de señales grandes no suelen producir parámetros S precisos. Si se usa este modelo, se debe comprobar que los parámetros S simulados se aproximen a los del Data Sheet del fabricante. Este tipo de modelos es útil para simulaciones de CC (Corriente Continua).

- 2. En Infineon, y en muchos otros fabricantes, los transistores tienen un modelo SPARA, que actúa como una caja negra con un puerto de entrada conectado a la base y un puerto de salida conectado al colector, formando así una matriz de 4 parámetros de scattering. En el interior de la caja negra se encuentra el transistor evaluado con diferentes puntos de trabajo (combinaciones de valores de corriente de colector I<sub>C</sub> y tensión de colector-emisor V<sub>CE</sub>) medidos por el fabricante. Cabe esperar que el método SPARA sea más optimo que el anterior, debido a que se trata de un archivo con muchas mediciones hechas por el propio fabricante que determinan un comportamiento medio de los parámetros S del transistor para cada frecuencia. Sin embargo, este método está limitado por el número de combinaciones V<sub>CE</sub>, I<sub>C</sub> que haya medido y incluido el fabricante en el paquete y además, tampoco será útil si queremos evaluar no linealidades como el comportamiento de los harmónicos, entre otros, ya que se trata de un modelo de pequeña señal.

Figura 2.10: Diferentes combinaciones  $V_{CE} - I_C$  para el transistor SPARA

3. Usar un "Dynamic N-Port S-parameter File": un elemento de ADS que permite importar una lista Touchstone de parámetros S para una frecuencia dada. Este Touchstone se puede realizar en el laboratorio tomando las medidas S del transistor y anotándolas por columnas o descargando listas de medidas hechas por los propios fabricantes.

Figura 2.11: Cómo seleccionar un archivo Touchstone haciendo uso del N-Port S-Parameter File

En este capítulo se usarán las opciones 1 y 2 para comprobar cuál de los dos modelos se parece más al Data Sheet y, más adelante, cuando se construya el amplificador se usará la opción 3 para importar las mediciones y comparar cuál de los dos se parece más a los resultados medidos en el laboratorio.

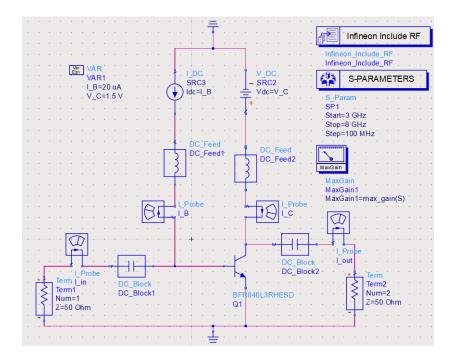

Para medir los parámetros S se ha usado la función S-Parameters con un rango de frecuencias de 3 GHz a 8 GHz como se muestra a continuación:

Figura 2.12: Modelo no lineal PSPICE. Se ha incluido el S-parameters

Se toma una corriente de colector  $I_C$  y una tensión de colector-emisor  $V_{CE}$  de referencia para usar en ambos casos. Para realizar la simulación de los parámetros S se va a usar el punto de polarización que se ha encontrado en el apartado 2.1.1, donde se produce mínima figura de ruido para el transistor BFR840L3RHESD y el que se recomienda en el Data Sheet para el resto de transistores

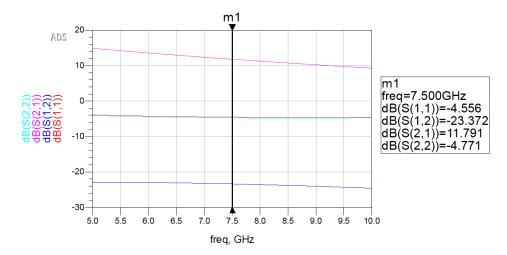

Figura 2.13: Parámetros de Scattering del transistor BFR840L3RHESD.  $V_{CE}=1,5V,\,I_{C}=4mA$  y  $I_{B}=11\mu A$

Observar que el sistema no está adaptado, ya que todavía no se han añadido las redes de adaptación. En la siguiente tabla se muestran los resultados de los parámetros S para ambos modelos de cada transistor:

| Transistor                     | S(1,1) | S(1,2)  | S(2,1)     | S(2,2)  | Unidad | $V_{CE},I_{C}$             |

|--------------------------------|--------|---------|------------|---------|--------|----------------------------|

| BFR840L3RHESD                  | -4,556 | -23,372 | 11,791     | -4,771  | dB     | $V_{CE} = 1,5V, I_C = 4mA$ |

| BFR840L3RHESD SPARA            | -4,313 | -22,476 | 13,298     | -5,883  | dB     | $V_{CE} = 1,5V, I_C = 4mA$ |

| BFP720                         | -3,420 | -23,714 | $12,\!470$ | -11,092 | dB     | $V_{CE} = 3V, I_C = 5mA$   |

| BFP720 SPARA                   | -4,715 | -24,466 | 12,217     | -10,522 | dB     | $V_{CE} = 3V, I_C = 5mA$   |

| BFP740 (NXP BFU725F)           | -2,641 | -24,804 | 9,983      | -7,552  | dB     | $V_{CE} = 3V, I_C = 6mA$   |

| BFP740 (NXP BFU725F) SPARA     | -3,178 | -23,104 | 10,664     | -9,798  | dB     | $V_{CE} = 3V, I_C = 6mA$   |

| BFR843EL3 (NXP BFU730LX)       | -5,323 | -28,339 | 12,735     | -4,830  | dB     | $V_{CE}=1,\!8V,I_C=8mA$    |

| BFR843EL3 (NXP BFU730LX) SPARA | -6,212 | -26,558 | 12,203     | -5,742  | dB     | $V_{CE} = 1.8V, I_C = 8mA$ |

Tabla 2.3: Resultados de las simulaciones de los parámetros de scattering a una frecuencia de 7,5 GHz para cada transistor

Notar que en ningún caso hay diferencias importantes entre el modelo no lineal PSPICE de un transistor y su modelo SPARA, por lo que de momento no se puede saber cuál de los dos se aproxima más a la realidad.

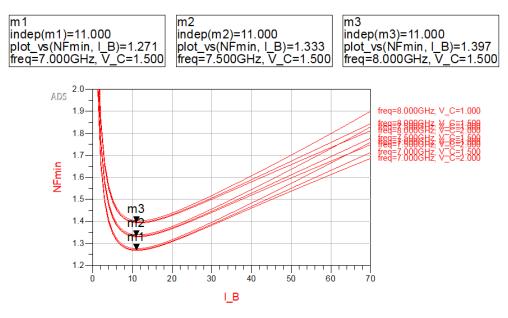

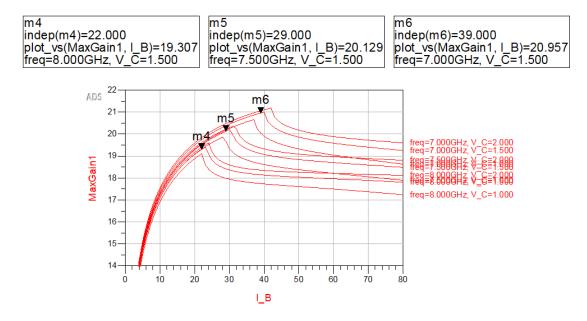

### 2.3. Figura de ruido mínima y ganancia máxima

En este apartado se va a realizar de nuevo una comparación de ganancia máxima y figura de ruido mínima entre el modelo no lineal y el modelo SPARA de cada transistor. El transistor que ofrezca la menor figura de ruido y la mayor ganancia será el que se usará en el diseño del amplificador.

Para cada transistor, se usarán los mismos valores de  $V_{CE}$  y  $I_C$  que en la tabla 2.3. Cabe destacar que para que ADS calcule la figura de ruido hay que ir a la función S-parameters y seleccionar  $Calculate\ noise$  en la pestaña de Noise.

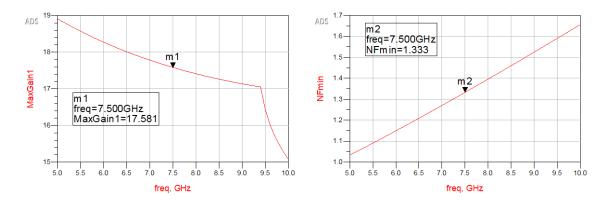

Figura 2.14: Figura de ruido mínima y ganancia máxima con transistor BFR840L3RHESD

Figura 2.15: Figura de ruido mínima y ganancia máxima con transistor BFR840L3RHESD SPARA

Si se realizan estas mismas simulaciones para los otros 3 transistores, se obtienen los siguientes valores de figura de ruido mínima y ganancia máxima para la frecuencia de 7,5GHz:

| Transistor          | NFmin | Gmax   | Unidad | VCE, IC                    |

|---------------------|-------|--------|--------|----------------------------|

| BFR840L3RHESD       | 1,333 | 17,581 | -      | $V_{CE} = 1,5V, I_C = 4mA$ |

| BFR840L3RHESD SPARA | 0,755 | 17,887 | -      | $V_{CE} = 1,5V, I_C = 4mA$ |

| BFP720              | 0,944 | 18,092 | -      | $V_{CE} = 3V, I_C = 5mA$   |

| BFP720 SPARA        | 0,809 | 15,673 | -      | $V_{CE} = 3V, I_C = 5mA$   |

| BFP740              | 1,203 | 17,394 | -      | $V_{CE} = 3V, I_C = 6mA$   |

| BFP740 SPARA        | 1,122 | 16,884 | -      | $V_{CE} = 3V, I_C = 6mA$   |

| BFR843EL3           | 1,058 | 17,786 | -      | $V_{CE} = 1.8V, I_C = 8mA$ |

| BFR843EL3 SPARA     | 1,106 | 16,072 | -      | $V_{CE} = 1.8V, I_C = 8mA$ |

Tabla 2.4: Ganancia y figura de ruido a una frecuencia de 7,5 GHz para cada transistor

En vista de estos resultados el transistor que ofrece una menor figura de ruido es el BFR840L3RHESD SPARA. Además, es el transistor que exige menor alimentación en sus terminales. Es por esto que se ha elegido este transistor para diseñar el LNA.

Notar que en todos los casos, el modelo SPARA es mucho más eficiente en términos de figura de ruido que el modelo no lineal PSPICE. Como se ha comentado en el apartado 2.2, cabe esperar que el modelo SPARA sea más exacto en términos de figura de ruido que el modelo de señal grande. Sin embargo, debido a la diferencia tan importante entre ambos modelos no podemos asegurar cuál de los dos es más preciso, por lo que se tendrá comprobar experimentalmente.

2.4. Frecuencia de corte

#### 2.4. Frecuencia de corte

La frecuencia de corte (o *cutoff frecuency* en inglés) en un transistor es el límite de la respuesta frecuencial en el que la energía que fluye a través de este se reduce al valor de -3dB (la mitad) de la potencia respecto al nivel de referencia de 0dB.

La frecuencia de corte suele ser unas 10 veces más grande que la frecuencia de operación. En el caso de este transistor, la frecuencia de corte será de unos 80 GHz.

#### 2.5. Estabilidad

Tal y como se explica en [14, pág 564], la estabilidad es un parámetro que controla las posibles oscilaciones indeseadas que pueden generar distorsión en la señal de potencia. Estas oscilaciones se generan por culpa de una impedancia con parte real negativa a la entrada ( $|S_{11}| = |\Gamma_{in}| > 1$ ) o a la salida ( $|S_{22}| = |\Gamma_{out}| > 1$ ) de los puertos de la red de parámetros S.

Además, la estabilidad depende de la frecuencia, por lo que un amplificador puede ser estable a ciertas frecuencias y hacerse inestable en otras.

Durante el análisis de la estabilidad nos podemos encontrar con 3 situaciones:

- Inestabilidad: el transistor provoca oscilaciones y por tanto no puede funcionar como amplificador. La inestabilidad es útil en osciladores.

- Estabilidad incondicional: una red de puertos es incondicionalmente estable a una frecuencia dada si las partes reales de  $Z_{in}$  y  $Z_{out}$  son positivas para todas las impedancias de fuente y de carga. Este estado es el más deseado, debido a que el transistor siempre será estable. Para determinar si nuestro sistema es incondicionalmente estable usamos el factor de estabilidad o factor de John Rollett:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} > 1$$

(2.3)

donde

$$\Delta = |S_{11}S_{22}| - |S_{12}S_{21}| < 1 \tag{2.4}$$

Cuando K>1 y  $|\Delta|<1$ , el transistor será incondicionalmente estable, es decir, se encontrará en la zona estable, donde se produce la máxima ganancia. Si los parámetros de scattering no satisfacen estas dos condiciones el sistema no sería incondicionalmente estable y habría que usar los círculos de estabilidad para ver si hay valores de  $\Gamma_s$  y  $\Gamma_L$  para los que haya estabilidad condicional.

Sin embargo, hay otro parámetro mucho más útil que el factor K de Rollett que permite evaluar cuan estable es el sistema. Este se denomina  $\mu - test$

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta S_{11}^*| + |S_{12}S_{21}|} > 1 \tag{2.5}$$

Estabilidad 2.5. 16

A diferencia de la K, que solo indica si un sistema es estable cuando K > 1, el parámetro  $\mu$ , que de igual forma satisface estabilidad incondicional cuando  $\mu > 1$ , también es capaz de comparar la estabilidad de dos dispositivos distintos, siendo más estable aquel que tenga mayor  $\mu$ . Por ejemplo, si tenemos un sistema A con estabilidad incondicional  $\mu = 3$  y un sistema B con  $\mu = 6$ , sabemos que ambos sistemas son estables, pero el sistema B es más estable que el A.

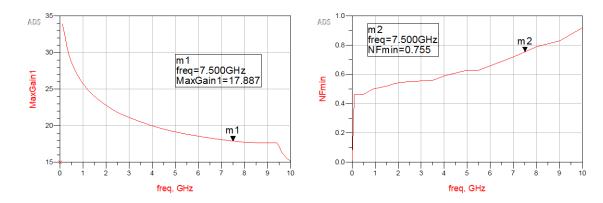

A continuación se muestra la simulación de los parámetros K y  $\mu$  del circuito usado en la figura 2.12:

Figura 2.16: Factor de Rollett y  $\mu - test$  transistor BFR840L3RHESD y BFR840L3RHESD **SPARA**

Notar que el circuito no es incondicionalmente estable a la frecuencia de 7 GHz. De hecho tendría que llegar a los 9,3 GHz para que empezara a serlo. Para hacer la simulación se ha usado la función StabFact y mu del ADS.

• Estabilidad condicional: una red de puertos es condicionalmente estable a una frecuencia dada si las partes reales de  $Z_{in}$  y  $Z_{out}$  son negativas para algunas de las impedancias de fuente y de carga. Para analizar la estabilidad condicional del transistor se usan los círculos de estabilidad, que determinan las regiones de  $\Gamma_s$  y  $\Gamma_L$  donde este será condicionalmente estable. Para ello buscamos el centro (C) y radio (R) de los círculos de ganancia de fuente y carga a partir de los parámetros S. Recordar que cada conjunto de parámetros S viene asociado a un valor de frecuencia, por lo que la estabilidad dependerá directamente de esta.

$$C_s = \frac{(S_{11} - \Delta s_{22}^*)^*}{|S_{11}| - |\Delta|^2} \qquad ; \qquad R_s = \left| \frac{S_{12} S_{21}}{|S_{11}|^2 - |\Delta|^2} \right| \tag{2.6}$$

$$C_{s} = \frac{(S_{11} - \Delta s_{22}^{*})^{*}}{|S_{11}| - |\Delta|^{2}} \qquad ; \qquad R_{s} = \left| \frac{S_{12}S_{21}}{|S_{11}|^{2} - |\Delta|^{2}} \right|$$

$$C_{L} = \frac{(S_{22} - \Delta S_{11}^{*})^{*}}{|S_{22}| - |\Delta|^{2}} \qquad ; \qquad R_{L} = \left| \frac{S_{12}S_{21}}{|S_{22}|^{2} - |\Delta|^{2}} \right|$$

$$(2.6)$$

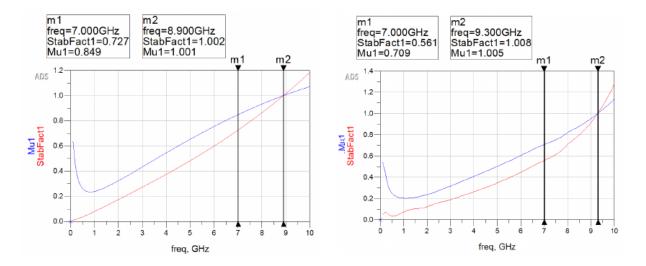

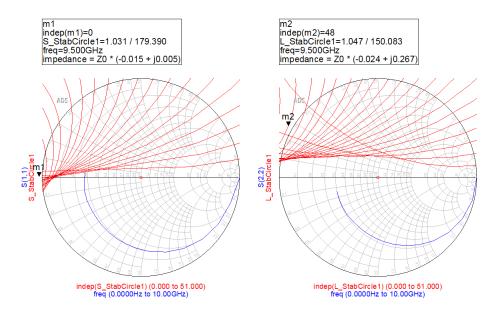

Para hacer la simulación se han usado las funciones S\_StabCircle para la fuente y L\_StabCircle para la carga. Cabe destacar que es necesario normalizar la carta de smith 2.5. Estabilidad 17

para visualizar correctamente los círculos de estabilidad yendo a *plot options*, desmarcando la casilla *auto scale* y poniendo 1 en "max".

Figura 2.17: Círculos de estabilidad de fuente y de carga para transistor BFR840L3RHESD

Figura 2.18: Círculos de estabilidad de fuente y de carga para transistor BFR840L3RHESD SPARA

Hay estabilidad en todas aquellas impedancias, que, asociadas a un círculo de estabilidad, se encuentran fuera de la carta de smith. Interesa que todos los círculos se encuentren fuera de la carta de Smith para asegurar que todas las impedancias que hay dentro de esta hagan el circuito estable (o lo que es lo mismo, haya estabilidad incondicional). En este caso, vemos que a partir de 9 GHz para el transistor BFR840L3RHESD y 9,5 para el BFR840L3RHESD SPARA empieza a haber estabilidad incondicional; que comparando con el método del parámetro  $\mu$  (estabilidad a partir de 8,9 GHz para el transistor

BFR840L3RHESD y 9,3 GHz para el transistor BFR840L3RHESD SPARA), los resultados son muy parecidos.

En resumen, el transistor es inestable para el rango de frecuencias en el que debe trabajar. Hay varias soluciones y una de ellas es usar un filtro paso alto.

Es muy importante saber que la estabilidad que se ha estudiado solo se aplica para 1 transistor. Para diseños de más de una etapa hay que buscar otros métodos para comprobar la estabilidad del circuito (p. ej. observando el aislamiento o evitando picos de inestabilidad en el parámetros S21).

#### 2.6. Círculos de ganancia y figura de ruido

En el diseño de un front-end de RF es importante que la primera etapa de amplificación tenga características de bajo ruido y alta ganancia para desacoplar los efectos de ruido de las siguientes etapas. No obstante, es muy difícil diseñar amplificadores que cumplan con los dos parámetros de diseño, por lo que se crea un cierto compromiso o "trade-off". De ahí la utilidad de contar con los círculos de ganancia y los círculos de figura de ruido, que indican qué impedancias (normalmente complejas) a la entrada y salida del transistor consiguen mejores resultados.

El objetivo de este apartado es encontrar dichas impedancias complejas que en el siguiente capítulo serán adaptadas a  $50\Omega$  mediante las redes de adaptación. No obstante, para entender mejor el funcionamiento de estos círculos antes debe hacerse un análisis teórico con la ayuda de [14, pág 575].

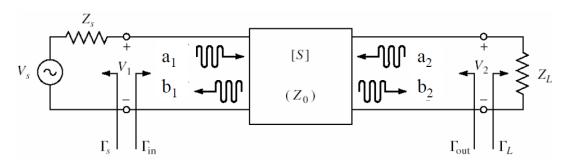

#### 2.6.1. Análisis teórico de los círculos de ganancia

Considerando un bipuerto genérico de dos puertas caracterizado por su matriz de parámetros S, conectado a una impedancia de fuente y de carga genérica,  $Z_S$  y  $Z_L$ .

Figura 2.19: Red de dos puertas genérica con impedancia de fuente y carga arbitraria

donde  $a_1$  y  $a_2$  son las ondas progresivas a la entrada y a la salida de la red de parámetros [S] y  $b_1$  y  $b_2$  sus respectivas ondas regresivas. Los coeficientes de reflexión vistos hacia la fuente

y hacia la carga son:

$$\Gamma_S = \frac{a_1}{b_1} = \frac{Z_s - Z_o}{Z_s + Z_o} \quad ; \quad \Gamma_L = \frac{a_2}{b_2} = \frac{Z_L - Z_o}{Z_L + Z_o}$$

(2.8)

Además, como que la red no está adaptada  $\Gamma_{in} \neq S_{11}$  y  $\Gamma_{out} \neq S_{22}$  porque  $Z_o \neq Z_L \neq Z_S$ . De esta forma podemos expresar el coeficiente de reflexión a la entrada y a la salida del bipuerto en función de la matriz de parámetros S del bipuerto y el coeficiente de reflexión de fuente y carga respectivamente.

$$\Gamma_{in} = \frac{b_1}{a_1} = s_{11} + \frac{s_{12}s_{21}\Gamma_L}{1 - s_{22}\Gamma_L} \qquad ; \qquad \Gamma_{out} = \frac{b_2}{a_2} = s_{22} + \frac{s_{12}s_{21}\Gamma_s}{1 - s_{11}\Gamma_s}$$

(2.9)

Podemos diferenciar tres definiciones de ganancia:

■ Ganancia de potencia  $G_P = P_L/P_{in}$ : definida según el ratio entre la potencia disipada en la carga y la potencia entregada al bipuerto. Es independiente de  $Z_S$ .

$$G_P = |s_{21}|^2 \frac{1 - |\Gamma_L|^2}{(1 - |\Gamma_{in}|^2)|1 - s_{22}\Gamma_L|^2}$$

(2.10)

• Ganancia disponible  $G_A = P_{avn}/P_{avs}$ : definida según el ratio entre la potencia disponible desde la salida del bipuerto y la potencia disponible desde la fuente. Asume adaptación conjugada en la fuente y en la carga. Depende de  $Z_S$  pero no de  $Z_L$ .

$$G_A = |s_{21}|^2 \frac{1 - |\Gamma_s|^2}{(1 - |\Gamma_{out}|^2)|1 - s_{11}\Gamma_s|^2}$$

(2.11)

■ Ganancia de transferencia  $G_T = P_L/P_{avs}$ : definida según el ratio entre la potencia disipada en la carga y la potencia disponible desde la fuente. Depende de  $Z_S$  y  $Z_L$

$$G_T = |s_{21}|^2 \frac{(1 - |\Gamma_s|^2)(1 - |\Gamma_L|^2)}{|(1 - s_{11}\Gamma_s)(1 - s_{22}\Gamma_L) - s_{12}s_{21}\Gamma_s\Gamma_L|^2}$$

(2.12)

Un caso especial ocurre cuando la ganancia de transferencia se calcula en condiciones de adaptación, reflexión nula en la carga y en la fuente ( $\Gamma_L = \Gamma_s = 0$ ), simplificándose por tanto la expresión.

$$G_T = |s_{21}|^2 (2.13)$$

Otro caso especial se produce cuando el parámetro S12=0. Esta condición de no reciprocidad es común en muchos dispositivos, estableciendo la condición de ganancia unilateral según:

$$G_{TU} = \frac{P_L}{P_{avs}} = G_s G_o G_L = \frac{(1 - |\Gamma_s|^2)}{|1 - s_{22}\Gamma_L|^2} |s_{21}|^2 \frac{(1 - |\Gamma_L|^2)}{|(1 - |s_{22}\Gamma_L|)|^2}$$

(2.14)

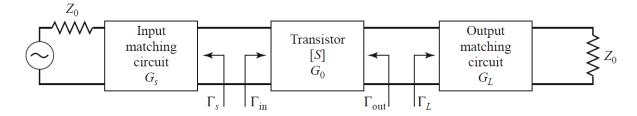

Un amplificador de una etapa se puede entender como una estructura que consta de tres partes: el transistor que realiza el proceso de amplificación, caracterizado por una matriz de parámetros S, y dos redes de adaptación (a la entrada y la salida) que realizan la función de adaptar la impedancia Zo a la impedancia de fuente y carga  $(Z_S, Z_L)$ . De ahí que la mejor definición es

la de ganancia de transferencia porque toma en cuenta errores de fuente y carga y además de forma separada como indica la figura 2.20.

Figura 2.20: Circuito general de un amplificador de una etapa

De la definición de ganancia de transferencia unilateral podemos establecer la definición de círculos de ganancia.

$$G_{TU} = \frac{P_L}{P_{avs}} = G_s G_0 G_L \tag{2.15}$$

donde:

$$G_S = \frac{1 - |\Gamma_S|^2}{|1 - \Gamma_{in}\Gamma_S|^2} \tag{2.16}$$

$$G_0 = |S_{21}|^2 (2.17)$$

$$G_L = \frac{1 - |\Gamma_L|^2}{|1 - S_{22}\Gamma_L|^2} \tag{2.18}$$

Si además el transistor es unilateral, es decir que  $S_{12}=0$  (o es tan pequeño que puede despreciarse), entonces las expresiones de 2.9 pueden reducirse a  $\Gamma_{in}=S_{11}, \Gamma_{out}=S_{22}$ .

Definimos círculos de ganancia constante a todos los valores de  $\Gamma_s$  (equivalentemente  $\Gamma_L$ ) que mapeados sobre la carta de Smith definen un valor único de  $G_S$  (equivalentemente  $G_L$ ). Estos valores permiten definir una familia de círculos con centro:

$$C_s = \frac{\frac{G_s}{G_{s-max}} s_{11}^*}{1 - \left(1 - \frac{G_s}{G_{s-max}}\right) |s_{11}|^2}$$

(2.19)

y radio

$$R_s = \frac{\sqrt{1 - \frac{G_s}{dG_{s-max}}} (1 - |s_{11}|^2)}{1 - (1 - \frac{G_s}{G_{s-max}})|s_{11}|^2}$$

(2.20)

Observar que la ganancia máxima se obtiene para  $\Gamma_s = s_{11} * y$  es de valor  $G_{s-max} = \frac{1}{1-|s_{11}|^2}$ .

#### 2.6.2. Análisis teórico de los círculos de figura de ruido

Continuando con el análisis del libro [14, pág 580], los círculos de figura de ruido de un amplificador dependerán únicamente del factor de ruido mínimo, intrínseco al transistor,  $R_n$ , y

el coeficiente de fuente óptimo,

$$F = F_{min} + \frac{4R_n}{Z_o} \frac{|\Gamma_s - \Gamma_{opt}|^2}{(1 - |\Gamma_s|^2)|1 + \Gamma_{opt}|^2}$$

(2.21)

que permite llegar a la definición de una familia de círculos de factor de ruido constante en el plano de  $|\Gamma_s|$  con centro

$$C_F = \frac{\Gamma_{opt}}{N+1} \tag{2.22}$$

y radio

$$R_F = \frac{\sqrt{N(N+1-|\Gamma_{opt}|^2)}}{N+1} \qquad ; \qquad N = \frac{F-F_{min}}{4R_n/Z_o}|1+\Gamma_{opt}|^2$$

(2.23)

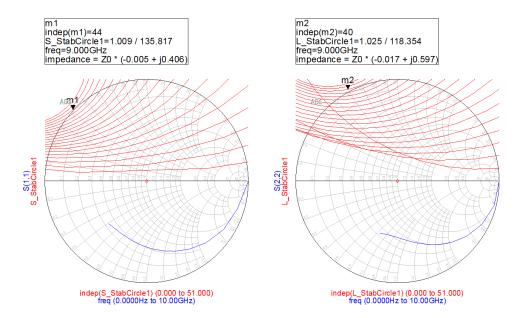

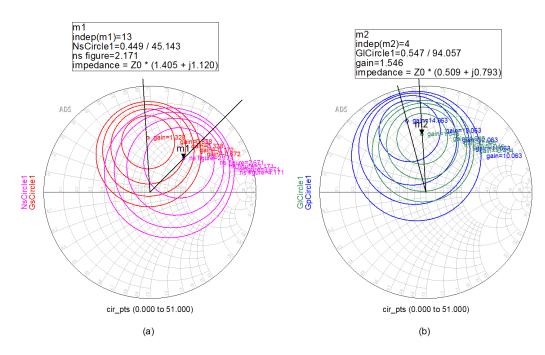

#### 2.6.3. Simulación de los círculos de ganancia y ruido

Habiendo entendido el funcionamiento teórico de los círculos de ganancia y de ruido se procede a simularlos mediante las siguientes funciones de ADS:

- GsCircle: devuelve los círculos de ganancia referentes a la fuente (Source) y correspondientes a la expresión 2.16. El centro y el radio de los círculos se calcula mediante las expresiones 2.19 y 2.20 respectivamente.

- GlCircle: devuelve los círculos de ganancia referentes a la carga (Load) y correspondientes a la expresión 2.18. El centro y el radio de los círculos se calcula mediante las expresiones 2.19 y 2.20 respectivamente.

- GpCircle: devuelve los círculos de ganancia de potencia correspondientes con la expresión

2.10. El primer círculo de esta función corresponde con la función maxGain.

- NsCircle: devuelve los círculos de figura de ruido referentes a la fuente (Source). El centro y el radio de los círculos se calcula mediante las expresiones 2.22 y 2.23 respectivamente. Cabe destacar que en el análisis teórico el ruido se refiere a la entrada, pero en realidad todos los dispositivos lo introducen a la salida. Esto es así para que expresiones como la de Friis tengan coherencia a la hora de aplicarlas teóricamente. Por este motivo que no existe una función "NlCircle" en ADS.

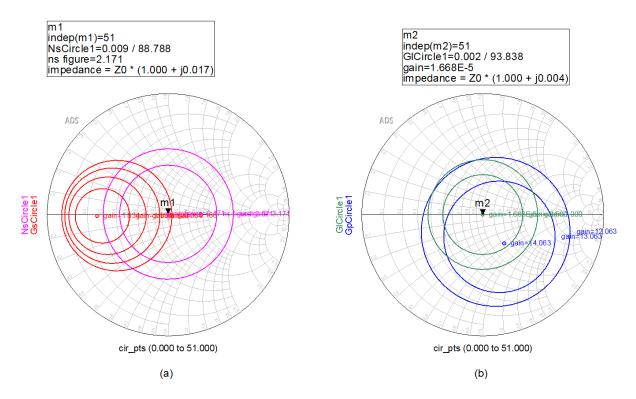

Se recomienda usar el botón de help que hay dentro de las funciones para saber cómo funciona la sintaxis de cada una. En la figura 2.21 se observan los círculos de ganancia usando las funciones DC-Feed y DC-Block

Figura 2.21: A la izquierda (a) círculos de ganancia de fuente y de figura de ruido. A la derecha (b) círculos de ganancia de carga y ganancia de potencia

| Círculos | 1r círculo | 20 círculo | 3r círculo | 40 círculo | 50 círculo |

|----------|------------|------------|------------|------------|------------|

| NsCircle | 2,171      | 2,671      | 3,171      | 3,671      | 4,171      |

| GsCircle | 1,328      | 0,828      | 0,328      | -0,172     | -0,672     |

| GlCircle | 1,546      | 1,046      | 0,546      | 0,046      | -0,454     |

| GpCircle | 14,063     | 13,063     | 12,063     | 11,063     | 10,063     |

Tabla 2.5: Círculos de ganancia y ruido desadaptados

Observar que, para cada caso, el círculo del centro representa el punto más óptimo y a medida que nos alejamos de este, los siguientes círculos van representando una disminución en su efectividad de 0,5 dB (este *step* se puede modificar en la sintaxis de las funciones).

De hecho, si se compara el valor del primer círculo de la figura de ruido con la función NFmin de la tabla 2.4 se comprueba que el valor es exactamente el mismo. También se observa que la función maxGain de ADS coincide con el primer círculo de la ganancia de potencia (que es independiente de  $Z_S$ ).

A continuación se calcula la ganancia de transferencia unilateral siguiendo la expresión 2.15. Notar que es bastante mala porque todavía no se ha adaptado el sistema:

$$G_{TU} = G_s G_0 G_L = 10^{\frac{0.328}{10}} \cdot |3,273|^2 \cdot 10^{\frac{1.546}{10}} = 16,49 = 12,17dB$$

La impedancia de la que se partirá en el siguiente capítulo para diseñar las redes de adaptación o *Matching Networks* de entrada y de salida está marcada con los markers.

#### 2.7. DC-Block Y DC-Feed

Los DC-Block y los DC-Feed son capacitancias y inductancias, respectivamente, que tienen un papel muy importante en todo amplificador:

- El DC-Feed bloquea el paso a RF a altas frecuencias para que la señal no se vaya a la alimentación y deja pasar la tensión en continua a bajas frecuencias para que alimente al transistor.

- El DC-Block, en cambio, bloquea la continua cuando ésta alimenta al transistor para que no se vaya hacia las Matching Networks y se solape con la señal de potencia RF que se inyecta por el terminal 1 y se extrae por el 2.

Sin embargo, cuando se quiere diseñar el modelo real del amplificador que funciona a altas frecuencias ( $\sim 7,5GHz$ ) los elementos concentrados como las bobinas y las capacidades se ven influenciados por parásitos que perjudican el sistema. Es por esto que a estas frecuencias se intentan usar elementos distribuidos como las líneas de transmisión, que no introducen pérdidas, sino un desfase en la onda dependiendo de la longitud de estas.

Es por esto que se pueden idear otras formas de construir los DC-Feed como usar una línea de transmisión de  $\lambda/4$  de alta impedancia conectada a la fuente de alimentación y a otra línea de transmisión de  $\lambda/4$  de alta impedancia con forma cuadrada o con forma de stub radial (que dará mejor comportamiento en ancho de banda) conectada a un circuito abierto. Lo que equivale a usar una capacidad conectada a un circuito abierto, pero ahorrándonos los inconvenientes que implica hacer esto (como los parásitos). A continuación se muestra una figura extraída de [15, pág 25] donde se muestra la representación del DC-Feed que acabamos de explicar:

Figura 2.22: DC-Feed con dos líneas de transmisión de  $\lambda/4$  acabadas en forma de stub radial.

Por su parte los DC-Block pueden sustituirse por líneas acopladas en vez de usar capacidades

reales. Sin embargo, a temperatura ambiente introducen más ruido que las capacidades reales. Esto es debido a la separación S de las líneas acopladas, que necesita ser muy pequeña para tener una figura de ruido óptima, pero, a su vez, si es demasiado pequeña no será posible fabricarla. A continuación se muestra una figura extraída de [16, pág 71] donde se muestra la representación del DC-Block que acabamos de explicar:

Figura 2.23: Circuito de líneas acopladas con función DC-Block

### Capítulo 3

# Diseño del LNA de 1 etapa

En todo proceso de ingeniería de microondas primero hay que realizar un estudio del modelo eléctrico ideal para comprobar sus límites y establecerlos como objetivos. En este capítulo partimos del diseño de un modelo ideal de LNA de una etapa que usaremos como referencia para elaborar y explicar el modelo eléctrico real, pasando por las distintas fases de construcción, como las redes de polarización o bias tee, las redes de estabilización, de adaptación... Para, finalmente, llegar al modelo electromagnético que usaremos para construir el amplificador en el laboratorio.

### 3.1. Modelo eléctrico ideal

En el modelo ideal usaremos las funciones DC-Block y DC-Feed de ADS y no tendremos en cuenta el sustrato.

Figura 3.1: Modelo eléctrico de un amplificador de 1 etapa desadaptado

A continuación se realizarán las *Matching Networks* de entrada y de salida para adaptar el sistema. Para ello se parte de la impedancia marcada en la figura 2.21 (a) para la *Matching Network* de entrada y de la impedancia marcada en la figura 2.21 (b) para la *Matching Network* de salida. Sabiendo esto hay dos maneras de elaborar estas redes de adaptación:

1. Smith Chart Utility: esta herramienta sirve para elaborar rápidamente las redes de adaptación usando las líneas de transmisión y los stubs en circuito abierto y cortocircuito de la paleta. De esta forma, para una red de adaptación de entrada llevar el punto verde de  $Z_L^*$  a  $Z_S = 50\Omega$  y para la red de adaptación de salida llevarlo de  $Z_S^*$  a  $Z_L = 50\Omega$ , tal y como se ve en la figura 3.2.

Figura 3.2: Herramienta Smith Chart para le red de adaptación de la entrada. Seleccionar el pin de la impedancia de carga y introducir el valor de impedancia **conjugada** que se quiere adaptar. En la impedancia de fuente se tienen  $50\Omega$

Si se selecciona la línea de transmisión o el stub que se han dibujado automáticamente en la Network Schematic se puede extraer el valor de sus longitudes eléctricas. Hay que tener en cuenta que haciendo esto se modifica la impedancia de entrada de la red de adaptación de salida (ya no corresponderá con el m2 de la figura 2.21.b). Por tanto hay que simular de nuevo el círculo de ganancia a la carga para obtener la nueva impedancia de la que partir para adaptar la salida.

2. **Tunning**: otra forma de crear las redes de adaptación es usando la herramienta tunning sobre las longitudes eléctricas e ir probando diferentes líneas de transmisión (*TLIN* en ADS) y stubs en cortocircuito (*TLSC* en ADS) y circuito abierto (*TLOC* en ADS) hasta llegar al centro:

Figura 3.3: Herramienta de tunning con 4 barridos en longitud eléctrica (uno por cada elemento distribuido)

Tener en cuenta que se pueden crear varias redes de adaptación, pero habrá que quedarse con la que menos longitud eléctrica tenga para que el prototipo sea lo más pequeño y menos costoso posible.

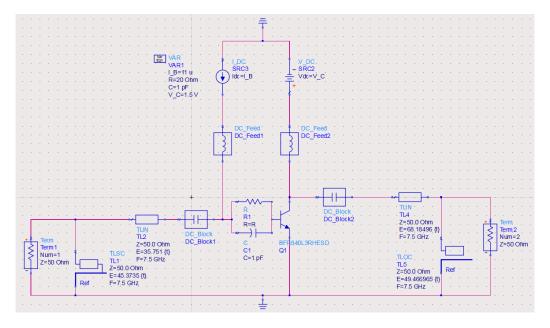

Figura 3.4: Matching Networks de entrada y de salida para la primera etapa de un modelo ideal

Si se simulan los círculos de ganancia y de ruido se puede observar que estos se han movido

al centro de la carta de Smith, confirmando que la adaptación que hemos hecho es correcta. Notar que estos círculos marcan ganancias de fuente y de carga muy bajas porque nos indican cuánta ganancia de fuente y de carga le falta al sistema para estar perfectamente adaptado.

Figura 3.5: Círculos de ganancia y figura de ruido adaptados

| Círculos | 1r círculo | 20 círculo | 3r círculo | 40 círculo | 50 círculo |

|----------|------------|------------|------------|------------|------------|

| NsCircle | 2,171      | 2,671      | 3,171      | 3,671      | 4,171      |

| GsCircle | 1,834      | 1,334      | 0,834      | 0,334      | -0,166     |

| GlCircle | 1,668E-5   | -0,500     | -1         | -1,500     | -2,000     |

| GpCircle | 14,063     | 13,063     | 12,063     | 11,063     | 10,063     |

Tabla 3.1: Círculos de ganancia y de ruido adaptados

Calculando de nuevo la ganancia de transferencia se observa que esta es prácticamente máxima para los círculos que se han elegido.

$$G_{TU} = 10^{\frac{-0.166}{10}} \cdot |3.939|^2 \cdot 10^{\frac{1.668E - 5}{10}} = 1 \cdot 15.516 \cdot 1 = 15.516 = 11.908dB$$

### 3.2. Modelo eléctrico real

Antes de diseñar el amplificador de 3 etapas, primero se hará uno de 1 etapa con un sustrato que esté disponible en el laboratorio. Cuando se finalice este primer prototipo y el resultado

sea el esperado, se añadirán las siguientes dos etapas para conseguir el objetivo de los 35dB de ganancia.

#### 3.2.1. Elección del sustrato

La elección del sustrato es muy importante en el diseño de cualquier dispositivo con tecnología microstrip. Hay muchos tipos de sustratos y una buena opción para decidir cuál de ellos elegir es buscar el sustrato que presente menos pérdidas en transmisión para nuestra frecuencia de trabajo de 7,5 GHz. Estas pérdidas en transmisión se cuantifican con la tangente de pérdidas (comúnmente denominadas "dissipation factor" en los Data Sheet) y son la disipación de energía electromagnética de un material dieléctrico.

$$\tan(\delta) = \frac{w\varepsilon'' + \sigma}{w\varepsilon'} = \frac{1}{Q}$$

(3.1)

donde  $\sigma$  es la conductividad de las pistas del sustrato (normalmente de cobre) y Q es el factor de calidad. Cuando no se tiene claro el sustrato que se quiere elegir se puede abrir un esquemático en ADS y añadir una línea de transmisión real MLIN conectada a dos terminales. Luego mirar todos los sustratos disponibles en el laboratorio y trasladar sus propiedades a ADS con la función MSUB. De esta forma, mediante la herramienta tunning podemos evaluar la tangente de pérdidas de cada sustrato y quedarnos con el que mejores condiciones tenga para nuestra frecuencia (7,5 GHz).

Otro aspecto a tener en cuenta cuando se elige el sustrato de un amplificador es que el grosor del transistor y del sustrato sean muy parecidos. Si el sustrato fuera mucho más ancho que el transistor, el pin de éste se doblaría y se rompería en el momento de soldarlo, por lo que sería necesario añadir una pequeña plataforma debajo de este para que estuviera a la misma altura. Este amplificador usará el sustrato Rogers ARLON AD1000, que está disponible en el laboratorio y cuyo Data Sheet encontramos en [17]

| General Parameters         | Value          | Uints |  |

|----------------------------|----------------|-------|--|

| Dielectric constant (Dk)   | 10,2           | -     |  |

| Substrate thickness (H)    | 25             | mils  |  |

| Dissipation factor (TanD)  | 0,0023         | -     |  |

| Conductor thickness (T)    | 0.006 to 0.127 | mils  |  |

| Copper conductivity (Cond) | $5.8\cdot10^7$ | S/m   |  |

Tabla 3.2: Propiedades del Sustrato Rogers AD1000

### 3.2.2. Capacidades y resistencias reales

A lo largo de este proyecto se usarán varios tipos de capacidades y resistencias reales, pero en este apartado solo se explicarán un caso de cada tipo para comprender la influencia de los

parásitos. Se han elegido los componentes de Murata porque en su página web [18] los tienen bien documentados y en general, suelen ser muy económicos.

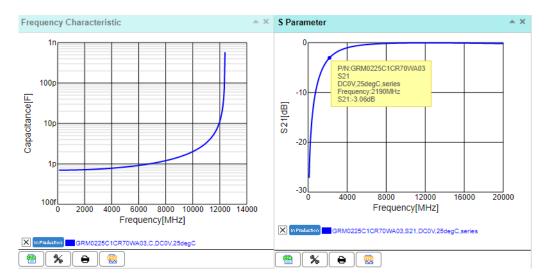

Los DC-Block del modelo ideal deben sustituirse por una capacidad de aproximadamente 1pF para una frecuencia de 7,5GHz. Es muy importante comprobar que las capacidades funcionen como deseamos a la frecuencia de trabajo. Se ha elegido la capacidad GRM0225C1CR70WA03 que, aunque tiene una capacitancia de 0,7pF, los elementos parasitarios hacen que a nuestra frecuencia valga 1,1pF como vemos en la figura 3.6:

Figura 3.6: Representación de la capacitancia y del parámetro  $S_{21}$  de la capacidad GRM0225C1CR70WA03 de Murata

Para la resistencia del estabilizador se ha usado una resistencia real SCPX\_0705\_D\_19950814 de  $10\Omega$ . A diferencia de las capacidades y las bobinas, los modelos reales de las resistencias no varían considerablemente en función de la frecuencia.

Figura 3.7: Representación de la impedancia en función de la frecuencia para la resistencia SCPX\_0705\_D\_19950814 de  $10\Omega$

### 3.2.3. Redes de polarización