Universitat

Autònoma

de Barcelona

ESCUELA TÉCNICA SUPERIOR DE INGENIERÍA

# Análisis y diseño de un procesador RISC simple para adquisición y proceso de datos

Memoria del proyecto final de carrera correspondiente a la titulación de Ingeniería Superior Informática realizado por Javier Gimbert Moreno y dirigido por Joan Oliver Malagelada.

Bellaterra, 14 de junio de 2007

El firmante, Joan Oliver Malagelada, profesor del Departamento de Microelectrónica y Sistemas Electrónicos de la Universidad Autónoma de Barcelona

CERTIFICA:

Que la presente memoria ha sido realizada bajo su dirección por Javier Gimbert Moreno

Bellaterra, 14 de junio de 2007

Joan Oliver Malagelada

# Índice general

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| <b>1. Introducción</b>                                                  | <b>9</b>  |

| <b>2. Análisis de procesadores simples</b>                              | <b>13</b> |

| 2.1. El Procesador DLX . . . . .                                        | 13        |

| 2.2. El Procesador MicroBlaze <sup>TM</sup> . . . . .                   | 16        |

| 2.3. El Procesador Nios®II . . . . .                                    | 19        |

| 2.4. El Procesador AVR®32 . . . . .                                     | 22        |

| 2.5. El Procesador LatticeMico32 <sup>TM</sup> . . . . .                | 24        |

| 2.6. Simple RISC Computer . . . . .                                     | 26        |

| 2.7. Comparativa de procesadores . . . . .                              | 28        |

| <b>3. Análisis de buses</b>                                             | <b>31</b> |

| 3.1. Bus AMBA <sup>TM</sup> . . . . .                                   | 31        |

| 3.2. Bus Avalon . . . . .                                               | 33        |

| 3.3. Bus Wishbone . . . . .                                             | 35        |

| <b>4. Análisis de prestaciones. Tecnología de diseño. Planificación</b> | <b>39</b> |

| <b>5. El procesador SR3C</b>                                            | <b>43</b> |

| 5.1. Introducción . . . . .                                             | 43        |

| 5.2. Arquitectura . . . . .                                             | 45        |

| 5.3. Sistema de interrupciones . . . . .                                | 53        |

| 5.4. SR3C con Multiplexores . . . . .                                   | 57        |

| 5.5. SR3C compatible con Bus Wishbone . . . . .                         | 58        |

| 5.6. Ensamblador . . . . .                                              | 59        |

| 5.7. Simulador . . . . .                                                | 60        |

| <b>6. Resultados</b>                                                    | <b>63</b> |

| <b>7. Conclusiones</b>                                                  | <b>69</b> |

| <b>A. Conjunto de instrucciones del SR3C</b>                            | <b>73</b> |

| <b>B. Manual del ensamblador</b>                                        | <b>83</b> |

| <b>C. Manual del simulador</b>                                          | <b>87</b> |

| <b>Bibliografía</b>                                                     | <b>90</b> |

# Índice de figuras

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| 2.1. Arquitectura del procesador DLX . . . . .                                      | 16 |

| 2.2. Arquitectura del procesador MicroBlaze <sup>TM</sup> . . . . .                 | 17 |

| 2.3. Arquitectura del procesador PicoBlaze <sup>TM</sup> . . . . .                  | 19 |

| 2.4. Arquitectura del procesador Nios <sup>®</sup> II . . . . .                     | 20 |

| 2.5. Pipeline del procesador AVR <sup>®</sup> 32 . . . . .                          | 23 |

| 2.6. Arquitectura del procesador LatticeMico32 <sup>TM</sup> . . . . .              | 25 |

| 2.7. Arquitectura de 1 Bus del procesador SRC . . . . .                             | 28 |

| 3.1. Sistema típico AMBA <sup>TM</sup> . . . . .                                    | 32 |

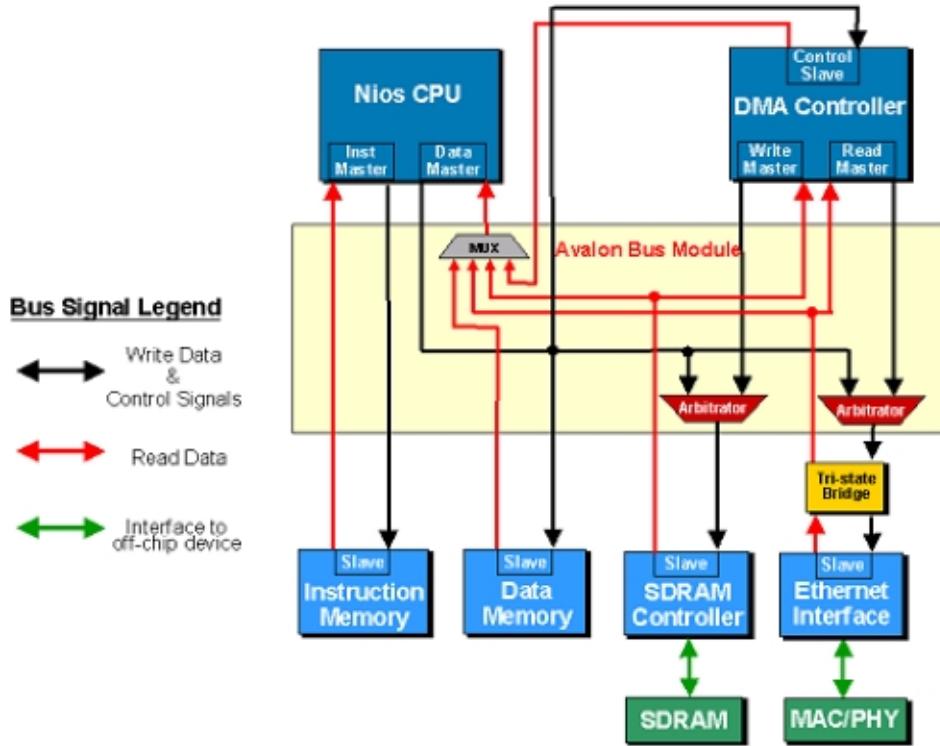

| 3.2. Sistema típico Avalon . . . . .                                                | 35 |

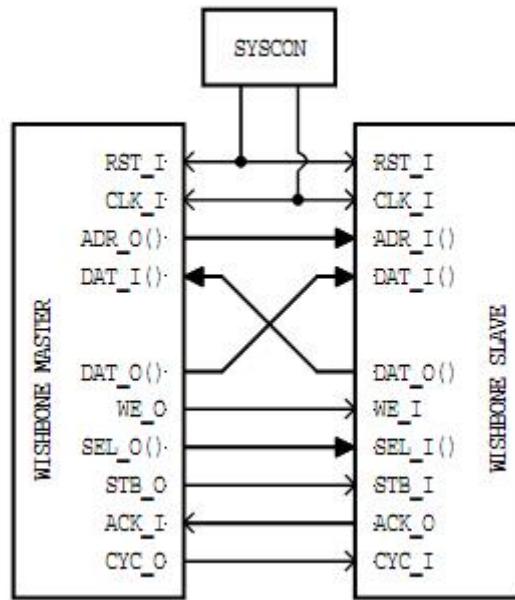

| 3.3. Interconexión Punto a Punto Wishbone . . . . .                                 | 36 |

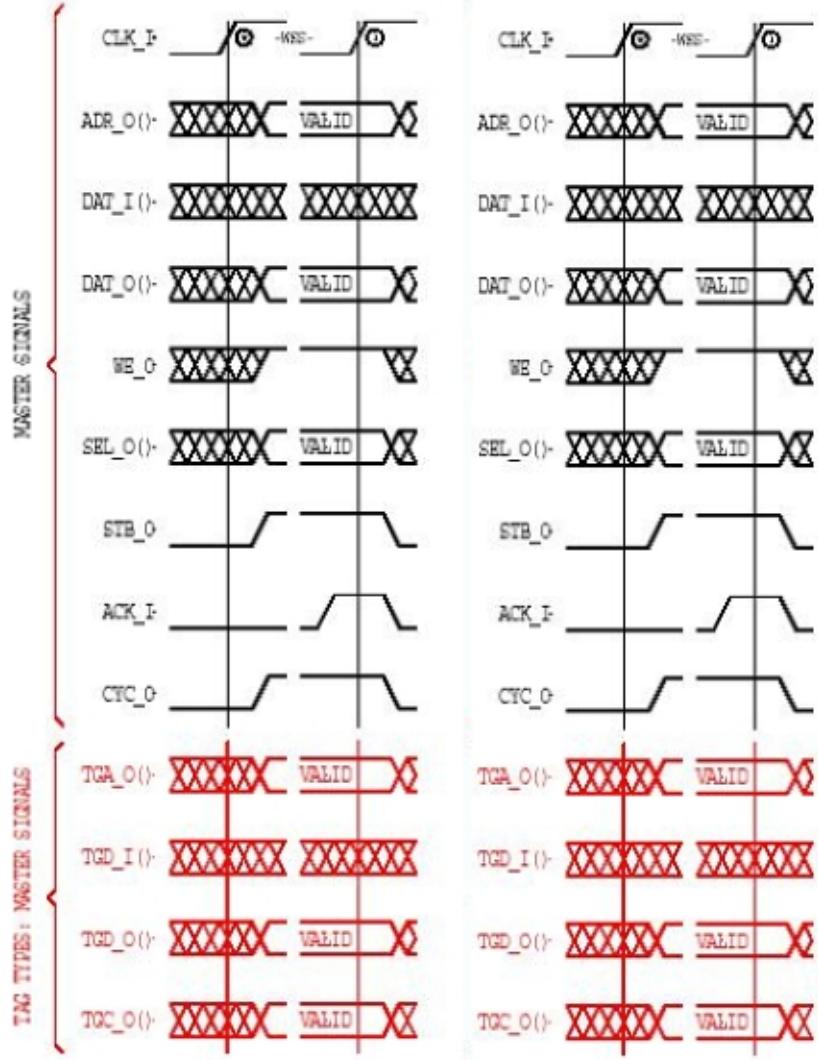

| 3.4. Ciclos Read/Write Simples . . . . .                                            | 37 |

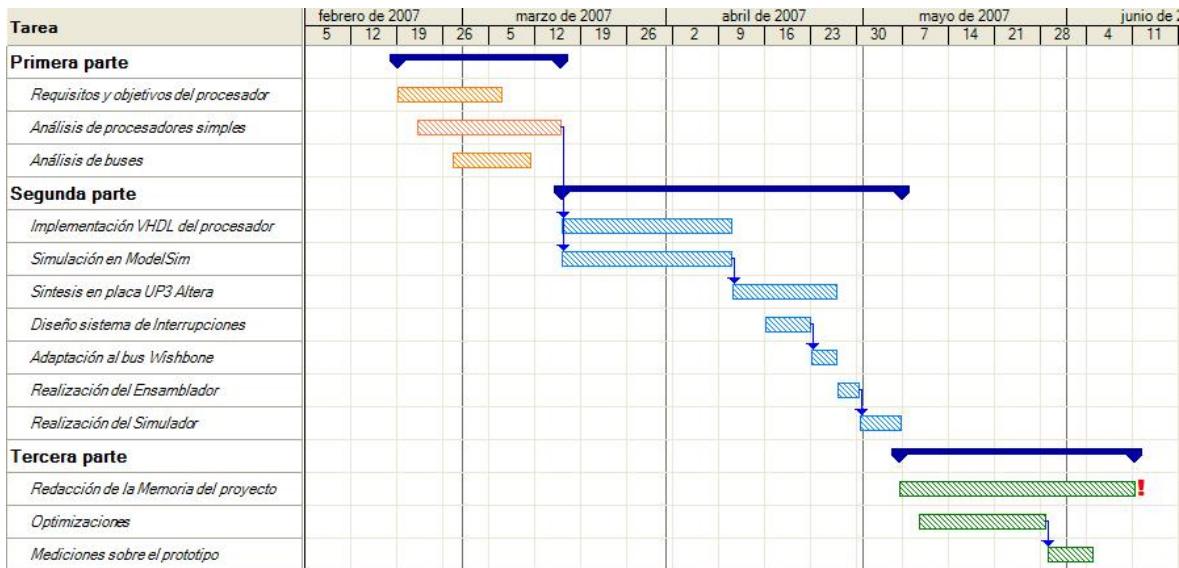

| 4.1. Diagrama de Gantt que muestra la planificación del proyecto . . . . .          | 41 |

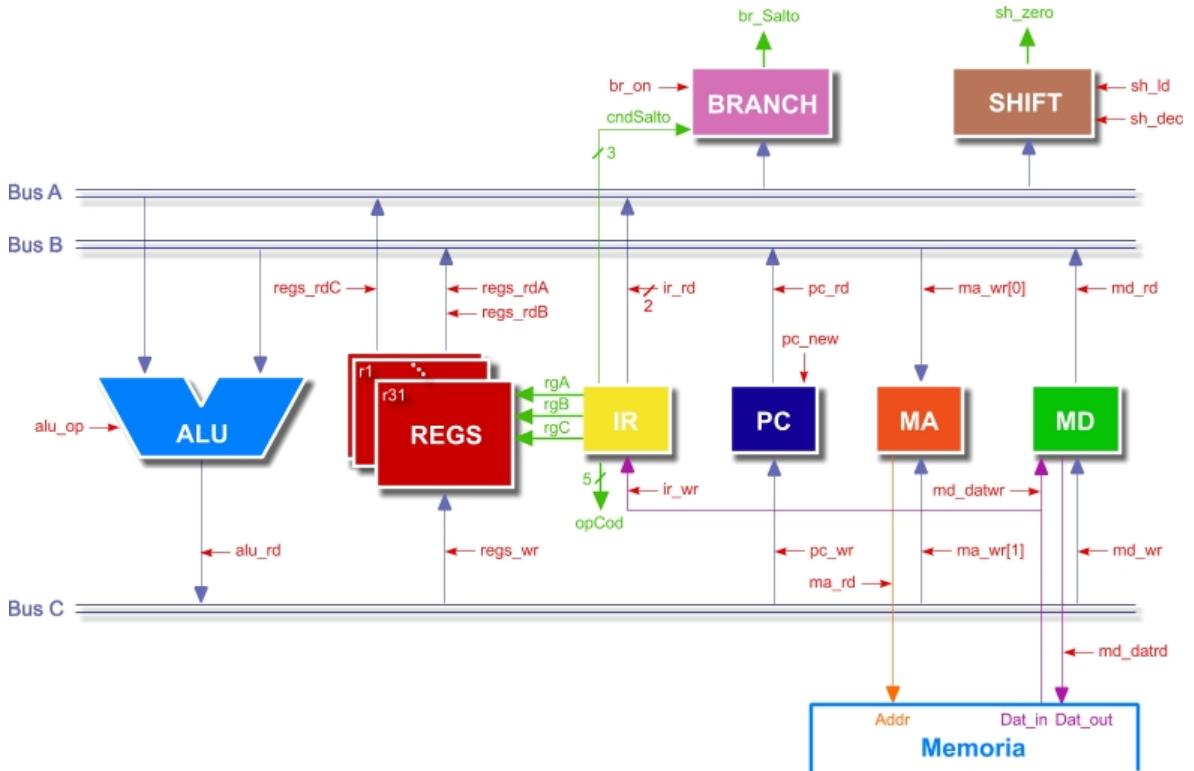

| 5.1. Arquitectura de la Unidad de Proceso del Procesador SR3C . . . . .             | 47 |

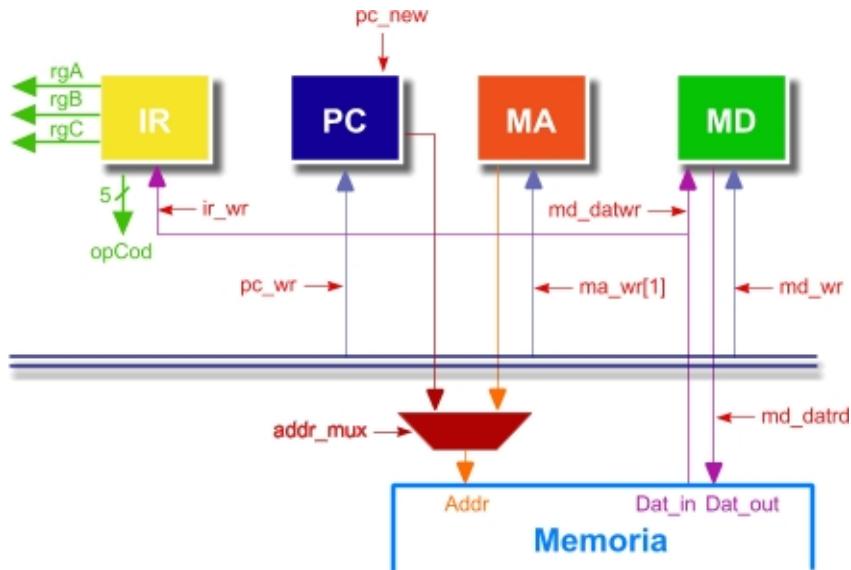

| 5.2. UP modificada para la búsqueda de instrucciones en un ciclo de reloj . . . . . | 53 |

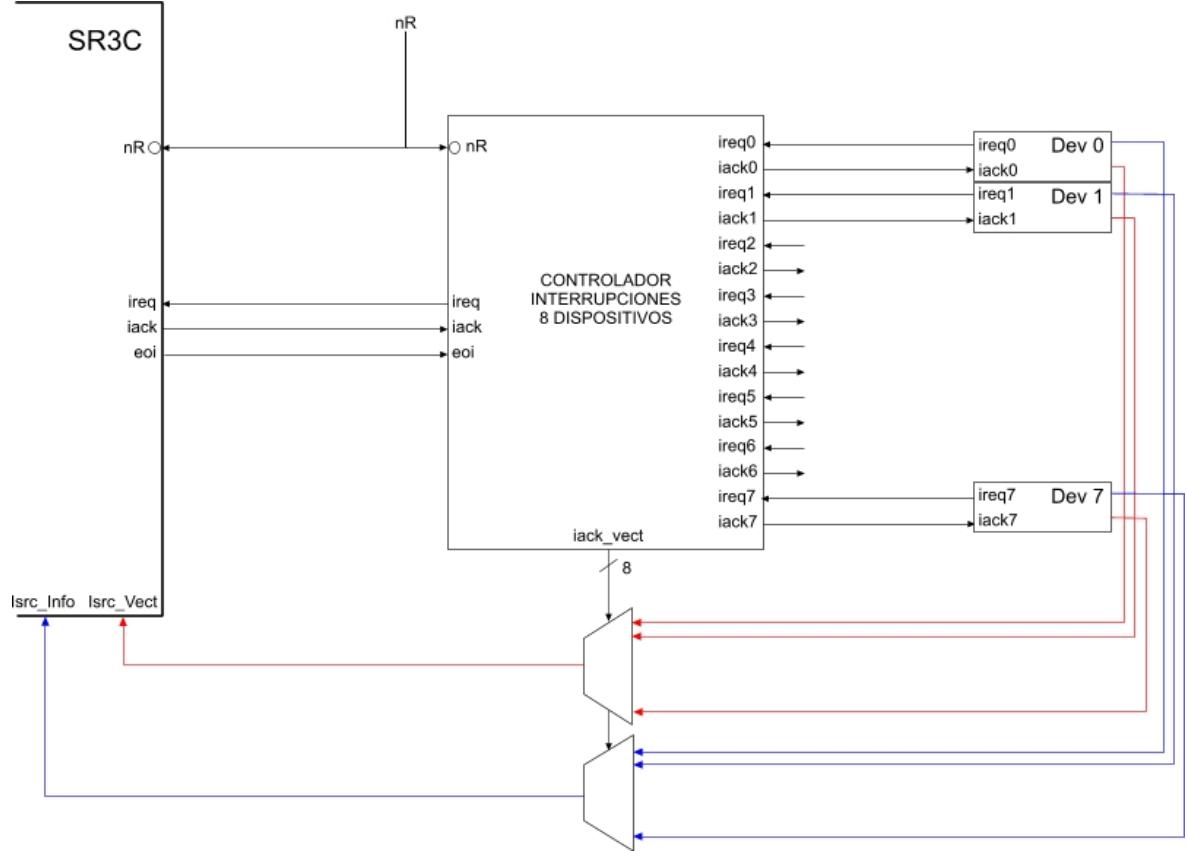

| 5.3. Esquema de conexiones del controlador de interrupciones . . . . .              | 56 |

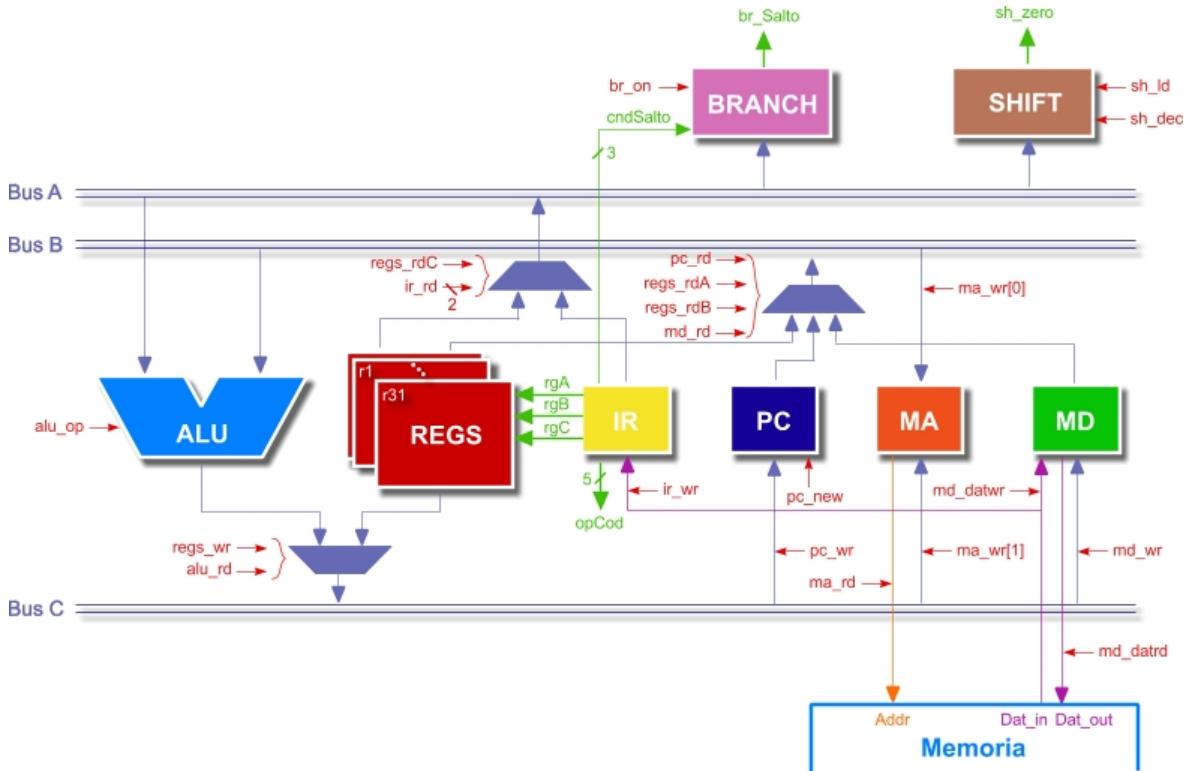

| 5.4. Arquitectura de la UP del Procesador SR3C con Multiplexores . . . . .          | 57 |

| 5.5. Diagrama de Conexiones y de tiempos de la memoria síncrona FASM RAM . . . . .  | 59 |

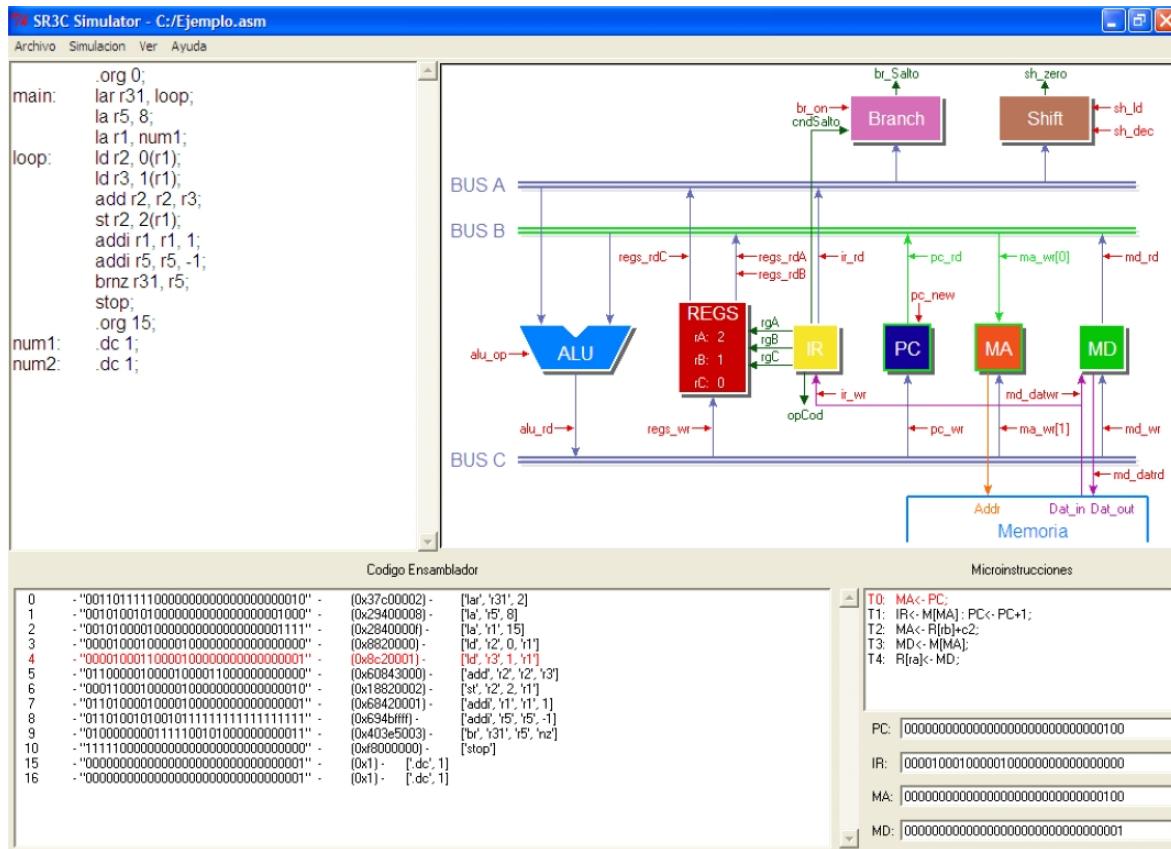

| 5.6. Captura de pantalla del Simulador del procesador SR3C . . . . .                | 60 |

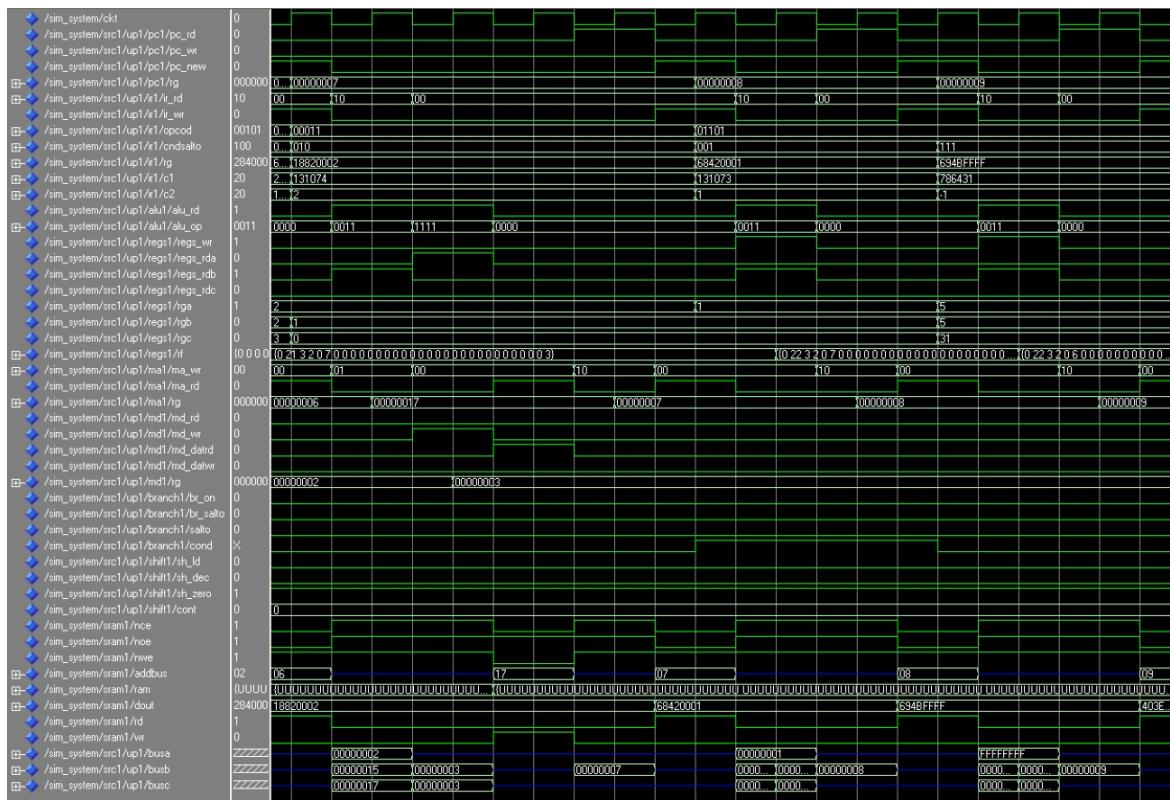

| 6.1. Diagrama temporal de la simulación algoritmo de Fibonacci . . . . .            | 64 |

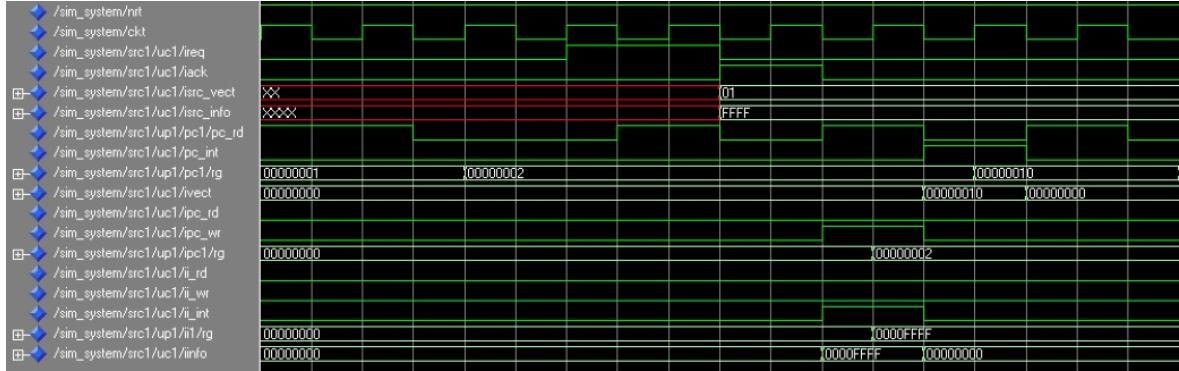

| 6.2. Diagrama temporal de la simulación de una interrupción . . . . .               | 65 |

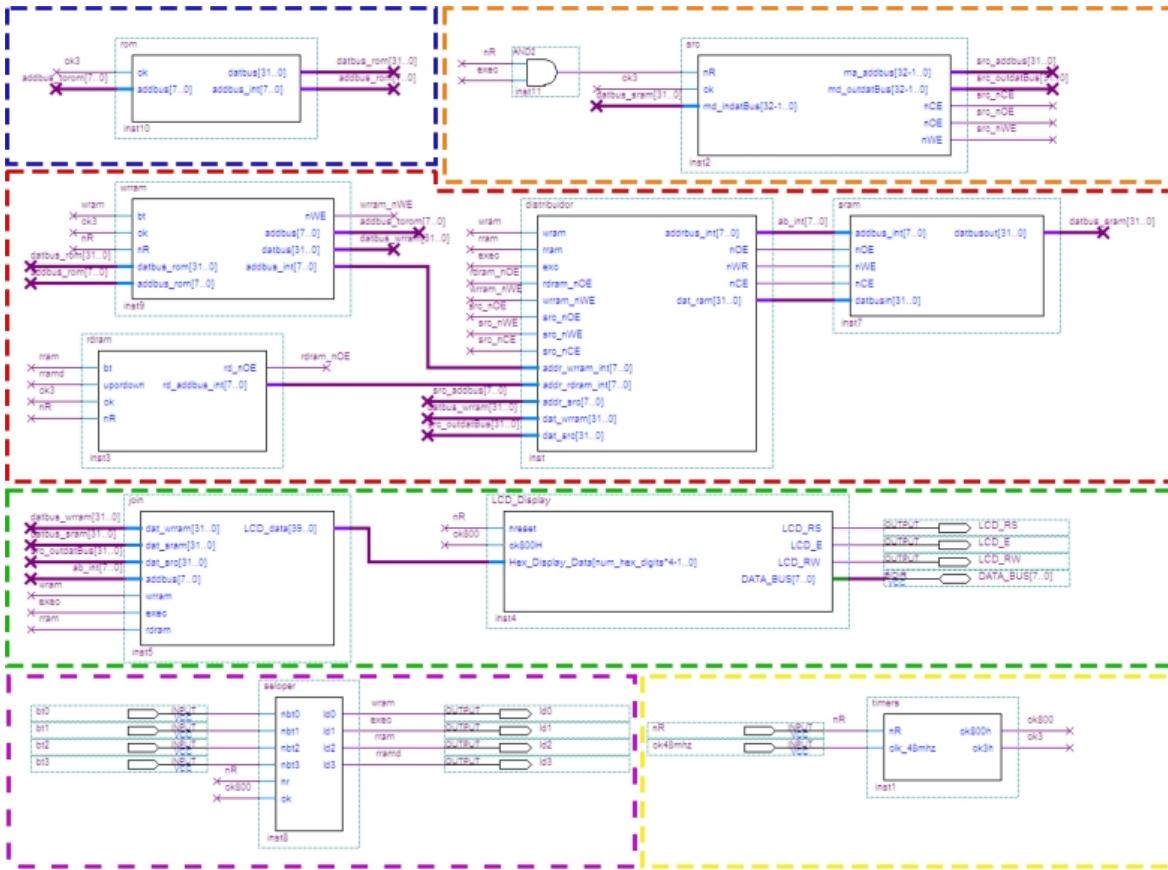

| 6.3. Diagrama del Sistema sintetizado en la FPGA . . . . .                          | 66 |

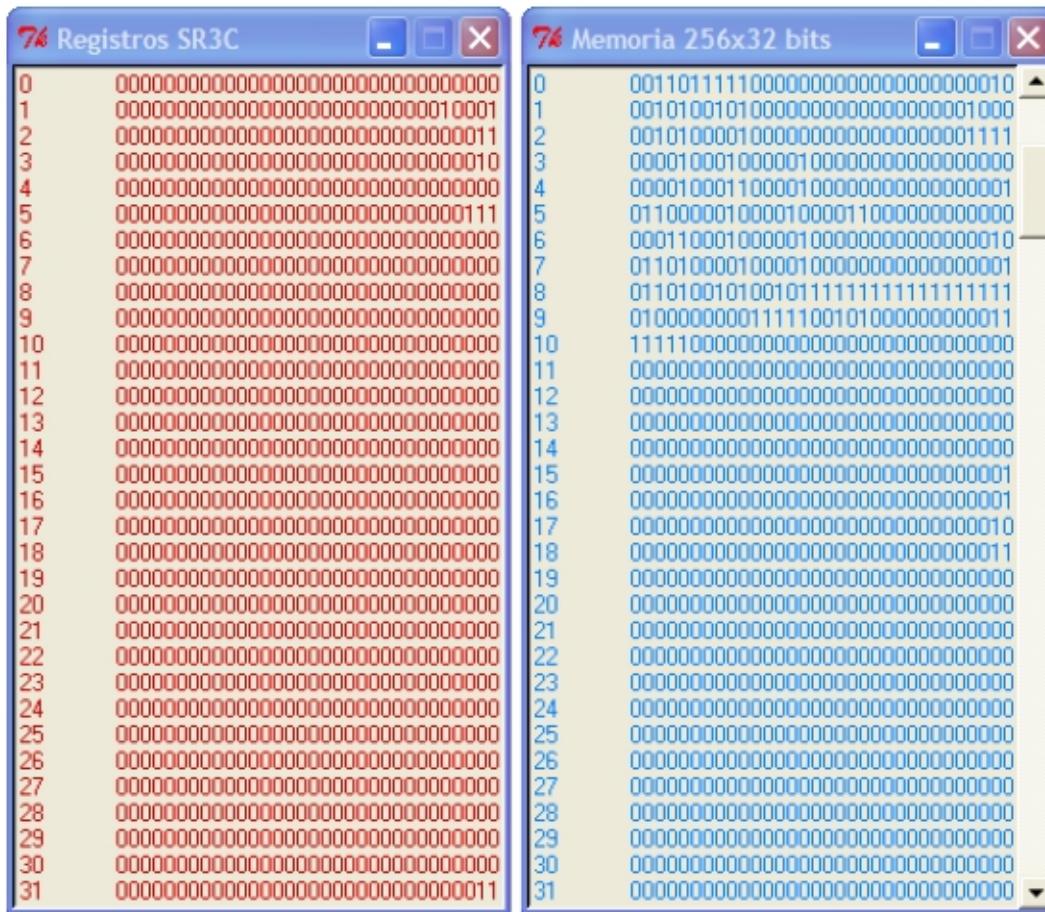

| C.1. Ventanas que muestran el contenido de la memoria y de los registros . . . . .  | 88 |

# Índice de cuadros

|      |                                                                             |    |

|------|-----------------------------------------------------------------------------|----|

| 2.1. | Formato instrucciones DLX . . . . .                                         | 15 |

| 2.2. | Formato instrucciones MicroBlaze <sup>TM</sup> . . . . .                    | 17 |

| 2.3. | Formato instrucciones Nios <sup>®</sup> II . . . . .                        | 22 |

| 2.4. | Formato instrucciones LatticeMico32 <sup>TM</sup> . . . . .                 | 26 |

| 2.5. | Formato instrucciones SRC . . . . .                                         | 27 |

| 2.6. | Resumen procesadores analizados . . . . .                                   | 30 |

| 6.1. | Resultados de síntesis en FPGA obtenidos . . . . .                          | 67 |

| 6.2. | Ciclos requeridos para la ejecución de las instrucciones del SR3C . . . . . | 68 |

| A.1. | Busqueda de Instrucciones . . . . .                                         | 74 |

| A.2. | Instrucciones de Carga . . . . .                                            | 75 |

| A.3. | Instrucciones de Almacenamiento . . . . .                                   | 76 |

| A.4. | Instrucciones Aritméticas . . . . .                                         | 77 |

| A.5. | Instrucciones de Salto . . . . .                                            | 78 |

| A.6. | Instrucciones de Desplazamiento . . . . .                                   | 79 |

| A.7. | Otras Instrucciones . . . . .                                               | 80 |

| A.8. | Instrucciones de Interrupción . . . . .                                     | 81 |

# Capítulo 1

## Introducción

Existen dos clases principales de microprocesadores: los microprocesadores computacionales de propósito general utilizados en servidores y ordenadores personales, y los microprocesadores especializados para sistemas empotrados y aplicaciones system-on-chip (SoC). Los primeros pueden contener uno o varios núcleos homogéneos utilizando memoria principal externa. Los últimos, en cambio, normalmente combinan uno o varios núcleos heterogéneos utilizando memoria en el interior del propio chip.

Aunque la mayoría de investigaciones actuales se centran en los procesadores computacionales de propósito general, éstos representan solo una pequeña parte del total de procesadores fabricados cada año. De hecho, los procesadores especializados para aplicaciones empotradas son los más abundantes hoy en día y representan la mayor parte de procesadores fabricados anualmente[16].

En algunos sectores del mercado de SoC, el costoso proceso de personalización de procesadores de alto rendimiento es difícil de justificar, por lo que muchas compañías prefieren diseñar y utilizar su propio procesador. Además, como los diseñadores a menudo conocen el tamaño necesario para almacenar los programas y los datos en tiempo de diseño, pueden incluir las estructuras de memoria necesarias, ajustándose al máximo.

Con múltiples procesadores (algunos especializados, otros genéricos), múltiples estructuras de memoria y controladores especializados, uno de los grandes objetivos de los SoC es diseñar una estructura de buses robusta que pueda cumplir con los requisitos de comunicaciones y permita una integración y verificación de sistemas complejos.

En la actualidad, algunas empresas suelen comprar procesadores genéricos como propiedades intelectuales (IP) para integrarlos dentro de sus diseños. Uno de los procesadores más populares en este sentido es el ARM 7 TDMA [17]. Este procesador bajo licencia es de 32 bits y de arquitectura RISC (*Reduced Instruction Set Computer*). Su éxito viene provocado en parte por su diseño compacto y en parte por la gran cantidad de componentes IP disponibles en el mercado que utilizan el mismo bus AMBA que el

procesador.

La filosofía de diseño RISC ya hace tiempo que se ha establecido como un concepto importante en el diseño de procesadores de propósito general [27]. Las principales características de la arquitectura RISC son la separación de las instrucciones de acceso a memoria de las operaciones aritméticas, además de una ejecución de instrucciones en pipeline. Estas características hacen posible que los procesadores RISC puedan trabajar a altas frecuencias de reloj y por lo tanto que consigan un gran rendimiento. Esta filosofía de diseño se usa como concepto básico en el diseño de microcontroladores y procesadores de propósito general.

En general, las arquitecturas RISC utilizan la técnica del pipeline todo lo posible para intentar paralelizar el máximo de tareas posibles, utilizando así los recursos hardware del procesador eficientemente. Esto permite trabajar con frecuencias de reloj más altas y por lo tanto proporcionar un mayor rendimiento. En los procesadores utilizados para servidores y ordenadores personales podemos observar arquitecturas de pipeline de diez, veinte y de incluso, más de treinta etapas. Pero el uso de un pipeline de muchas etapas puede tener algún inconveniente. Por ejemplo cuando se ejecuta una instrucción de salto, el pipeline se rompe y debe ser rellenado de nuevo con la instrucción a la que apuntaba la instrucción de salto. Cuantas más etapas tenga el pipeline más ciclos de reloj serán necesarios para volver a llenar el pipeline. En los sistemas empotrados, los bucles en los programas suelen ser relativamente cortos y suelen ser procesados más veces que en aplicaciones ofimáticas. Algunas investigaciones han demostrado que las instrucciones de salto pueden llegar al 30 % del total de instrucciones ejecutadas [15].

Este proyecto tiene como objetivo el análisis de prestaciones de procesadores RISC de bajo coste y el diseño de un procesador RISC simple para aplicaciones de propósito general relacionadas con la adquisición y el proceso simple de datos. El procesador propuesto debe poder ser ampliado en el futuro añadiéndole un pipeline, que siguiendo con la misma filosofía de simplicidad, tendrá que ser de pocas etapas. Además también se ha de poder acoplar fácilmente a sistemas más complejos mediante el cumplimiento de algún estándar de buses para SoC.

A continuación se muestran las características más importantes que el procesador ha de cumplir:

- Tiene que ser simple. Sus principales aplicaciones serán las relacionadas con la adquisición y el proceso simple de datos.

- El conjunto de instrucciones, a su vez, debe ser también simple y eficiente.

- Ha de poseer una interfaz compatible con algún estándar de buses.

- Se simulará y sintetizará mediante el lenguaje de descripción de hardware VHDL en una FPGA (*Field Programmable Gate Array*). Al ser un soft-core podrá utilizarse para aplicaciones reales en SoC.

- Se ha de acompañar con un simulador para poder utilizarlo como plataforma educativa [28].<sup>1</sup>

Los capítulos 2 y 3 proporcionan una visión del *state-of-the-art* sobre procesadores RISC simples y arquitecturas de buses para sistemas SoC actuales. Dado este *state-of-the-art* los siguientes capítulos ya se centran propiamente en el proyecto. De esta manera, en el capítulo 4 se realiza un análisis de sus prestaciones, además de comentar la viabilidad y costes del proyecto. En el capítulo 5 se describe el procesador implementado, y para finalizar, en los capítulos 6 y 7 se realiza un estudio de los resultados obtenidos y una conclusión, respectivamente. Al final del documento también se pueden encontrar varios Apéndices a los que se les irá realizando referencia a lo largo de este documento.

---

<sup>1</sup> Actualmente existen muchos procesadores descritos mediante lenguajes de descripción de hardware (normalmente Verilog o VHDL) sintetizables mediante FPGAs (se puede ver una extensa lista en [18] o en [9]). Sin embargo son muy pocos los procesadores que están orientados a ámbitos educativos, pero menos aún los que pueden utilizarse tanto para aplicaciones reales en SoC como para el ámbito educativo.

# Capítulo 2

## Análisis de procesadores simples

En este capítulo se lleva a cabo una breve descripción de los procesadores RISC simples más populares que existen actualmente y se realiza una comparación entre ellos a fin de ver sus principales ventajas y carencias.

### 2.1. El Procesador DLX

El procesador DLX es un procesador teórico basado en arquitectura RISC diseñado por Hennessy y Patterson e introducido por primera vez en [20]. Cabe destacar que sus autores fueron a su vez los diseñadores principales de las arquitecturas MIPS y Berkeley RISC respectivamente.

El DLX es básicamente un procesador MIPS revisado y simplificado con una arquitectura simple de carga/almacenamiento (*load/store*) de 32 bits. Pensado principalmente para propósitos educativos, se utiliza ampliamente en cursos de nivel universitario sobre arquitectura de computadores.

Sus diseñadores se basaron en las observaciones sobre las primitivas más frecuentemente utilizadas en los programas para realizar su arquitectura. Al igual que la mayoría de procesadores de carga/almacenamiento el DLX hace enfasis en:

- Un sencillo repertorio de instrucciones de carga/almacenamiento.

- Diseño de segmentación (*pipelining*) eficiente.

- Un repertorio de instrucciones fácilmente decodificables.

- Eficiencia como objeto del compilador.

El procesador tiene 32 registros de propósito general (GPR) de 32 bits; el valor de R0 siempre es 0. Adicionalmente, hay un conjunto de registros de punto flotante (FPR),

que pueden utilizarse como 32 registros de simple precisión (32 bits), o como parejas par-impar que contienen valores de doble precisión. Se pueden realizar operaciones en simple y doble precisión. También existe un conjunto de registros especiales utilizados para acceder a la información sobre su estado, algunos de los cuales se pueden transferir a y desde registros enteros.

La memoria es direccionable por bytes en el modo «Big Endian» con una dirección de 32 bits. Todas las referencias a memoria se realizan a través de cargas o almacenamientos entre memoria y los GPR o FPR. Todos los accesos a memoria deben estar alineados. También hay instrucciones para transferencia entre un FPR y un GPR.

Todas las instrucciones son de 32 bits y deben estar alineadas. Hay cuatro clases de instrucciones:

- Cargas y almacenamientos. Cualquiera de los registros de propósito general o de punto flotante se pueden cargar o almacenar, excepto cargar R0 que no tiene efecto. Hay un modo único de direccionamiento, registro base + desplazamiento de 16 bits con signo. Las cargas de media palabra y de byte ubican el objeto cargado en la parte inferior del registro.

- Operaciones de ALU. Todas las instrucciones de la ALU son instrucciones de registro-registro. Las operaciones incluyen operaciones aritméticas sencillas y operaciones lógicas: suma, resta, AND, OR, XOR, y desplazamientos (*shifts*). Se proporcionan las formas inmediatas de todas estas instrucciones, con un valor inmediato con signo-extendido a 16 bits. También hay instrucciones de comparación, que comparan dos registros. Si la condición es cierta, estas instrucciones colocan un 1 en el registro destino, en otro caso colocan el valor 0.

- Saltos y bifurcaciones. El control se realiza mediante un conjunto de bifurcaciones y saltos. Las tres instrucciones de bifurcación están diferenciadas por las dos formas de especificar la dirección destino y por si existe o no existe enlace. Dos bifurcaciones utilizan un desplazamiento (*offset*) con signo de 26 bits sumado al contador de programa; las otras dos instrucciones de bifurcación especifican un registro que contiene la dirección destino. Hay dos tipos de bifurcación: bifurcación simple, y bifurcación y enlace (utilizada para llamadas a procedimientos). La última coloca la dirección de retorno en el registro R31. Todos los saltos son condicionales. La condición de salto se especifica en la instrucción.

- Operaciones en punto flotante. Las instrucciones de punto flotante manipulan los registros de punto flotante e indican si la operación a realizar es en simple o en doble precisión. Las operaciones de punto flotante son suma, resta, multiplicación y división. El formato de punto flotante es el del IEEE 754.

| Formato       | Bits      |    |     |    |     |                              |    |    |    |           |      |   |

|---------------|-----------|----|-----|----|-----|------------------------------|----|----|----|-----------|------|---|

|               | 31        | 26 | 25  | 21 | 20  | 16                           | 15 | 11 | 10 | 6         | 5    | 0 |

| <b>Tipo I</b> | código op |    | rs1 |    | rd  |                              |    |    |    | inmediato |      |   |

| <b>Tipo R</b> | código op |    | rs1 |    | rs2 |                              | rd |    |    |           | func |   |

| <b>Tipo J</b> | código op |    |     |    |     | desplazamiento añadido al PC |    |    |    |           |      |   |

Cuadro 2.1: Formato instrucciones DLX

Todas estas instrucciones se pueden separar en tres tipos de instrucciones (en el Cuadro 2.1 se puede observar sus formatos):

- Clase I (*inmediato*). Estas instrucciones especifica un registro fuente, un registro destino y un valor inmediato de 16 bits.

- Clase R (*registro*). Estas instrucciones especifican tres registros (dos registros fuente donde se encuentran los operandos y un registro destino para el resultado de la operación).

- Clase J (*salto*). Estas instrucciones únicamente especifican un valor inmediato de 26 bits que es usado para calcular la dirección de destino.

Los códigos de instrucción contenidos en las instrucciones son de 6 bits, lo que hace un total de 64 posibles instrucciones básicas. Hacen falta 5 bits para seleccionar cada uno de los 32 registros de propósito general que incorpora el procesador.

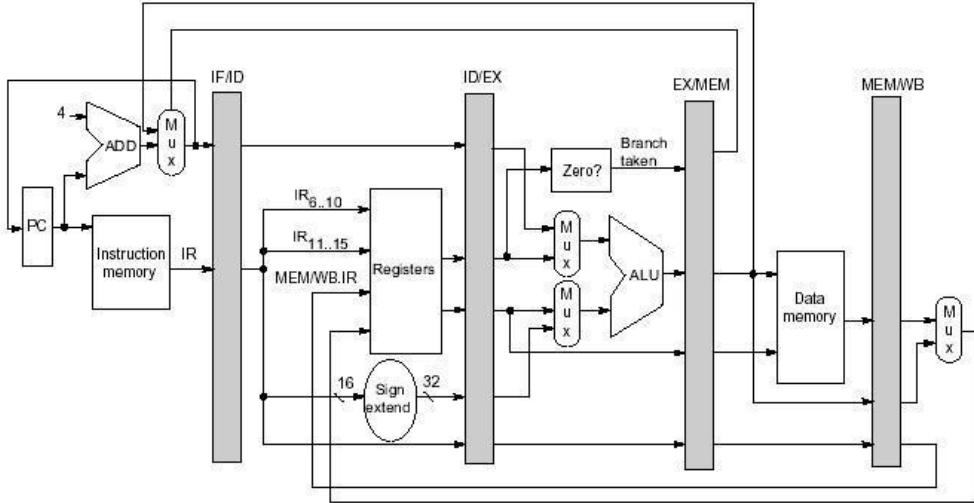

El DLX, al igual que el MIPS, basa su rendimiento en el uso del pipeline. En el caso del DLX el pipeline se divide en cinco etapas (Figura 2.1):

- IF - Unidad de obtención de instrucción.

- ID - Unidad de decodificación de instrucción. Esta unidad toma la instrucción del IF, y extrae el código de operación y los operandos.

- EX - Unidad de ejecución. Ejecuta la instrucción, normalmente referido como ALU (Unidad Aritmético Lógica).

- MEM - Unidad de acceso a memoria. Obtiene datos de la memoria, controlada desde el ID y el EX.

- WB - Unidad de WriteBack o de almacenamiento.

Este procesador ha sido utilizado por otros autores en sus libros para explicar conceptos relacionados con la arquitectura de computadores o el diseño de sistemas digitales, como en el caso de Ashenden, que en su libro [13] describe, mediante lenguaje VHDL, el procesador DLX.

Figura 2.1: Arquitectura del procesador DLX

Existe una aproximación más sencilla de este procesador denominada DLXS (la S proviene de Stuttgart) diseñada por Gumm [19] y utilizada para propósitos educativos en la universidad de Stuttgart [14].<sup>1</sup> La principal diferencia del DLXS respecto al DLX original es que no incorpora pipeline, simplificando enormemente su arquitectura y funcionamiento. Esta basado en una arquitectura de tres buses y la mayoría de instrucciones se ejecutan en cinco ciclos.

## 2.2. El Procesador MicroBlaze™

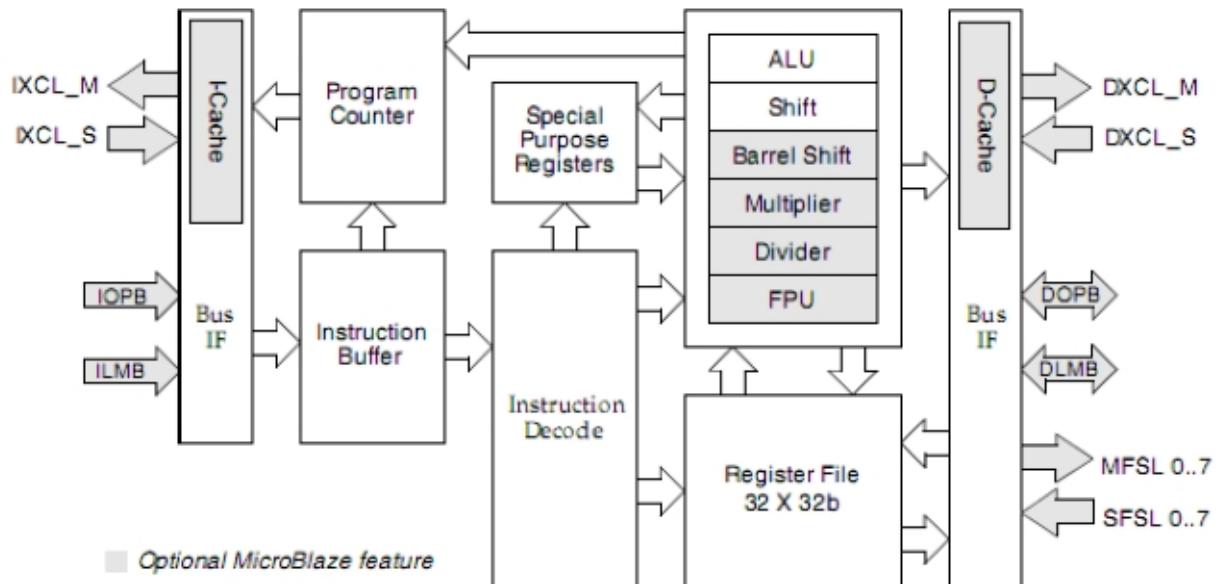

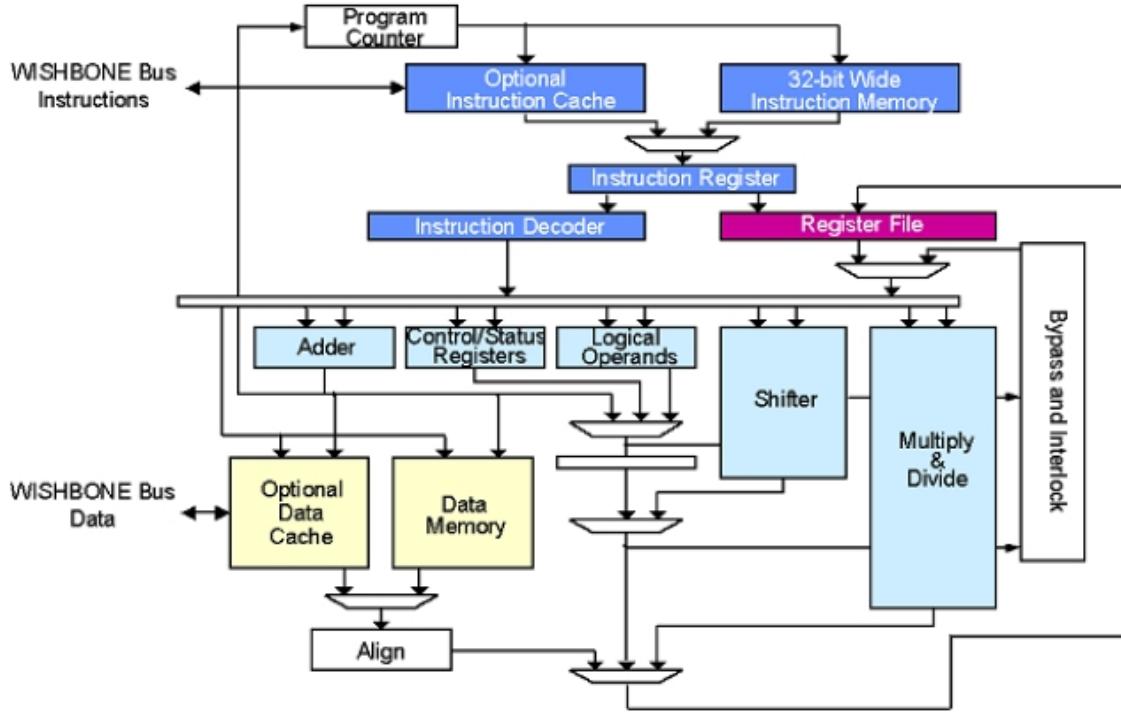

El procesador MicroBlaze™[8] es un procesador soft-core de arquitectura RISC de 32 bits diseñado por Xilinx® y optimizado para funcionar en sus FPGAs. Se puede observar un esquema de su arquitectura en la Figura 2.2.

Este procesador permite un cierto grado de configuración dependiendo de las necesidades. Las características fijas que incluye el procesador son las siguientes:

- 32 registros de propósito general de 32 bits.

- Instrucciones de 32 bits con tres operandos y dos tipos de direccionamiento.

- Bus de direcciones de 32 bits.

- Pipeline de 3 o 5 etapas.

<sup>1</sup>Además de utilizarse para propósito educativo, el procesador DLXS se ha llegado a sintetizar en un ASIC [12].

Figura 2.2: Arquitectura del procesador MicroBlaze<sup>TM</sup>

Además de las características fijas, el procesador MicroBlaze se puede configurar para habilitar nuevas funcionalidades. Las versiones antiguas de este procesador solo soportan algunas de estas características adicionales, en cambio, la última versión de este procesador soporta todas las características adicionales. Por eso, Xilinx recomienda el uso de la última versión para la realización de nuevos proyectos.

MicroBlaze utiliza el formato de representación de datos «Big-endian». Soporta trabajar con datos de 8, 16 y 32 bits.

Las instrucciones de este procesador son de 32 bits y se pueden clasificar en dos tipos (en el Cuadro 2.2 se puede observar sus formatos):

- Instrucciones de tipo A. Estas instrucciones especifican dos registros fuente y un registro destino.

- Instrucciones de tipo B. Estas instrucciones especifican un registro fuente y un operando inmediato de 16 bits, el cual se puede extender a 32 bits precediendo a la instrucción con una instrucción especial llamada IMM). Las instrucciones de tipo B también especifican un registro destino.

| Formato | Bits      |   |    |    |     |    |     |    |    |           |  | 31 |

|---------|-----------|---|----|----|-----|----|-----|----|----|-----------|--|----|

|         | 0         | 5 | 6  | 10 | 11  | 15 | 16  | 20 | 21 |           |  |    |

| Tipo A  | código op |   | rd |    | rs1 |    | rs2 |    |    | func      |  |    |

| Tipo B  | código op |   | rd |    | rs1 |    |     |    |    | inmediato |  |    |

Cuadro 2.2: Formato instrucciones MicroBlaze<sup>TM</sup>

Las instrucciones, a su vez, se pueden clasificar según su funcionalidad en las siguientes categorías:

- Instrucciones aritméticas.

- Instrucciones lógicas.

- Instrucciones de salto.

- Instrucciones de carga/almacenamiento.

- Instrucciones especiales.

El procesador MicroBlaze incorpora 32 registros de propósito general de 32 bits y hasta 18 registros de propósito especial, dependiendo de las opciones de configuración elegidas. El valor del registro R0 siempre es 0. El registro R14 se utiliza para almacenar la dirección de retorno tras tratar una interrupción. Si el procesador se configura de forma que éste soporte las excepciones hardware, en el registro R17 se almacena la dirección de la instrucción siguiente a la que ha causado la excepción. El registro especial MSR (*Machine Status Register*) contiene bits de control y estado del procesador.

La ejecución de las instrucciones del procesador se realiza a través de un pipeline. Cada etapa del pipeline tarda un ciclo de reloj en ejecutarse para la mayoría de instrucciones. Por lo tanto, el número de ciclos necesarios para completar cada instrucción es igual al número de etapas del pipeline. En definitiva, en cada ciclo de reloj se completa una instrucción. Únicamente unas cuantas instrucciones requieren varios ciclos de reloj para completar alguna etapa del pipeline. Para solucionar este problema el pipeline se paraliza.

Cuando se utiliza una memoria lenta, la búsqueda de instrucciones puede requerir varios ciclos. Esta latencia adicional afecta directamente a la efectividad del pipeline. El procesador MicroBlaze implementa un buffer de instrucciones buscadas que reduce el impacto producido por esta latencia. De esta forma, cuando el pipeline requiere más de un ciclo para realizar la etapa de ejecución, el buffer de instrucciones se continúa llenando secuencialmente. Cuando el pipeline acaba la etapa de ejecución, la etapa de búsqueda puede cargar una nueva instrucción directamente del buffer sin verse afectado por la latencia de la memoria.

Cuando se habilita la optimización de área, el pipeline se divide en tres etapas para minimizar el coste de hardware. En cambio cuando se deshabilita, el pipeline se divide en cinco etapas para optimizar el rendimiento.

Este procesador está implementado con una arquitectura de memoria tipo Harvard, lo que significa que los accesos a instrucciones y a datos se realizan en espacios de direccionamiento diferentes. Cada espacio de direccionamiento es de 32 bits. Los datos deben estar alineados en memoria, aunque el procesador está configurado para soportar

Figura 2.3: Arquitectura del procesador PicoBlaze<sup>TM</sup>

excepciones de no alineamiento. El procesador no separa los accesos a datos de memoria de los accesos a datos de E/S (Entrada/Salida), es decir, el procesador utiliza E/S mapeada en memoria.

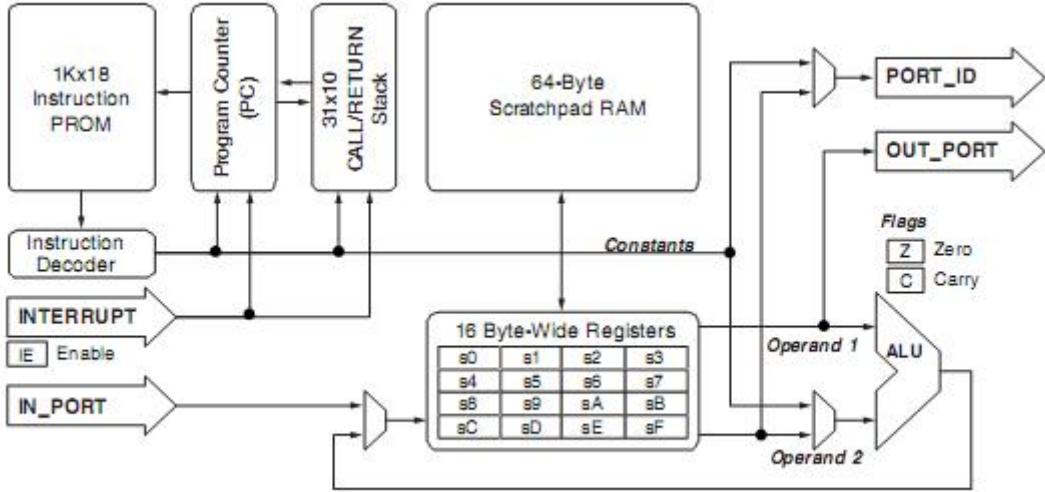

Xillinx también posee otro procesador mucho más sencillo y menos potente llamado PicoBlaze<sup>TM</sup>.

El procesador PicoBlaze [5], es un microcontrolador compacto basado en arquitectura RISC de 8 bits, diseñado y optimizado para ser sintetizado en las FPGAs de la propia empresa. El procesador sin embargo es de código abierto y se proporciona en lenguaje VHDL sintetizable, para su uso en FGPAs Xillinx.

Xillinx también proporciona un ensamblador, un entorno gráfico de desarrollo integrado, y un simulador gráfico. PicoBlaze consigue un rendimiento de entre 44 y 100 MIPS (Millones de instrucciones por segundo) dependiendo de la familia de FPGAs en las que se sintetice.

El procesador incluye 16 registros de 8 bits cada uno, puede ejecutar programas de hasta 1024 instrucciones y posee sistema de interrupciones. En la Figura 2.3 se puede observar su arquitectura.

### 2.3. El Procesador Nios<sup>®II</sup>

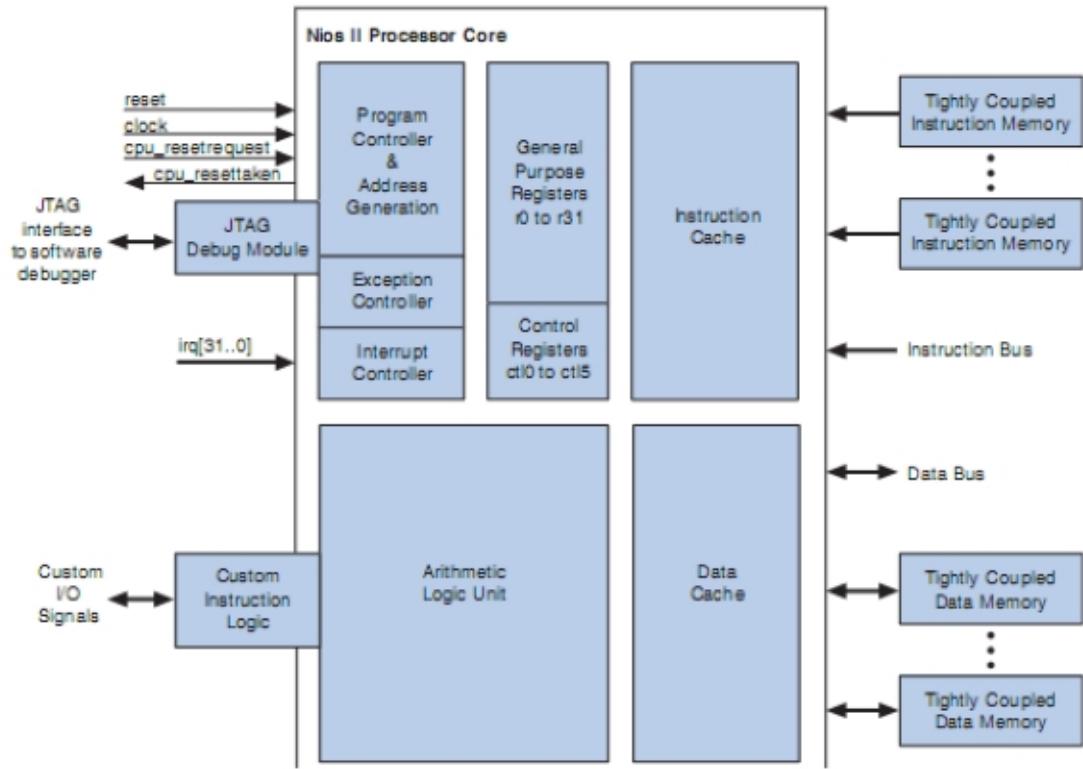

El procesador Nios<sup>®II</sup> [10] es un procesador de arquitectura RISC de 32 bits y soft-core, desarrollado por el fabricante de FPGAs Altera<sup>®</sup> y optimizado para funcionar en sus FPGAs. En la Figura 2.4 se puede ver un esquema de su arquitectura.

Un sistema Nios II es equivalente a un microcontrolador o a un «ordenador on-

Figura 2.4: Arquitectura del procesador Nios®II

chip», que incluye un procesador y una combinación de periféricos y memoria en un único chip.

Las principales características del procesador son las siguientes:

- Arquitectura RISC, conjunto de instrucciones y espacio de direcciones de 32 bits.

- 32 Registros de propósito general de 32 bits.

- Soporte para 32 fuentes externas de interrupción.

- Instrucciones de multiplicación y división de 32 bits.

- Instrucciones dedicadas para computo de productos de 64 y 128 bits de números en punto flotante.

- Incorpora un barrel shifter.

- Proporciona acceso a múltiples periféricos dentro del propio chip e interfaces para memorias y periféricos externos.

- Rendimiento de hasta 250 DMIPS (*Dhrystone Million Instructions Per Second*).

El procesador Nios II es un procesador soft-core configurable. Esto significa que se le pueden añadir funcionalidades aumentando su rendimiento o quitárselas disminuyendo

su área, según las necesidades del sistema.

Existen tres configuraciones básicas del procesador que a su vez se pueden personalizar:

- **Nios II/e.** El Nios II/“*economy*” esta diseñado para ocupar el mínimo espacio posible. Como resultado este procesador tiene unas funcionalidades limitadas y algunas configuraciones no están disponibles para este procesador.

- **Nios II/s.** El Nios II/“*standard*” esta diseñado para ocupar un espacio reducido pero manteniendo el rendimiento.

- **Nios II/f.** El Nios II/“*fast*” esta diseñado para obtener el máximo rendimiento. Como resultado este procesador presenta un elevado rango de opciones de personalización.

El procesador incorpora 32 registros de propósito general de 32 bits, además de seis registros de 32 bits de control. La arquitectura está preparada para albergar registros de punto flotante en futuras versiones del procesador.

La arquitectura de este procesador soporta buses de instrucciones y de datos separados, clasificándose así como una arquitectura de tipo Harvard. Ambos buses se implementan como puertos maestros del bus Avalon (ver Capítulo 3). El puerto de datos se conecta a componentes de memoria y a periféricos, mientras que el puerto de instrucciones solo se conecta a componentes de memoria. El Nios II utiliza E/S mapeada en memoria y el formato de representación de datos es «Little-endian». La arquitectura soporta cinco tipos de direccionamiento diferentes.

La ALU de este procesador opera con los datos almacenados en los registros de propósito general. Las operaciones pueden requerir uno o dos operandos y almacenan el resultado en un registro. La ALU de este procesador soporta operaciones aritméticas, de comparación, lógicas y de desplazamiento y rotaciones. Las operaciones más complejas se realizan mediante software utilizando combinaciones de las anteriores. El procesador además soporta instrucciones definidas por el propio usuario, incorporando la lógica necesaria para implementarlas en hardware, a la ALU. Las operaciones en punto flotante están soportadas según la especificación IEEE 754.

Las instrucciones se pueden clasificar de manera similar al procesador DLX, aunque con alguna diferencia (en el Cuadro 2.3 se puede observar sus formatos):

- Clase I (*inmediato*). Estas instrucciones especifican un registro fuente, un registro destino y un valor inmediato de 16 bits.

- Clase R (*registro*). Estas instrucciones especifican tres registros (dos registros fuente donde se encuentran los operandos y un registro destino para el resultado de la operación), además de un campo de extensión de operaciones.

- Clase J (*salto*). Estas instrucciones únicamente especifican un valor inmediato de 26 bits que es usado para calcular la dirección de destino.

| Formato       | Bits      |           |   |    |    |    |    |    |    |    |

|---------------|-----------|-----------|---|----|----|----|----|----|----|----|

|               | 0         | 5         | 6 | 16 | 17 | 21 | 22 | 26 | 27 | 31 |

| <b>Tipo I</b> | código op | inmediato |   |    |    |    | A  | B  |    |    |

| <b>Tipo R</b> | código op | OPX       |   |    | C  | B  |    | A  |    |    |

| <b>Tipo J</b> | código op | inmediato |   |    |    |    |    |    |    |    |

Cuadro 2.3: Formato instrucciones Nios®II

La configuración más sencilla de este procesador (Nios II/e) no incorpora pipeline obteniendo una tasa de 6 ciclos por instrucción en la mayoría de estas. En cambio, tanto la configuración media (Nios II/s), como la configuración más potente (Nios II/f) de este procesador incorporan un pipeline de 5 y 6 etapas, respectivamente. Además estas dos últimas configuraciones también incorporan un predictor de saltos.

Tal como su nombre indica, el Nios II tiene un predecesor: el Nios [4]. Este procesador soporta dos tipos de arquitecturas: de 16 o de 32 bits, aunque ambas trabajan con instrucciones de 16 bits. Incorpora un banco de registros en ventana, disponiendo de un máximo de 512 registros de propósito general. En cada ventana son visibles 24 registros más 8 globales fijos. Esta técnica permite llamadas a subrutinas muy rápidas y eficientes. También incorpora un pipeline de 5 etapas con memorias de instrucciones y datos separadas (Arquitectura Harvard). Al igual que el Nios II también trabaja con el bus Avalon.

## 2.4. El Procesador AVR®32

El procesador AVR®32 [6] pertenece a la compañía Atmel®. Posee una arquitectura innovadora y un diseño completamente síncrono y sintetizable. Se puede integrar en SoC fácilmente debido a que Atmel lo proporciona como IP (*Intellectual Property*). Se ha diseñado para intentar conseguir densidades de código óptimas. Además de bajar los requisitos de la memoria, un código compacto también contribuye a disminuir el consumo.

La arquitectura AVR32 define varias microarquitecturas para intentar así llegar a un rango más amplio de aplicaciones. Cada microarquitectura está especializada en un

Figura 2.5: Pipeline del procesador AVR®32

tipo de aplicación final diferente, dando la opción al diseñador de elegir la que más se adecue a su sistema.

El procesador dispone de 15 registros de propósito general, además del PC (*Program Counter*), el registro de enlace, y el registro SP (*Stack Pointer*). Adicionalmente dispone de un registro donde se almacena el valor de retorno de una función que es usado implícitamente por algunas instrucciones.

Las operaciones de carga y almacenamiento se pueden realizar para tamaños de 8, 16, 32 y 64 bits. Los datos se suelen guardar en formato «Big-endian» y todas las instrucciones son interpretadas así. De todas maneras, para soportar transferencias de datos en formato «Little-endian» el procesador dispone de instrucciones de carga y almacenamiento especiales, capaces de modificar el formato de Big a Little-endian y viceversa. El sistema de memoria soporta accesos no alineados para algunas instrucciones de carga y almacenamiento. Cualquier otro acceso no alineado provoca una excepción de dirección. La E/S es mapeada en memoria.

El conjunto de instrucciones del AVR32 incluye dos tipos de instrucciones: compactas y extendidas. Las instrucciones compactas tienen una longitud de 16 bits mientras que las extendidas tienen una longitud de 32 bits. De esta manera, el procesador posee un conjunto de instrucciones con formatos muy diferentes dependiendo de la instrucción. Además para conseguir una reducción de código, algunas instrucciones tienen múltiples modos de direccionamiento, siendo el compilador el que elige el necesario en cada momento.

La arquitectura AVR32 define un acelerador hardware de Java® como opción, en forma de máquina virtual de Java hardware.

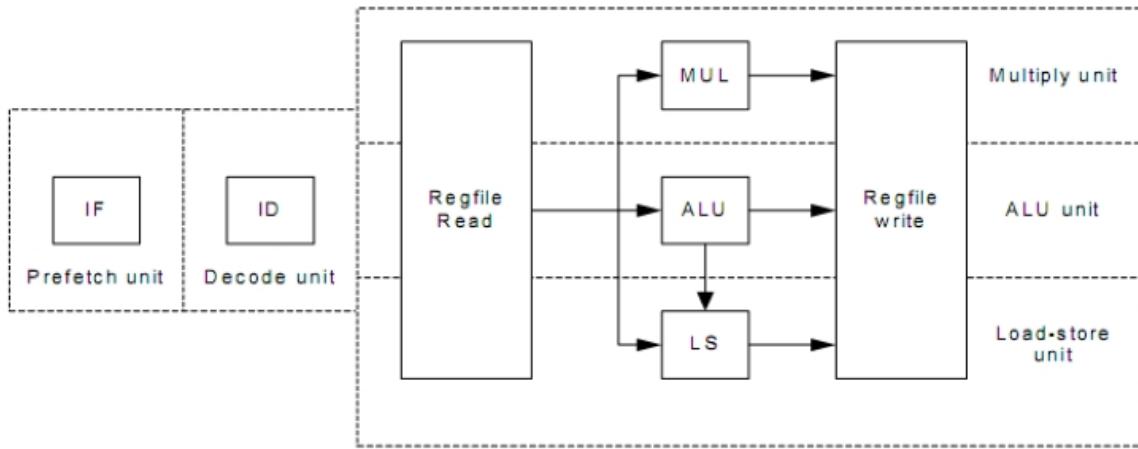

Los últimos procesadores AVR32 disponen de un pipeline de 3 etapas. En la primera etapa, se busca y almacena una instrucción de 32 bits o dos de 16 bits en el buffer de

instrucciones, cada ciclo de reloj. La segunda etapa decodifica la instrucción y genera las señales necesarias para la ejecución de la misma. Por último, la tercera etapa ejecuta la instrucción mediante una de sus tres unidades: ALU, unidad de multiplicación y unidad de carga/almacenamiento. No existen problemas de dependencias de datos en este pipeline, por lo que los registros pueden ser actualizados en el mismo ciclo en que la instrucción se está ejecutando. En la Figura 2.5 se puede ver un esquema del pipeline del AVR32.

Atmel también dispone de procesadores AVR de 8 bits mucho más sencillos que los de la familia AVR32. Estos procesadores de 8 bits trabajan con instrucciones de 16 bits y disponen de 32 registros de propósito general de 8 bits. Al igual que los AVR32, la E/S es mapeada en memoria y pueden direccionar hasta 26 bits de memoria. Disponen de un pipeline sencillo de 2 etapas, pudiendo ejecutar la mayoría de instrucciones en un ciclo de reloj. Al igual que la arquitectura AVR32, esta también dispone de diversas versiones, con rendimientos y características diferentes dependiendo de las aplicaciones en las que se vayan a utilizar.

## 2.5. El Procesador LatticeMico32<sup>TM</sup>

El procesador LatticeMico32<sup>TM</sup> [7] es un procesador soft-core configurable para las FPGAs de la propia empresa Lattice<sup>®</sup>. Combina una arquitectura RISC de 32 bits con 32 registros de propósito general, proporcionando un rendimiento y flexibilidad adecuados para una gran variedad de aplicaciones.

Con buses de instrucciones y de datos separados, este procesador de arquitectura Harvard es capaz de ejecutar una instrucción por ciclo de reloj. Proporciona un conjunto de instrucciones simple, pero eficiente. En la Figura 2.6 se puede ver un esquema de su arquitectura.

Algunas de las características principales de este procesador son las siguientes:

- Arquitectura RISC de 32 bits.

- Instrucciones de 32 bits.

- 32 registros de propósito general.

- Hasta 32 interrupciones externas.

- Caché de instrucciones y de datos opcionales.

- Interfaz de memoria dual (instrucciones y datos) Wishbone (Ver Capítulo 3).

Figura 2.6: Arquitectura del procesador LatticeMico32<sup>TM</sup>

Este procesador utiliza un pipeline de 6 etapas. Incorpora un detector de dependencias *read-after-write* que permite una compactación del código al eliminar las instrucciones *nop*.

Como ya se ha comentado, el procesador incorpora 32 registros de propósito general de 32 bits cada uno. Al igual que en otros procesadores, el registro R0 siempre contiene el valor 0, pero al principio de cada programa el usuario tiene que cargar manualmente este valor en el registro ya que éste no se resetea a 0 automáticamente. El registro R29 lo utiliza la instrucción de llamada a función para guardar el valor de retorno. El registro R30 se utiliza para almacenar el valor del PC (*Program Counter*) en caso de que ocurra una excepción y el registro R31 se utiliza para lo mismo, pero en caso de que ocurra una excepción de breakpoint. Además, el procesador incluye otros registros de control y estado.

El procesador tiene un espacio de direcciones de 32 bits direccionable por bytes. La E/S es mapeada en memoria y en caso de utilizar una memoria caché, se mapea en la parte no cacheable del espacio de direcciones. El procesador utiliza el formato «Big-endian».

El conjunto de instrucciones del LatticeMico32 se divide en las siguientes categorías:

- Instrucciones aritméticas. Operaciones de 32 bits aritméticas estándar. Las instrucciones de multiplicación y de división son opcionales.

- Instrucciones lógicas. Operaciones lógicas de 32 bits estándar.

- Instrucciones de comparación. Operaciones de comparación básicas entre registros, entre registro y valor inmediato, y comparaciones con signo y sin signo.

- Instrucciones de desplazamiento. El número de bits a desplazar se indican mediante un registro o mediante un valor inmediato de 5 bits.

- Instrucciones de transferencia de datos. Las transferencias de memoria pueden ser de 8, 16 o 32 bits entre memoria y registros. Las direcciones de memoria son relativas y se consiguen mediante la suma de un registro y un valor inmediato con signo de 16 bits. También existen instrucciones de transferencia de datos entre registros.

- Instrucciones de control de programa. Incluyen instrucciones de salto, llamadas a funciones y excepciones, y retornos.

No todas las instrucciones están disponibles en todas las configuraciones del procesador. Todas las instrucciones tienen alguno de los cuatro formatos que se pueden ver en el Cuadro 2.4.

| Formato        | Bits |           |    |       |    |       |           |       |           |       |   |  |  |

|----------------|------|-----------|----|-------|----|-------|-----------|-------|-----------|-------|---|--|--|

|                | 31   | 30        | 26 | 25    | 21 | 20    | 16        | 15    | 11        | 10    | 0 |  |  |

| <b>Tipo RI</b> | 0    | código op |    | Reg 0 |    | Reg 1 |           |       | inmediato |       |   |  |  |

| <b>Tipo RR</b> | 1    | código op |    | Reg 0 |    | Reg 1 |           | Reg 2 |           | 00x00 |   |  |  |

| <b>Tipo CR</b> | 1    | código op |    | CSR   |    | Reg   |           |       | x0000     |       |   |  |  |

| <b>Tipo I</b>  | 1    | código op |    |       |    |       | inmediato |       |           |       |   |  |  |

Cuadro 2.4: Formato instrucciones LatticeMico32™

## 2.6. Simple RISC Computer

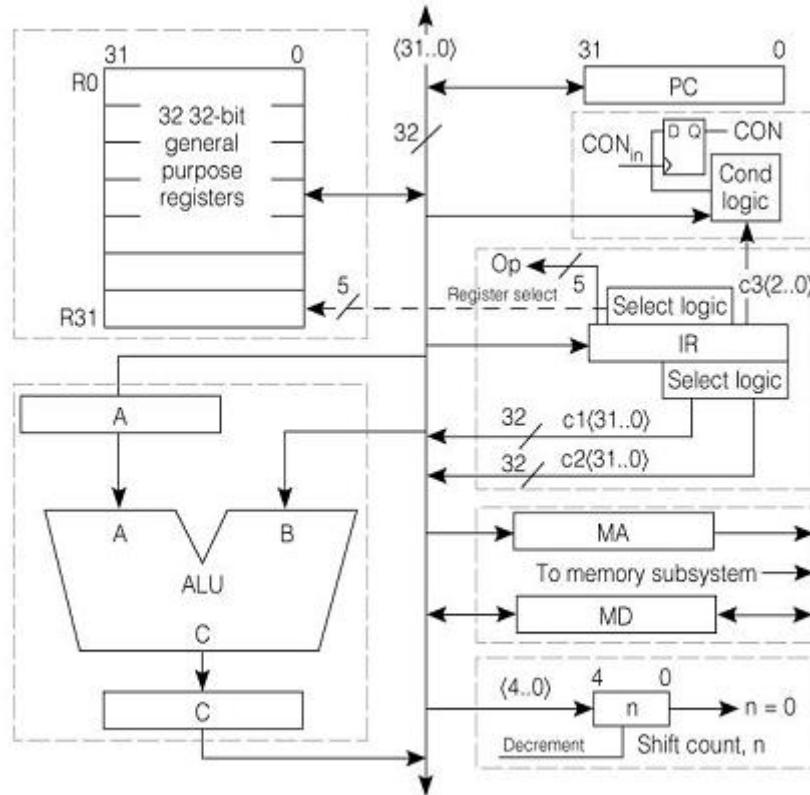

El procesador SRC (*Simple RISC Computer*), al igual que el DLX, es un procesador teórico introducido por Heuring y Jordan en [21]. Este procesador, como su propio nombre indica, se basa en una arquitectura RISC de 32 bits. Los autores proporcionan la descripción RTN (*Register Transfer Notation*) del procesador y el diseño de circuitos lógicos correspondientes a componentes del procesador.

El procesador incorpora 32 registros de propósito general de 32 bits cada uno, además de un registro contador de programa y un registro de instrucción.

La memoria principal está organizada como un vector de 8 bits y únicamente se puede trabajar con datos de 32 bits. El procesador puede llegar a direccionar hasta 4 Gb de memoria gracias a sus 32 bits. Los valores almacenados en la memoria

únicamente pueden ser accedidos mediante la utilización de instrucciones de carga y almacenamiento. La E/S es mapeada en memoria.

El código de operación de cada instrucción es de 5 bits y de tamaño fijo, pudiendo llegar a tener, por lo tanto, hasta 32 instrucciones diferentes. Sin embargo, el procesador original introducido en [21] únicamente utiliza 28 códigos de operación diferentes, de los cuales cinco son utilizados para dar soporte al sistema de interrupciones. El conjunto de instrucciones del SRC se divide en las siguientes categorías:

- Instrucciones de carga/almacenamiento. Existen cuatro instrucciones de carga y dos de almacenamiento.

- Instrucciones de salto. Existen dos instrucciones de salto que permiten realizar saltos condicionales e incondicionales a posiciones de memoria almacenadas en registros. Una de ellas permite realizar saltos almacenando el contenido del registro PC (*Program Counter*) en el registro indicado.

- Instrucciones aritméticas. Existen cuatro instrucciones aritméticas, algunas de ellas con sus variantes de un operando como valor inmediato.

- Instrucciones lógicas y de desplazamiento. Existen nueve instrucciones de este tipo. En las operaciones de desplazamiento, el desplazamiento en sí se puede encontrar en un registro o en un valor inmediato.

- Instrucciones varias. Operaciones sin operandos.

El formato de las instrucciones del SRC se puede ver en el Cuadro 2.5.

Este procesador no dispone de ninguna unidad ni soporte para números en coma flotante, por lo que su diseño se simplifica bastante. Si dispone de control de interrupciones basado en un único par de líneas.

| Formato         | Bits      |    |         |    |         |    |    |    |    |         |   |       |   |   |

|-----------------|-----------|----|---------|----|---------|----|----|----|----|---------|---|-------|---|---|

|                 | 31        | 27 | 26      | 22 | 21      | 17 | 16 | 12 | 11 | 5       | 4 | 3     | 2 | 0 |

| <b>Tipo 1</b>   | código op |    | ra      |    | rb      |    |    |    |    | c2      |   |       |   |   |

| <b>Tipo 2</b>   | código op |    | ra      |    |         |    |    |    |    | c1      |   |       |   |   |

| <b>Tipo 3</b>   | código op |    | ra      |    | sin uso |    | rc |    |    | sin uso |   |       |   |   |

| <b>Tipo 4</b>   | código op |    | sin uso |    | rb      |    | rc |    |    | sin uso |   | cond  |   |   |

| <b>Tipo 5</b>   | código op |    | ra      |    | rb      |    | rc |    |    | sin uso |   | cond  |   |   |

| <b>Tipo 6</b>   | código op |    | ra      |    | rb      |    | rc |    |    | sin uso |   |       |   |   |

| <b>Tipo 7 a</b> | código op |    | ra      |    | rb      |    |    |    |    | sin uso |   | count |   |   |

| <b>Tipo 7 b</b> | código op |    | ra      |    | rb      |    | rc |    |    | sin uso |   | count |   |   |

| <b>Tipo 8</b>   | código op |    |         |    |         |    |    |    |    | sin uso |   |       |   |   |

Cuadro 2.5: Formato instrucciones SRC

Figura 2.7: Arquitectura de 1 Bus del procesador SRC

En [22] se describe el procesador SRC en su versión de un único bus interno (Figura 2.7), aunque también se muestran brevemente las arquitecturas de dos y tres buses. Además, en el mismo texto también se introduce una versión con pipeline de cinco etapas.

El procesador SRC, en su variante de un bus único se ha llegado a sintetizar en un ASIC [23].

## 2.7. Comparativa de procesadores

En el Cuadro 2.6 se puede ver un resumen de las características principales de los procesadores analizados en este capítulo. Básicamente las características mostradas hacen referencia a sus arquitecturas, conjunto de instrucciones y rendimientos. También se muestra el año de aparición de cada procesador.

Los datos referentes al pipeline únicamente se muestran si el procesador o alguna de sus variantes posee pipeline.

Los valores de rendimiento mostrados son el CPI (Ciclos por instrucción) y los MIPS (Millones de Instrucciones Por Segundo). Estos valores, en su mayoría, se han

obtenido de los propios fabricantes o diseñadores. Existe alguna excepción, como en el caso del procesador DLX y su variante DLXS, o el SRC. En concreto, en el caso del DLX no se han conseguido valores sobre su rendimiento en MIPS, al no encontrar ninguna implementación de este procesador. En el caso del DLXS, los datos relativos al CPI y MIPS se han obtenido de terceras partes [12, 14], al igual que en el caso de los MIPS del SRC [23].

Para el cálculo del CPI de las diferentes versiones del procesador SRC (1 bus, 2 buses y 3 buses) es necesario conocer los ciclos de reloj necesarios para ejecutar cada instrucción, y la mezcla típica de instrucciones. El cálculo de la mezcla típica de instrucciones del procesador es una tarea muy complicada y muy variable respecto al código del programa a ejecutar. Por ello se han tomado unos valores aproximados, que aunque no sirvan para calcular un CPI exacto, si pueden ser de utilidad a la hora de realizar comparaciones:

|                |     |

|----------------|-----|

| alu            | 50% |

| salto          | 20% |

| carga          | 20% |

| almacenamiento | 10% |

| Características           | Procesadores                 |                       |                                   |                         |                              |                     | SRC                       |

|---------------------------|------------------------------|-----------------------|-----------------------------------|-------------------------|------------------------------|---------------------|---------------------------|

|                           | DILX                         | DLXS                  | MicroBlaze                        | PicoBlaze               | Nios II                      | AVR32               |                           |

| Bits                      | 32                           | 32                    | 32                                | 8                       | 32                           | 32 • 16             | 32                        |

| Arquitectura              | Pipeline                     | 1 Bus                 | Pipeline                          | No Pipeline             | Pipeline / Pipeline          | Pipeline            | 1, 2 o 3 Buses / Pipeline |

| Pipeline                  | 5 etapas                     | 3–5 etapas            |                                   | 5–6 etapas              | 5 etapas                     | 3 etapas            | 6 etapas                  |

| Tamaño instrucción        | 32 bits                      | 32 bits               | 32 bits                           | 18 bits                 | 32 bits                      | 16 bits             | 32 y 16 bits              |

| Instrucciones             | 83                           | 52                    | 55                                | 37                      | 83                           | 75-63               | 220                       |

| Tipos de direccionamiento | 1                            | 2                     | 2                                 | 2                       | 5                            | 5                   | 5                         |

| Registros                 | 32 de 32b<br>32 de 64b       | 32 de 32b             | 32 de 32b                         | 16 de 8b                | 32 de 32b                    | hasta 512 de 16b    | 15 de 32b                 |

| Bus de direcciones        | 32 bits                      | 32 bits               | 32 bits                           | 8 bits                  | 32 bits                      | 32-16 bits          | 32 bits                   |

| Tipo de E/S               | Mapeada memoria              | Mapeada memoria       | 512 puertos                       | Mapeada memoria         | Mapeada memoria              | Mapeada memoria     | Mapeada memoria           |

| Soporte números flotantes | SI IEEE 754<br>SI (opcional) | NO                    | SI IEEE 754                       | NO                      | SI                           | NO                  | NO                        |

| Operaciones complejas     | mult div barrel shifter      | barrel shifter        | mult • sw div - sw barrel shifter | mult div barrel shifter | mult div - sw barrel shifter | mult barrel shifter | mult div barrel shifter   |

| CPI                       | 1                            | 5                     | 1                                 | 2                       | 6 / 1                        | 1                   | 1                         |

| MIPS                      | 10 – 6.6                     | 240 – 94 <sup>1</sup> | 100 – 44                          | 218 – 31 <sup>1</sup>   | 80 – 30                      | 210 <sup>1</sup>    | 20                        |

| Fecha anunciada           | 1990                         | 1995                  | 2002                              | 2004                    | 2001                         | 2006                | 1996                      |

|                           |                              |                       |                                   |                         |                              | 2006                | 1997                      |

<sup>1</sup> DMIPS (Dhrystone Million Instructions Per Second). Cantidad resultante de dividir la puntuación obtenida en el Dhrystone Benchmark entre 1,575 (número de DPS • Dhrystones Per Second obtenidos por el computador VAX 11/780, normalizado como computador de 1 MIPS).

Cuadro 2.6: Resumen procesadores analizados

# Capítulo 3

## Análisis de buses

En este capítulo se lleva a cabo una breve descripción de tres tipos de arquitecturas de buses diferentes. Estas tres arquitecturas de buses son de las más populares actualmente. El bus AMBA<sup>TM</sup> se utiliza en prácticamente todos los sistemas con procesadores ARM. El bus Avalon se utiliza en los sistemas con procesadores soft-core Nios II de Altera. Por último el bus Wishbone se utiliza en bastantes diseños, sobretodo, dentro del proyecto Opencores [9].

Las tres arquitecturas de buses analizadas en este capítulo persiguen el mismo objetivo: conectar componentes IP. Los tres tipos de buses proporcionan un proceso de negociación y buses de datos de tamaños variables. Ninguno de ellos especifica una frecuencia de reloj determinada, ya que esto supondría un serio problema a la hora de conectar componentes de diferentes diseñadores.

### 3.1. Bus AMBA<sup>TM</sup>

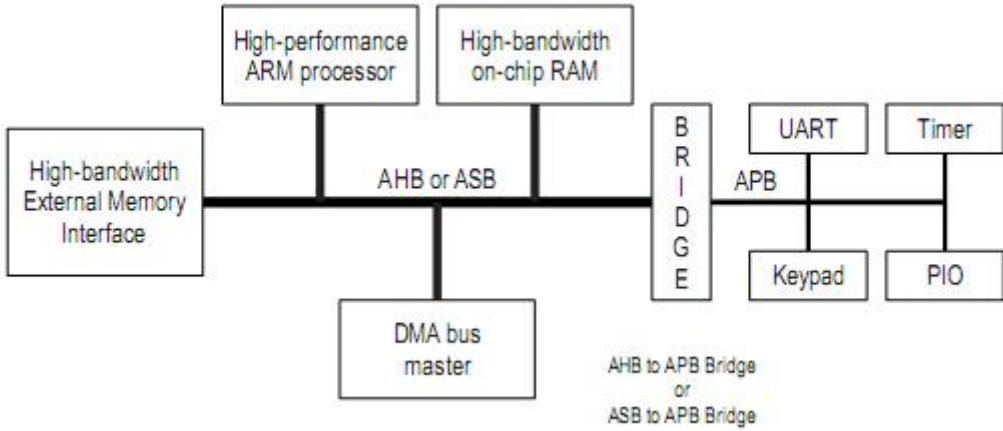

El bus AMBA<sup>TM</sup> (*Advanced Microcontroller Bus Architecture*) se introdujo en 1996. Se utiliza sobretodo en SoC basados en procesadores ARM, aunque es independiente de estos. Los primeros buses AMBA fueron el ASB (*Advanced System Bus*) y el APB (*Advance Peripheral Bus*). En la segunda generación se incluyó el AHB (*Advanced High Performance Bus*) [1].

AMBA define un sistema de buses multinivel, formado por un bus de sistema y un bus de bajo nivel para la comunicación con los periféricos. Existen dos buses de sistema diferentes: el AHB y el ASB. En la Figura 3.1 se puede observar un sistema típico AMBA.

Los buses de sistema soportan 32, 64 y 128 bits de bus de datos con un espacio de direccionamiento de 32 bits. Estos buses son síncronos, no multiplexados y soportan

Figura 3.1: Sistema típico AMBA<sup>TM</sup>

pipeline y bursting. El ASB se utiliza en sistemas simples. En cambio, para sistemas más sofisticados es necesario el uso del bus AHB. Actualmente el procesador ARM trabaja con el bus AHB.

El sistema de buses AMBA define una jerarquía de buses formada, como ya se ha comentado, por un bus de sistema y un bus de interconexión de periféricos. Estos dos buses se comunican mediante un bridge que funciona como un master para los componentes esclavos conectados al bus de los periféricos.

En una configuración típica el bus de sistema conecta el procesador o procesadores con el controlador de memoria, el controlador DMA y con cualquier otro componente de alto rendimiento. Los componentes periféricos lentos se conectan mediante el bus más sencillo de periféricos APB. El bus de sistema y el bus de periféricos pueden funcionar a diferentes frecuencias de reloj.

Actualmente existe una tercera generación de AMBA que incluye un nuevo bus: el AXI (*Advanced eXtensible Interface*).

Las características de los diferentes buses AMBA son las siguientes:

### **AHB (Advanced High Performance Bus)**

Este bus esta diseñado para ser utilizado en la comunicación de dispositivos de alto rendimiento, tales como CPUs, DMAs y DSPs.

- Bus de altas prestaciones.

- Multi Master.

- Transferencias a trozos.

- Selección de master en un ciclo.

- 32 a 128 bits de bus de datos.

- Incorpora un mecanismo de protección de acceso.

- Espacio de direcciones limitado a 32 bits.

- Proporciona sistema de retención de datos para los dispositivos más lentos.

- Soporta arbitraje, REQ, GNT y LOCK.

- Soporta transferencias de bytes, words, etc...

### **ASB (Advanced System Bus)**

Bus de propósito general. Se utiliza para la interconexión de microcontroladores y periféricos.

- Bus de sistema de primera generación.

- Multi Master.

- Transferencias Pipeline.

- 32 a 128 bits de bus de datos.

- Incorpora un mecanismo de protección de acceso.

- Bus de datos bidireccional.

- Espacio de direcciones limitado a 32 bits.

- Proporciona sistema de retención de datos para los dispositivos más lentos.

- Soporta arbitraje, REQ, GNT y LOCK.

- Soporta transferencias de bytes, words, etc...

### **APB (Advance Peripheral Bus)**

Bus de interconexión de periféricos. Este bus se centra en un mínimo consumo y en la facilidad de uso.

- Bus de periféricos de baja potencia y bajo rendimiento.

- Single Master.

- Únicamente 4 señales de control (mas clock y reset).

- Espacio de direcciones limitado a 32 bits.

- Hasta 32 bits de bus de datos.

- Bus de datos de lectura y escritura separados.

Tanto los protocolos de comunicación como las diferentes señales empleadas en las interfaces de los componentes pueden variar dependiendo de la versión de bus (AHB, ASB, APB o AXI) empleada.

## **3.2. Bus Avalon**

Avalon [2] es una arquitectura de bus simple diseñada para interconectar procesadores integrados y periféricos dentro de un SOPC (*System-on-a-programmable chip*). Diseñado por Altera para utilizarlo junto a su procesador, soft-core, Nios II. Avalon

es un interfaz que especifica los pines de conexión entre los componentes maestros y esclavos, además de los tiempos requeridos para su comunicación.

La transacción básica de este bus es capaz de transferir de 8 a 32 bits entre un componente maestro y un periférico esclavo. Después de completarse una transferencia, el bus queda inmediatamente libre para que en el siguiente ciclo de reloj se pueda producir otra transferencia, bien entre los mismos componentes o bien entre otros distintos. El bus Avalon también soporta otros modos de transferencia más avanzados que logran varias transferencias, entre distintos componentes, simultáneas.

Avalon soporta una técnica de arbitraje que permite conectar varios componentes maestros con un mismo componente esclavo, de manera que el árbitro decide en cada momento que componente maestro realizará una transferencia con el periférico esclavo.

Las características principales del bus Avalon son las siguientes:

- Arquitectura multi master.

- Espacio de direcciones de 32 bits donde mapear los distintos componentes de memoria y periféricos.

- Todas las señales del bus están sincronizadas con el reloj.

- Bus de direcciones y de datos separados.

- El bus Avalon genera automáticamente las señales de Chip Select para todos los periféricos.

Todo sistema que utilice el bus Avalon debe incorporar un módulo específico, el cual contiene todas las señales de control, de datos y de direcciones, además de la lógica de arbitraje necesaria para conectar todos los componentes del sistema entre sí. Este modulo, denominado módulo de bus Avalon, implementa una arquitectura de bus configurable que puede variar para adaptarse a los requerimientos de interconexión solicitados por el diseñador. El diseñador del sistema no tiene que conectar manualmente todos los componentes, ya que es la propia herramienta SOPC Builder la que construye el módulo dependiendo de los componentes a conectar. La visión del diseñador del bus se limita a los puertos específicos de cada componente. Se puede observar un ejemplo de sistema con bus Avalon en la Figura 3.2.

Un periférico conectado al bus Avalon es un componente lógico que puede estar implementado dentro del mismo chip o fuera de él. Cada periférico puede tener una tarea diferente y pueden ser añadidos o eliminados del sistema (y por lo tanto su conexión al módulo del bus Avalon) en tiempo de diseño, dependiendo de los requerimientos.

Los periféricos conectados al bus Avalon pueden ser maestros o esclavos. Un periférico maestro puede iniciar una transferencia mediante el bus Avalon y al menos tiene

Figura 3.2: Sistema típico Avalon

un puerto maestro, que se conecta al módulo del bus Avalon. Un periférico maestro también tiene un puerto esclavo que le permite recibir transferencias mediante el bus, iniciadas por otros componentes maestros. En cambio, un periférico esclavo únicamente acepta transferencias del bus Avalon y no puede iniciar él mismo las transferencias. Estos últimos, que suelen ser memorias u otros periféricos, normalmente tienen un puerto esclavo que se conecta al módulo del bus Avalon.

Las especificaciones del bus Avalon definen las señales y los requerimientos temporales requeridos para la correcta transferencia de datos entre un puerto maestro y un puerto esclavo, vía el módulo del bus Avalon. Las señales que componen la interfaz entre dicho módulo y el periférico pueden ser diferentes, dependiendo del tipo de transferencia.

Avalon es un bus síncrono, dirigido por el reloj del bus. Todas las transferencias ocurren de forma síncrona con dicho reloj y se inician en el flanco de subida del reloj.

### 3.3. Bus Wishbone

Wishbone [3] es un bus hardware de código abierto utilizado para comunicar los diferentes componentes de un circuito integrado. Wishbone intenta ser un bus lógico, no

especificando información eléctrica o de topología. Por eso es útil para comunicar diferentes componentes diseñados en lenguajes de descripción de hardware, ya sea Verilog, VHDL u otros.

La arquitectura de bus Wishbone es bastante simple. Únicamente existe un solo bus. Un sistema con varios componentes puede incluir dos buses diferentes: uno para componentes de alto rendimiento y otro para componentes de más bajo rendimiento. En la Figura 3.3 se puede observar una conexión punto a punto.

Figura 3.3: Interconexión Punto a Punto Wishbone

A continuación se muestran algunos detalles técnicos:

- Arquitectura de un bus para todas las aplicaciones.

- Arquitectura simple.

- Multi master.

- Espacio de direcciones de 64 bits.

- Bus de datos de 8 a 64 bits.

- Basado en protocolos estándares de transferencia de datos.

- Soporta varios tipos de interconexiones.

- Protocolo de handshake para regular la velocidad de transferencia de datos.

- Soporta varias terminaciones de ciclos.

- TAGs definidos por el usuario para identificar el tipo de transferencia de datos.

- Basado en arquitectura Maestro/Esclavo.

En la especificación Wishbone se detallan características, clasificadas en los siguientes términos:

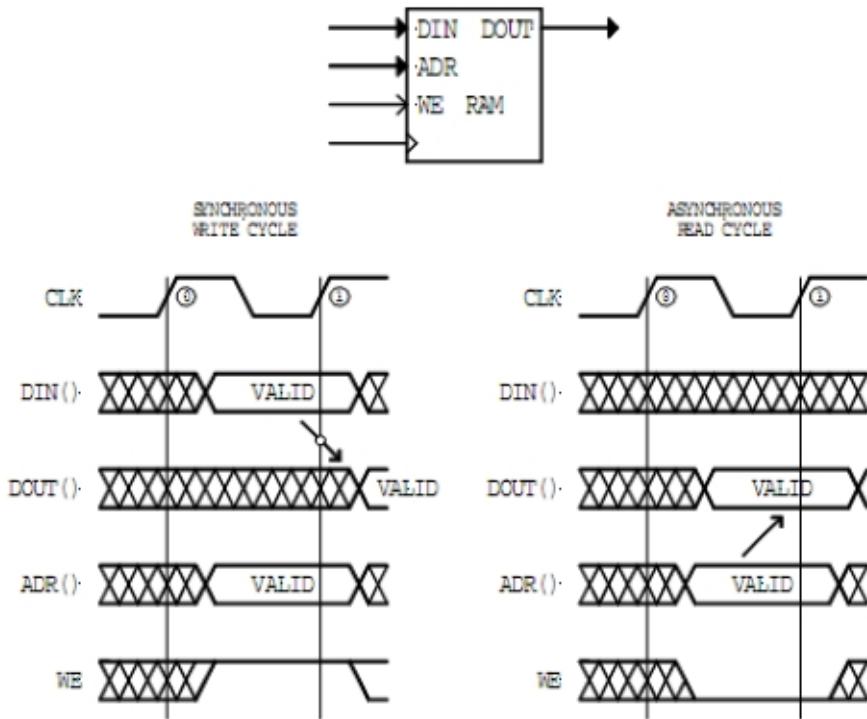

Figura 3.4: Ciclos Read/Write Simples

- Regla. Todas deben ser seguidas para asegurar una compatibilidad entre interfaces.

- Recomendaciones. Cuando aparece una recomendación, se aconseja seguirla. El no adoptarla puede implicar una pérdida de rendimiento.

- Sugerencia. Es un consejo que puede ser considerado por el diseñador. Puede ser útil, pero no vital para el funcionamiento de la interfaz.

- Permiso. Cuando se indica que algo puede hacerse o no, la decisión de implementarlo puede quedar a cargo del diseñador.

- Observación. Usualmente son textos que clarifican alguna situación, pero no aportan nada más que eso.

Las señales permiten tres ciclos básicos: Read, Write y RMW. Pero no hay obligación de soportarlos todos. Además permiten un handshake para adecuar la velocidad

de transferencia de datos, e indicar errores y reintentos.

Las señales no son bidireccionales, siempre son entradas o salidas. Esto es así debido a que muchas veces el diseño puede llegar a querer implementarse en hardware que no soporta internamente señales bidireccionales, como por ejemplo las FPGAs de Altera. A todas las señales se les agrega la coletilla “\_I” o “\_O” al final de las mismas para indicar si son salidas o entradas al componente.

Las interfaces Wishbone deben de inicializarse con el primer flanco de subida del reloj en el que el reset esté activo. Una vez inicializadas ya se pueden realizar ciclos de lectura y escritura. En la Figura 3.4 se puede ver un diagrama de tiempos de los ciclos de lectura y escritura simples.

Wishbone es totalmente gratuito y es utilizado en muchos componentes diseñados dentro del proyecto OpenCores [9]. El usuario también tiene la posibilidad de crear su propio substandard de Wishbone, especificando el orden de los datos (little / big endian) y el significado de los TAGs.

# Capítulo 4

## Análisis de prestaciones. Tecnología de diseño. Planificación

Este capítulo está dividido en tres secciones. En la primera se desvela el procesador elegido para su descripción mediante el lenguaje de descripción de hardware VHDL. En la segunda sección se comenta la tecnología empleada para la realización de su prototipo y por último, en la tercera sección se explica brevemente la planificación del proyecto.

### ANÁLISIS DE PRESTACIONES

Como se ha comentado con anterioridad, el procesador propuesto se utilizará en aplicaciones de adquisición y proceso simple de datos, por lo que es necesario que el procesador posea una arquitectura sencilla y un conjunto de instrucciones simple. Por lo tanto el procesador no necesita soporte para números en coma flotante ni soporte hardware para operaciones complejas. Además, tal como se comenta en la introducción de este texto, es preferible un procesador sin pipeline y con una arquitectura de buses bien definida para poder ser utilizado en propósitos educativos (aunque es recomendable que el procesador posea alguna versión con pipeline para futuras modificaciones). Por todo esto el procesador elegido es el Simple RISC Computer en su variante de 3 buses.

El SRC, en su variante de 3 buses, consigue unas buenas prestaciones con una arquitectura simple de 3 buses obteniendo un buen compromiso entre rendimiento y sencillez. Además dispone de una Unidad Aritmético Lógica sencilla, sin operaciones complejas. De todas maneras en este procesador se aprecian algunas limitaciones a intentar superar, tales como la capacidad de trabajar con un único dispositivo interruptor, o un CPI algo elevado (alrededor de 5 ciclos por instrucción).

La estructura de buses de la unidad de proceso tiene un importante impacto en el rendimiento del procesador. Por un lado, un incremento del número de buses significa

reducir los ciclos por instrucción (CPI) necesarios para ejecutar cada instrucción [22]. Por otro lado aumentamos los retardos provocados por la propagación de las distintas señales por los buses, lo que significa aumentar el período mínimo de reloj y disminuir con ello la frecuencia del procesador.

Con una arquitectura de tres buses podemos obtener una mejora de más de un 80 % respecto de una arquitectura de un solo bus. Aun teniendo en cuenta los retardos introducidos por los buses en el período mínimo de reloj, la mejora sigue siendo importante, estando alrededor del 50 %. La mejora provocada en el CPI por la introducción de un cuarto bus se vería contrarrestada por el aumento del período mínimo de reloj. A partir de aquí la incorporación de más buses solo provocaría un aumento del período mínimo de reloj bajando el rendimiento del procesador en picado.

El período de reloj mínimo para una transferencia de registro dada es el tiempo requerido para propagar datos enteramente alrededor del circuito, de modo que el nuevo valor esté en el registro de destinación y listo para otro ciclo. El período mínimo de reloj para esta transferencia de registro en particular se calcula de la siguiente forma:

$$t_{min} = t_g + t_{bp} + t_{comb} + t_l$$

$t_{min}$ : Período mínimo de reloj.

$t_g$ : Tiempo de propagación de puerta lógica.

$t_{bp}$ : Tiempo de propagación de bus.

$t_{comb}$ : Retardo lógico (ALU).

$t_l$ : Tiempo de propagación de Flip-Flop.

Como se puede observar el término  $t_{comb}$  representa los retardos lógicos introducidos por la ALU, por lo que simplificar la ALU puede provocar la disminución del período mínimo de reloj o lo que es lo mismo: aumentar la frecuencia de reloj del procesador. La Unidad Aritmético Lógica es, por lo tanto, otro punto clave en el diseño del procesador.

Todos los procesadores estudiados en el capítulo 2 a excepción del SRC incorporan un barrel shifter en la Unidad Aritmético Lógica. Este componente utilizado para realizar desplazamientos de varias posiciones en el mismo ciclo de reloj supone un incremento sustancial de la lógica requerida para la síntesis del procesador, además de incrementar notablemente el período mínimo de reloj.

Un shifter de un único bit por ciclo de reloj provoca, en cambio, que el número de instrucciones del programa a ejecutar crezca y por lo tanto que se tengan que realizar más accesos a memoria [26], bajando el rendimiento del procesador.

Teniendo en cuenta lo anterior y que los desplazamientos de más de dos posiciones no son muy comunes en los programas, existe la posibilidad de utilizar una técnica que estaría a medio camino entre las dos anteriores. Se trata de equipar a la ALU

Figura 4.1: Diagrama de Gantt que muestra la planificación del proyecto

de únicamente desplazamientos de un bit, pero permitir que el procesador decodifique instrucciones de desplazamiento de más bits. Para conseguir este propósito es necesario utilizar un contador para llevar el control del número de desplazamientos de un bit necesarios para completar el desplazamiento de n bits indicado por la instrucción. Con esta técnica se simplifica enormemente la ALU y no se realizan más accesos a memoria. Por el contrario se incrementa el CPI, aunque de forma lineal y únicamente en el caso de desplazamientos de más de un bit. Esta técnica es la empleada en el procesador SRC.

En relación a los tres tipos de buses analizados en el Capítulo 3, el que más se adapta a la filosofía de simplicidad del procesador elegido es el Wishbone. Además de ser el más simple de los tres buses es muy flexible y el único totalmente libre de derechos.

## TECNOLOGÍA DE DISEÑO

En el Capítulo 1 se comenta que el procesador se ha de simular y sintetizar mediante el lenguaje de descripción de hardware VHDL en una FPGA.

Según estudios recientes [24], los circuitos implementados en FPGAs, respecto a los implementados en Standard Cells (ASICs), ocupan aproximadamente 35 veces más, son entre 3,4 y 4,6 veces más lentos de media y consumen 14 veces más. El uso de memorias y multiplicadores dedicados por parte de las FPGAs más modernas producen una considerable reducción del área requerida y del consumo del circuito, en cambio estos bloques no tienen efectos importantes en cuanto a velocidad.

Aun teniendo en cuenta estos valores, se ha decidido apostar por una implementación del procesador en una FPGA debido al menor tiempo de diseño necesario y

sobretodo por los excesivos costes asociados a un diseño en Standard Cells y su posterior fabricación. El diseño del procesador en Standard Cells únicamente sería rentable para tiradas largas debido a los altos costes NRE (*Non-Recurring engineering*). Además los fabricantes de FPGAs ofrecen unas herramientas de diseño con un interfaz sencillo y amigable, lo que permite acortar notablemente la curva de aprendizaje. Por esto una implementación en Standard Cells se hace inviable, sobre todo para la realización del prototipo del procesador.

## PLANIFICACIÓN

Hasta ahora se han introducido los objetivos del proyecto, se han analizado distintas alternativas de procesadores y de arquitecturas de buses, y se ha realizado un análisis de sus prestaciones. Todo esto lo podríamos englobar en la primera parte de las tres en las que se puede dividir el proyecto. En la Figura 4.1 se puede ver un diagrama de Gantt representando la planificación seguida en el proyecto. La planificación inicial, que no era tan precisa, únicamente difería de ésta en que la primera etapa del proyecto estaba planificada para realizarla durante los meses de octubre y diciembre.

En el diagrama se pueden observar las tres grandes partes en las que se divide el proyecto y las tareas que forman parte de ellas. La segunda parte del proyecto es la más costosa debido principalmente a la implementación, simulación y prototipado del procesador, sin menospreciar el tiempo dedicado a la realización de las herramientas software (ensamblador y sobretodo, simulador).

# Capítulo 5

## El procesador SR3C

En este capítulo se describe a fondo el procesador SR3C (Simple RISC 3-buses Computer) implementado en este proyecto. Este procesador, tal como se puede observar por su nombre, es una evolución del procesador SRC introducido en el Capítulo 2.

En el primer apartado de este capítulo se introduce el procesador SR3C clasificándolo según su conjunto de registros y su conjunto de instrucciones. Después se describe su arquitectura, el sistema de interrupciones diseñado, algunas modificaciones realizadas sobre él y por último se expone el ensamblador y simulador realizados.

### 5.1. Introducción

El procesador SR3C, aún basándose en el procesador SRC, incorpora bastantes modificaciones importantes. Básicamente las modificaciones introducidas son las siguientes:

- Modificaciones en la arquitectura para disminuir los ciclos por instrucción y aumentar el rendimiento del procesador.

- Especificación de un controlador de interrupciones.

- Introducción de instrucciones adicionales en el repertorio del procesador.

- Adaptación a la interfaz estándar de buses Wishbone.

- Versión con multiplexores para la eliminación de estados en alta impedancia, evitando así consumos innecesarios.

Antes de explicar la arquitectura del procesador, es interesante situar el procesador, según sus registros y el tipo de instrucciones que posee, dentro de las posibilidades

existentes.

### CLASIFICACIÓN DEL SR3C SEGÚN EL TIPO DE REGISTROS INCORPORADOS

Respecto a los registros de un procesador, éstos se pueden clasificar dentro de una de las siguientes categorías:

- Registros acumuladores. El procesador necesita una dirección de memoria en cada instrucción aritmética para poder operar. La ventaja es que disminuye el tamaño de memoria requerida, pero por contra los procesadores que únicamente disponen de este tipo de registros son muy limitados para el cálculo de expresiones con muchos términos y factores.

- Pila. No se hace necesaria ninguna dirección de memoria en las instrucciones aritméticas. Siempre se opera con los elementos más arriba de la pila. El número de instrucciones requeridas para realizar una instrucción aritmética crece notablemente.

- Registros de propósito general. El coste viene dado por identificar dichos registros en la instrucción (numero de bits según número de registros). Este problema se disuelve con procesadores de 32 bits.

El procesador SR3C únicamente dispone de un conjunto de 32 registros de propósito general de 32 bits cada uno.

### CLASIFICACIÓN DEL SR3C SEGÚN EL TIPO DE INSTRUCCIONES

Respecto al tipo de instrucciones que posee el procesador, hay que considerar el número de direcciones de memoria que incluye en las instrucciones.

En una instrucción aritmética de 2 operandos se necesitan los siguientes datos:

- Operación a realizar.

- Localización del primer operando.

- Localización del segundo operando.

- Lugar para almacenar el resultado.

- Localización de la siguiente instrucción a ejecutar.

Los procesadores se pueden clasificar de la siguiente forma según el número de instrucciones de memoria que utilicen para indicar los datos anteriores:

- Procesadores de 4 direcciones. Las instrucciones son demasiado largas y se deben realizar demasiados accesos a memoria. Únicamente en el caso de que los accesos

a memoria fuesen más rápidos que los tiempos de ALU, tendrían que tenerse en cuenta como alternativa de diseño.

- Procesadores de 3 direcciones. Se incluye un registro contador de programa (PC) para indicar la siguiente instrucción. Las instrucciones ocupan menos y el tiempo de acceso disminuye. La unidad de control es la encargada de gobernar el PC.

- Procesadores de 2 direcciones. El resultado de la instrucción se guarda en la misma dirección que uno de los operandos. Se reduce el tamaño de la instrucción pero no el número de accesos a memoria. Muy similares a los procesadores de 3 direcciones.

- Procesadores de 1 dirección. Se utiliza un registro acumulador, que al ser único no hace falta mencionar en la dirección. Se disminuye el tamaño de la instrucción pero se necesitan más instrucciones para cargar y guardar los valores del acumulador.

- Procesadores de 0 direcciones. Los operandos se encuentran en las dos últimas posiciones de una pila. Es necesario instrucciones de push y de pop que si que requieren un campo de dirección. No se han implementado muchas máquinas de este tipo debido a que las maquinas con registros de propósito general son mas dadas a técnicas de speedup como por ejemplo el pipeline.

- Procesadores de  $1-\frac{1}{2}$  direcciones. Este tipo de procesadores se basan en que se requiere menos espacio en la instrucción para direccionar registros que direcciones de memoria. Estos procesadores suelen tener una dirección de memoria y un registro en las instrucciones (de ahí el nombre  $1-\frac{1}{2}$ ). De esta forma se reduce el tamaño de las instrucciones.

El procesador SR3C, al igual que la mayoría de procesadores RISC es de tipo carga/almacenamiento, siendo las instrucciones de carga y almacenamiento las únicas que utilizan una dirección de memoria. Dichas instrucciones se pueden clasificar en el tipo de instrucciones de  $1-\frac{1}{2}$  direcciones. En cambio el resto de instrucciones no utilizan ninguna dirección de memoria ya que los operandos se indican mediante registros.

## 5.2. Arquitectura

El procesador SR3C, al igual que la mayoría de procesadores simples se compone de una UP (Unidad de proceso) y de una UC (Unidad de control). La UP contiene los registros y unidades de proceso mientras que la UC es la encargada de interpretar las

instrucciones y generar las señales de control necesarias para ejecutarlas.

## UNIDAD DE PROCESO

La Unidad de Proceso (UP) del SR3C está compuesta por los siguientes registros y unidades funcionales:

- PC (Contador de Programa). Registro de 32 bits donde se almacena la siguiente instrucción a ejecutar. Incluye una señal (*pc\_new*) que la activa la UC para incrementar en 1 el PC <sup>1</sup>.

- IR (Registro de Instrucción). Registro de 32 bits donde se almacena la actual instrucción a ejecutar. Este registro decodifica la instrucción enviando el código de operación de la instrucción en curso a la Unidad de Control del procesador. Además selecciona los registros activos en dicha instrucción y la condición de salto (para instrucciones de salto). Puede volcar en el Bus A la instrucción entera, el valor inmediato c1, o el valor inmediato c2 (Ver apartado Instrucciones del SR3C).

- MA (Registro Dirección de Memoria). Registro de 32 bits donde se almacena la dirección de memoria a acceder. Está conectado al bus de dirección de memoria.

- MD (Registro Dato de Memoria). Registro de 32 bits donde se almacena el dato a escribir en memoria o donde se recibe el dato leído de memoria.