# Departament d'Arquitectura de Computadors i Sistemes Operatius Màster en Computació d'Altes Prestacions

# Deadlock Avoidance with Virtual channels

Memoria del trabajo de investigación del "Máster en Computación de Altas Prestaciones", realizada por Fragkakis Emmanouil, bajo la dirección de Daniel Franco Puntes Presentada en la Escuela Técnica Superior de Ingeniería (Departamento de Arquitectura de Computadores y Sistemas Operativos)

Barcelona Julio de 2009

# 41746 - Iniciació a la recerca i treball fi de màster Máster en Computación de Altas Prestaciones

Curso 2008-09

# Título

# **Deadlock Avoidance with Virtual Channels**

Autor

# Fragkakis Emmanouil

Director

# **Daniel Franco Puntes**

Departamento Arquitectura de Computadores y Sistemas Operativos

Escuela Técnica Superior de Ingeniería (ETSE)

Universidad Autónoma de Barcelona

| Autor | Director |

|-------|----------|

Firmado

#### **Abstract**

High Performance Computing is a rapidly evolving area of computer science which attends to solve complicated computational problems with the combination of computational nodes connected through high speed networks.

This work concentrates on the networks problems that appear in such networks and specially focuses on the Deadlock problem that can decrease the efficiency of the communication or even destroy the balance and paralyze the network.

Goal of this work is the Deadlock avoidance with the use of virtual channels, in the switches of the network where the problem appears. The deadlock avoidance assures that will not be loss of data inside network, having as result the increased latency of the served packets, due to the extra calculation that the switches have to make to apply the policy.

Keywords: HPC, High Speed Networking, Deadlock Avoidance, Virtual Channels

#### Resumen

La computación de alto rendimiento es una zona de rápida evolución de la informática que busca resolver complicados problemas de cálculo con la combinación de los nodos de cómputo conectados a través de redes de alta velocidad.

Este trabajo se centra en los problemas de las redes que aparecen en este tipo de sistemas y especialmente se centra en el problema del "deadlock" que puede disminuir la eficacia de la comunicación con la paralización de la red.

El objetivo de este trabajo es la evitación de deadlock con el uso de canales virtuales, en los conmutadores de la red donde aparece el problema. Evitar el deadlock asegura que no se producirá la pérdida de datos en red, teniendo como resultado el aumento de la latencia de los paquetes, debido al overhead extra de cálculo que los conmutadores tienen que hacer para aplicar la política.

**Palabras clave:** Computación de altas prestaciones, Redes de alta velocidad, Evitación de "deadlock", canales virtuales

#### Resum

La computació d'alt rendiment és una àrea de ràpida evolució de la informàtica que pretén resoldre complicats problemes de càlcul amb la combinació de nodes de còmput connectats a través de xarxes d'alta velocitat.

Aquest treball se centra en els problemes de les xarxes que apareixen en aquest tipus de sistemes i especialment se centra en el problema del "deadlock" que pot disminuir l'eficàcia de la comunicació amb la paralització de la xarxa.

L'objectiu d'aquest treball és l'evitació de deadlock amb l'ús de canals virtuals, en els commutadors de la xarxa on apareix el problema. Evitar deadlock assegura que no es produirà la pèrdua de dades en xarxa, tenint com a resultat l'augment de la latència dels paquets, degut al overhead extra de càlcul que els commutadors han de fer per aplicar la política.

**Paraules clau:** Computació d'altes prestacions, Xarxes d'alta velocitat, evitació de "deadlock", canals virtuals

To my family,

For all their efforts, and support

To Dani, Diego and Gonzalo,

For their precious help on this project

To CAOS department,

For the all the knowledge and experiences

# **Table of Contents**

| M | ASTER    | EN COMPUTACIÓ D'ALTES PRESTACIONS               | 1   |

|---|----------|-------------------------------------------------|-----|

| 1 | INTR     | ODUCTION                                        | 13  |

|   | 1.1      | PARALLEL COMPUTERS                              | 14  |

|   | 1.2      | NETWORK TOPOLOGIES                              | 17  |

|   | 1.3      | NETWORK PROBLEMS                                | 22  |

|   | 1.4      | VIRTUAL CHANNELS                                | 25  |

|   | 1.5      | NETWORK SIMULATOR – OPNET                       | 26  |

| 2 | STAT     | E OF THE ART                                    | 31  |

|   | 2.1      | IN WHICH LEVEL IS SITUATED OUR PROBLEM          | 31  |

|   | 2.2      | WHAT ARE THE EXISTING PROPOSALS FOR THE PROBLEM | 33  |

|   | 2.3 RELA | TED WORKS                                       | 37  |

| 3 | THEC     | DRETICAL BACKS                                  | 39  |

|   | 3.1      | THEORY                                          | 39  |

|   | 3.1.1    |                                                 |     |

|   | 3.1.2    | Virtual Channels                                | 43  |

|   | 3.1.3    | OPNET                                           | 47  |

| 4 | ANALYSI  | S                                               | 61  |

|   | 4.1      | Previous model                                  | 61  |

|   | 4.1.1    | SWITCH                                          | 62  |

|   | 4.1.2    | NODE                                            | 71  |

|   | 4.2      | DESCRIPTION OF THE PROPOSITION                  | 72  |

|   | 4.2.1    | Network Elements                                | 78  |

| 5 | DESIGN.  |                                                 | 91  |

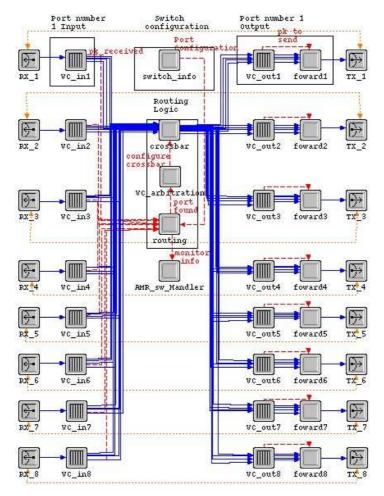

|   | 5.1 GEN  | eral Switch Structure                           | 91  |

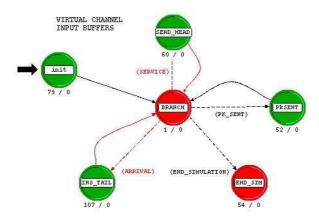

|   | 5.1.1    | Input Virtual Channel Buffers                   | 93  |

|   | 5.1.2    | Routing Unit                                    | 95  |

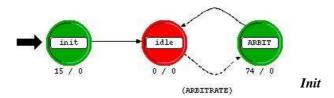

|   | 5.1.3    | Arbitration                                     | 97  |

|   | 5.1.4    | Crossbar                                        | 100 |

|   |          | Output Virtual Channel Buffers                  |     |

|   | 5.1.6    | Forward unit                                    | 102 |

| 6 | EXPERIM  | TENTATION AND SIMULATION RESULTS                | 105 |

|   | 6.1 Syst | EM DETAILS                                      | 105 |

|   | 6.2 SIMU | JLATION MODELS                                  | 106 |

|   | 6.2.1    | Mesh                                            | 106 |

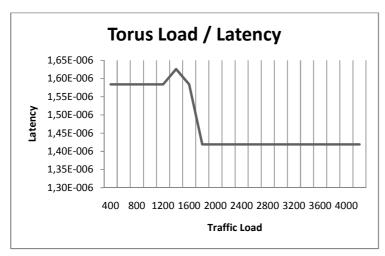

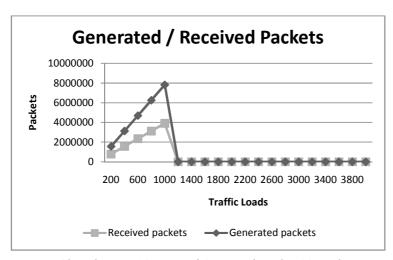

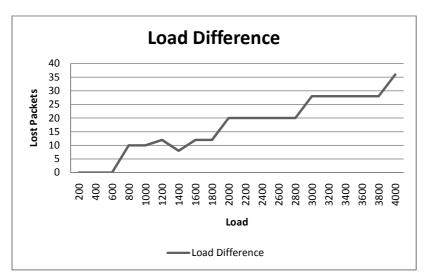

|   | 6.2.2    | Torus                                           | 107 |

|   | 6.2.2    | Fat Tree                                        | 109 |

|   | 6.3 RESU | ILT EVALUATION                                  | 109 |

| 7 | CON      | CLUSIONS                                        | 115 |

| 8 | BIBL     | OGRAPHY                                         | 117 |

# **Index of Images and Tables**

| IMAGE 1 MESH, TORUS, AND FAT TREE TOPOLOGIES                   | 28        |

|----------------------------------------------------------------|-----------|

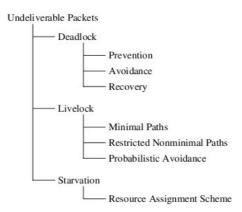

| IMAGE 2 CAUSES OF UNDELIVERED PACKETS                          | 34        |

| Image 3 Deadlocked configuration                               | <u>39</u> |

| IMAGE 4 STAGES OF TRAVERSING PACKET                            | 41        |

| IMAGE 6 WAIT FOR AND HOLD GRAPH                                |           |

| IMAGE 5 DEPENDENCE GRAPH                                       | 42        |

| IMAGE 7 DEPENDENCE GRAPH WITH 2 VC                             |           |

| IMAGE 8 SIMPLE BUFFER & BUFFER WITH VC                         |           |

| IMAGE 9 COMMUNICATION LINES WITH VC                            | 45        |

| IMAGE 10 PACKETS ADVANCES WITH THE USE OF VC'S                 |           |

| IMAGE 11 NETWORK DOMAIN                                        | 50        |

| IMAGE 12 COMMUNICATION CHANNELS                                | 51        |

| IMAGE 13 PROCESSOR MODULE                                      | <u>53</u> |

| IMAGE 14 QUEUE MODULE                                          | 53        |

| IMAGE 15 SUBQUEUE REPRESENTATION                               | 54        |

| IMAGE 16 RECEIVER – TRANSMITTER                                | 55        |

| IMAGE 17 PACKET STREAM                                         | 56        |

| IMAGE 18 STATISTIC STREAM                                      | 56        |

| IMAGE 19 UNFORCED AND FORCED STATES OF THE PROCESSES           | 57        |

| IMAGE 20 TRANSITIONS BETWEEN STATES                            | 59        |

| IMAGE 21 4X4 MESH TOPOLOGY                                     | 62        |

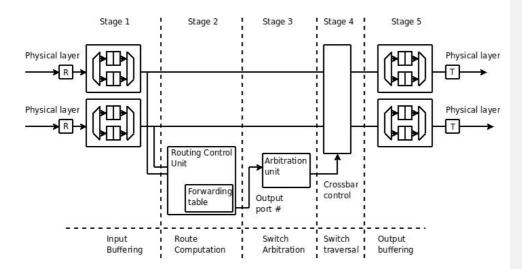

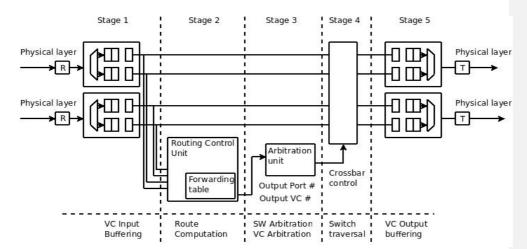

| IMAGE 22 MICHROARCHITECTURE PIPELINE OF AN INPUT-OUTPUT SWITCH | 63        |

| TABLE 1 INTERNAL MODULES OF PREDEFINED SWITCH MODEL            | 64        |

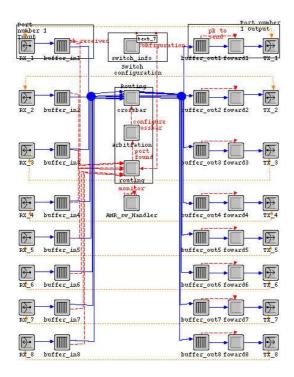

| IMAGE 23 ORIGINAL SWITCH STRUCTURE                             | 65        |

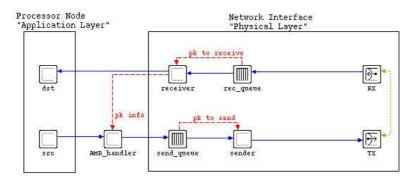

| IMAGE 24 ORIGINAL NODE STRUCTURE                               | 71        |

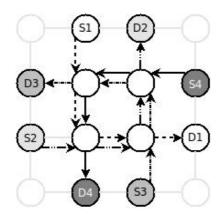

| IMAGE 25 TOPOLOGIES OF MESH, TORUS AND FAT TREE                | 73        |

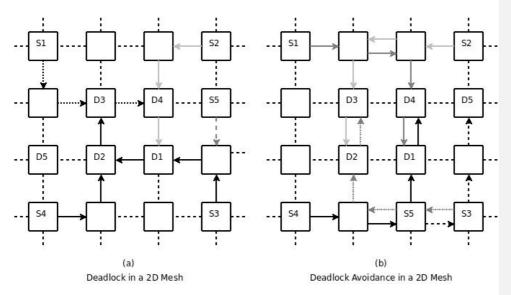

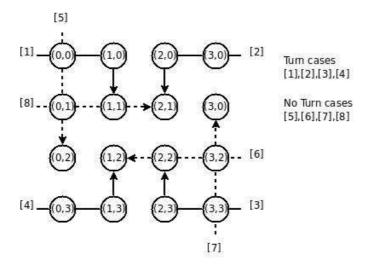

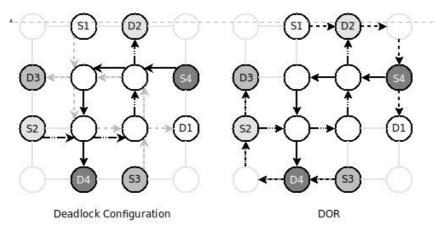

| IMAGE 26 DEADLOCK AVOIDANCE IN A 4X4 MESH                      | 75        |

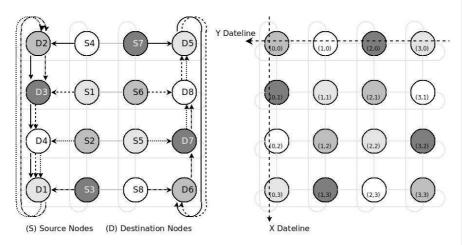

| IMAGE 27 DOR ON TORUS TOPOLOGY                                 | 76        |

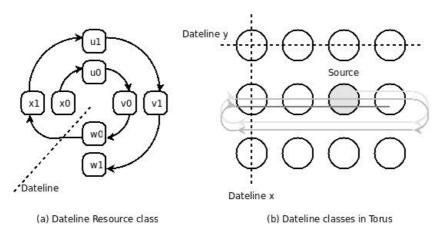

| IMAGE 28 DATELINE CLASSES IN TORUS                             | 77        |

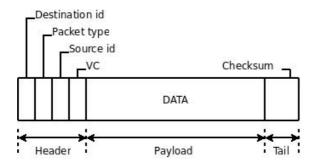

| IMAGE 29 PACKET STRUCTURE                                      | 80        |

| IMAGE 30 PIPELINED SWITCH MICHROARCHITECTURE WITH 2VC          | 81        |

| TABLE 2 INPUT VC STATE FIELDS REPRESENTED BY A 5-VECTOR GROPC  | 83        |

| TABLE 3 OUTPUT VC STATE FIELDS REPRESENTED BY A 3-VECTOR GIC   | 83        |

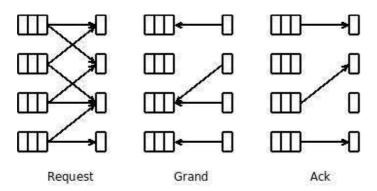

| IMAGE 31 3 PHASE ARBITRATION                                   | 87        |

| IMAGE 32 CASES OF PACKET TRAFFIC                               | 88        |

| IMAGE 33 VC SWITCH STRUCTURE                                   | 92        |

| IMAGE 34 INPUT VIRTUAL CHANNEL BUFFERS                         | 93        |

| IMAGE 35 ROUTING UNIT                                          | 95        |

| IMAGE 36 ARBITRATION UNIT                                      | 97        |

| TABLE 4 DEADLOCK AVOIDANCE POLICY                              | 99        |

| TABLE 5 DATELINE CLASSES FOR TORUS                             | 99        |

| IMAGE 37 CROSSBAR UNIT                                         | 100       |

| IMAGE 38 OUTPUT VIRTUAL CHANNEL BUFFERS                        |           |

| IMAGE 39 FORWARD UNIT                                          | 103       |

| Image 40 Mesh – Deadlock Configuration                         |           |

| IMAGE 41 TORUS DEADLOCK CONFIGURATION & DATELINE POLICY        |           |

| TABLE 6 TORUS WITHOUT THE USE OF VC                            |           |

| TABLE 7 TORUS WITH THE USE OF VC                               |           |

| IMAGE 42 DEADLOCK AVOIDANCE WITH THE USE OF DOR.               |           |

Formatted: Font: 10 pt, English (U.S.), Small caps

Deleted: 39

Field Code Changed

Formatted: Font: 10 pt, English

(U.S.), Small caps

Formatted: English (U.S.)

Deleted: 53

**Formatted:** Font: 10 pt, English (U.S.), Small caps

Formatted: Font: 10 pt, English

(U.S.), Small caps

Formatted: English (U.S.)

Field Code Changed

# 1 Introduction

In the 1<sup>st</sup> chapter we will see the world of High Performance Computing and the various elements that HPC consists of. We will refer to the significance of the HPC and the complex problems that attends to solve through parallel programming. Important elements of HPC will be referred as some of the different kinds of parallel computers that are used for that reason and some of the interconnection networks that support the complexity of those machines. As problems can occur on the interconnection networks we will refer on the most basic of them and what are the possible solutions. Finally we will refer on some of the most known network simulators and how through them we can study and propose a solution for a problem on an interconnection network.

**HPC** is a term that describes the High Performance Computing, an area that is mostly related with the scientific research. HPC generally refers to the engineering applications that run on a parallel computer or on a cluster based computer system. These systems work closely so that in many respects they form a single computer. Computers of that form are capable of processing / calculating with speed big amounts of data. In the latest years the need for more computation power has increased and in other areas than science, like data warehouses, online applications or transaction processes.

For the efficient control and processing of all the amount of data produced, has been evolved also the area of **parallel computing**. Parallel computing is the form of computation, in which many calculations are carried out simultaneously, operating with the principle that large problems can often divided in smaller ones. This calculation can be done concurrently, in parallel, through the combination of a parallel computer, a high speed interconnection network and a big storage base.

Due to the technological evolution and the way that our lives evolve, new grand challenges have arisen. **Grand challenge problem** is one problem that cannot be solved in a reasonable amount of time with today's computers. Some of them are listed below.

- Applied Fluid Dynamics

- Meso to macro-scale environmental modelling

- Ecosystem simulations

- · Biomedical imaging and biomechanics

- · Molecular design and process optimization

- Cognition

- Fundamental computation

- Nuclear power and weapons simulations

- Strong Artificial Intelligence

- Robust, Predictive macroeconomic simulations

Fundamental scientific problems currently being explored generate increasingly complex data, require more realistic simulations of the processes under study, and demand greater and more intricate visualizations of the results. These problems often require numerous large-scale calculations and collaborations between people with multiple disciplines and locations. Also the time of the calculations is a very important factor, thus in some problems like weather prediction, the result of the calculation has to be resolved before a predefined time. These calculations are done by machines called parallel computers.

# 1.1 Parallel Computers

Parallel computers can be classified according to the level at which the hardware supports parallelism with multi-core and multi-processor computers having multiple processing elements within a single machine, while clusters, MPPs, and Grids use multiple computers to work on the same task. In all the times a very good interconnection network is needed with architecture that will support respectively the computer. Specialized parallel computer architectures are sometimes used alongside traditional processors, for accelerating specific tasks.

# Type of parallel computers

- multicore computing

- symmetric multiprocessing

- distributed computing

- cluster computing

- massive parallel computing

- grid computing

# Multicore computing

A multicore computer is a machine which includes multiple execution units, cores. Multicore computer can execute multiple instructions per cycle from multiple instruction streams. Each core in a multicore computer can potentially be a superscalar core, meaning that on every cycle each core can execute multiple instructions by a single stream.

# Symmetric multiprocessing

A symmetric multiprocessing system is a computer system with multiple identical processors that share the same memory and they are connected through a bus. The caused bus contention in these systems does not provide scalability.

# Distributed computing

A distributed computing system is a distributed memory system with multiple computing and storage elements which are connected through an interconnection network. Cluster computers execute concurrent processes under a loose or strict policy. Distributed systems have also the advantage of high scalability.

# Cluster computing

A cluster system is a machine that consists by multiple computers connected through an interconnection network. The elements of a cluster computer work so closely so that in many respects we can say that they work as a single computer. Most known type of a cluster computer is a Beowulf computer which consists by several high-end commercial computers connected through a high performance TCP/IP local area network (LAN).

## Massive parallel computing

A massive parallel computer is a term that describes the computer architecture of a system with many independent computational units that run in parallel. The term massive means the use of hundreds or thousand computational units. The computing units are connected through a network, creating with that way a very large scale system.

# **Grid computing**

A Grid system is the most known type of a distributed system. Grid architecture makes use of several computational units, usually computers, connected through internet that work together to solve a scientific or technical problem. Because of the low bandwidth and the high latency of those connections the Grid systems are usually occupied with small amount of calculations.

#### **Specialized Parallel Computers**

- Reconfigurable computing with field programmable gate arrays

- General purpose computing on graphics processing units (GPGPU)

- Applications specific integrated circuits

- Vector processors

#### Reconfigurable computing with field programmable gate arrays

Reconfigurable computing is the use of a field programmable gate array (FPGA) as a co-processor to a general purpose computer. An FPGA is a computer chip that can rewire itself for a given task.

# General purpose computing on graphics processing units (GPGPU)

General purpose computing on graphics processing units (GPGPU) is a fairly recent trend in computer engineering research. GPUs are co-processors that have been heavily optimized for computer graphics processing. Computer graphics processing is a field dominated by data parallel operations such as linear algebra matrix operations.

# Applications specific integrated circuits

Application specific integrated circuit (ASIC) have been used for dealing with parallel applications. An ASIC is an integrated circuit (IC) customized for a particular use, rather than intended for general purpose use.

## **Vector processors**

A vector processor is a computer system dedicated to execute the same instruction over large sets of data. Vector processors have the ability of high level operations, over linear arrays of numbers of number or vectors. Cray system was the first known for its vector processing.

# 1.2 Network Topologies

The **interconnection network** plays a central role in determining the overall performance of all above parallel computers systems. Thus the computation nodes do all the data process and calculations. These calculations are based on the interconnection network for the communication among them or with some data storage base. Any given node in the network will have one or more links to one or more other nodes in the network and the mapping of these links and nodes onto a graph results in a geometrical shape that determines the physical topology of the network. The interconnection network characterized by the

topology, the routing algorithm, the switching strategy and the flow control mechanism. Routing is responsible for the path selection that the network traffic has to follow inside a network. Switching is the network communication strategy that defines how are established the connections inside a network and the flow control mechanism is responsible to manage the rate of data transmission. All these characteristics are combined for the proper functionality and the high speed of the network. If the network cannot provide adequate performance, for a particular application, nodes will frequently be forced to wait for data to arrive. Important for the proper functionality and quality of the network service, is the topology that describes it. Some of the most known network topologies are listed below.

- Fully connected all-to-all

- Mesh

- Rings

- Hypercube

- Torus

- Fat-tree

- Butterflies

- Benes network

# Fully connected all-to-all

In a fully connected network each node on the system is connected with all the others nodes through point to point links. This makes possible the simultaneous transmition of data from one node to all the others.

#### Mesh

In a Mesh network all the nodes in each dimension form a linear array. Mesh and torus topologies consist of N=k<sup>n</sup> nodes in a N dimensional cube with k nodes along each dimension. The mesh topology incorporates a unique network design in which each computer on the network connects to every other, creating a point-to-point connection between every device on the network. The purpose of the mesh design is to provide a high level of redundancy. Mesh networks

have two groups, Full-Mesh and Partial-Mesh.

The Full-Mesh Topology connects every single node together. This will create the most redundant and reliable network around- especially for large networks. If any link fails, we (should) always have another link to send data through. The Partial-Mesh Topology is much like the full-mesh, only we don't connect each device to every other device on the network. Instead we only implement a few alternate routes.

# Rings

Ring is the type of network topology in which each of the nodes of the network is connected to two other nodes in the network and also the first and last nodes being connected to each other, forming a ring. Data inside ring are transmitted from one node to the next node in a circular manner and the data generally flows in a single direction only.

#### Hypercube

A special kind of mesh, limiting the number of hops between two nodes, is Hypercube.

Hypercube is a configuration of nodes in which the locations of the nodes correspond to the vertices of a mathematical hypercube and the links between them correspond to its edges. A Hypercube network has  $2^n$  nodes, and each of these nodes is arranged on cube shape, having n sets of links for interconnecting other nodes, so as to form an n-dimensional hyper cube type network.

#### **Torus**

Torus network consists of  $N=k^n$  nodes arranged in a N dimensional cube with k nodes along each dimension. In torus topology the nodes in each dimension form a ring topology. A torus is a mesh topology with wrap around links and with the double number of bisection channels, for the same radix and dimension.

#### Fat-tree

Fat tree topology is the type of network in which a central root node in the higher level of hierarchy is connected to one or more other nodes that are in the lower level of the hierarchy. These nodes in their turn are connected with one or

more nodes that are in one lower level on the hierarchy. That structure gives us the hierarchy tree. The nodes on the lower level of the tree, are the leafs of the tree.

#### **Butterflies**

A butterfly network is a quintessential indirect network with two characteristics. Firstly a butterfly has no path diversity which means that there is only one route for each source node to its destination node. Secondly a butterfly network needs long wires at least equal with the half of the machine diameter, thing that decreases the speed of the wire quadratically as its length increase. This makes butterfly unattractive for large interconnection networks.

# Benes network

A Benes network is a rearrangeably nonblocking network, widely used in telecommunication networks. Consists of n input nodes, n output nodes and in the middle has switches wired together.

**Network topology** refers to the static arrangement of channels and nodes in an interconnection network, characterizing the available paths that the packets have to travel to reach their destinations. The network topology is the first step in the design of a network, because **routing mechanism** and the **flow control method** will be heavily based on the topology. Whereas the topology determines the ideal performance of a network, routing and flow control are the two factors that determine how much of its potential is realized. A pathway is needed before every route can be selected and the traversal of that route scheduled. The network topology not only specifies the type of the network but also the radix of the switch, meaning the maximum number of possible connected devices to it, the number of stages and the width and bit rate of each channel.

Usually, we choose the topology based on its cost and performance. The **cost** is determined by the number and the complexity of the required machines for the network realization and the density and length of the interconnections between those machines. **Performance** is described by two components, bandwidth and latency. Bandwidth is the measurement of the available or consumed data communication resources expressed in bit/s or multiples of it, Kbit/s or Mbit/s.

Latency is the synonym expression of delay in networks. Refer to the amount of time that a packet makes from its source to its destination. Both these components are determined by factors other than network topology, like flow control, routing mechanism and traffic pattern.

A way of connecting more than two devices is either through a shared media network or with a switched media network.

**Shared media network** is the most traditional way of interconnection between devices. In half-duplex mode data can be carried in either dimension over the network that connects the machines, but without having the possibility of simultaneous transmission and reception by the same machine. In full-duplex mode it can be simultaneous reception and transmission by the same machine.

**Switched media networks** is the alternative approach that does not share the entire network path at once, but progressively advance switching between disjoint portions of the network. These portions are point-to-point links, between active switch components. As the packet traverses through the network, it establishes communication between sets of source and destination pairs. These passive and active components make up the network switch fabric or network fabric.

Main advantage of the switched media networks is that the amount of network resources implemented scales with the number of the connected devices, increasing the aggregate network bandwidth. These networks allow multiple pair of nodes to communicate simultaneously allowing much higher effective bandwidth than that provided by the shared media networks. Also the system in switch media networks can scale to a very large number of nodes, thing which is not feasible in shared media networks.

In switch-based networks as these we are going to study, packet traverses inside network using several switches before it reach its destination. The packets have to pass through the communication lines and the switches. A switch acts as interface for communication between communications circuits in a networked environment. In addition, most modern switches have integrated network

managing capabilities and may operate on numerous layers. Some of the integrated mechanisms that are implemented inside switches are routing, arbitration and switching.

**Routing** is defined as the set of operations that need to be performed to compute a valid path from the packet source to its destination. Routing is setting the question "Which of the possible paths are allowable for packets."

**Arbitration** is required to resolve a conflict, when several packets compete for the same resources in the same time. Arbitration is setting the question "When are paths available for packets."

**Switching** is the mechanism that provides a path for a packet to advance to its destination, when the requested resources are granted. Switching is setting the question "How are paths allocated to packets"

# 1.3 Network Problems

Although when the exchange of information increases and the number of the participating nodes is big is more often for a problem to appear. Problems occur due to failures or limitations on the hardware resources of the network. These can destroy the balance, or reduce the speed and the functionality of the network. Some of the most important problems that appear in the interconnections network are listed below.

- Deadlock

- Livelock

- Starvation

**Deadlock** is a very common problem that happens in different communication levels, in our case in the interconnection network of a High Performance Computer. It is the situation that occurs when different processes wait one another to release specific resources. With that way there is cyclic dependency between these different processes for the same resources, creating like that a circular chain.

*Livelock* is a condition that occurs when two or more processes continually change their state in response to changes in the other processes. The result is that none of the processes will complete. An analogy is when two people meet in a hallway and each tries to step around the other but they end up swaying from side to side getting in each other's way as they try to get out of the way.

*Starvation* is similar in effect to deadlock. Starvation is a multitasking-related problem, where a process is perpetually denied necessary resources. Without those resources, the program can never finish its task.

In High Performance Computing, networking is a very important issue, and that is because the interconnection network is the key element in the structure of a parallel computer. A well structured network can improve the performance of the computer minimizing the time that a packet takes from its source to its destination and as a sequence decrease the computation time. We have to implement several techniques that will solve or prevent problems that appear in such networks. Some solution proposals for the most important of the interconnection problems are listed below (Details are done in the next chapter).

- Deadlock

- Prevention

- Avoidance

- Recovery

- Livelock

- Minimal Paths

- Restricted non minimal paths

- Probabilistic Avoidance

- Starvation

- Resource assignment scheme

One of the most serious problems that occur and we have to deal with, in this specific project, is Deadlock. Thus deadlock can be catastrophic and paralyze the network, is very important to eliminate any possibility that a deadlock will occur. There are four necessary conditions for a deadlock to occur, knows as Coffman conditions. These conditions are listed below.

- 1. Mutual exclusion

- 2. Hold and wait condition

- 3. No pre-emption condition

- 4. Circular wait condition

Deadlock can be avoided if certain information about processes is available in advance of resource allocation. For every resource request, the system sees if granting the request will mean that the system will enter an *unsafe* state, meaning a state that could result in deadlock. The system then only grants requests that will lead to *safe* states. In order for the system to be able to figure out whether the next state will be safe or unsafe, it must know in advance at any time the number and type of all resources in existence, available, and requested. One known algorithm that is used for deadlock avoidance is the Banker's algorithm, which requires resource usage limit to be known in advance. However, for many systems it is impossible to know in advance what every process will request. This means that deadlock avoidance is often impossible.

A total ordering on a minimal set of resources within each dimension is required, if we would like to use these resources in full capacity. In contrary some resources along the dimension links have to stay free so that can remain below the full capacity and avoid deadlock. To allow full access to the network resources of the network, we have either to duplicate the physical links or duplicate the logical buffers associated with each link. This results respectively to physical channels or virtual channels.

Routing algorithms based on this technique, called Duato's protocol, can be defined that allow alternative paths provided by the topology, to be used for a given pair of source-destination nodes in addition to the escape resource set.

One of those allowed paths must be selected, preferably the most efficient one.

# 1.4 Virtual Channels

Virtual channels are the representation of the partitioned buffer queue inside a switch. Buffers can exist in the input and the output of a switch, characterizing with that way the type of the switch. Buffers can be placed in the input port of a switch and give us the **input buffered switch**, centrally within the switch which give us a **centrally buffered switch** and finally at both input and output ports of the switch which give us an **input-output buffered switch**.

The packets traverse through the network using the same communication lines, and use the switches as intermediate stops until their destination. With the structure of virtual channels is provided to the incoming packets of a switch, an alternative path to select in case that a previous packet is blocked inside a buffer. This alternative path is selected through the flow control mechanism that is implemented in the switch, with the use information that each packet carries in its header, so that can properly directed to its destination.

For the proper construction and the effective representation of all those elements that structure an interconnection network, is necessary the use of a tool like a network simulator. Network simulator is a tool that can provide us detail in multiple layers of the interconnection network construction and allow us to make changes in all those layers.

# 1.5 Network Simulator – OPNET

Network simulators serve a variety of needs. Compared to the cost and time involved in setting up an entire test bed containing multiple networked computers, routers and data links, network simulators are relatively fast and inexpensive. They allow engineers to test scenarios that might be particularly difficult or expensive to emulate using real hardware- for instance, simulating the effects of a sudden burst in traffic or a DoS attack on a network service. Networking simulators are particularly useful in allowing designers to test new networking protocols or changes to existing protocols in a controlled and reproducible environment.

Network simulators, as the name suggests are used by researchers, developers and Quality Assistants to design various kinds of networks, simulate and then analyze the effect of various parameters on the network performance. A typical network simulator encompasses a wide range of networking technologies and helps the users to build complex networks from basic building blocks like variety of nodes and links. With the help of simulators one can design hierarchical networks using various types of nodes like computers, hubs, bridges, routers, optical cross-connects, multicast routers, mobile units, MSAUs etc.

There is a wide variety of network simulators, ranging from the very simple to the very complex. Minimally, a network simulator must enable a user to represent a network topology, specifying the nodes on the network, the links between those nodes and the traffic between the nodes. More complicated systems may allow the user to specify everything about the protocols used to handle network traffic. Graphical applications allow users to easily visualize the workings of their simulated environment. Text-based applications may provide a less intuitive interface, but may permit more advanced forms of customization. Others, such as GTNets, are programming-oriented, providing a programming framework that the user then customizes to create an application that simulates the networking environment to be tested. A list of the most important network simulators is listed below.

- ns2 / ns3

- Opnet

- Cisco Packet Tracer

- Cisco NetworkSims

- GloMoSim

- OMNeT++ and Simulation Software based on Omnet++

- Simmcast

- GTNets

OPNET Modeler, a network modeling and simulation software solution, is one of **OPNET Technologies, Inc.** flagship solutions and also its oldest product. Opnet Modeller includes many predefined and ready-to-use models of switches, routers or servers, supports a variety of protocols and provides intervention in various levels of construction with the use of C/C++ programming language.

# What is our proposal for the problem?

Proposal for the study of the Deadlock problem is the implementation through a network simulator, in our case the Opnet network simulator, of switch and node models that will form our preferred network topologies which are the Mesh, Torus and Fat tree. These models will make use of the Virtual channels in their hardware level, in the input and output buffers. In this structure will be also

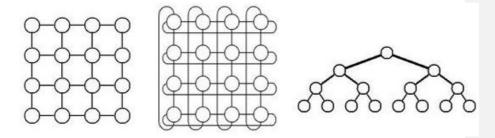

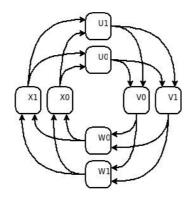

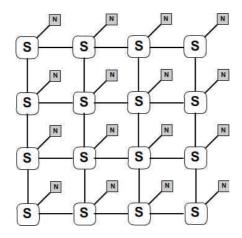

applied an efficient flow control method for packets, in a manner that the network can avoid to enter in a deadlock situation. In the below image 1 we can see the topologies of Mesh, Torus and Fat tree where the circles represent the switches.

Image 1 Mesh, Torus, and Fat Tree topologies

Through this implementation on the network simulator Opnet and the evaluation of the result collection, we will view the efficiency and the functionality of the created models. We will examine through the simulation process if the Deadlock avoidance policy has achieved and also how our models react, with variable network sizes and with different packet loads, for each one of our examined topologies.

What is the addition that the project makes to the world of HPC and interconnection networks.

This project will be made through the use of Opnet network simulator. That means that we can see fast and easy the results of the applied techniques, which we will make to our models. Having this way of experimenting we reduce the cost to minimum, avoiding in contrary the using of a real parallel computer with its high speed interconnection network.

The addition that this project has to offer in HPC community is the elimination of a serious network problem, through an implementation on a network simulator. That can work as a base so that we can further examine other

problems and techniques in high speed interconnection networks, and conclude to a proper network architecture that can serve our purposes.

As a conclusion to the first chapter we can say that the need for HPC in our times is very important so that we can give answers to important questions and solve complex problems. Thus the complexity of a High Performance Computer must be supported by an equal robust high speed network, problems that appear on those machines and to the networks that support them are important to solve. We need to pay attention on the details of such structures, like the network switches or the interconnection lines that support our systems, depending always on the different purposes and use for which we need such machines.

# 2 State of the art

In this 2<sup>nd</sup> chapter we will situate the position of our problem explaining the related areas of interest for our work. We will refer to the proposed actions that exist and can handle deadlock, focusing specially on the deadlock avoidance concept and its possible solutions. In the final section we are going to refer the relative with our project previous works that have studied the deadlock problem and its solution through the use of the virtual channels.

# 2.1 In which level is situated our problem

The HPC area is a rapidly evolving area of investigation which attends to help on the solution of complex problems. To succeed this purpose High Performance Computing has to make use of a combination of sophisticated hardware computing infrastructures with high speed interconnection networks. The hardware or network infrastructures may vary depending on the needs of the HPC designer. HPC hardware structures making use of parallel programming techniques to solve the complex problems, techniques that need continuous and high speed data exchange between the computational nodes. As the complexity of a problem increases and the programming technique acquire more data exchange to achieve the solution of the problem, the interconnection network is some times unable to handle all this amount of data due to finite hardware resources.

The interconnections networks are used nowadays for several applications and for different purposes. The type of the interconnection network varies depending on the goal that we want to achieve or the system architecture that is going to be applied. Different types of networks are listed below.

- Backplane buses and system networks

- Processor to memory interconnections

- Internal networks for asynchronous transfer mode (ATM)

- Multicomputer networks

- High Performance Computing interconnection networks

- Distributed shared-memory multiprocessor interconnection

- LAN's, MAN's, WAN's

- Industrial application networks

In our case we will focus on the interconnection network of High Performance Computers. Thus the demand for bigger computation power is always increasing, it create needs for the reliability and the accuracy of the interconnection network. The communication between processors in a computational node of an HPC system is done through buses. These connections have small length which is limited in the length of few millimeters and due to their construction materials can provide small communication latency. This latency compared with the communication latency on an interconnection network is almost zero, thus the length of a communication line can exceed in some meters or tens of meters and the constructional material of the communication wire can cause extra latency to the packet delivery. Having in mind that the network is the slowest form of communication between processors, we would like to make the communication time as smaller as possible and eliminate communication problems. The network has to support respectively the transition of the information, without causing delays or rejection of packets, due to several problems that can appear.

For the design of the interconnection network we have to consider the network infrastructure that will form the network and will connect the nodes between them. The type of communication wires, the switches or routers and their combination with the routing techniques that we need, have to be examined in detail so that we can have a robust interconnection network and avoid the problems that can appear under a heavy communication load.

To understand the causes of an interconnection problem, we have to focus on the way that the intermediate hardware infrastructures, that our network uses, work. The switches on an interconnection network play a serious role in the transition of packet from their source to their destinations, thus they manage and provide a path for the traversed packet. In the case that a problem occurs or the heavy load makes these infrastructures unable to serve the network, we need to focus our interest on the internal architecture of a switch and examine the pipeline with which it functions. We need to study the different elements from which a switch is structured, how they are combined together to work and what are the necessary alterations that we need to make in hardware and logic level to solve a network problem.

For the purposes of the deadlock avoidance with the use of virtual channels is necessary to examine in this lower level, how the packets enter and make use of the switch hardware resources, how the problems appear while the traffic load increases and what are the possible changes that need to be made in hardware and software level, to eliminate the possibility that a deadlock will occur.

While the amount of traffic load increases, increase also and the possibility of simultaneous need by the packets to have access over the same hardware resources, such as the input and output buffers of the switch. Because of that we have to use a technique such as virtual channels that can provide alternative ways of access on these resources and will not stop or delay significantly the packet traversal on the network.

For the investigation of such a problem, we will need a tool that can provide us access to the various levels of the network structure, allowing us to alter the internal logic and components of our network elements. Proper tool for that purpose can be a network simulator that will support changes in that level and can give us results, through which we can examine the effects of our alterations and if needed improve the structural logic.

# 2.2 What are the existing proposals for the problem

As the big delays on the packets transition can significantly reduce the calculation ability of an HPC structure, the undelivered packets can have

catastrophic sequences for the ability of such a machine to produce the correct amount of work, due to lack of information exchange. Some of the most serious problems that can cause undelivered packets inside our network are listed below in image 2 with their proposed solutions.

Image 2 Causes of undelivered packets

Phenomena like deadlock, livelock or starvation, appear in interconnection networks due to the finite number of resources and can create the problem of undelivered packets or even paralyze the network. This is caused because of conflicts between agents and resources, in our case packets and packet buffers. An explanation for each one of the phenomena follows.

# Deadlock

Deadlock is the situation where two or more competing agents waiting each one for the other to release critical resources. The problem occurs because none of the agents is able to progress due to the denial of another agent to release its resources or to reach in a compromise.

# Livelock

Livelock is the condition when two or more agents are continually changing their state in response with the state of other agents, causing a continuous loop. Result of that is that none of the agents can have access to the resources. Livelock is similar with deadlock thus no progress is made over the resources, and differs in the way that none of the agents is blocked or waiting for a resource.

#### Starvation

Starvation is the situation that the competing agents may never be granted to the requested resources falling in the situation that an agent is starved. A network falls in starvation when the requests by the agents for resources are coming more frequently that they can been handled.

For our case, we will examine the deadlock phenomenon, which is the most serious of all the above. Deadlock may occur due to four conditions which are the Mutual exclusion, the Hold and Wait condition, a no pre-emption condition or due to circular wait condition. A small explanation for each one of them follows.

- 3 *Mutual exclusion* condition is when a resource is either assigned to one agent or it is available.

- 4 *Hold and wait condition* is when an agent which already holding resources may request new resources.

- 5 *Non preemption condition* is when only an agent who holds a resource may release it

- 6 *Circular wait condition* is the condition where two or more agents form a circular chain where each agent waits for a resource that the next agent in the chain holds.

For Deadlock there are three known solution techniques, Prevention, Recovery and Avoidance. Each one of them refers to a different approach for the deadlock.

### Prevention

The system itself is built in such a way that there are no deadlocks. That means that the system makes sure, that at least one of the necessary for deadlock conditions will never occur. This is done for example in circuit switching where the resources are granted before the transmission starts. It is very conservative approach and may lead to very low resource utilization.

#### Recovery

Deadlock recovery does not impose any restrictions to the routing mechanism, but rather allows deadlock to occur. Deadlock recovery attends to give a solution to the problem after that has caused, forcing the agents that hold resources to release them, allowing with that way other agents to use those resources and break the deadlock.

#### Avoidance

Deadlock avoidance is the technique where certain information about agents is available in advance of resource allocation. For every resource request, the system sees if granting the request will mean that the system will enter an unsafe state, meaning a state that could result in deadlock. The system then only grants request that will lead to safe states. In order for the system to be able to figure out whether the next state will be safe or unsafe, it must know in advance at any time the number and type of all resources in existence, available, and requested. One known algorithm that is used for deadlock avoidance is the Banker's algorithm. However, for many systems it is impossible to know in advance what every process will request. This means that deadlock avoidance is often impossible.

In our project we will focus specially on the deadlock avoidance technique and how this is achieved with the use of virtual channels. The virtual channels will provide to our system extra alternative resources that can be used by the agents, meaning packets, to avoid other blocked resources and with that way avoid

deadlock. Changes in the mechanism of the switch have to be done so that can support this new structure and avoid resource dependencies to occur. The logic of the mechanism now has to put a specific order on the resources and restrictions on the way that these resources are going to be accessed by the packets. The implementation and the examination of that proposal will be studied through the network simulator in which we will implement and test our models.

## 2.3 Related works

Previous implementations for the deadlock refer to the solution of the problem in different levels and with various ways. Deadlock problem appears from processor to processor communications, to different types of networks, deadlock on chip level or most often in databases and multi-threaded applications. Deadlock occurs in software where a shared resource is locked by one thread and another thread is waiting to access it and something occurs so that the thread holding the locked item is waiting for the other thread to execute. Another case where deadlock can occur is in databases where one application has asked for a lock on a table. It then requires a second table but another application has locked the second table and is waiting to get a lock on the first.

Some of the related with our project implementation refer to various approaches like the use of adaptive routing using only one virtual channel [4], virtual lanes for ATM networks [5] or the implementation on QNOC router with a dynamic virtual channel allocation [6]. In these researches is studied the effect and the utilization of the virtual channels and the appropriate number of them for the deadlock solution but with different types of network or routing strategy.

None of the previous implementations or approaches to the problem is referring to the solution of deadlock avoidance through a simulation process, for the specific network models that we are going to study, and the comparison of the results between these tree topologies. In our case, thus the construction of a network with the appropriate policy needs further examination and implementation we are using a network simulator. This approach offers the ability to change the numbers of virtual channels and the buffer capacity that each one of they contains. Also we can experiment with the deadlock avoidance policy and see how we can implement it to our network topologies, with the minimum cost on resources while having the desired result.

# 3 Theoretical backs

In the 3<sup>rd</sup> chapter we will focus on the problem of deadlock and its possible solutions. We will see the reasons that cause the deadlock and how we can avoid it by the use of virtual channels. The definition of virtual channels will be given next and the possible uses that the virtual channels have. At the last part of the chapter will be described the parts of the Opnet network simulator that our implementation is going to uses and important details about their use and functionality.

# 3.1 Theory

#### 3.1.1 Deadlock Avoidance

A **deadlock** is a situation where in two or more competing actions are waiting for the other to finish, and thus neither ever does. It is often seen in a paradox like 'the chicken or the egg'.

**In computer science**, deadlock refers to a specific condition when two or more processes are each waiting for each other to release a resource, or more than two processes are waiting for resources in a circular chain. Deadlock is a common problem in multiprocessing where many processes share a specific type of mutually exclusive resources known as a software, or soft, lock.

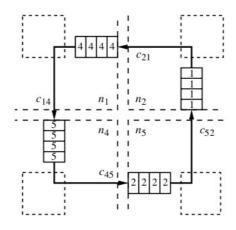

Image 3 Deadlocked configuration

Deadlock occurs **in an interconnection network** when a group of agents, usually packets are unable to make progress because they are waiting on one another to release resources, usually buffers on channels. If a sequence of waiting agents forms a cycle, as it shown in image 3, then the network is deadlocked. This can have catastrophic sequences for the network. When some resources of the network are been occupied with deadlocked packets other packets that coming block on these resources and cannot proceed to their destination. [1 ch.14]

For **Deadlock handling** there are three known techniques that has been used and these are

- 1. Deadlock Prevention.

- 2. Deadlock Avoidance

- 3. Deadlock Recovery

To prevent this situation, networks must either use deadlock avoidance, method that guarantee that a network cannot deadlock, or deadlock recovery in which deadlock is detected and corrected. As in almost all the modern networks [1 ch.14], our project will make use of the Deadlock Avoidance technique.

Deadlock appears because the network resources such as channels and buffers are limited. We have to focus that in the switched based networks, like these we are going to study, where each switch is connected with a processor. The switches that are connected with a processor can send and receive messages from the processor.. Due to the similarity between the direct networks and the switch based networks we can apply that policy for the deadlock avoidance. [3 ch.1]

To achieve the **Deadlock Avoidance**, the routing mechanism applied has to restrict the allowed paths for the packets that keep deadlock free the global network state. An approach for the solution of this is to **put an order on the resources** that want to be accessed by the packets, in the minimum way for having network full access. Assigning the resources partially or totally to the packets, so that cannot exist the possibility that a circular dependency will appear. With that way we are applying escape paths to the packets, no matter where they are inside the network, avoiding the probability that they will come in a deadlock situation.

**Critical resources** on the deadlock avoidance, in network level, are the **connection lines and the buffers** associated with them. There must be an order in the access of the resources by the packet, while these are travelling from their source to the destination.

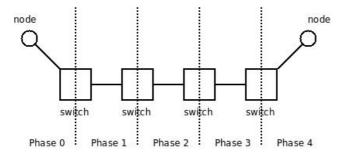

Image 4 Stages of traversing packet

When a packet inserted in the network at the phase 0 is entering in a switch. Through the communication lines goes to the phase 1 where the next switch is, and continues until it reach its destination. While not exist recirculation of packets, once a packet have reserved an output channels from the first phase, it cannot request any other output channel from the same phase, thus there are no dependencies between the output channels of the same phase. Similarly a packet that has reserved an output channel on a given phase, cannot request for an output channel at a previous phase. With that way we only have dependencies

from this phase to the next phase. Sequence of that is that we don't have cyclic dependency between channels and we avoid deadlock.

While using a flow control method, like **store and forward** or **virtual cut through**, the agents are packets and the resources are the packet buffers. At any given time each packet can only occupy one packet buffer. When a packet request for a new packet buffer, it should release the old packet buffer a short time later. In our case the resources will be the virtual channels that will replace the packet buffers as entities.

The lines (agents) and the virtual channels (resources) are related with "Wait for" and "Hold" relations. If a line holds a buffer, then that buffer is waiting from the line to be released. If that not happen, a deadlock occur.

A Wait Wait Hold Hold U V W X

Image 5 Dependence graph

Image 6 Wait for and Hold graph

A representation of the relations between agents and resources can be done through the **dependence graph** and the **wait-for graph**. In both above images 5 an 6, we can see how connections A and B occupying some resources while they are waiting for some others. A occupies channels **u** and **v** and waits for channel **w** which is occupied by the connection **B**. Similarly the connection **B** holds channels **w** and **x** and waits for channel **u**.

If we focus on the Hold relations that lead to the buffers  $\mathbf{u}$  and  $\mathbf{w}$  from the lines  $\mathbf{A}$  and  $\mathbf{B}$  in Image 6.a, and we redraw these lines to the opposite direction as

Wait for relations we have the Image 6.b. Here we can see, from the dotted arrows that appear a circulation between the resources. This circulation shows us that the configuration is deadlocked.

In order to occur deadlock, the lines have to acquire buffer resources and wait on others, with a way that creates a cycle in the wait for graph. This cycle is a necessary nut not sufficient condition for a deadlock. If we can manage to eliminate the cycles from the resource dependence graph we can we eliminate the possibility of a circular dependence on the wait for graph and as a sequence we avoid to deadlock the network.

If the above scheme we replace the buffer resources with the two equal virtual channels (explained in next section), we will have a dependence graph like the one below, in Image 7.

Image 7 Dependence graph with 2 VC

# 3.1.2 Virtual Channels

To avoid Deadlock to our network we have to apply a flow control method to allocate the appropriate for the packet resources. Important resources for the interconnection network are the communications lines and the buffers. Buffers are storage inside nodes and switches, with the form of a memory. In this

memory is where the packets are temporarily stored, while traversing to their destination through the communication lines. Dependent on the switching technique and flow control that we use, we may respect to the packets either as entire packets or as flits. Flits or flow control units, are the smaller units from which the packet consists and create the header, data and tail sections of the packet. The flits are also divided in smaller units called phits (phase digits) which are the binary representation of a flit.

While the topology of the network determines the possible ways that a packet has to reach its destination, the flow control is the method applied to the network that organizes the network traffic. Flow control determines when and how a travelling packet inside the network can overcome network problems and advance itself until destination. This applied strategy must avoid resource conflicts between packets, keeping with that way the channels idle.

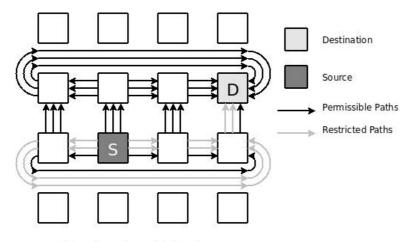

As an analogy to the real world, we should provide alternative pathways if it occurs a problem in a highway road, so that the incoming traffic can overcome the accident and continue its way. Having this analogy in mind, at hardware level, if a packet gets blocked in a buffer while expecting other resources to get free, incoming packets should not get blocked by this packet. The flow control mechanism should provide them an escape path in the form of an alternative buffer, so that the packet can proceed. The implementation of this in hardware is the partition of the used buffer in several pieces that we call virtual channels.

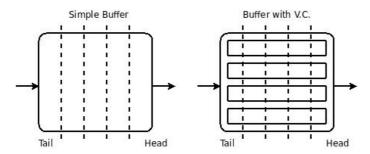

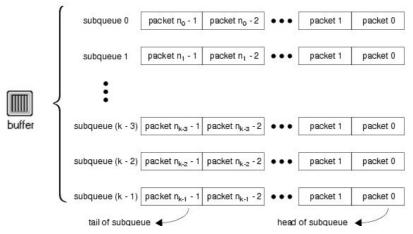

If we consider that the buffer is a (FIFO) **First In First Out queue**, Virtual Channels is the partitioned representation on several smaller parts of memory, called or else subqueues. These subqueues are those that used as escape paths for the packets. The implementation can be in hardware or software level. In hardware can be in form of separated buffers with a circuit flow control mechanism. In software level the unique buffer is treated as partitioned, applying the flow control policy through a software implementation over the virtual channels. To make our job easier for this purpose we will use the Opnet

network simulator, partitioning virtually a predefined model of a FIFO buffer queue as it shown below on image 8.

Image 8 Simple buffer & Buffer with VC

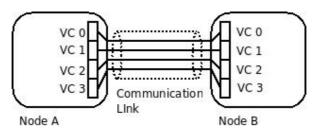

Buffers are commonly operated as FIFO queues. Therefore, once a message occupies a buffer for a channel, no other message can access the physical channel, even if the message is blocked. Alternatively, a physical channel may support several logical or virtual channels multiplexed across the physical channel. Each unidirectional virtual channel is realized by an independently managed pair of message buffers. Logically, each virtual channel operates as if each were using a distinct physical channel operating at half the speed. This representation can be seen in Image 9. Virtual channels were originally introduced to solve the problem of deadlock in wormhole-switched networks [3 ch2]. Deadlock is a network state where no messages can advance because each message requires a channel occupied by another message.

Image 9 Communication lines with VC

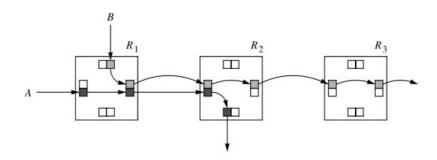

Virtual channels can also be used to improve message **latency** and **network throughput**. By allowing messages to share a physical channel, messages can make progress rather than remain blocked. For example, in Image 10 we see two messages crossing the physical channel between routers R1 and R2. With no virtual channels, message A will prevent message B from advancing until the transmission of message A has been completed.

Partitioning the buffer in virtual channels, both messages continue to make progress. The rate at which each message is forwarded is nominally one-half the rate achievable when the channel is not shared. In effect, the use of virtual channels decouples the physical channels from message buffers, allowing multiple messages to share a physical channel in the same manner that multiple programs may share a CPU. The overall time a message spends blocked at a router waiting for a free channel is reduced, leading to an overall reduction in individual message latency.

Image 10 Packets advances with the use of VC's

This approach described, does not place any restrictions on the use of the virtual channels. Therefore, when used in this manner these buffers are referred to as *virtual lanes* [5]. Virtual channels were originally introduced as a mechanism for deadlock avoidance in networks with physical cycles, and as such routing restrictions are placed on their use. Virtual channels also can have different classes, meaning that each virtual channels can have its own type of priority dependent on the characteristics that we want to provide them. Those classes may restrict the use of the virtual channels for packets, dependent on the virtual

channel buffer utilization or the priority type of a packet. For example, **packets** may be prohibited from being transferred between certain classes of virtual channels to prevent cyclic waiting dependencies for buffer space. Thus, in general we have virtual channels that may in turn be made of multiple lanes. While the choice of virtual channels at a router may be restricted, it does not matter which lane within a virtual channel is used by a message, although all of the flits within a message will use the same lane within a channel.

Acknowledgment traffic is necessary to regulate the flow of data and to ensure the availability of buffer space on the receiver. Acknowledgments are necessary for each virtual channel or lane, increasing the volume of such traffic across the physical channel. Furthermore, for a fixed amount of buffer space within a router, the size of each virtual channel or lane buffer is now smaller. Therefore, the effect of optimizations such as the use of acknowledgments for a block of flits or phits is limited. If physical channel bandwidth is allocated in a demand-driven fashion, the operation of the physical channel now includes the transmission of the virtual channel address to correctly identify the receiving virtual channel, or to indicate which virtual channel has available message buffers.

For the recognition of the packets and their corresponding direction to the virtual channels, has to be added a flit more to the header of each packet. That flit is inserted in the source node and will contain the number with the desired virtual channel for the packet. With that way, it will be described the preferred route that the packet will follow through the network, and will be applied the necessary flow control mechanism on the input or output virtual channels of a switch.

#### **3.1.3 OPNET**

For our project, the implementation will be based on the Opnet network simulator. Opnet network simulator is a simulation tool equipped with many predefined models of nodes, servers, switches and communication lines, which exist in the market. Also supports a wide range of protocols, and allows altering on the predefined characteristic models. The simulator allows user intervention in 4 different levels that start from the network or subnetwork level, to the module level, the process level and in the lower part is the code level. Here Opnet network simulator supports the use of external commands based in the programming language of C/C++. With that we way we can manage the existing models and protocols, or design and create a new one for our purposes.

### 3.1.3.1 **Network**

The network defines the overall scope of the system we are going to simulate. It's a representation of the objects that participate in the network construction. The network model specifies the objects inside the network, as well as their physical locations, interconnections and configurations. It can contain subnetworks and nodes, connected through several links, giving a more complex structure to the network. This supported complexity provides us easiness to design networks similar to the appearance and functions, with the real ones that we want to simulate.

The interprocessor communications as in High Performance Computing can be viewed as a hierarchy of services. These services begin form a higher level, the application layer, in which are performed actions for the preparation of the packets and the data encryption and data compression, until the physical layer which is responsible for the transition of the packets that come from a higher layer. We can view such a layering in the communications services, especially for the Local and Wide Area Networks (LAN's and WAN's). This layering can be characterized in three layers, and these are from the lower to the higher.

### Physical layer

The physical layer is responsible for packet transfer through the physical channel from switch to switch.

### **Switching layer**

Switching layer make use of the physical layer, implementing mechanisms so that can forward the messages to their destination.

### **Routing layer**

At the routing layer are taken the routing decisions for the output channels that can provide a path, so that the packet can continue through the network to its destination.

The routing mechanisms and their properties (deadlock or livelock freedom) are determined mostly by the switching layer. The switching techniques that are implemented inside the switching layer are responsible to set the switch inputs and outputs and the appropriate time that the packet needs to travel the path inside the switch. [3 ch.3]

These switching techniques make use of flow control mechanisms that are responsible for the packet transfer synchronization between the switches. The flow control mechanisms are related with the management of the packet buffers. Determine how the buffers are accessed and released by the packets and which is the appropriate policy when exist blocked packets inside these buffers. [3 ch3]

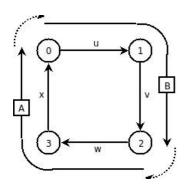

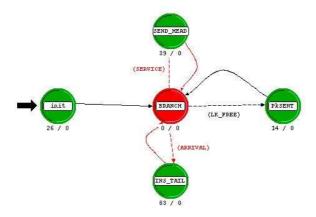

Image 11 Network Domain

In Image 11 we can view the network representation of 4x4 Mesh. We see the similarity with the real topology of a mesh, how the computation node that insert the packets in the network, are connected with the switches, and how the connections of the switches forms our topology.

### 3.1.3.2 **Nodes**

A communication node exists within a subnetwork and represents a network device with a wide range of possible capabilities. The actual function and behaviour of a node is determined by its node model, which is specified by the node's "node model" attribute. A node model is defined in the Node Editor and specifies the internal structure of the node. A node may refer to a derived node model rather than an actual node model specified in the Node Editor.

#### Switch node model

The Switch node model supports large numbers of incoming and outgoing data links and performs packet routing at high speeds. Within the model are defined the characteristics that we want to provide, in form of a sequence of modules

# **Computation node model**

Can generate and receive transfers of files or sparse packets, also depend on the architecture and the functionality that we want to apply to our network.

#### **Communication lines**

Links allow communication of information between nodes in the form of structured messages called packets. When a packet is submitted to a transmitter in a source node, the packet is conveyed over a link to a receiver in a destination node. A transmitter may support multiple outgoing channels into a link and, similarly, a receiver may support multiple incoming channels from a link as it shown below in the image 12.

Image 12 Communication channels

A link is actually composed of one or more communication channels, each of which defines a connection between a transmitter channel and a receiver channel. A communication channel can be thought of as a pipe, where packets are placed in one end by a transmitter channel and retrieved at the other end by a receiver channel. If a link has multiple communication channels, it can be thought of as a "bundle" of pipes, each one conveying packets from the source node to the destination node.

# **Simplex and Duplex Point-to-Point Links**

A **point-to-point** link can be thought of as a bundle of one or more communication channels between the transmitter(s) and receiver(s) that it connects. Within a point-to-point link, the number of communication channels is static, because there is one communication channel between each transmitter channel and receiver channel of the same index. Packets sent by transmitter channel in the source node will be received by the receiver channel with same index in the destination node. Each communication channel acts independently of the others in the same link, as though it were defined in a separate and parallel point-to-point link.

A **simplex point-to-point** link defines a connection from a transmitter in the source node to a receiver in the destination node. Packets are conveyed in that one direction. A duplex point-to-point link, however, defines a pair of connections between two nodes, connecting a transmitter in each node to a receiver in the other. Packets can flow in both directions, from each node to the other.

For a point-to-point link to be operable, it must be attached to point-to-point transmitters and receivers in the nodes that it connects. The transmitter and receiver of a simplex **point-to-point** link are designated using its "transmitter" and "receiver" object attributes. For duplex links, four attributes ("transmitter a", "receiver a", "transmitter b", and "receiver b") serve to identify the modules within the nodes to which the link is attached.

### 3.1.3.3 Node modules

The internal structural complexity of network nodes and their scope of activity can vary greatly depending on the system which is modelled. For this purpose exist several modules that can help us achieve the level of complexity we want.

### **Processor modules**

Image 13 Processor module

Processor modules are the primary general-purpose building blocks of node models. This process model can respond to external events or interrupts as desired to model a specific function. Processors can be connected to other modules to send and receive packets via any number of packet streams.

Processor modules are used to do general processing of data packets. A typical processor might receive a packet on an input stream, do some processing, and send the packet out again on an output stream. The output packet might be delayed for a short time, or it might be modified with respect to the input packet.

### **Queue Modules**

Image 14 Queue module

Node models may employ both processor modules and queue modules to implement general processing of packets. Normally, a processor module would be used in cases where a packet can be completely processed in response to the interrupt associated with its arrival or generation. If this is not the case, and it is

necessary to buffer the packet while awaiting a later event to complete processing, then a queue module, with its additional buffering resources, is likely to be more correct. This is particularly true if multiple packets must be buffered simultaneously.

Queue modules provide a superset of the functionality of processor modules. Like processors, they can execute an arbitrary process model that describes the behaviour of a particular process or protocol, and can be connected via packet streams to other modules, allowing them to send and receive data packets. The process model can also affect the queue object's list of attributes.

The primary difference between processors and queue modules is that queues contain additional internal resources called subqueues. Subqueues facilitate buffering and managing a collection of data packets. While it is possible to implement this functionality with ordinary processor modules, the use of subqueues, provide greater flexibility and ease of implementation of a variety of queuing disciplines. Moreover, subqueues automatically compute a number of statistics about their operation

Image 15 Subqueue representation

Each queue module contains a definable number of subqueues as we see on image 15. A subqueue is an object which is subordinate to the queue object and which has its own attributes used to configure it. The capacity of each subqueue to hold data is unlimited by default, but a limit may be set on the number of packets or the total size of all packets (or both) within a subqueue. It is up to the processes in the queue to determine what action to take when subqueues become full: packets may be removed to create space for new arrivals, or the new arrivals may be discarded. Because the user controls the process model executed by a queue, it is possible to model any queuing protocol by defining the manner in which the subqueues are accessed and managed.

#### Transmitters - Receivers

Transmitter modules serve as the outbound interface between packet streams inside a node and communication links outside the node. There are two types of transmitter modules, corresponding to the different types of communication links: point-to-point and bus.

Image 16 Receiver – Transmitter

Several of the parameters controlling transmission of packets from point-to-point and bus transmitter modules are actually specified as attributes of the link. Within a node model, a transmitter module is considered to be a data sink. Therefore, although they may have many input packet streams, transmitter modules do not have output packet streams. From the point of view of the network model, a transmitter module acts as the node's output port, to which a communication link of the corresponding type may be connected: simplex and duplex links to point-to-point transmitters and bus links to bus transmitters.

### 3.1.3.4 Connections

#### **Packet streams**

Image 17 Packet stream

Packet streams are connections that carry data packets from a source module to a destination module. They represent the flow of data across the hardware and software interfaces within a communication node. There are three different methods for transferring a packet over a stream and notifying the destination module of its arrival: scheduled, forced, or quiet.

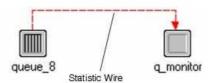

# Statistic wires

Image 18 Statistic stream