## ENTORNO GRÁFICO DE CONFIGURACIÓN PARA EL SOFT-CORE OPENRISC

Memòria del Projecte Fi de Carrera

d'Enginyeria en Informàtica

realitzat per Felipe Pinto Buerba

i dirigit per Marc Moreno Berengué

Bellaterra, Septembre de 2010

# ÍNDICE

|                                                |           |

|------------------------------------------------|-----------|

| <b>1 Introducción .....</b>                    | <b>1</b>  |

| 1.1 Motivación .....                           | 1         |

| 1.2 Objetivos del proyecto .....               | 2         |

| 1.3 Organización de la Memoria.....            | 3         |

| <br>                                           |           |

| <b>2 Metodología de trabajo i entorno.....</b> | <b>4</b>  |

| 2.1 Estado del Arte.....                       | 4         |

| 2.1.1 FPGAs.....                               | 5         |

| 2.1.2 SoCs e IPs .....                         | 8         |

| 2.1.3 Procesadores Softcores de 32 bits .....  | 10        |

| 2.2 Entorno de desarrollo OpenRISC .....       | 16        |

| 2.2.1 Entorno Hardware .....                   | 16        |

| 2.2.2 Entorno Software para OpenRISC.....      | 24        |

| 2.3 Entorno de desarrollo Web .....            | 25        |

| <br>                                           |           |

| <b>3 Diseño e implementación .....</b>         | <b>26</b> |

| 3.1 Arquitectura del sistema .....             | 26        |

| 3.2 Diseño de la aplicación.....               | 34        |

| 3.3 Diseño de los módulos .....                | 38        |

| 3.4 Entorno Gráfico .....                      | 47        |

| <br>                                           |           |

| <b>4 Test y Resultados .....</b>               | <b>52</b> |

| 4.1 Entorno de verificación .....              | 52        |

|                                                 |           |

|-------------------------------------------------|-----------|

| 4.2 Test y validación del sistema.....          | 56        |

| 4.3 Análisis de recursos de la aplicación ..... | 61        |

| <b>5 Conclusiones .....</b>                     | <b>63</b> |

| 5.1 Conclusiones.....                           | 63        |

| 5.2 Evolución futura.....                       | 64        |

| 5.3 Experiencia personal y profesional.....     | 64        |

| <b>Bibliografía .....</b>                       | <b>65</b> |

# ÍNDICE DE FIGURAS

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| 2.1. Estructura interna de una FPGA .....                               | 6  |

| 2.2. Procesador Leon 3.....                                             | 12 |

| 2.3. Diagrama de bloques del procesador MicroBlaze .....                | 13 |

| 2.4. Diagrama de bloques del procesador NIOS II .....                   | 15 |

| 2.5. Arquitectura del Core OpenRisc 1200.....                           | 16 |

| 2.6. Diagrama de Bloque CPU/DSP OpenRisc 1200 .....                     | 17 |

| 2.7. Interfaz e interconexiones en una arquitectura punto a punto ..... | 19 |

| 2.8. Read/Write simples bus Wishbone .....                              | 22 |

| 2.9. Conexión Wishbone punto a punto .....                              | 22 |

| 2.10. Conexión Wishbone bus compartido.....                             | 23 |

| 2.11. Conexión Wishbone con switch de conexiones.....                   | 23 |

| 2.12. Conexión Wishbone con pipeline .....                              | 24 |

|                                                                         |    |

| 3.1. Diagrama de casos de uso .....                                     | 27 |

| 3.2. Herramienta phpMyAdmin .....                                       | 30 |

| 3.3. Arquitectura del Sistema .....                                     | 33 |

| 3.4. Estructura de la Aplicación.....                                   | 35 |

| 3.5. Modelo Entidad-Relación .....                                      | 36 |

| 3.6. Esquema general de la base de datos .....                          | 36 |

| 3.7. Diagrama de Scripts del portal web.....                            | 38 |

| 3.8. Estructura fichero verilog .....                                   | 45 |

| 3.9. Fichero .vhf .....                                                 | 46 |

| 3.10. Entorno Gráfico (Portada) .....                                   | 47 |

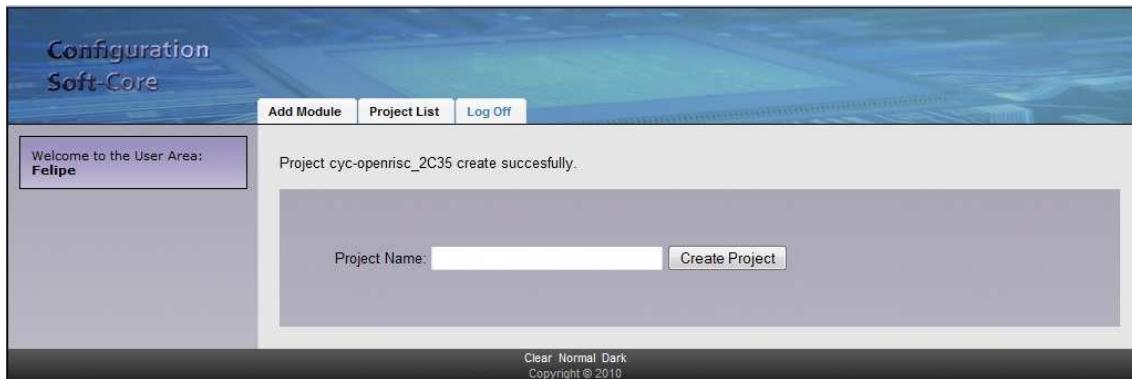

| 3.11. Entorno Gráfico (Creación de proyecto) .....                      | 47 |

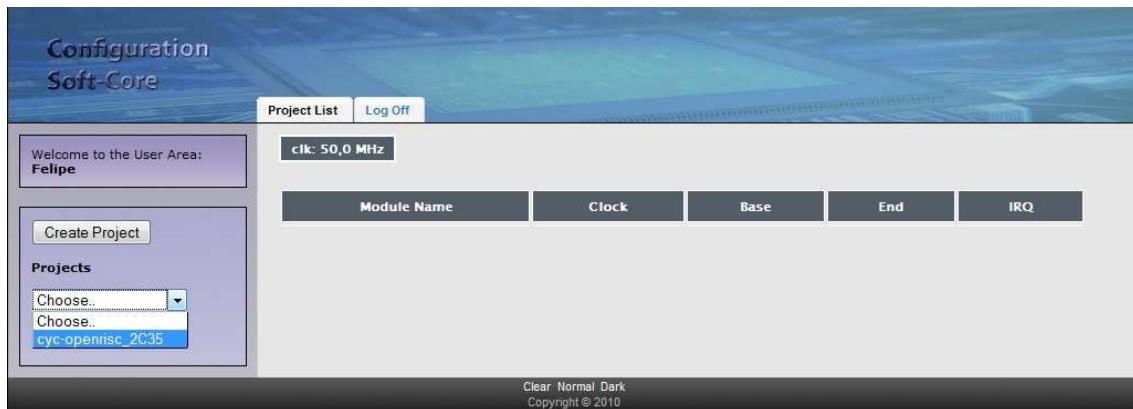

| 3.12. Entorno Gráfico (Selección proyecto).....                         | 48 |

|                                                          |    |

|----------------------------------------------------------|----|

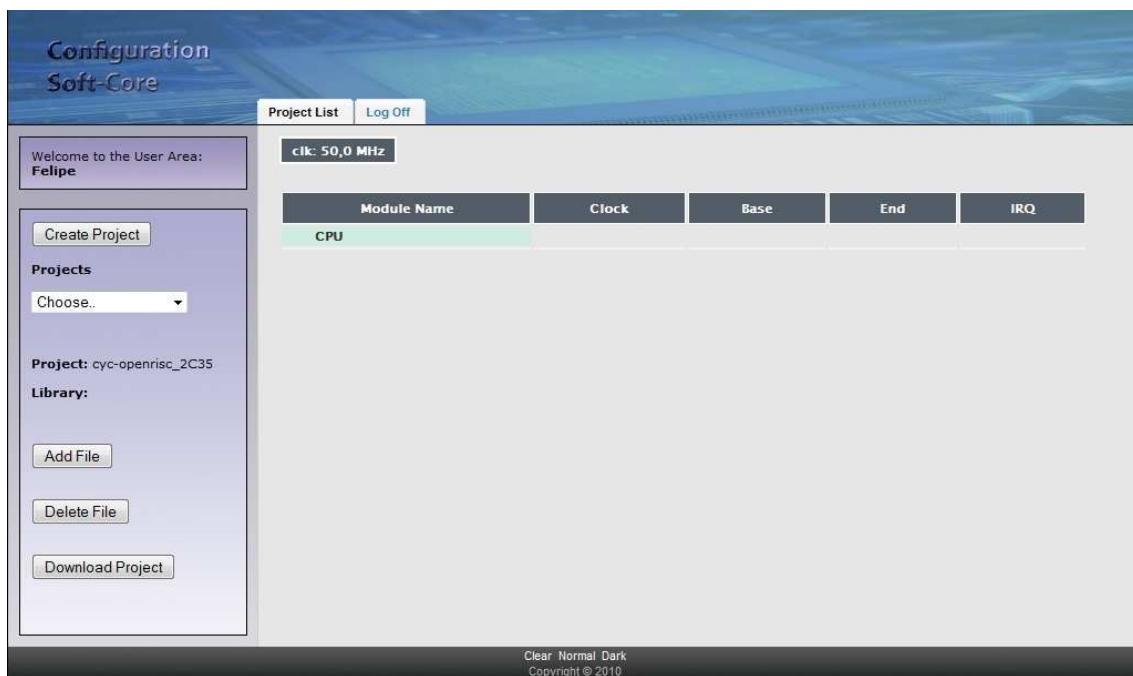

| 3.13. Entorno Gráfico (Librería Componentes).....        | 48 |

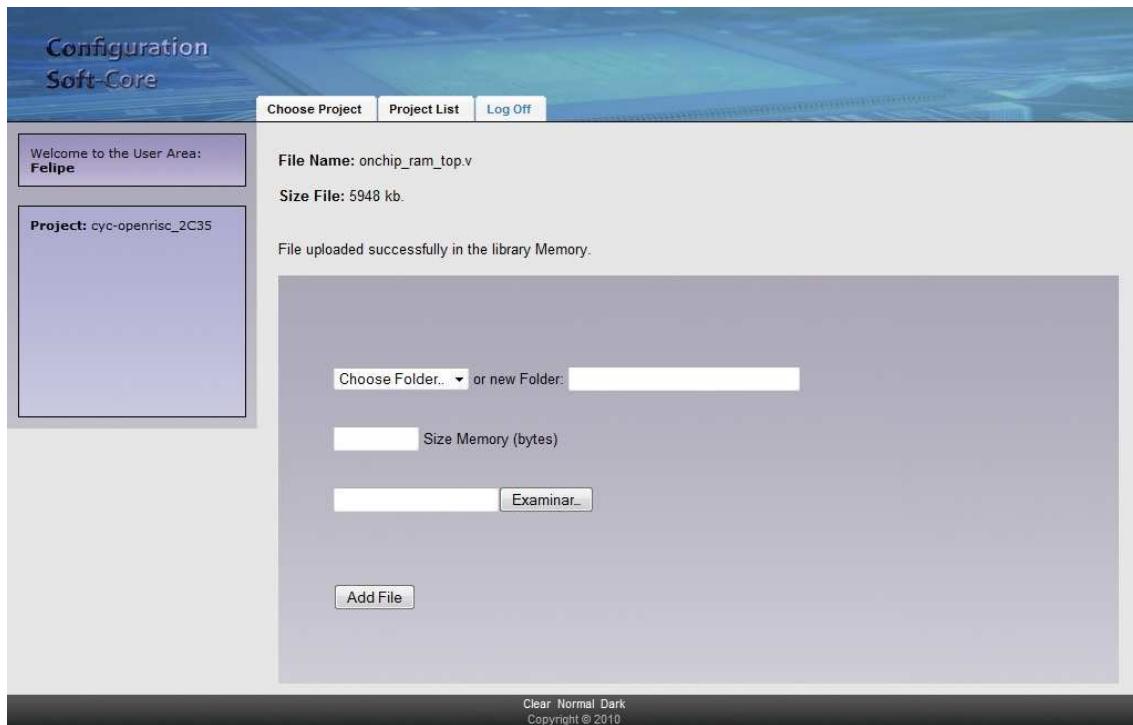

| 3.14. Entorno Gráfico (Subir archivos) .....             | 49 |

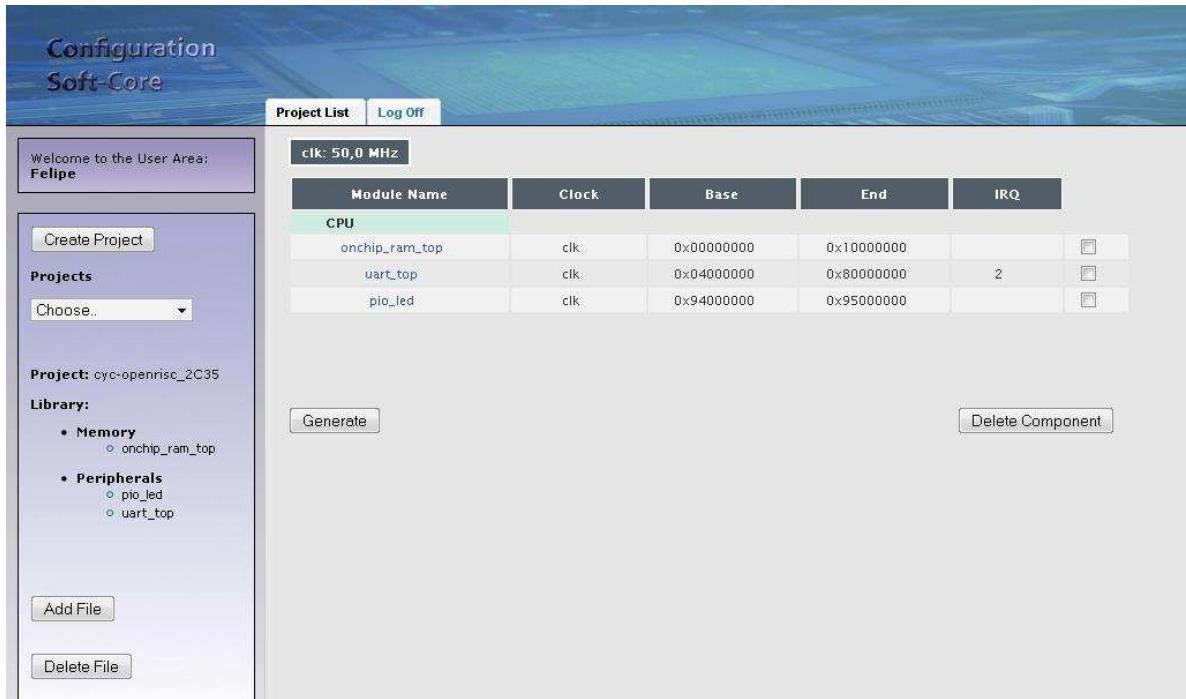

| 3.15. Entorno Gráfico (Componentes insertados) .....     | 50 |

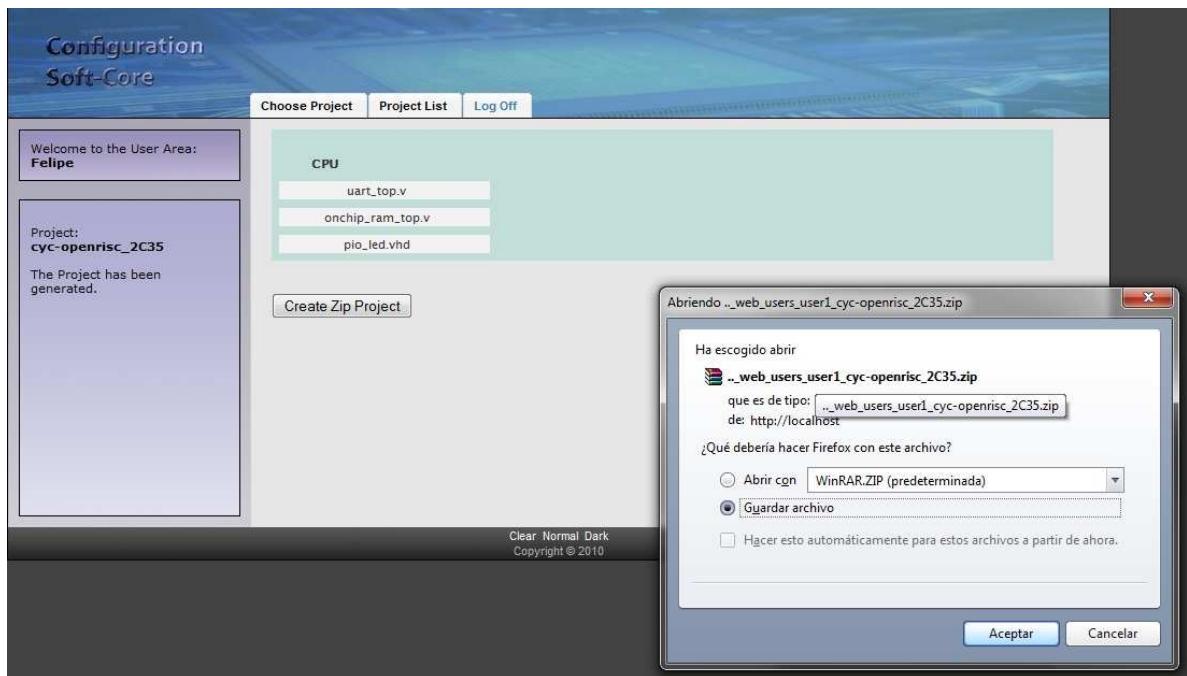

| 3.16. Entorno Gráfico (SoC generado).....                | 51 |

|                                                          |    |

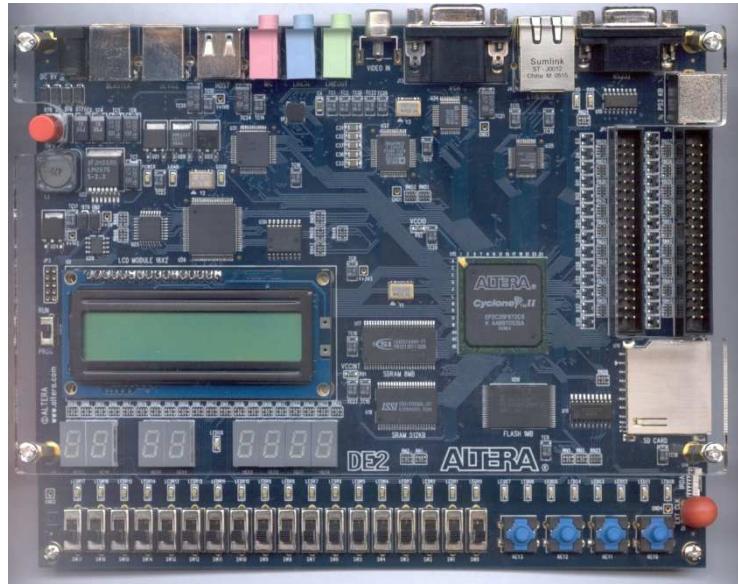

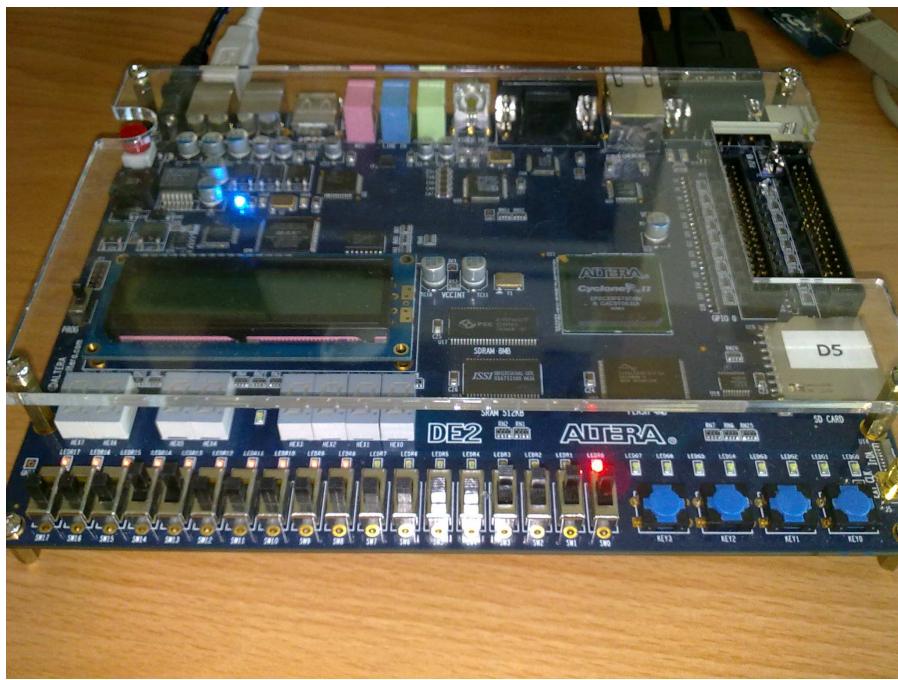

| 4.1. Placa DE2-ALTERA.....                               | 53 |

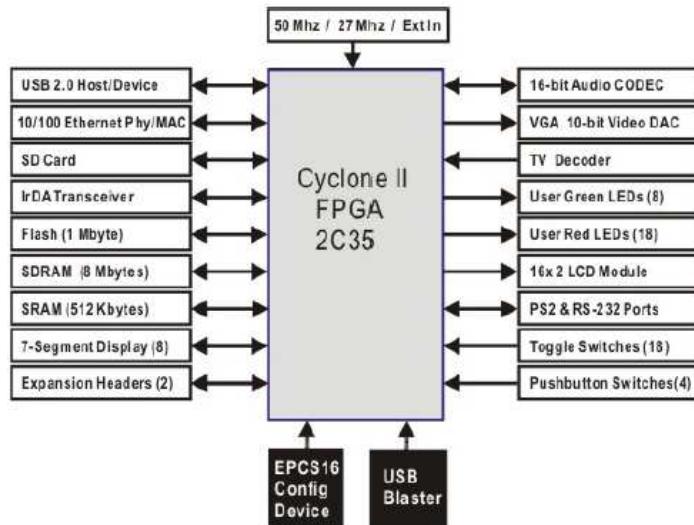

| 4.2. Diagrama Bloque de la placa DE2 .....               | 54 |

| 4.3. Bridge USB-a-UART .....                             | 54 |

| 4.4. Programa QUARTUS II.....                            | 56 |

| 4.5. SoC generado.....                                   | 57 |

| 4.6. Diagrama de Flujo del Sistema .....                 | 59 |

| 4.7. Prueba test_uart.c.....                             | 60 |

| 4.8. Prueba Pio Led .....                                | 60 |

| 4.9. Características Intel HEX.....                      | 61 |

| 4.10. Resumen de Síntesis y Análisis de nuestro SoC..... | 62 |

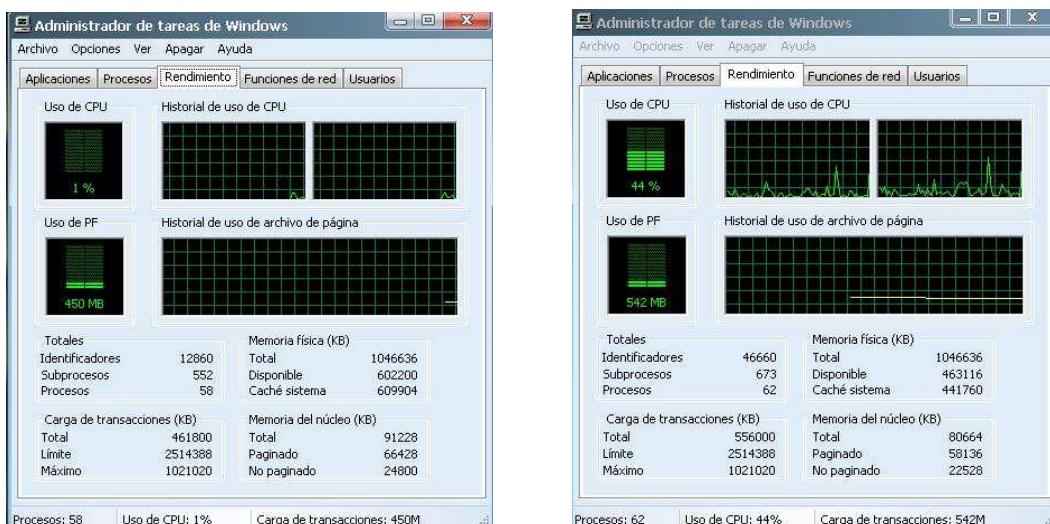

| 4.11. Uso CPU del sistema.....                           | 62 |

El sotasingnat, Marc Moreno Berengué

Professor/a de l'Escola Tècnica Superior d'Enginyeria de la UAB,

**CERTIFICA:**

Que el treball a què correspon aquesta memòria ha estat realitzat sota la seva direcció per en Felipe Pinto Buerba

I per tal que consti firma la present.

Signat: .....

Bellaterra, 6 de Setembre de 2010

## **Agradecimientos**

En primer lugar, agradecer a mi tutor su tarea de guía y consejo durante todo el desarrollo de este proyecto.

En segundo lugar a mi familia, que me ha ayudado en todos estos años de carrera, sobre todo en los malos momentos.

Y finalmente a mis compañeros de carrera, que sin ellos este camino no habría sido tan agradable como lo ha sido, compartiendo preocupaciones, alegrías, miedos, pero ante todo grandísimos momentos.

Gracias a todos.

# **Capítulo 1**

## **Introducción**

### **1.1 Motivación**

Mi motivación personal para el proyecto final de carrera era el poder construir o realizar un portal web mediante una base de datos, que ofreciera un servicio al demandante. Pero de lo que trataría o se encargaría el portal web tendría que ser medianamente interesante. Por este motivo, primeramente mi decisión como proyecto fue la elección de éste, entre otros expuestos, porque tenía la posibilidad de construir un portal web. Ahora bien, había que mirar si el contenido de este proyecto escogido, del que jugaría este portal web fuera interesante. El tema que ofrecía este proyecto, girando alrededor de un entorno gráfico basado en web, me intereso desde el primer momento, ya que no era el simple portal web de agencia de viajes, tienda on-line o basa de datos de un hospital, por poner unos ejemplos. Se centraba en intentar construir un portal para configurar un soft-core, principalmente el soft-core de OpenRISC. Con la motivación extra de que, dado que no existe nada en el mercado que realice esta tarea o funcionalidad, tampoco en Opencores, puede llegar a ser como una especie de primer prototipo. Y por esto sería interesante su realización y dado que como es de especificación abierta, podría ayudar a la comunidad en este primer paso.

Por eso, me pareció bastante interesante entrar en las entrañas de este tema, dado que se adentra por una parte en el tema de base de datos y web, que es lo que yo quería, y por otro lado adentra en el tema hardware y así poder asimilar bastantes conocimientos nuevos al respecto.

Todo esto llevaba a utilizar herramientas que yo deseaba poner en práctica, según mis conocimientos obtenidos durante estos años de carrera, para la realización del proyecto final de carrera, más las añadidas por la otra parte, dando un proyecto robusto y completo.

## 1.2 Objetivos del proyecto

El objetivo principal del proyecto es poder crear un entorno gráfico para generar SoCs basados en el procesador Soft-Core OpenRISC.

El funcionamiento principal del entorno es poder agregar componentes a tu SoC, de manera dinámica, que el propio entorno te cree de forma automática todo el sistema sin la necesidad de que el programador tenga que ir línea a línea para poder conectar/insertar los módulos al sistema.

El entorno web permitirá mostrar todos los componentes disponibles en sus librerías, unirlos al bus del sistema y combinarlos alrededor del procesador softcore OpenRISC. Las funciones principales que se podrán realizar son:

- Añadir controladores (UART, RAM, etc) y memorias On-Chip al bus del sistema.

- Visualizar el mapa de memoria de forma dinámica.

- Visualizar la librería de componentes disponibles.

- Agregar nuevos componentes a la librería de componentes.

- Generar el sistema confeccionado con el entorno web.

Al tratarse de OpenRISC<sup>1</sup>, estamos hablando de código abierto, donde el código fuente está en public domain y distribuido bajo una licencia LGPL (*Lesser General Public License*) que permite que este Soft-Core pueda ser manipulado por mucha gente. Por eso este proyecto pretende realizar un trabajo que pueda ser de ayuda para esta comunidad.

---

<sup>1</sup> *OpenRISC es un diseño de CPU RISC de especificación libre, realizado por OpenCores y publicado bajo la licencia GPL.*

## **1.3 Organización de la Memoria**

El contenido de esta memoria se divide en 5 puntos, además de la bibliografía y anexos.

El primer capítulo sirve para introducir el tema y poder situar el contexto con el que se va trabajar, con el propósito de situar al lector.

El segundo capítulo trata de informar sobre el método de trabajo y el entorno donde se moverá el proyecto. Se introducen los conceptos y tecnologías básicas como: FPGA's, SoCs e IPs y soft-cores de 32 bits (LEON, MICROBLAZE, NIOS II). Se muestra la variedad de soft-cores que existen en la realidad, para que el lector se familiarice con el tema a explicar, antes de entrar en el tema principal en el que se basa este proyecto. Dicho tema se centra mayormente en el funcionamiento y las características del soft-core de 32 bits, OpenRISC, donde se profundizará en su entorno, su arquitectura, operaciones, registros y bus Wishbone, que es el bus que utiliza este diseño. Al finalizar este capítulo se explicará en detalle el entorno de desarrollo web del proyecto.

En el tercer capítulo entraremos en la parte práctica del proyecto. Diseño del entorno gráfico web, especificación y análisis de requisitos, diseño de los módulos del sistema, base de datos y las herramientas con las que se ha llevado a cabo este entorno.

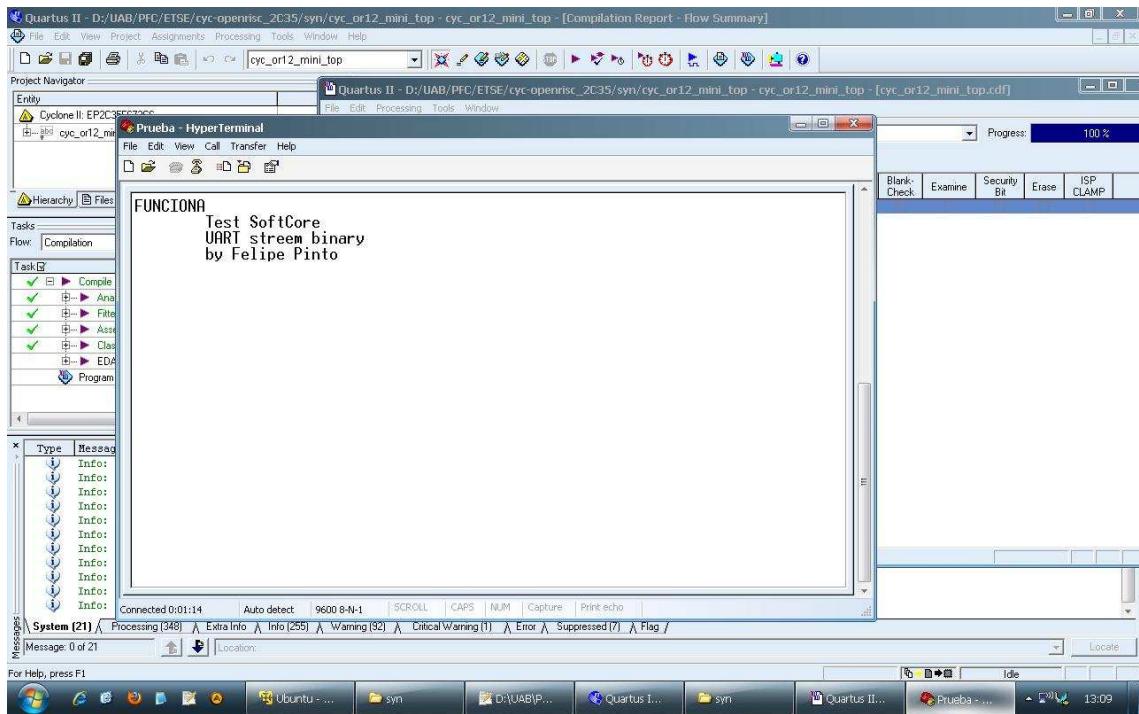

En el cuarto capítulo se explicarán los diferentes tests que se han podido realizar durante el desarrollo del proyecto y se analizarán los resultados obtenidos, como también la validación del sistema. Finalmente se analizarán también los recursos de la aplicación en su totalidad.

En quinto y último capítulo se explicarán las conclusiones que se han obtenido al terminar este proyecto, junto con la posible evolución futura del sistema realizado y finalmente la experiencia personal y profesional.

# Capítulo 2

## Metodología de trabajo i entorno

Este capítulo intentará introducirnos en el mundo de las plataformas reconfigurables.

### 2.1 Estado del Arte

Este proyecto se desarrolla alrededor de los procesadores soft-cores de 32 bits, y especialmente alrededor del OpenRISC. Antes de entrar en materia sobre esta CPU RISC introduciremos los conceptos más importantes relacionados con las plataformas reconfigurables como son: los sistemas empotrados o embedded systems, FPGA's, los SoC, Ip's y procesadores soft-cores 32 bits.

Primero empezaremos a hablar de los *embedded systems* o *sistemas empotrados*. Un sistema empotrado es un sistema de computación diseñado para realizar una o algunas pocas funciones dedicadas y que con frecuencia se realizan en tiempo real. Estos sistemas tienen una función específica y no son programables por el usuario. Los usuarios solamente pueden interaccionar a través de una interfaz específica a tal efecto. El hardware de este sistema solamente contiene la arquitectura de procesamiento y la entrada salida necesaria por llevar a cabo la tarea mandada. Este concepto de sistema empotrado es diferente del PC tradicional, entendido como ordenador de propósito general programable.

Las características de los sistemas empotrados son:

- Estos sistemas emplearán una combinación de recursos hardware y software para realizar una función específica.

- Estos sistemas realizan una única función o un conjunto muy limitado de funciones (no suelen ser de propósito general)

- La potencia, el coste y la realizabilidad suelen ser los principales factores de coste. consumos energéticos limitados, sistemas compactos, eficiente en prestaciones, etc.

- El diseño de procesadores de aplicación específica suelen ser un componente significativo de estos sistemas.

Hoy en día, los sistemas empotrados los podemos encontrar en cualquier lugar de nuestra vida, controlando algunas funcionalidades que hace unos cuantos años eran impensables de realizar por una máquina. Además, los sistemas empotrados cada vez

son más complejos debido al gran número de tareas diferentes, que deben realizar. Estos sistemas son utilizados para el control de buena parte de aplicaciones, en los dispositivos electrónicos de consumo (videoconsolas, reproductores de audio/vídeo), en la automoción (control de airbag, climatizador..), en la industria (control de procesos, robótica.), en las comunicaciones (teléfonos móviles, modem...), etc.

### 2.1.1 FPGAs

El diseño digital ha evolucionado durante todos estos años debido a los avances en las tecnologías de fabricación de circuitos integrados<sup>2</sup>. Hasta la aparición en los años '80 de los primeros dispositivos programables, las opciones viables para diseñar sistemas digitales eran el uso de circuitos integrados estándar de baja o media escala de integración, o el diseño de circuitos integrados a medida conocidos como ASICs (*Application Specific Integrated Circuits*)[1]. Un ASICs es un circuito integrado hecho a la medida para un uso en particular, en vez de ser concebido para propósitos de uso general. Pero estas dos opciones tenían problemas de flexibilidad a la hora de implementarlos por eso una de las alternativas a estos problemas fue la aparición de dispositivos lógicos programables, permitiendo gran flexibilidad a cambios de diseño futuros. Estos dispositivos son llamados FPGAs.

#### Estructura

Una **FPGA** (*Field Programmable Gate Array*) es un dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionalidad se puede programar. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una puerta lógica o un sistema combinacional hasta complejos sistemas en un chip, SoPC, (*System on Programmable Chip*), sistemas embebidos, aplicaciones de procesamiento digital de señales, etc.

Parte de la información de a continuación está extraída de [2]:

Las FPGA son la evolución tecnológica de los PLA's (*Programmable Logic Array*) que fueron desarrollados en los años 70. Los PLA's están constituidos por 2 planos de puertas lógicas, una OR y una AND. Éstos están separados entre sí por una pequeña zona divisoria que es la parte de conexionado, y a la vez tienen por el otro extremo una conexión a dos zonas externas donde se realiza la E/S. El usuario puede realizar cualquier función booleana con puertas AND y OR haciendo el conexionado adecuado.

Los PLA's mayoritariamente utilizan la tecnología de programación OTP (*One Time*

---

<sup>2</sup> Un **circuito integrado (CI)**, es una pastilla pequeña de material semiconductor, de algunos milímetros cuadrados de área, sobre la que se fabrican circuitos electrónicos generalmente mediante fotolitografía y que está protegida dentro de un encapsulado de plástico o cerámica.

*Programable*), a pesar de que también existen con EPROM (Erasable Programmable Read-Only) y EEPROM (*Electrically-erasable programmable read-only memory*).

Estos dispositivos todo y ser muy versátiles no disponían ni de flip-flops ni de memoria, elementos que en cambio si incorporan las FPGA.

Las FPGA están formadas por tres elementos:

- Bloques lógicos (CLB's).

- Bloques de entrada / salida (IOB).

- Interconexiones

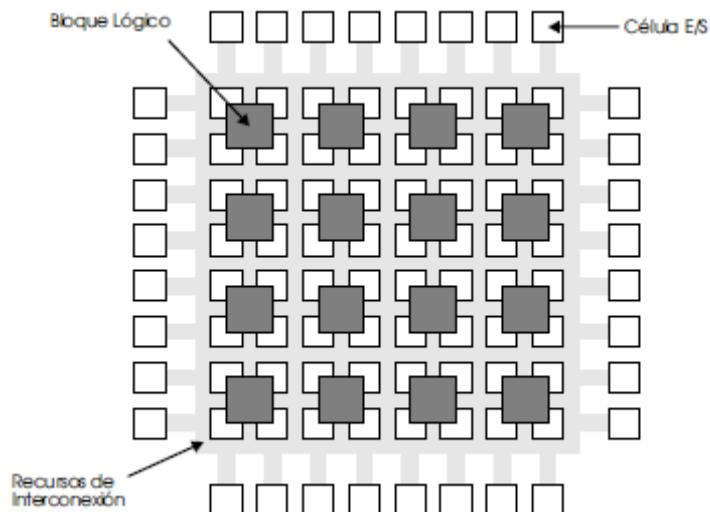

En la siguiente figura podemos observar su distribución:

Figura 2.1 Estructura interna de una FPGA.

Los **CLB's**, también denominados LE (Logic Elements) son los bloques principales de una FPGA, y están formados de puertas lógicas, flip-flops y memoria.

Cuando configuramos la FPGA estamos definiendo la funcionalidad de cada uno de los CLB's que intervendrán en el funcionamiento, puesto que es posible que no sea necesario utilizarlos todos, y el conexiónado entre CLB – CLB y el CLB – E/S.

## Clasificación

Podemos clasificar las FPGA's de muchas maneras, por ejemplo:

- Capacidad de memoria

- Pins E/S

- Velocidad

- Tecnología de configuración

### **Tecnologías de memoria de programación**

Las tecnologías de la memoria de programación de las FPGAs más comúnmente halladas son:

- **SRAM (RAM estática):** En éstas, el contenido se almacena mediante un proceso de configuración en el momento de encendido del circuito que contiene al FPGA.

- **Antifuse (antifusible):** un FPGA que utiliza este tipo de tecnología sólo puede ser programada una vez OTP (*One Time Programmed*).

- **Flash:** El avance experimentado en los últimos años en el diseño y prestaciones de las celdas de memoria flash ha permitido su incorporación a los dispositivos programables.

### **Implementación**

Para implementar un diseño en un FPGA se utilizan lenguajes de descripción de Hardware HDL (*Hardware Description Languages*)[3], como por ejemplo, VHDL (Very Hard Description Language) fue desarrollado como un lenguaje para el modelado de sistemas digitales. Proporciona una sintaxis amplia y flexible que permite el modelado estructural, en flujo de datos y de comportamiento de hardware.

VHDL es un estándar de la IEEE, favoreció su adopción en la industria lo que se ve reflejado en las constantes mejoras en las herramientas. Debido a su estandarización, un código en VHDL puede ser portado a diferentes herramientas y también, puede ser reutilizado en diferentes diseños.

### **Características**

Las características de las FPGA son su enorme flexibilidad, capacidad y volumen de procesamiento, y alta velocidad de reprogramación entre otros. Esto los convierte en dispositivos idóneos para:

- Prototipado rápido de sistemas digitales.

- Procesamiento de señal digital, por ejemplo de vídeo.

- Simulación y depuración en el diseño de ASICs.

Las FPGAs aparecen en el mercado en 1984, con una idea central: permitir realizar un circuito integrado a medida, sin los riesgos económicos asociados a las otras opciones tecnológicas. Hoy las FPGAs están presentes en campos tan diversos como la automoción, la electrónica de consumo, o la investigación espacial. La tecnología

FPGA tiene una aplicación horizontal en todas las industrias que requieren computación a alta velocidad. Algunos ejemplos de su uso podrían ser: arcos de seguridad de bancos, control industrial, equipos de transmisión de TV, Internet, electrónica espacial, seguridad electrónica, equipos de medicina y radiología, comunicaciones por fibra óptica. etc.

Fabricantes de FPGA tenemos por ejemplo: Actel, Altera, Atmel, Xilinx, Motorola, etc.

## 2.1.2 SoCs e IPs

### SoCs

Un SoC (*System-on-Chip*) [4] se basa en la idea de integrar todos los componentes de computación u otros sistemas electrónicos, en un solo chip.

Las características de los SoC son:

- Dimensión reducida: más componentes en el mismo dado de silicio.

- Mejores rendimientos: las comunicaciones entre los componentes del mismo dado de silicio son más rápidas que las comunicaciones entre elementos de diferentes chips.

- Reducción del consumo: puesto que se reduce la utilización de los pads E/S y la longitud de las líneas de transmisión. Los pads son unos de los componentes que consume mucha energía.

- Reducción de los costes: más pads E/S incrementan el coste del chip al igual que tener un PCB más complejo.

Normalmente, un SoC básico está compuesto por un (o varios) procesadores, bloques de memoria, un bus central y diferentes controladores E/S colgados de este bus. Hoy en día, los SoC son cada vez más complejos e integran diferentes tipos de procesadores y controladores en un mismo chip.

La mayoría de SoC se desarrollan a partir de bloques prediseñados, como son los IP Cores (bloques prediseñados de propiedad intelectual), junto con el software de los drivers que controlan su operación. Los bloques hardware se conectan mediante herramientas EDA (*Electronic Design Automation*), mientras que los módulos software son integrados usando un entorno de desarrollo de software.

Dentro de los grupos de los SoC, existe un subgrupo denominado *System on Programmable Chip*. Este grupo tiene los mismos componentes que un SoC, pero incorpora una parte de lógica programable para poder implementar componentes a medida o específico, para así, poder aumentar el rendimiento de nuestro sistema.

## IPs

Hasta ahora para llevar a cabo el diseño de hardware se estaban realizando mediante capturas de esquemáticos sobre elementos importados de las librerías de la tecnología de fabricación con la que vamos a fabricar nuestro ASIC. Este método, muy ligado a cada proyecto en concreto, compuerta muy poca reusabilidad de módulos entre proyectos. Pero con la aparición de los lenguajes HDL, comentados anteriormente, han permitido realizar diseños de una manera más ágil, llevándonos a obtener una portabilidad donde se pueden rehusar módulos ya desarrollados y testados.

Este diseño basado en la reutilización de módulos permite ensamblar sistemas complejos a través del uso de pequeños componentes. Estos módulos reutilizables se denominan IPs (*Intellectual Property*), y permiten la optimización de los recursos debido al reducido tiempo y coste de desarrollo.

Dentro de una FPGA o ASIC se puede incluir la funcionalidad de varios circuitos integrados. Esta funcionalidad puede ser desarrollada por el mismo equipo de trabajo o adquirida a través de un tercero. Debido a que estas funcionalidades son como componentes electrónicos, pero sin su parte física, se los suele llamar componentes virtuales. Por tanto se podrían denominar como bloques prediseñados y testados, para ser incorporados en cualquier proyecto, y pensados para ser reutilizados.

Los IP cores pueden ser muy complejos, como el IP de un microprocesador, o muy simples, como en el caso de un IP core para controlar un GPIO. Alrededor de los IP cores , existe todo un mercado dónde podemos encontrar empresas dedicadas al diseño y soporte de IP, herramientas específicas, y también comunidades de código libre. Los IP cores de estas comunidades de código libre, normalmente están sujetas a licencias de código libre (GPL, etc).

Podemos encontrar 3 tipos de IPs [2]:

- Hard\_ IP: la compañía nos da el layout, de una tecnología en particular, para generar la máscara del componente y la documentación asociada (funcionalidad, interfaz, etc). Estos tipos de IP cores no nos permiten cambiar su diseño, pero son componentes muy testados y optimizados por esta tecnología.

- Soft\_ IP: la compañía nos da el código HDL que puede ser sintetizado por las herramientas habituales de síntesis. Esta alternativa es más flexible que la anterior, puesto que a través de su código fuente, podemos modificar el IP. Muchos de este IP están escritos en VHDL<sup>3</sup> o Verilog<sup>4</sup>.

---

<sup>3</sup> VHDL es un lenguaje definido por el IEEE (*Institute of Electrical and Electronics Engineers*) (ANSI/IEEE 1076-1993) usado por ingenieros para describir circuitos digitales.

<sup>4</sup> Verilog es un lenguaje de descripción de hardware (HDL, del Inglés Hardware Description Language) usado para modelar sistemas electrónicos. El lenguaje, algunas veces llamado Verilog HDL, soporta el

- Firm\_IP: la compañía nos da una descripción detallada del componente (netlist) y sus restricciones (retardos máximos, etc). Esta alternativa está en el centro de las dos anteriores.

### 2.1.3 Procesadores Softcores de 32 bits

En los embedded systems, el elemento más importante es el procesador, puesto que él es quien controla la actividad de todo los componentes del sistema. Por esta razón, se define el procesador como componente principal de toda plataforma arquitectural.

Un procesador softcore es una descripción, en lenguaje de alto nivel hardware (HDL), de un modelo específico de procesador, que es fácilmente personalizable por una aplicación específica y sintetizable en un ASIC o FPGA. Estos procesadores son fácilmente integrables en un SoC.

Antes de mostrar algunos ejemplos de softcores, explicaré la arquitectura computacional RISC (*Reduced Instruction Set Computer*).

RISC es un tipo de microprocesador con las siguientes características fundamentales:

1. Instrucciones de tamaño fijo y presentadas en un reducido número de formatos.

2. Sólo las instrucciones de carga y almacenamiento acceden a la memoria por datos.

Además estos procesadores suelen disponer de muchos registros de propósito general.

El objetivo de diseñar máquinas con esta arquitectura es posibilitar la segmentación y el paralelismo en la ejecución de instrucciones y reducir los accesos a memoria. Las máquinas RISC protagonizan la tendencia actual de construcción de microprocesadores.

RISC es una filosofía de diseño de CPU para computadora que está a favor de conjuntos de instrucciones pequeñas y simples que toman menor tiempo para ejecutarse. El tipo de procesador más comúnmente utilizado en equipos de escritorio, el x86, está basado en CISC en lugar de RISC, aunque las versiones más nuevas

---

diseño, prueba e implementación de circuitos analógicos, digitales y de señal mixta a diferentes niveles de abstracción.

traducen instrucciones basadas en CISC x86 a instrucciones más simples basadas en RISC para uso interno antes de su ejecución.

La idea fue inspirada por el hecho de que muchas de las características que eran incluidas en los diseños tradicionales de CPU para aumentar la velocidad estaban siendo ignoradas por los programas que eran ejecutados en ellas. Además, la velocidad del procesador en relación con la memoria de la computadora que accedía era cada vez más alta. Esto conllevó la aparición de numerosas técnicas para reducir el procesamiento dentro del CPU, así como de reducir el número total de accesos a memoria.

Las características que generalmente son encontradas en los diseños RISC son:

- Codificación uniforme de instrucciones (ejemplo: el código de operación se encuentra siempre en la misma posición en cada instrucción, la cual es siempre una palabra), lo que permite una decodificación más rápida.

- Un conjunto de registros homogéneo, permitiendo que cualquier registro sea utilizado en cualquier contexto y así simplificar el diseño del compilador (aunque existen muchas formas de separar los ficheros de registro de entero y coma flotante).

- Modos de direccionamiento simple con modos más complejos reemplazados por secuencias de instrucciones aritméticas simples.

- Los tipos de datos soportados en el hardware (por ejemplo, algunas máquinas CISC tienen instrucciones para tratar con tipos byte, cadena) no se encuentran en una máquina RISC.

Los diseños RISC también prefieren utilizar como característica un modelo de memoria Harvard, donde los conjuntos de instrucciones y los conjuntos de datos están conceptualmente separados; esto significa que el modificar las direcciones donde el código se encuentra pudiera no tener efecto alguno en las instrucciones ejecutadas por el procesador (porque la CPU tiene separada la instrucción y el caché de datos, al menos mientras una instrucción especial de sincronización es utilizada). Por otra parte, esto permite que ambos cachés sean accedidos separadamente, lo que puede en algunas ocasiones mejorar el rendimiento.

Ejemplos de diseño RISC podrían ser:

El ARM (*Advanced RISC Machines*): Se encuentra en dispositivos PALM, Nintendo DS, Game Boy Advance y en múltiples PDAs, teléfonos móviles y reproductores multimedia (como el iPod).

Actualmente se utiliza en muchos sistemas empotrados en automóviles, routers, etc, así como en muchas consolas de videojuegos, como la Playstation 3, Xbox 360 y Nintendo Wii.

Con esta breve introducción a la arquitectura RISC, comentaré cuatro procesadores softcore:

Las características de los procesadores que se explicarán a continuación son extraídas de [4].

## Leon 3

AeroFlex Gaisler, que en los inicios fue un spin-off de la Agencia Espacial Europea (ESA) denominada Gaisler Research, es una compañía que provee IP cores y desarrolla herramientas para procesadores empotrados basados en la arquitectura SPARC. Uno de sus productos es la familia de procesadores sintetizables LEON. Jiri Gaisler, buscaba desarrollar un procesador resistente a radiaciones, modular, fácilmente portable, con interfaces estándar y que ejecutara hasta 100 MIPS. Además, el nuevo diseño, escrito en VHDL, se licenció bajo GPL, lo que permitiría integrarlo en un System-on-Chip (SoC).

Al primer prototipo se le llamó LEON-1. Una vez éste fue verificado se comenzó el desarrollo de un procesador más completo, con unidad de coma flotante y nuevos interfaces, estas fueron las versiones LEON-2 y LEON-3. Finalmente, la ESA encargó a Gaisler Research (hoy integrada en el grupo AEROFLEX) el desarrollo de un LEON-4.

El LEON 3 es un procesador de 32 bit escrito en VHDL y basado con una arquitectura SPARC V8. Este es muy parametrizable a través del uso de VHDL genéricos y una sencilla interfaz gráfica.

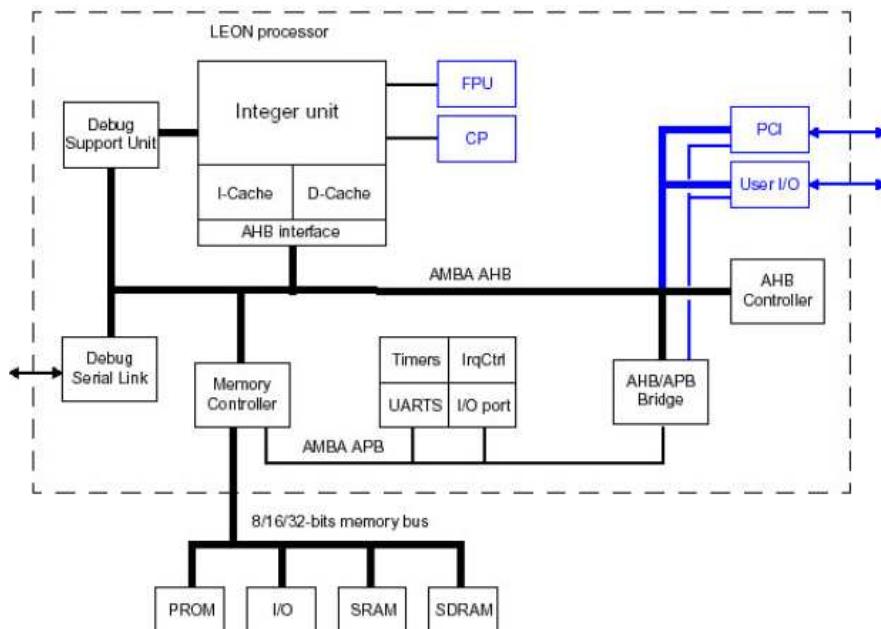

Figura 2.2. Procesador Leon 3.

- Incorpora las extensiones de SPARC v8e.

- Utiliza un pipeline de siete etapas: Fetch, Decode, Register Access, Execute, Memory, Exception, Write.

- Incorpora, de forma opcional, una unidad de coma flotante de alto rendimiento y compatible con el estándar IEE-754.

- Soporte para Multiprocesador.

- Powerdown mode.

## MicroBlaze

El MicroBlaze es un procesador RISC de 32 bits optimizado para ser implementado solamente en las FPGA de Xilinx, las Spartan y Virtex . Aún siendo un *soft-processor*, el usuario no tiene acceso a los detalles VHDL del circuito. Sólo puede analizarse a partir de la documentación del fabricante y de los resultados experimentales. Aún así, es una herramienta muy potente para desarrollar proyectos relacionados con arquitecturas paralelas, codiseño y control; y en general, en toda investigación sobre software, puesto que permite una comparación inmediata con otras arquitecturas y metodologías de desarrollo.

El conjunto de características que incluye este procesador está formado por 32 registros de propósito general, palabra de instrucción de 32 bits con 3 operandos y 2 modos de direccionamiento, pipeline y direcciones de 32 bits. Para tal de añadir más características a esta arquitectura predefinida, el MicroBlaze nos permite activar un gran número de funcionalidades.

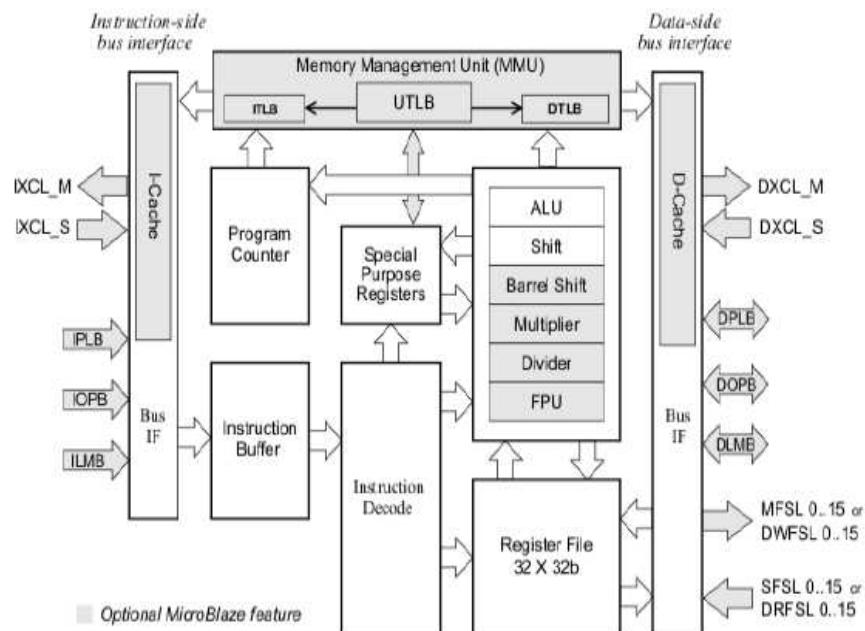

Figura 2.3. Diagrama de bloques del procesador MicroBlaze.

Las principales funcionalidades parametrizables son:

- Dimensiones de las caches de instrucciones y datos.

- Multiplicadores y divisores por hardware.

- Barrel shifter por hardware.

- Memory Management Unit (MMU).

- Floating Point Unit (FPU).

- Fast Simplex Link (FSL) interfaces (0/15).

## NIOS II

El procesador NIOS II es similar a los otros microcontroladores softcores. Es un procesador RISC de 32 bits diseñado especialmente por las familias de FPGA de Altera. Las características que podemos destacar de este procesador son: un ISA de 32bits, una palabra de instrucción de 3 operandos, datapath independiente entre instrucciones y datos, 32 registros de propósito general y 256 CI para mejorar el rendimiento de esta arquitectura.

Las herramientas de configuración del NIOS II, nos permiten seleccionar 3 cores diferentes para este procesador:

- NIOS II/e “economy”: El core NIOS II/e está diseñado para ser el más pequeño posible en cuanto al consumo de área. Este core no dispone de caches, pipeline y otros componentes hardware.

- NIOS II/s “standard” : El core NIOS II/s está diseñado para tener un buen compromiso entre el rendimiento y área utilizada. Este core tiene 5 etapas de pipeline, predictor de saltos estático y posibilidad de cache de instrucciones y datos.

- NIOS II/s “fast”: El core NIOS II/f está diseñado para tener unas altas prestaciones de computación. Como resultado, este core permite ser configurado a través de un amplio abanico de parámetros para tal de mejorar su rendimiento. Básicamente este core está compuesto de 6 etapas de pipeline, un predictor de saltos dinámico y la posibilidad de utilizar caches de instrucciones y datos.

Para mejorar las prestaciones del NIOS II/f, podemos seleccionar nuevos elementos como multiplicación y división por hardware, o mejorar la jerarquía de memoria aumentando o disminuyendo la medida de las caches y/o seleccionando las Tightly Coupled Memory (TCM).

Las tres versiones del core, permiten mejorar su set de instrucciones a partir de incorporar hasta 256 *custom instructions*. Éstas pueden aportar un aumento significativo del rendimiento del procesador.

Los cores no incluyen ningún periférico para comunicarnos con el mundo exterior. Puesto que estos cores están pensados para ser conectados del bus Avalon, como un componente más del SoC. Por lo tanto, los cores solamente contienen los circuitos necesarios para implementar una arquitectura NIOS II.

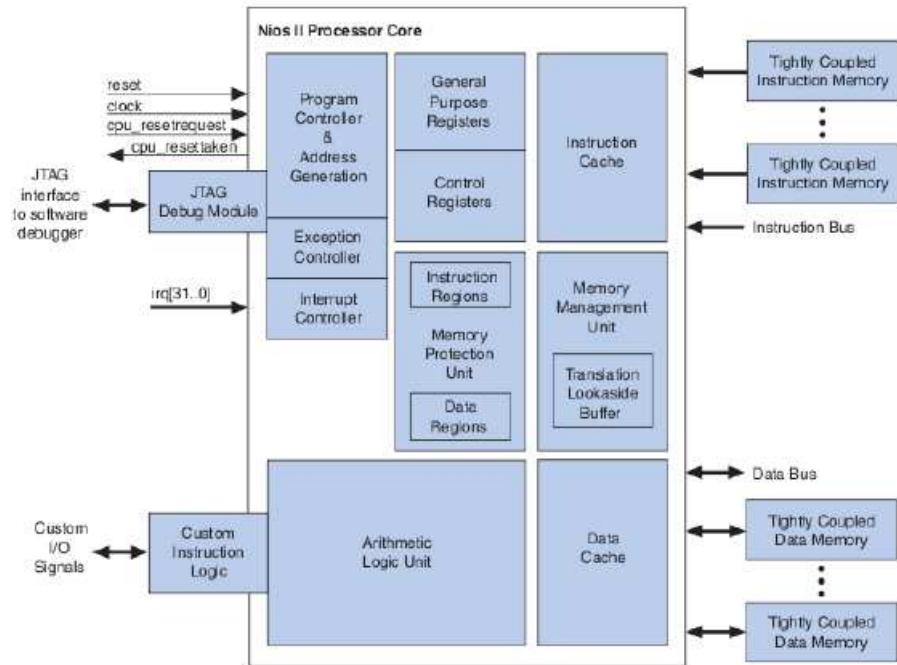

Figura 2.4. Diagrama de bloques del procesador NIOS II.

Las unidades funcionales más destacadas de la arquitectura NIOS II son:

- Interface to custom instruction logic (CI).

- Memory management unit (MMU).

- Memory protection unit (MPU).

- Instruction and data cache memories.

- Tightlycoupled memory interfaces for instructions and data.

- JTAG debug module.

El NIOS II se distribuye como un componente más, dentro del Mega Wizard de Altera SOPC Builde. Como ya hemos comentado, nosotros podemos añadir el NIOS II como un componente más del bus Avalon, y allí sí, podemos incorporar los periféricos necesarios por construir nuestros SoC.

## 2.2 Entorno de desarrollo OpenRISC

### 2.2.1 Entorno Hardware

Seguidamente explicaré el softcore que trataremos en este proyecto.

El procesador OpenRisc utilizado para este proyecto es un diseño de CPU RISC de especificación abierta, realizado por OpenCores<sup>5</sup> y publicado bajo la licencia LGPL. El diseño está implementado en el lenguaje de descripción de hardware Verilog y contempla el conjunto de instrucciones ORBIS32 (Instrucciones básicas de 32 bits).

Específicamente el CORE utilizado es el *OpenRisc 1200*:

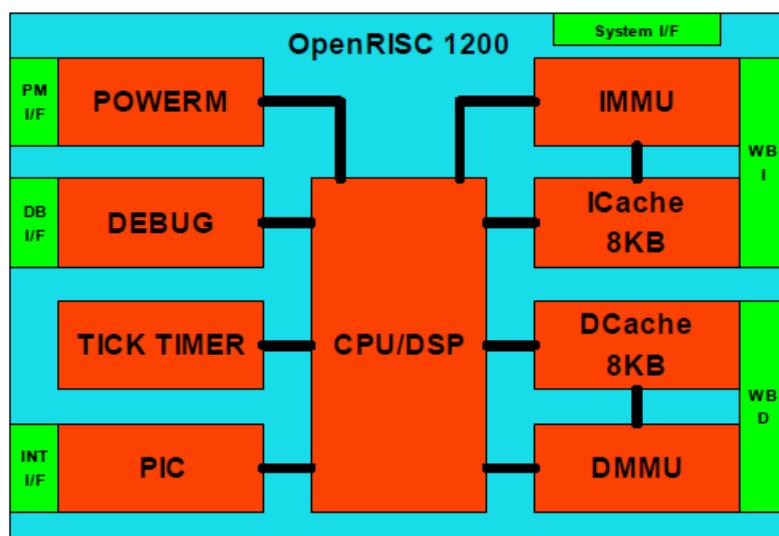

Figura 2.5. Arquitectura del Core OpenRisc 1200.

Este core está completamente realizado en Verilog y contempla el conjunto de instrucciones ORBIS32. El OpenRisc 1200 es un procesador segmentado, con 32 registros de propósito general, con un pipeline de 5 etapas, bus del sistema WishBone, del que luego entraremos en detalle, caches de instrucciones y datos separados, y basadas con la arquitectura Hardvard. Tiene soporte para gestión de memoria virtual e instrucciones básicas para el procesamiento de señales digitales (DSP).

<sup>5</sup> OpenCores es una comunidad de gente que está interesada en el desarrollo de código abierto de hardware digital a través de automatización de diseño electrónico, con un espíritu similar al movimiento del software libre ([www.opencores.org](http://www.opencores.org)).

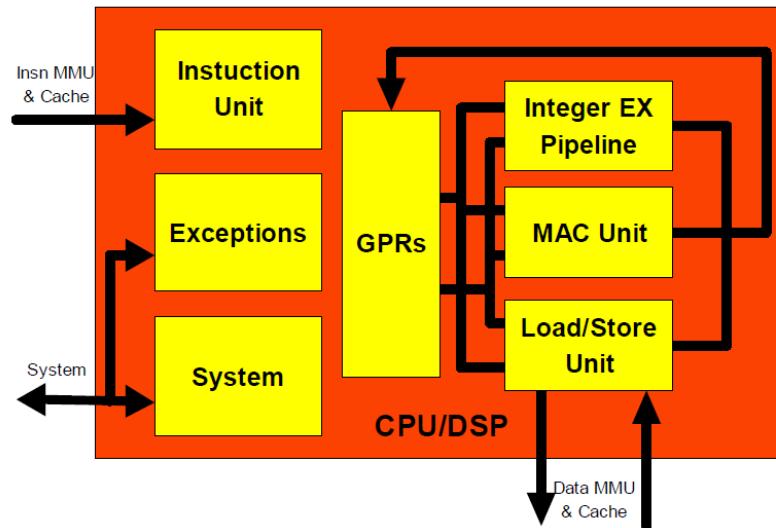

CPU / DSP es una parte central del procesador RISC OR1200. OR1200 CPU / DSP implementa sólo una parte de 32-bit de la arquitectura OpenRISC 1000. 64 Bit parte de la arquitectura, así como de punto flotante y operaciones de vectores no se implementan en OR1200.

Figura 2.6. Diagrama de Bloque CPU/DSP OpenRisc 1200.

Está compuesto por varios bloques cuyas características principales listamos a continuación:

- Unidad de Gestión de memoria (*Memory Management Unit (MMU)*).

- Arquitectura Harvard de 32 bits.

- Cachés separadas de datos e instrucciones.

- Hasta 8 Custom Instructions (CI).

- Gestión de energía (*Sophisticated Power Management Unit (SPMU)*).

- Reducción de la potencia de 100x a 2x.

- Frecuencia de reloj controlada por software en modos slow e idle.

- Interrupción wake-up en los modos doze y sleep.

- Unidad de depuración avanzada.

- Depuración no intrusiva.

- Acceso y control a la unidad de depuración desde el RISC y el interfaz externo.

- Medición precisa del tiempo.

- Multiplicador Hardware.

- Controlador programable de interrupciones.

- Doble interfaz Wishbone para datos e instrucciones.

- On-chip RAM.

- Controlador uart.

- Controlador Ethernet.

- Variedad de periféricos listos para usar con el OpenRisc 1200.

- Nuevas instrucciones definidas por el usuario.

Como hemos mencionado, una de las características más interesantes del OpenRisc 1200 es su capacidad de adaptación y personalización para acomodarse a las diferentes necesidades y tecnologías de implementación que encontramos en el mercado.

Para la implementación podemos optar tanto por FPGAs como por ASICS. De serie, el OpenRisc 1200 está preparado para ser sintetizado por las herramientas Synplify, Xilinx XST y Altera QIS. De cualquier modo, no resulta difícil adaptarlo a cualquiera otra herramienta de síntesis del mercado.

Dentro del diseño de un SoC, juega un papel fundamental el modo en que vamos a interconectar los distintos componentes. Normalmente se utilizan buses estándares llamados on-chip buses cuya elección vendrá determinada por la cpu y los periféricos, ya que han de ser compatibles. Dentro de una arquitectura de interconexión, podemos diferenciar dos conceptos: la topología y el protocolo lógico. La topología se refiere a la forma, física o lógica, de los caminos de datos entre los distintos componentes. Por otro lado, el protocolo lógico da las reglas de comunicación para que el sistema funcione a través del bus físico. Cada arquitectura de interconexión estándar, suele definir uno o varios protocolos lógicos interoperables a través de puentes y diferentes posibilidades en cuanto a topología se refiere.

Las arquitecturas más utilizadas en el mercado actualmente son: ARM AMBA, IBM CoreConnect, Altera Avalon y Wishbone.

En nuestro caso, OpenCores utiliza el bus Wishbone, fundamentalmente porque es el único que está libre de patentes, royalties y copyright.

## **Bus Wishbone**

Wishbone intenta ser un bus lógico, no especificando información eléctrica o de topología. Por eso es útil para comunicar diferentes componentes diseñados en lenguajes de descripción de hardware, ya sea Verilog, VHDL u otros.

En el diseño de Wishbone [6] se han buscado dos objetivos principalmente: simplicidad y flexibilidad. La simplicidad ha sido entendida como la capacidad de conseguir grandes tasas de datos con una complejidad de hardware mínima.

A diferencia de otros estándares que definen una jerarquía de varios protocolos, en Wishbone sólo existe uno, que es de alta velocidad con capacidad de adaptarse a dispositivos lentos. De este modo, en caso de necesitar conectar dispositivos de alta y baja velocidad es recomendable utilizar dos interfaces Wishbone, una para dispositivos de alta velocidad y otra para dispositivos de baja velocidad en lugar de complicar la gestión del bus.

Desde el punto de vista de la flexibilidad, el estándar nos permite utilizar diversas topologías de bus (bus compartido, crossbar switch, punto a punto) y deja margen para configurar otros parámetros, como los anchos de los buses, el significado de las etiquetas de datos y direcciones, endianness, niveles eléctricos, etc.

La metodología de diseño de un SoC basado en Wishbone vendrá determinada fundamentalmente por el tipo de topología que utilicemos y de los parámetros de configuración que establezcamos.

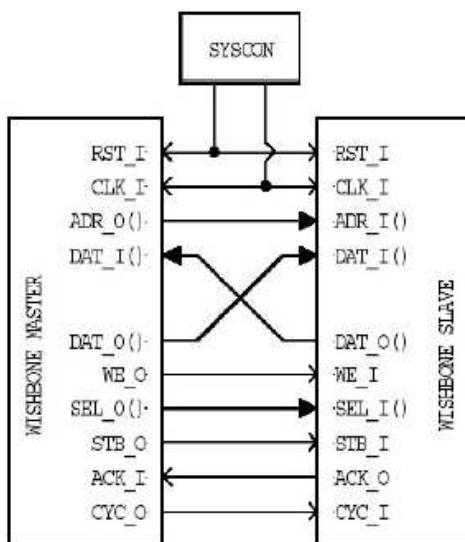

Ejemplo de interfaz e interconexiones en una arquitectura punto a punto [7]:

Figura 2.7. Interfaz e interconexiones en una arquitectura punto a punto.

Características técnicas del bus:

- Arquitectura de un bus para todas las aplicaciones.

- Arquitectura simple.

- Multi master.

- Espacio de direcciones de 64 bits.

- Bus de datos de 8 a 64 bits.

- Basado en protocolos estándares de transferencia de datos.

- Soporta varios tipos de interconexiones.

- Protocolo de handshake para regular la velocidad de transferencia de datos.

- Soporta varias terminaciones de ciclos.

- TAGs definidos por el usuario para identificar el tipo de transferencia de datos.

- Basado en arquitectura Maestro/Esclavo.

### Comunes a Master y Slave

- CLK\_I: entrada de reloj.

- RST\_I: reset del diseño.

- DAT\_I() y DAT\_O(): buses de entrada y salida de datos.

- TGD\_I() y TGD\_O()

- Opcional.

- Lleva información asociada al bus de datos.

- Validas cuando STB\_O activo.

- Ej: paridad.

### MASTER

### SLAVE

|                                                                                                                                                                                                      |                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR_O(N..n) <ul style="list-style-type: none"> <li>- N: Límite superior dado por el ancho del bus de direcciones</li> <li>- n: límite inferior dado por la granularidad del bus de datos.</li> </ul> | ADR_I(N..n) <ul style="list-style-type: none"> <li>- N: Límite superior dado por el ancho del bus de direcciones</li> <li>- n: límite inferior dado por la granularidad del bus de datos.</li> </ul> |

| - CYC_O: Indica que se está llevando a cabo un ciclo de bus válido. Se activa al comienzo del ciclo y permanece hasta el final.                                                                      | - CYC_I: Indica el comienzo de un ciclo.                                                                                                                                                             |

| WE_O: Indica si el ciclo es de lectura o escritura.                                                                                                                                                  | WE_I: Indica si la transacción es de lectura o escritura.                                                                                                                                            |

| STB_O: indica que se está llevando a cabo un ciclo valido de transferencia de datos.                                                                                                                 | STB_I: indica que se está llevando a cabo un ciclo valido de transferencia de datos.                                                                                                                 |

| ACK_I: recibe la confirmación de una transferencia                                                                                                                                                   | ACK_O: recibe la confirmación de una transferencia                                                                                                                                                   |

| ERR_I: recibe la indicación de un error en la transferencia.                                                                                                                                         | ERR_O: recibe la indicación de un error en la transferencia.                                                                                                                                         |

| RTY_I: recibe pedido de re-transmisión de datos.                                                                                                                                                     | RTY_O: recibe pedido de re-transmisión de datos.                                                                                                                                                     |

| SEL_O(): asociado con la granularidad, indica donde hay o donde espera datos validos en el bus.                                                                                                      | SEL_I(): asociado con la granularidad, indica donde hay o donde espera datos validos en el bus.                                                                                                      |

WISHBONE facilita el trabajo a los diseñadores, ya que estandariza la interfaz.

Está basado en una arquitectura de Maestro/Esclavo y se comunican a través de una interfaz usualmente denominada INTERCON.

### **Funcionamiento general:**

#### **- Reset**

El reset se produce en forma síncrona.

Todas las interfaces WISHBONE deben de inicializarse con el primer flanco de subida en el que RST\_I este activo.

#### **- Inicialización de ciclo de transacción**

Se indica que hay un ciclo válido si CYC\_O está activo. Cuando CYC\_O es 0 ninguna de las otras señales del MASTER tienen sentido.

#### **- Protocolo de Handshake**

Handshake permite adecuar la velocidad de transferencia de datos, e indicar errores y reintentos.

El handshake para la transferencia de datos es sumamente sencillo, el MASTER activa STB\_O y lo mantiene así hasta que el esclavo activa alguna de las señales ACK\_I, ERR\_I, RTY\_I. Al ocurrir esto el Maestro desactiva la señal.

Las señales de respuesta ACK\_O, ERR\_O, RTY\_O deben generarse solo si están activas CYC\_I y STB\_I.

Las interfaces del esclavo deben de ser diseñadas para que ACK\_O, ERR\_O, RTY\_O se activen y desactiven respondiendo a STB\_O.

Las señales permiten tres ciclos básicos: Read, Write y RMW.

Las señales no son bidireccionales, siempre son entradas o salidas. Esto es así debido a que muchas veces el diseño puede llegar a querer implementarse en hardware que no soporta internamente señales bidireccionales, como por ejemplo las FPGAs de Altera.

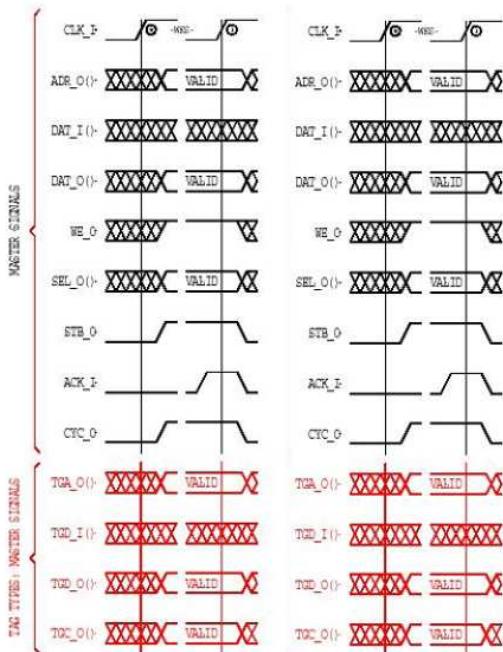

## Ciclos READ/WRITE simples

Figura 2.8. Read/Write simples bus Wishbone.

## Ciclos READ/WRITE en bloque

Durante las transferencias en bloque, la interfaz básicamente realiza transferencias simples Read/Write.

Este tipo de transferencias es útil, sobre todo en sistemas con varios Master.

### **Interconexiones de módulos:**

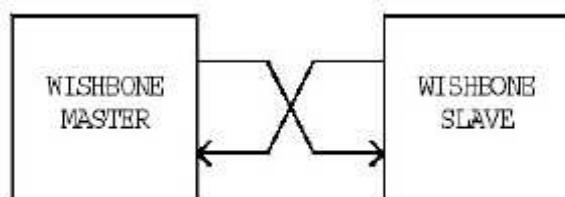

#### Conexión punto a punto:

Figura 2.9. Conexión Wishbone punto a punto.

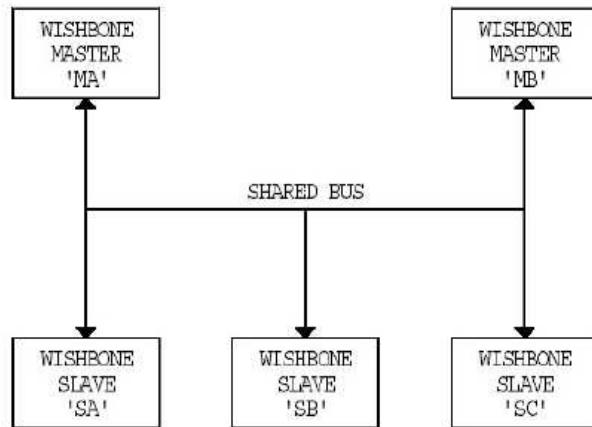

### Bus Compartido:

Todos los dispositivos están conectados sobre un mismo bus y cualquier Master puede iniciar una transacción con cualquier esclavo.

Un árbitro es el que determina cuando le toca el turno a cada uno de los Master.

Figura 2.10. Conexión Wishbone bus compartido.

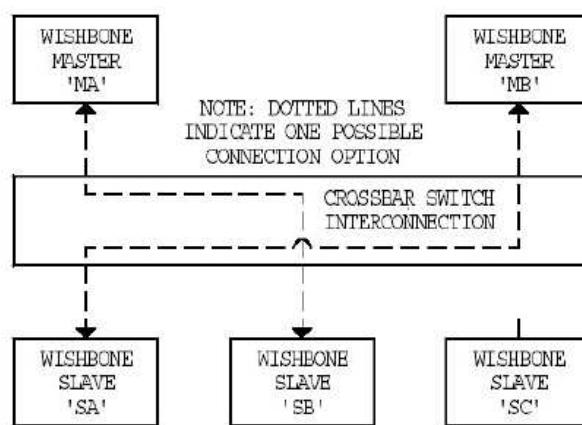

### Switch de interconexiones:

Consumo más recursos, pero permite variadas comunicaciones entre pares Maestro/Esclavo a la misma vez.

Figura 2.11. Conexión Wishbone con switch de conexiones

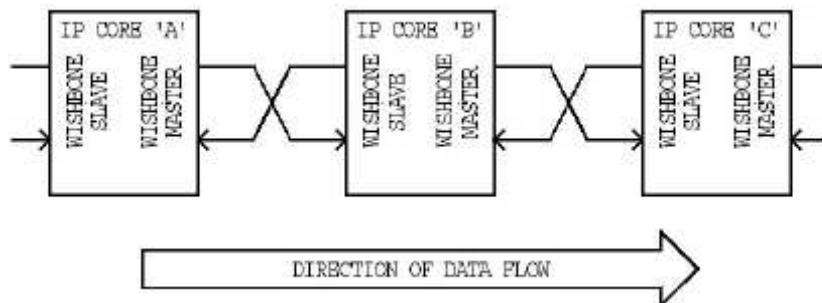

### Flujo de Datos (Pipeline)

Es una posible arquitectura para implementar diseños que procesen datos en pipeline.

Figura 2.12. Conexión Wishbone con pipeline.

## 2.2.2 Entorno Software para OpenRISC

Para compilar nuestro software disponemos del conjunto de herramientas de GNU, también llamado GNU toolchain. La GNU toolchain ha sido portada a OpenRISC para permitir el desarrollo en distintos lenguajes. Linux y µCLinux han sido también portados a este procesador.

El *GNU toolchain* es un término que agrupa a una serie de proyectos que contienen las herramientas de programación producidas por el proyecto GNU. Estos proyectos forman un sistema integrado que es usado para programar tanto aplicaciones como sistemas operativos.

El GNU toolchain es un componente vital en el desarrollo del núcleo Linux, el desarrollo del BSD y software para sistemas embebidos. Partes del toolchain de GNU también son usadas en Solaris Operating Environment y la programación de Microsoft Windows con Cygwin y MinGW/MSYS.

Este proyecto aspira a mantener un conjunto de herramientas, de fácil uso, de desarrollo para la plataforma de procesador de OpenRISC.

Las herramientas incluidas son actualmente [12]:

- GNU binutils 2.18.50 (with binutils 2.20.1 available experimentally): *una colección de herramientas binarias.*

- GNU GCC 4.2.2: colección de compilación que incluye el ANSI C compiler, C++, Java, Fortran y otros compiladores.

- GNU Make: proyecto dedicado a la automatización de la estructura y de la compilación.

- GNU GDB 6.8 (with GDB 7.1 available experimentally): depurador interactivo.

- uClibc 0.9.29.

- newlib 1.18.0: librería destinada al uso en sistemas embedidos.

- Linux 2.6.24.

- BusyBox 1.7.5.

- or1ksim 0.4.0 (or1skim 0.3.0 for precompiled tool chains).

## 2.3 Entorno de desarrollo Web

En este apartado se explicará los procedimientos y herramientas para el desarrollo de la página web.

Se ha escogido el uso de WAMP, sistema de infraestructura de internet que usa las siguientes herramientas:

- Windows, como sistema operativo;

- Apache, como servidor web;

- MySQL, como gestor de bases de datos;

- PHP (generalmente), Perl, o Python, como lenguajes de programación.

El uso de un WAMP permite servir páginas html a internet, además de poder gestionar datos en ellas, al mismo tiempo un WAMP, proporciona lenguajes de programación para desarrollar aplicaciones web.

El servidor Apache/2.2.11 fundamentalmente para gestionar un servidor web HTTP.

Lenguaje PHP/5.3.0 para poder interactuar con la Base de Datos.

MySQL como servidor de Base de Datos.

# Capítulo 3

## Diseño e Implementación

Este capítulo explicará que elementos se necesitarán para crear nuestra aplicación.

### 3.1 Arquitectura del sistema

#### Descripción General

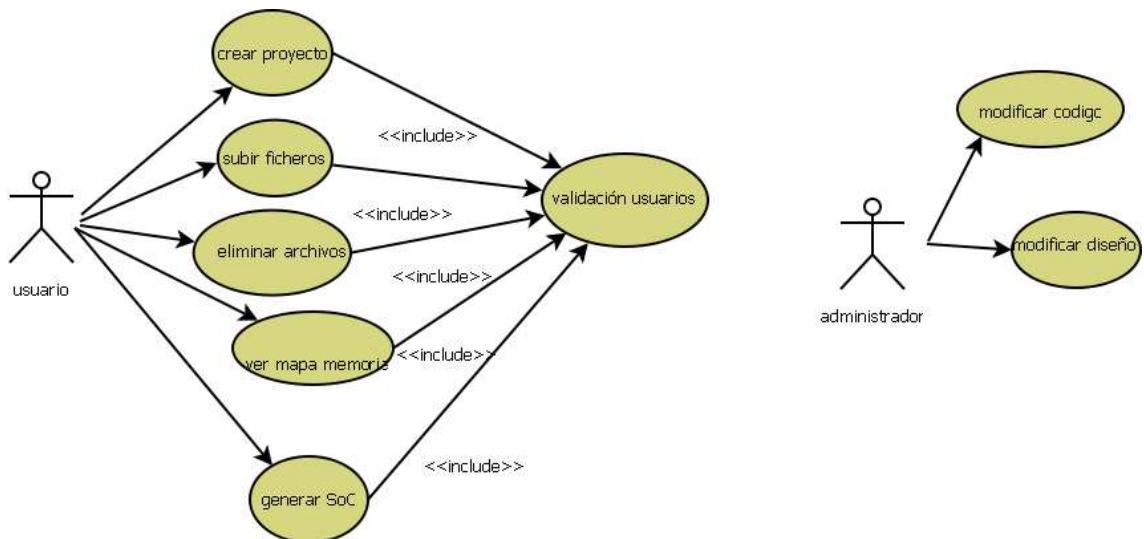

Dentro de este apartado explicaremos todo lo necesario para poder llevar a cabo esta aplicación web. Primeramente habrá que diferenciar los principales usuarios que interactuarán con la aplicación. Principalmente sólo hay dos:

- **Administrador:** será la persona encargada del buen funcionamiento de la aplicación, y sobre todo del correcto funcionamiento del código de generación de proyectos para obtener un buen resultado, sin fallos para su comprobación más tarde.

- **Usuario:** el usuario será la persona que mediante sus ficheros .v (verilog) y .vhd (VHDL) pueda generar el proyecto deseado. Con libre acceso para poder subir los ficheros que deseen, borrarlos, etc.

Seguidamente hablaremos de los requerimientos del sistema que serían:

*Requerimientos Técnicos:*

#### Servidor:

- Apache/2.2.11

- PhpMyAdmin 3.2.0.1

- MySQL 5.1.36

#### Requerimientos a nivel de página web:

- Métodos de autenticación para acceso a zonas privadas del usuario.

- Detección de subida de ficheros correctos al servidor.

### Requisitos funcionales de la aplicación web

La función principal de la aplicación es poder unir módulos insertados por el usuario o de la librería principal de la aplicación, y generar una vista principal del sistema en donde se puedan ver los elementos insertados correctamente para su comprobación y uso posterior. Por tanto se necesitará de un sistema de subida de ficheros, un repositorio de módulos para la librería principal, un entorno de unión de componentes al sistema y el visualizador del sistema.

Otra función de esta aplicación es poder ver el mapa de memoria del sistema según se vayan insertando los módulos de manera dinámica y poder ver las interrupciones.

### Diagrama de casos de uso

Figura 3.1. Diagrama de casos de uso.

## **Requisitos de la aplicación**

### **Interface:**

- **Conexión:** La aplicación es totalmente on-line y necesita un acceso permanente a la base de datos, implicando un uso del servidor las 24h.

- **Navegadores:** intentar que la aplicación pueda ser visualizada correctamente en cualquiera de los navegadores más comunes que existen a día de hoy (Internet Explorer, Firefox, Google Chrome, Opera, Safari).

- **Sistema Operativo:** La Aplicación esta realizada sobre Windows. Si el usuario usará otro S.O como por ejemplo Linux, se necesitaría adaptar mínimamente la aplicación por ejemplo en el acceso a directorios.

## **Requisitos a nivel de diseño**

- **Seguridad:** El sistema debe disponer de un sistema de autentificación de usuarios.

- **Usabilidad:** Se ha intentado crear una aplicación fácil de usar, con un aspecto sencillo.

- **Mantenimiento:** El administrador debería ser capaz de realizar ampliaciones o modificaciones de los aspectos de la aplicación sin que eso conlleve ningún problema para el correcto uso por parte de los usuarios.

## **Requisitos de Software externo**

Se necesita el uso de un servidor de base de datos y de aplicaciones. El servidor de base de datos debido a que la información debe estar accesible en cualquier momento, y el servidor de aplicaciones, en este caso Php, para poder ejecutar aplicaciones dinámicas.

## Bases de Datos

Todos los sistemas gestores que mencionaremos utilizan SQL (*Structured Query Language*), puesto que hoy en día es el lenguaje de acceso a bases de datos relacionales más usado. SQL es un lenguaje declarativo de alto nivel que permite especificar diversos tipos de operaciones sobre las bases de datos, permitiendo recuperar información de una forma efectiva y muy eficiente.

Los posibles gestores de base de datos podrían ser Oracle, MySQL, PostgreSQL o el Microsoft SQL Server. El sistema gestor de base de datos escogido para esta aplicación ha sido el MySQL, (*Structured Query Language*), uno de los lenguajes de acceso a base de datos relacionales más utilizado y además con licencia libre, y que no ha hecho falta conocer muy a fondo dado que ya era conocido.

SQL es un lenguaje declarativo de alto nivel que permite especificar diversos tipos de operaciones sobre las bases de datos, permitiendo recuperar información de una forma efectiva y muy eficiente.

## MySQL

MySQL [13] es un software de código abierto, licenciado bajo la GPL de la GNU, aunque MySQL AB distribuye una versión comercial, en lo único que se diferencia de la versión libre, es en el soporte técnico que se ofrece, y la posibilidad de integrar este gestor en un software propietario, ya que de otra manera, se vulneraría la licencia GPL.

Características principales:

- El principal objetivo de MySQL es velocidad y robustez.

- Soporta gran cantidad de tipos de datos para las columnas.

- Gran portabilidad entre sistemas, puede trabajar en distintas plataformas y sistemas operativos.

- Cada base de datos cuenta con 3 archivos: Uno de estructura, uno de datos y uno de índice y soporta hasta 32 índices por tabla.

- Aprovecha la potencia de sistemas multiproceso, gracias a su implementación multihilo.

- Flexible sistema de contraseñas (passwords) y gestión de usuarios, con un muy buen nivel de seguridad en los datos.

- El servidor soporta mensajes de error en distintas lenguas

La versión del servidor utilizada es la 5.1.36.

Para la creación de las tablas de la base de datos se ha utilizado la herramienta phpMyAdmin, que explicaremos a continuación.

## phpMyAdmin

*phpMyAdmin* [14] es una herramienta escrita en PHP, de libre distribución con la intención de manejar la administración de MySQL a través de páginas web, utilizando Internet.

La aplicación en si no es más que un conjunto de archivos escritos en PHP que podemos copiar en un directorio de nuestro servidor web, de modo que, cuando accedemos a esos archivos, nos muestran unas páginas donde podemos encontrar las bases de datos a las que tenemos acceso en nuestro servidor de bases de datos y todas sus tablas.

Actualmente puede crear y eliminar Bases de Datos, crear, eliminar y alterar tablas, borrar, editar y añadir campos, ejecutar cualquier sentencia SQL, administrar claves en campos, administrar privilegios, exportar datos en varios formatos y está disponible en 50 idiomas. Se encuentra disponible bajo la licencia GPL.

Como esta herramienta corre en máquinas con Servidores Webs y Soporte de PHP y MySQL, la tecnología utilizada ha ido variando durante su desarrollo.

The screenshot shows the phpMyAdmin interface for the 'openisc' database. The left sidebar shows the database structure with 'files' selected. The main area displays the 'files' table with the following data:

| id_file | id_project | Nombre         | Clik | Base       | End        | IRQ | Tamaño | Generar |

|---------|------------|----------------|------|------------|------------|-----|--------|---------|

| 36      | 1          | uart_top       | clik | 0x57000000 | 0x0000009b | 2   | 4      | 1       |

| 37      | 1          | onchip ram top | clik | 0x00000000 | 0x00000100 |     | 4096   | 1       |

| 38      | 1          | pio led        | clik | 0x90000000 | 0x0000000a |     | 1      | 1       |

Below the table, there are buttons for 'Perfil/Perfeccionamiento', 'Editar', 'Explicar el SQL', 'Crear código PHP', and 'Actualizar'. A note at the bottom says 'Podría ser aproximado. Leéase la FAQ 3.11'.

Figura 3.2. Herramienta phpMyAdmin.

## Servidor de aplicaciones

Un *servidor de aplicaciones* [15] usualmente se trata de un dispositivo de software que

proporciona servicios de aplicación a los equipos o dispositivos cliente, por lo general a través de Internet y utilizando el protocolo http (*HyperText Transfer Protocol*). Generalmente gestiona la mayor parte (o la totalidad) de las funciones de lógica de negocio y de acceso a los datos de la aplicación. Los principales beneficios de la aplicación de la tecnología de servidores de aplicación son la centralización y la disminución de la complejidad en el desarrollo de aplicaciones. Los servidores de aplicación se distinguen de los servidores web por el uso extensivo del contenido dinámico y por su frecuente integración con bases de datos.

La característica principal es que permiten la interactividad del usuario con la web,

Por tanto podemos distinguir 2 tipos de Scripts, o instrucciones que darán esa interactividad:

**Client Side Scripts**: scripts que se ejecutan en el Cliente, en el Navegador

**Server Side Scripts**: donde los Scripts (instrucciones) se procesan en el Servidor WEB.

Los Scripts Server Side se ejecutan en el servidor y, por tanto, deberemos asegurarnos que nuestro servidor web los soporta si queremos aplicarlos. Para su funcionamiento, el programa se ejecutará en el servidor con los datos o peticiones que el usuario manda desde su navegador y el servidor muestra los resultados del programa en una página HTML que el usuario verá normalmente en su browser.

Los más usados hoy en día son:

**CGI** Scripts. Abreviatura de "Common Gateway Interface" , protocolo de comunicación entre el servidor web y el cliente, el navegador. Este protocolo puede implementarse en cualquier lenguaje de los utilizados para Internet: PERL, C, Java, Visual Basic, PHP... Se utiliza habitualmente para contadores, formularios, chats, buscadores.

**ASP**. Abreviatura de Active Server Pages y tecnología propietaria de Microsoft. Se utiliza a menudo para la gestión de Bases de Datos ya que puede conectarse a SQL, Access, Oracle u otras. Requiere por parte del servidor un Microsoft Web Server , el navegador es indiferente pues el trabajo se realiza del lado del Server. Muestra páginas con extensión ASP, que se montan "on the fly" - al vuelo- según unas plantillas y personalizadas según petición de usuario.

**PHP**. Lenguaje similar al ASP pero código abierto y gratuito. Su gran potencia se encuentra en la interacción con bases de datos más utilizadas: Oracle, Sybase, MySQL.

**JSP**. Abreviatura de "Java Server Pages". La respuesta de SUN al ASP. No hemos entrado en detalles técnicos pues no era el objeto de este documento.

Finalmente nos hemos decidido por el servidor basado en PHP, debido al rápido aprendizaje, a su facilidad de uso y a la calidad de la documentación asociada, así como al hecho de ser código abierto.

## PHP

*PHP* [16] es un acrónimo recursivo que significa *PHP Hypertext Pre-processor* (initialmente PHP Tools, o, *Personal Home Page Tools*) y es un lenguaje de programación de alto nivel interpretado, diseñado originalmente para la creación de páginas web dinámicas. Es usado principalmente en interpretación del lado del servidor (server-side scripting), independiente del navegador que use el visitante, pero actualmente puede ser utilizado desde una interfaz de línea de comandos o en la creación de otros tipos de programas incluyendo aplicaciones con interfaz gráfica usando las bibliotecas Qt o GTK+.

Una de las características más importantes de PHP es que permite manejar bases de datos desde una interfaz web. Dado que PHP es un lenguaje de código abierto, se puede usar libremente sin necesidad de pagar licencia.

Generalmente se ejecuta en un servidor web, tomando el código en PHP como su entrada y creando páginas web como salida. Puede ser desplegado en la mayoría de los servidores web y en casi todos los sistemas operativos y plataformas sin costo alguno.

Las principales ventajas de los servidores de aplicaciones que trabajan con PHP son:

- Facilidad de aprendizaje.

- PHP puede funcionar bajo casi todos los sistemas operativos (Unix, Windows, Mac OS).

- Soporta conexiones con casi cualquier tipo de bases de datos.

- PHP tiene licencia open-source, lo cual implica un coste nulo en la adquisición del software del servidor.

- Es fácil y rápido ampliar las funcionalidades del lenguaje PHP y solventar errores, gracias a numerosas extensiones que surgen a menudo gracias a tener licencia abierta.

- PHP permite leer y manipular datos desde diversas fuentes, incluyendo datos que pueden ingresar los usuarios desde formularios HTML.

- Permite técnicas de programación orientada a objetos.

El servidor utilizado para dar soporte al servidor de aplicaciones es el servidor Apache.

## Apache

El servidor HTTP Apache [17] es un servidor Web de tecnología Open Source sólido y para uso comercial desarrollado por la Apache Software Foundation (<http://www.apache.org>) para plataformas Unix (BSD, GNU/Linux, etc.), Microsoft Windows, Macintosh y otras, que implementa el protocolo HTTP/1.1 y la noción de sitio virtual.

Es un servidor web que se carga como un servicio más del sistema operativo. Cuando está activo, convierte tu máquina en un servidor capaz de enviar contenido a cualquier navegador.

La versión utilizada es la 2.2.11.

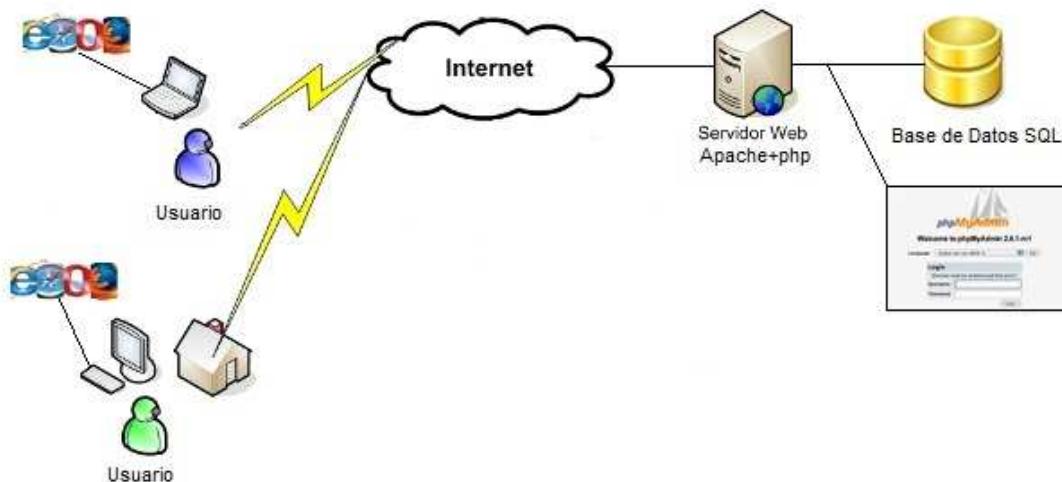

## Arquitectura implementada

La arquitectura implementada está formada por: MYSQL para el uso de la base de datos, PHPMyAdmin para la creación de las tablas de la BD y la administración de esta, y el servidor Apache+PHP para dar servicio.

En el siguiente dibujo podemos observar la arquitectura utilizada:

Figura 3.3. Arquitectura del Sistema.

Para el diseño de la página también se han usado hojas de estilo, CSS.

## CSS

CSS [16] es un lenguaje de hojas de estilos creado para controlar el aspecto o presentación de los documentos electrónicos definidos con HTML y XHTML. CSS es la mejor forma de separar los contenidos y su presentación y es imprescindible para crear páginas web complejas.

La idea que se encuentra detrás del desarrollo de CSS es separar la *estructura* de un documento de su presentación.

También se ha utilizado javascript para validar los form de <html> y concretamente se ha usado una librería javascript, overLIB, para insertar pequeñas ventanas "popup" informativas.

## Javascript

JavaScript [17] es un lenguaje de programación que se utiliza principalmente para crear páginas web dinámicas.

Una página web dinámica es aquella que incorpora efectos como texto que aparece y desaparece, animaciones, acciones que se activan al pulsar botones y ventanas con mensajes de aviso al usuario.

Técnicamente, JavaScript es un lenguaje de programación interpretado, por lo que no es necesario compilar los programas para ejecutarlos. En otras palabras, los programas escritos con JavaScript se pueden probar directamente en cualquier navegador sin necesidad de procesos intermedios.

## 3.2 Diseño de la aplicación

Las funciones principales de la aplicación son:

- Poder subir archivos (módulos) al server.

- Eliminar archivos (módulos) del server.

- Crear proyectos OpenRISC.

- Insertar componentes de la librería al sistema.

- Poder observar el mapa de memoria del Sistema a generar.

- Visualizar la librería de componentes disponibles.

- Generar un SoC basado en el procesador OpenRisc.

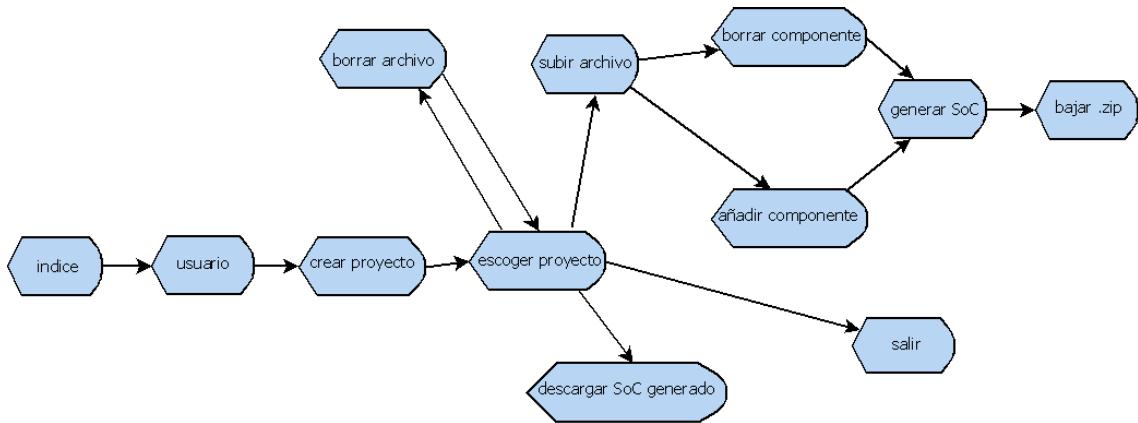

### Diagrama de la aplicación web

Figura 3.4. Estructura de la Aplicación.

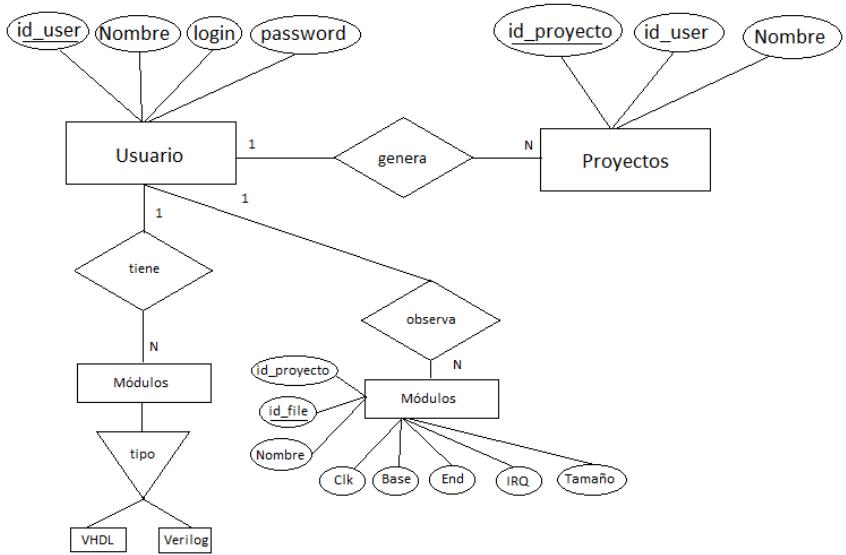

### Diseño de la Base de Datos

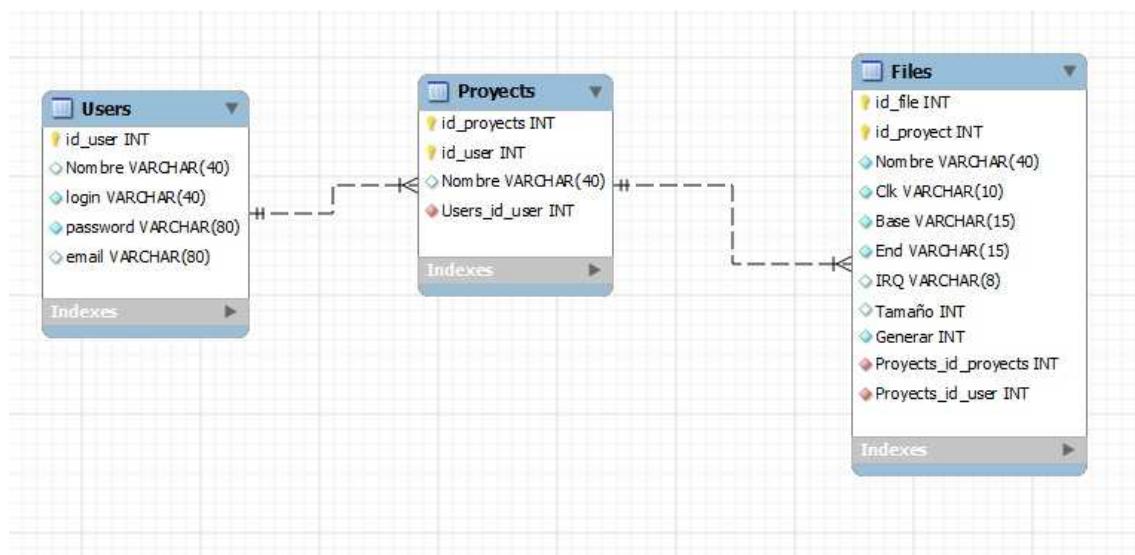

Mostraremos a continuación el diagrama de entidad-relación que modela la pequeña base de datos con la que trabajará nuestra aplicación. Para guardar la información de los módulos se usará una base de datos, no muy extensa, solamente el uso de 3 tablas.

Figura 3.5. Modelo Entidad-Relación.

## Implementación de la base de datos

La base de datos contiene 3 tablas como podemos observar en la siguiente imagen:

Figura 3.6. Esquema general de la base de datos.

## **Tablas de la Base de Datos**

### **Tabla *Users***

Esta tabla es la responsable de controlar el acceso de los usuarios a la aplicación.

Campos:

- id\_user: identificador del usuario.

- Nombre: Nombre del usuario.

- login: nombre para poder entrar a la aplicación.

- password: palabra de paso del usuario.

- e-mail: dirección de correo electrónico del usuario.

### **Tabla *Projects***

Esta tabla es la responsable de almacenar los distintos proyectos del usuario.

Campos:

- id\_proyect: identificador del proyecto.

- id\_user: identificador del usuario.

- Nombre: Nombre del proyecto.

### **Tabla *Files***

Esta tabla es la responsable de guardar los datos de los módulos que los usuarios irán insertando.

Campos:

- id\_file: identificador del archivo.

- id\_proyect: identificador del proyecto.

- Nombre: Nombre del archivo.

- Clk: ciclo de reloj del SoC.

- Base: dirección de inicio del módulo en el sistema.

- End: dirección de final del módulo en el sistema.

- IRQ: interrupción del módulo.

- Tamaño: tamaño en bytes del módulo.

- Generar: indica si el módulo ha sido insertado.

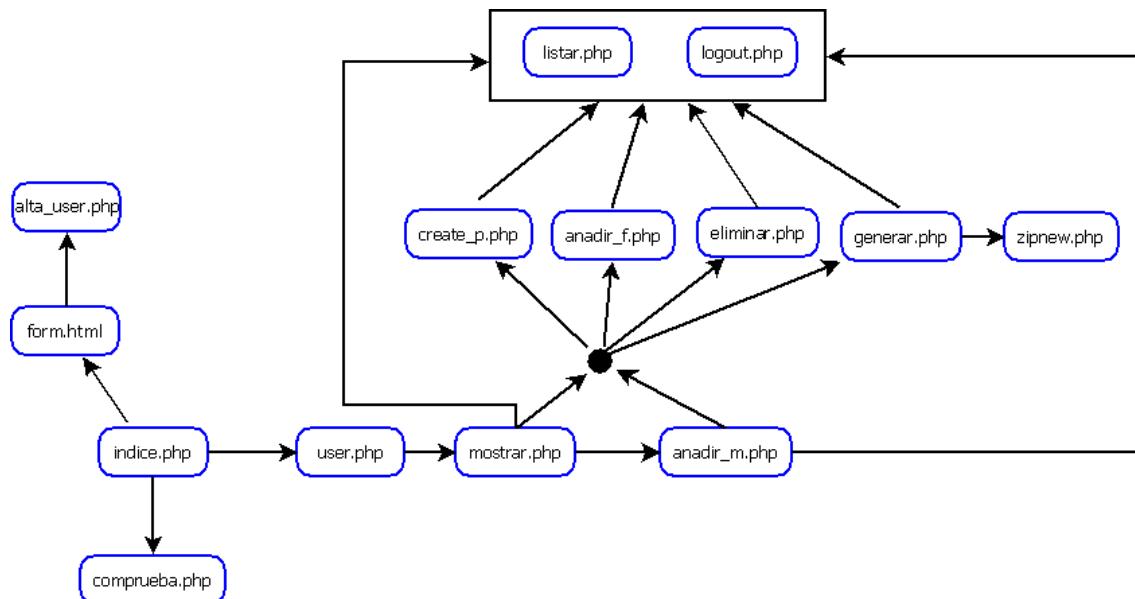

### 3.3 Diseño de los módulos

#### Diagrama de scripts

Figura 3.7. Diagrama de Scripts del portal web.

A continuación explicaremos cada script que componen esta aplicación. Casi todos los scripts contienen una función para conectarse a la base de datos para realizar las distintas consultas que se requieren en cierto momento. También comentar que todos los scripts tienen un menú en la parte superior, que muestra unas opciones como son: escoger proyecto, listar proyectos y salir de la aplicación.

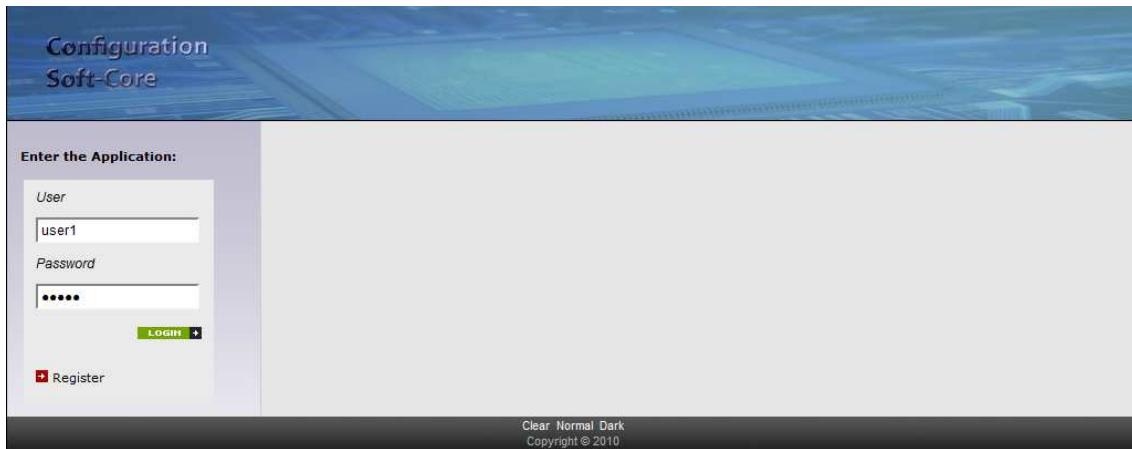

#### indice.php

Esta es la página inicial de la aplicación. A la izquierda de la página estará la parte de login para poder entrar en ella. Justo debajo hay un link a form.html para poder darse de alta.

#### comprueba.php

El encargado de validar los datos introducidos para acceder a la aplicación.

### **form.html**

Este script es el encargado de obtener los datos de usuario para su registro mediante un formulario que una vez completado será validado por alta\_user.php

### **alta\_user.php**

Es el encargado de validar los datos del usuario introducidos en el formulario, accediendo a la base de datos y mirando si el usuario existe o se puede crear.

### **user.php**

La página que da la bienvenida al usuario dando la opción de insertar sus componentes al sistema.

### **mostrar.php**

Este script, en la parte izquierda, mostrará la opción de escoger proyecto o de crear uno nuevo. Una vez escogido el proyecto a generar, se le abrirá la librería de componentes separados por módulos. Al clicar en el módulo, se le desplegará una lista de componentes disponibles para insertar. Previamente el usuario habrá tenido que subir el fichero al servidor. Si no ha subido nada, los módulos estarán vacíos.

También en esta parte el usuario tiene las opciones de subir los archivos al server, de eliminarlos o de bajar el proyecto ya generado.

En la parte central de la aplicación se le mostrarán los componentes que tiene insertados, con la descripción del mapa de memoria de cada uno de ellos.

En la parte inferior derecha, el usuario tiene la opción de borrar de la lista de componentes el que él deseé, donde rápidamente se actualizará la lista de componentes insertados. Justo a la izquierda de esta opción el usuario podrá generar el archivo principal, donde se insertarán todos los componentes de esta lista.

Una vez aceptada la opción de generar este script nos dirigirá a generar.php.

### **anadir\_m.php**

Al clicar como he mencionado antes, en el módulo, se abrirá la lista de componentes. Si ahora clicamos en el componente, éste es insertado en el sistema, dando a generar el script anadir\_m.php. Este script es casi lo mismo que mostrar, llevando a cabo las mismas funcionalidades pero pasando las variables del componente por la url. Concretamente el nombre del fichero y el identificador de proyecto. Cada vez que se clique en un componente se llamará si mismo este script.

### **create\_p.php**

Aquí se crea un proyecto, dándole un nombre y creándose una carpeta en el servidor con este nombre.

### **anadir\_f.php**

Este script es el encargado de subir los ficheros al servidor en una carpeta existente o la que el desee crear. Hay una opción para insertar el tamaño del componente a subir. Normalmente se usa para los componentes tipo Memoria (flash, sram, onchip, etc.). Al mismo tiempo de subir el fichero, este es insertado en la base de datos.

### **eliminar.php**

Encargado de eliminar los ficheros del servidor.

### **listar.php**

Script que muestra todos los proyectos del usuario con los componentes que han sido insertados.

### **logout.php**

Script encargado de cerrar la sesión de la aplicación.

### **generar.php**

Este script es el más importante ya que es el encargado de insertar los módulos en el sistema.

### **zipnew.php**

El encargado de generar el zip final del proyecto insertando las carpetas propias de OpenRISC. En este apartado se ha utilizado la librería pclzip-2-6, para poder crear el zip.

### **funciones.php**

Script que contiene todas las funciones utilizadas en la aplicación. Mostramos por ejemplo las más importantes:

```

function conectar_bd(){

include("config.php");

```

```

$link=mysql_connect($server,$dbuser,$dbpass); //conectamos a BD

if (!$link)

{

die ('No se ha podido conectar con la Base de Datos<br>' .mysql_error());

}

$db_selected = mysql_select_db($database,$link);

if (!$db_selected)

{

die ('No puedo usar la Base de Datos<br>' .mysql_error() );

}

return $link;

}

```

Esta primera función nos conecta con la base de datos correspondiente.

```

closedir($dir);

}

```

Esta segunda función, nos imprime por pantalla los componentes disponibles en la librería.

```

function BuscaFiles($cpt, $registrod)

{

$file='nofile';

$dir = opendir($cpt) or die('Error');

$e=0;

while ($elemento = @readdir($dir))

{

if ($e==0)

{

if (($elemento != '.') && ($elemento != '..'))

{

$ele=explode(".", $elemento);

if ($ele[0] == $registrod)

{

$file=$elemento;

$e=1;

}

else

{

$file='nofile';

}

}

}

}

return $file;

}

```

Y esta tercera función busca los ficheros en el servidor, si lo encuentra devuelve su nombre.

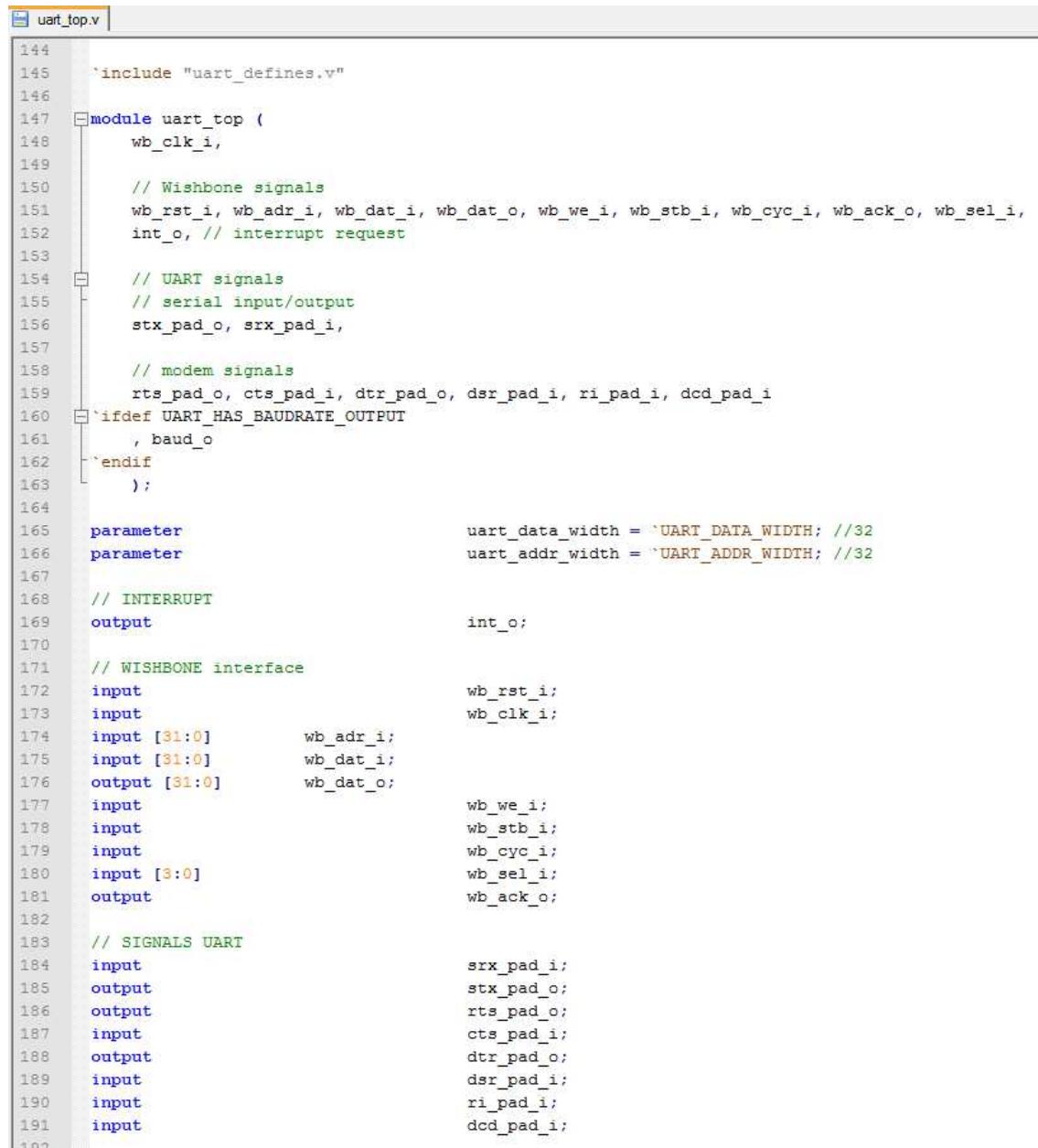

## Proceso de generación del SoC

Seguidamente explicaremos el proceso para generar el SoC. El softcore OpenRisc contiene dos archivos importantes donde se encuentra la información sobre los componentes. Los archivos son *cyc\_or12Defines.v* y *cyc\_or12\_mini\_top.v*.

### **cyc\_or12Defines.v**

Contiene las direcciones de memoria de los componentes insertados en el SoC.

En el siguiente código podemos observar su contenido:

```

`define CYCLONE

```

Primeramente tenemos las interrupciones del sistema:

```

//

// Interrupts

//

`define APP_INT_RES1      1:0

`define APP_INT_UART      2

`define APP_INT_RES2      3

`define APP_INT_ETH       4

`define APP_INT_PS2       5

`define APP_INT_RES3     19:6

```

Seguidamente tenemos el mapa de memoria, que nos muestra qué elementos tenemos insertados en el sistema:

```

//

// Address map

//

`define APP_ADDR_DEC_W      8

`define APP_ADDR_ONCHIP `APP_ADDR_DEC_W'h00

`define APP_ADDR_UART `APP_ADDR_DEC_W'h04

`define APP_ADDR_DECP_W    4

`define APP_ADDR_PIO `APP_ADDR_DEC_W'h9

// `APP_ADDR_DEC_W'h97

// `APP_ADDR_DEC_W'h92

// `APP_ADDR_DEC_W'h9d

// `APP_ADDR_DEC_W'h90

// `APP_ADDR_DEC_W'h94

// `APP_ADDR_DEC_W'h9e

// `APP_ADDR_DEC_W'h9f

`define APP_ADDR_FAKEMC    4'h6

```

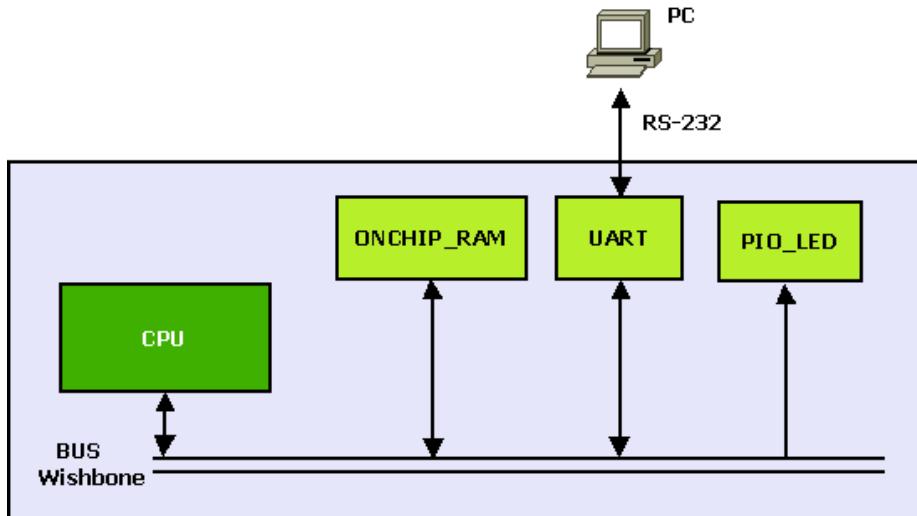

Aquí podemos observar que en el sistema tenemos insertados 3 componentes: un módulo onchip\_ram, una UART, y un módulo pio led.

Para generar este fichero cuando el usuario inserta un componente y genera el proyecto, tenemos que ir leyendo el fichero, y averiguar qué dirección está libre para poder añadírsela. Como también buscar si el componente ya esté insertado y no ofrecerle otra dirección distinta. Por tanto la dirección que le indicaremos será la dirección base, la dirección de inicio del componente que después nos servirá para mostrar en el mapa de memoria.

Justo con esta dirección de inicio y el tamaño del componente se calculará la dirección end, la dirección de final.

### **cyc\_or12\_mini\_top.v**

Este archivo es el que contiene toda la información del sistema. Aquí estarán todas las señales de los componentes insertados y dónde también se juntarán con las líneas del bus Wishbone.

Para la creación de este archivo:

- 1- Se obtiene una búsqueda en la base de datos de los componentes que se quieren insertar en el SoC. Esto nos lo mostrará el campo Generar cuando esté activado a 1.

- 2- Se busca en el server que los archivos existan físicamente.

- 3- Si el archivo se encuentra, diferenciamos si el componente está escrito en verilog o en vhdl, dado que no es la misma sintaxis.

- 4- Se busca la ruta del archivo a insertar y se abre en modo lectura.

- 5- Se leen todas las variables necesarias para la inclusión del componente en el Soc.

- 6- Una vez leídas las variables se abre el fichero cyc\_or12\_mini\_top.v en modo lectura. Gracias a unos tags en este fichero sabremos donde situar cada variable donde le corresponda.

- 7- Al mismo tiempo se crea un cyc\_or12\_mini\_top\_temp.v para ir añadiendo las variables que hemos guardado anteriormente.

- 8- Una vez acabado de leer el cyc\_or12\_mini\_top.v principal, el fichero temporal se reescribe por éste para así seguir con el siguiente componente que se quiera insertar, haciendo que se vaya actualizando el fichero principal.

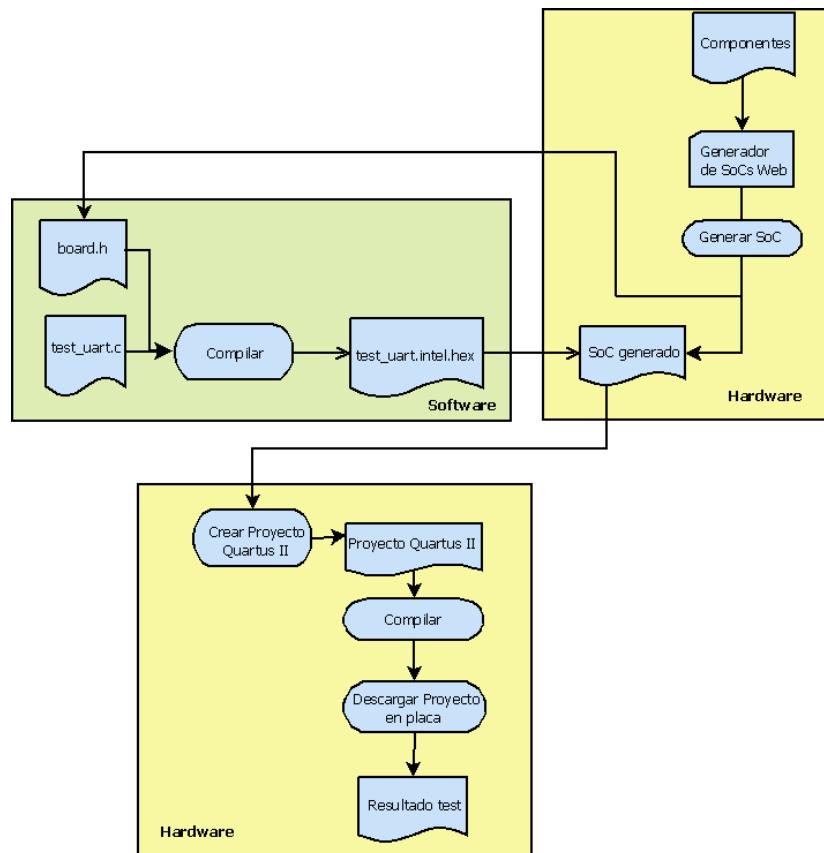

- 9- Una vez acabado con la inserción de todos los componentes, se llevará a cabo la creación del zip, que incluirá todos los archivos propios del Soc OpenRISC. para poder comprobar después, por ejemplo con el Quartus<sup>6</sup> que todo se ha realizado correctamente.

---

<sup>6</sup> **Quartus II** es una herramienta de software producida por Altera para el análisis y la síntesis de diseños realizados en HDL.

En esta imagen podemos observar como es un fichero en verilog, concretamente este es el fichero del componente UART: