---

This is the **published version** of the master thesis:

Midane, Walid Hlou; Paco Sánchez, Pedro Antonio de , dir. L-Band Solid State Power Amplifier for space applications. 2022. 90 pag. (1170 Màster Universitari en Enginyeria de Telecomunicació / Telecommunication Engineering)

---

This version is available at <https://ddd.uab.cat/record/259428>

under the terms of the  license

A Thesis for the

**Master in Telecommunication Engineering**

---

**L-Band Solid State Power Amplifier

for space applications**

by

Walid Hlou Midane

---

Company Supervisor: Oscar Cuñado

*Electrical Engineering Department*

**Communications Division**

**SENER Aeroespacial**

Academic Supervisor: Pedro de Paco

*Departament de Telecomunicació i Enginyeria de Sistemas*

**Escola Tècnica Superior d'Enginyeria (ETSE)**

**Universitat Autònoma de Barcelona (UAB)**

El sotasingnant, *Pedro de Paco*, Professor de l'Escola Tècnica Superior d'Enginyeria (ETSE) de la Universitat Autònoma de Barcelona (UAB),

CERTIFICA:

Que el projecte presentat en aquesta memòria de Treball Final de Master ha estat realitzat sota la seva direcció per l'alumne *Walid Hlou Midane*.

I, perquè consti a tots els efectes, signa el present certificat.

Bellaterra, 17 de gener del 2022.

Signatura: *Pedro de Paco*

## Resum

Aquesta tesi es va fer al departament d'enginyeria elèctrica de la Divisió de Comunicacions de l'empresa SENER Aeroespacial. A causa de la demanda creixent d'Amplificadors de Potència d'Estat Sòlid (SSPA) de GaN per a aplicacions espacials, l'empresa va promoure un projecte intern R+D per superar els reptes clau de la implementació de la tecnologia GaN en amplificadors de potència qualificats per a l'espai, combinant l'experiència multidisciplinària de SENER Aeroespacial que inclou el disseny de RF, el disseny mecànic-tèrmic, la fabricació i la qualitat.

Entre totes les disciplines esmentades, aquesta tesi se centra especialment en la part corresponent al disseny i caracterització RF dels SSPAs. Es proposa el disseny i desenvolupament complet del producte des d'un transistor MMIC de potència GaN en format die fins a la fabricació dels prototips representatius. La validació de les proves dels prototips es realitza a la Sala Neta utilitzant instruments de RF, i posteriorment, a partir dels resultats inicials, es fa la correlació de les mesures i la simulació per corregir i validar els models de simulació considerats inicialment.

## Resumen

Esta tesis se realizó en el departamento de ingeniería eléctrica de la División de Comunicaciones de la empresa SENER Aeroespacial. Debido a la creciente demanda de Amplificadores de Potencia de Estado Sólido (SSPA) de GaN para aplicaciones espaciales, la empresa promovió un proyecto interno I+D para superar los retos clave de la implementación de la tecnología GaN en amplificadores de potencia calificados para el espacio, combinando la experiencia multidisciplinaria de SENER Aeroespacial que incluye el diseño de RF, el diseño mecánico-térmico, la fabricación y la calidad.

Entre todas las disciplinas citadas, esta tesis se centra especialmente en la parte correspondiente al diseño y caracterización RF de los SSPAs. Se propone el diseño y desarrollo completo del producto desde un transistor MMIC de potencia GaN en formato die hasta la fabricación de los prototipos representativos. La validación de las pruebas de los prototipos se realiza en la Sala Limpia utilizando instrumentos de RF, y posteriormente, a partir de los resultados iniciales, se realiza la correlación de la medida y la simulación para corregir y validar los modelos de simulación considerados inicialmente.

## Abstract

This thesis was carried out in the electrical engineering department at the Communications Division of the company SENER Aeroespacial. Due to the increasing demand of GaN Solid State Power Amplifiers (SSPA) for space applications, an internal R+D project was promoted by the company to overcome the key challenges to implement GaN technology in space-qualified power amplifiers by combining the SENER Aeroespacial multi-disciplinary expertise including, RF design, mechanical-thermal design, manufacturing and quality.

Among all the cited disciplines, this thesis is focused particularly on the part corresponding to the SSPA RF design and characterization. Complete product design and development is proposed from a GaN power MMIC transistor in die format to the manufacturing of the representative prototypes. Test validation of the prototypes is performed in the Clean Room using RF instruments, then, based on the initial results, correlation of the measurement and simulation is performed to correct and validate the simulation models considered initially.

# Acknowledgements

This thesis is a result of my final Master year devoted to research and study, thus, I would like to acknowledge all the people who have been part of this journey with me.

I would like to express my gratitude to Oscar Cuñado. Thank you for giving me the opportunity to work on this amazing project and for giving me advice and support. I would like also to express my gratitude to Ivan Baro and Mohamed Chaibi for their support and instructions about RF design and measurements techniques.

I am especially grateful to all the clean room staff for their extremely professionalism and kindness.

I also would like to thank my supervisor, Dr. Pedro de Paco, for his support throughout this thesis.

Finally, even it's needless to say, I would like to thank all my dear people for their unconditionally support at good and tough times, not only throughout this thesis but since ever.

# Contents

|                                                       |      |

|-------------------------------------------------------|------|

| <i>Acknowledgments</i>                                | iii  |

| <i>List of Figures</i>                                | xii  |

| <i>List of Tables</i>                                 | xiii |

| <i>Acronyms</i>                                       | xv   |

| <b>1 Introduction</b>                                 | 1    |

| 1.1 Context . . . . .                                 | 1    |

| 1.1.1 Satellite Amplifier Technology . . . . .        | 1    |

| 1.1.2 Challanges of GaN technology in space . . . . . | 2    |

| 1.2 Motivations . . . . .                             | 3    |

| 1.3 Scope and objectives . . . . .                    | 4    |

| 1.4 Thesis Outline . . . . .                          | 5    |

| <b>2 State-of-the art</b>                             | 7    |

| 2.1 PA figures of merit . . . . .                     | 7    |

| 2.1.1 Power . . . . .                                 | 7    |

| 2.1.2 Gain . . . . .                                  | 9    |

|          |                                                        |           |

|----------|--------------------------------------------------------|-----------|

| 2.1.3    | Efficiency . . . . .                                   | 10        |

| 2.1.4    | Stability . . . . .                                    | 11        |

| 2.1.5    | Intermodulation and Harmonic Distortion . . . . .      | 12        |

| 2.1.6    | Adjacent Channel Power Ratio . . . . .                 | 14        |

| 2.1.7    | Error Vector Magnitude . . . . .                       | 16        |

| 2.2      | PA classes . . . . .                                   | 16        |

| 2.2.1    | Transconductance Power amplifiers . . . . .            | 18        |

| 2.2.2    | High Efficiency Power amplifiers . . . . .             | 19        |

| <b>3</b> | <b>SSPA design using Power Bar</b>                     | <b>25</b> |

| 3.1      | Mechanical and Thermal Design . . . . .                | 25        |

| 3.2      | Electrical design . . . . .                            | 26        |

| 3.2.1    | 8-cells Power Bar Description . . . . .                | 26        |

| 3.2.2    | Biasing procedure . . . . .                            | 28        |

| 3.2.3    | Optimal load and source impedance extraction . . . . . | 29        |

| 3.2.4    | Stability Network Design . . . . .                     | 31        |

| 3.2.5    | Pre-matching network design . . . . .                  | 32        |

| 3.2.6    | Input Matching Network Design . . . . .                | 33        |

| 3.2.7    | Output Matching Network . . . . .                      | 35        |

| 3.2.8    | Part Stress and Derating Analysis . . . . .            | 35        |

| 3.2.9    | SSPA full layout . . . . .                             | 36        |

| <b>4</b> | <b>SSPA Functional Test</b>                            | <b>39</b> |

| 4.1      | Prototype 1 . . . . .                                  | 39        |

|          |                                                |           |

|----------|------------------------------------------------|-----------|

| 4.1.1    | Small signal measurement . . . . .             | 39        |

| 4.1.2    | Large signal Measurements . . . . .            | 41        |

| 4.2      | Prototype 2 . . . . .                          | 48        |

| 4.2.1    | Dissipation Issues . . . . .                   | 49        |

| 4.2.2    | Small signal measurements . . . . .            | 50        |

| <b>5</b> | <b>Simulation and Measurements Correlation</b> | <b>53</b> |

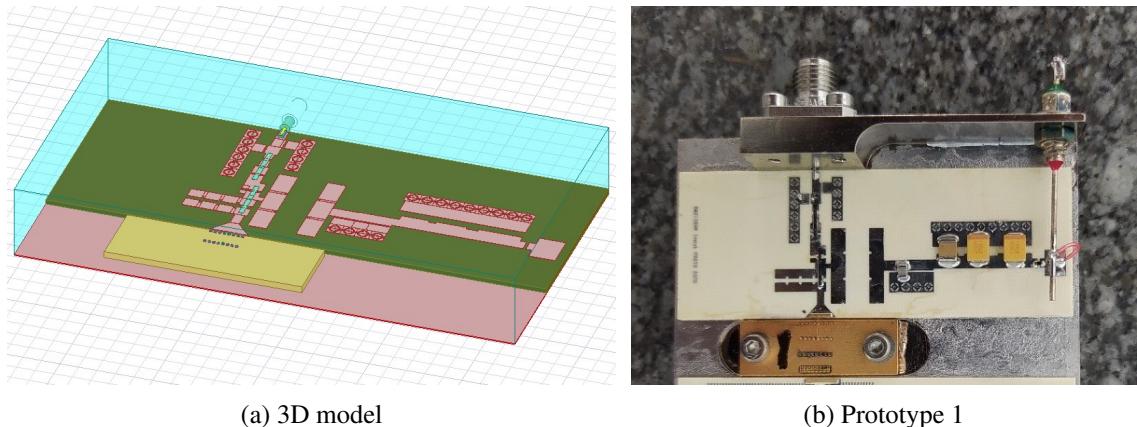

| 5.1      | Input network . . . . .                        | 53        |

| 5.1.1    | Border capacitors . . . . .                    | 56        |

| 5.1.2    | Bonding Wires . . . . .                        | 59        |

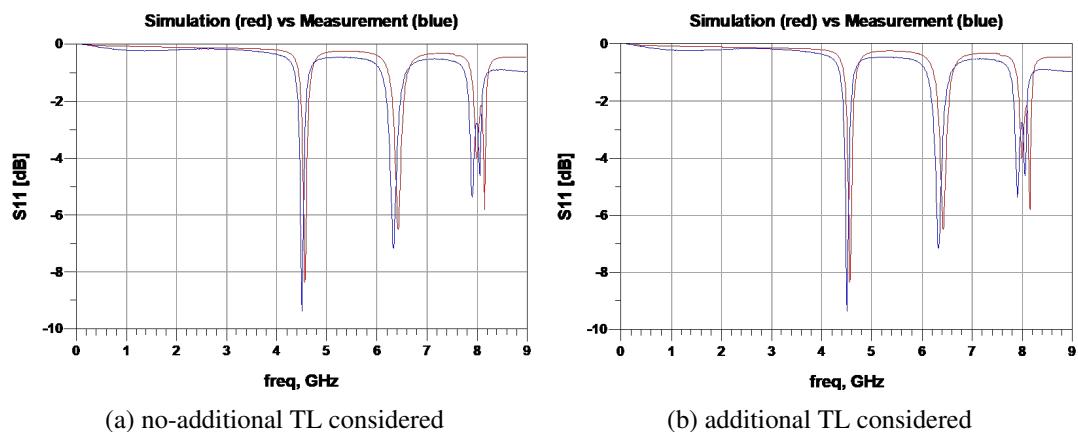

| 5.2      | SSPA full layout . . . . .                     | 66        |

| <b>6</b> | <b>Conclusions and Future work</b>             | <b>69</b> |

| 6.1      | Conclusions . . . . .                          | 69        |

| 6.2      | Future work . . . . .                          | 70        |

# List of Figures

|      |                                                                                                                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Linearizer [1]                                                                                                                                                                                   | 4  |

| 2.1  | PA diagrams                                                                                                                                                                                      | 8  |

| 2.2  | $P_{1dB}$ and $P_{3dB}$ definition [2]                                                                                                                                                           | 9  |

| 2.3  | Intermodulation and harmonic distortion [3]                                                                                                                                                      | 13 |

| 2.4  | Representation of the figures of merit when a the PA exhibits strong nonlinearity [3]                                                                                                            | 15 |

| 2.5  | Efficiency enhancement mechanisms their hybrids and possible areas for further improvement [4]                                                                                                   | 17 |

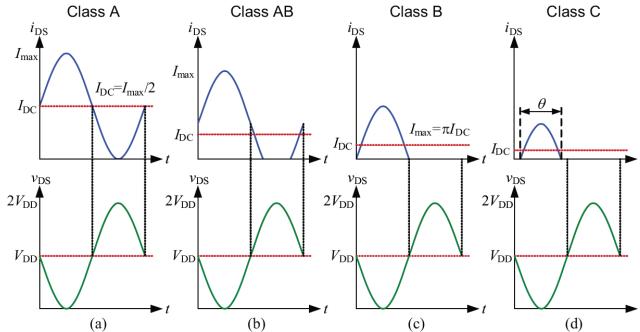

| 2.6  | Various DC bias points of Class-A,AB,B and C [5]                                                                                                                                                 | 18 |

| 2.7  | Voltage and current waveform [5]                                                                                                                                                                 | 18 |

| 2.8  | Voltage-mode Class-D PA: (a) simplified circuit schematic, (b) voltage and current waveforms [5]                                                                                                 | 20 |

| 2.9  | Class-E PA: (a) simplified circuit schematic, (b) voltage and current waveforms [5]                                                                                                              | 20 |

| 2.10 | Frequency-domain high-efficiency PAs (Class-F and Class-F <sup>-1</sup> ): (a) simplified circuit schematic, and voltage and current waveforms of (b) Class-F and (c) Class-F <sup>-1</sup> PAs. | 21 |

| 2.11 | Class F waveforms considering finite harmonics (up to third harmonic)                                                                                                                            | 23 |

|      |                                                                             |    |

|------|-----------------------------------------------------------------------------|----|

| 3.1  | Baseplate 3D view                                                           | 27 |

| 3.2  | Power Bar configuration                                                     | 27 |

| 3.3  | Maximum Gain and stability simulated performance                            | 28 |

| 3.4  | Elementary Cell Load Pull Performance                                       | 28 |

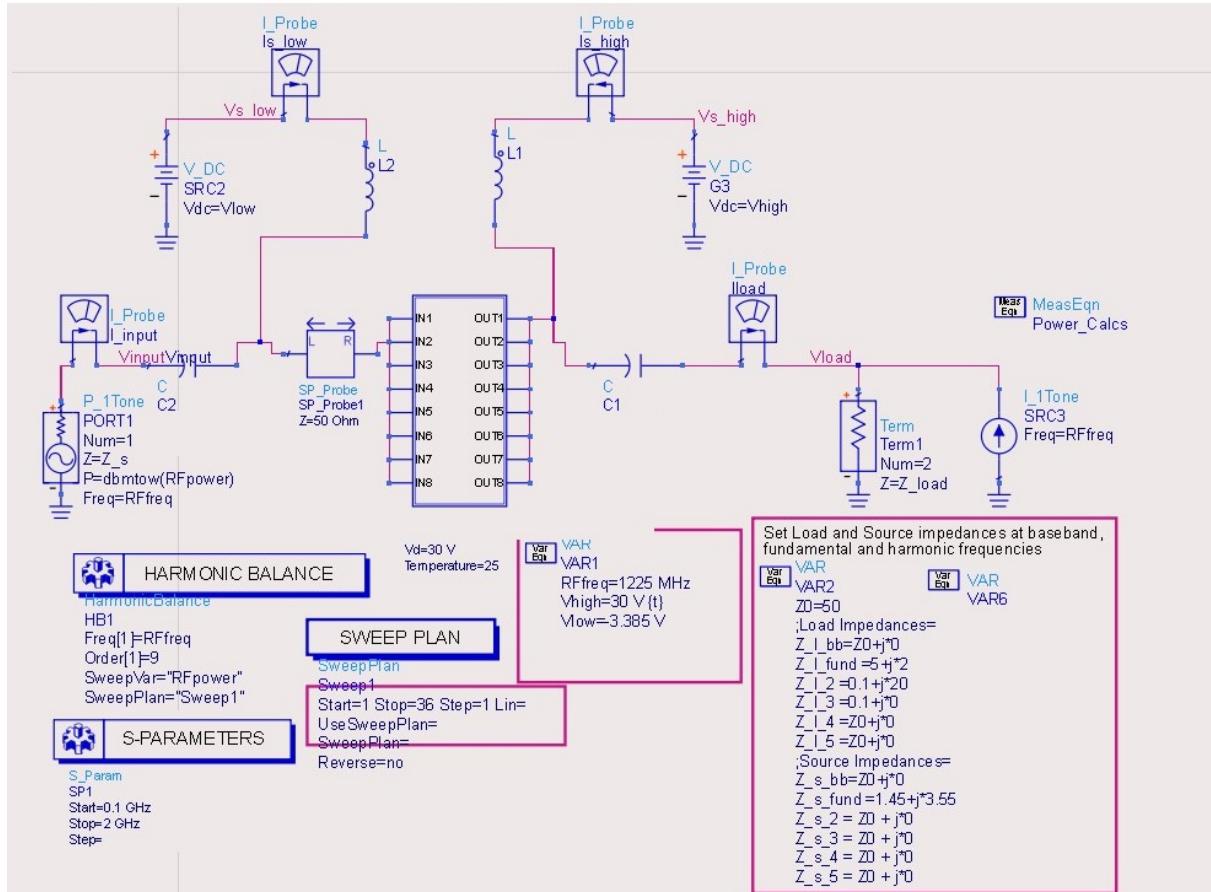

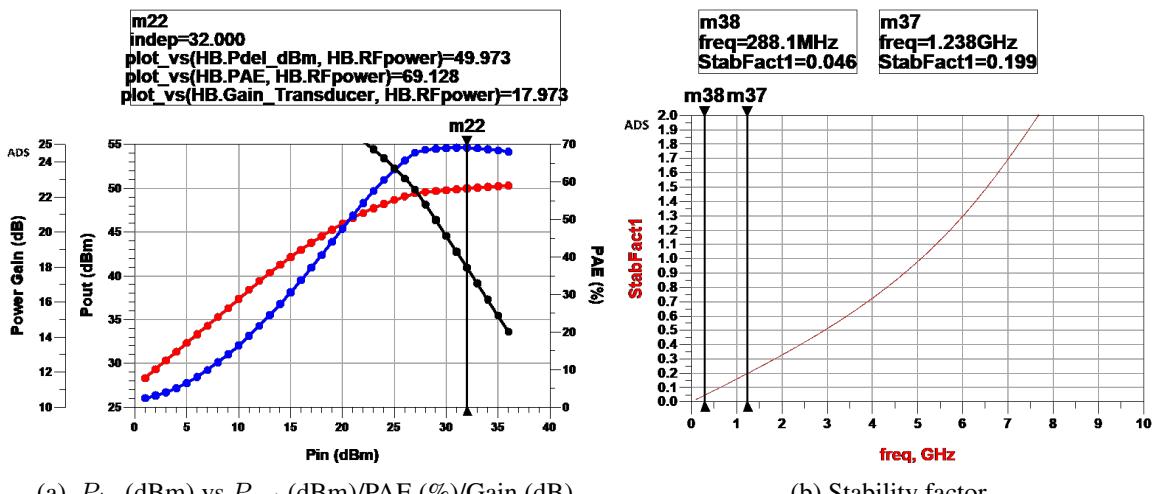

| 3.5  | Harmonic Balance Simulation schematic                                       | 30 |

| 3.6  | Harmonic Balance Simulation performance                                     | 30 |

| 3.7  | Harmonic Balance Simulation performance using Harmonic Loads                | 31 |

| 3.8  | Harmonic Balance Simulation schematic including stability network           | 32 |

| 3.9  | Harmonic Balance Simulation performance including stability network         | 32 |

| 3.10 | Pre-matching Network                                                        | 33 |

| 3.11 | Harmonic Balance Simulation performance including stability network + Taper | 34 |

| 3.12 | Input Matching Network                                                      | 34 |

| 3.13 | Output Matching Network                                                     | 35 |

| 3.14 | Harmonic Balance Simulation performance including input and output networks | 36 |

| 3.15 | Input network considering Resistors deratings                               | 37 |

| 3.16 | SSPA full layout                                                            | 37 |

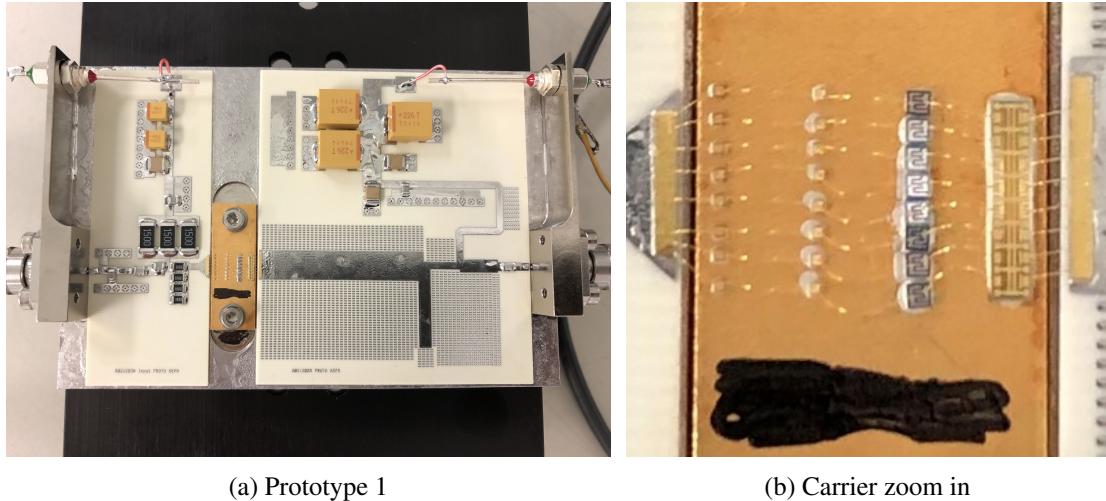

| 4.1  | Fabricated SSPA prototype 1                                                 | 40 |

| 4.2  | Small signal measurement test bench                                         | 40 |

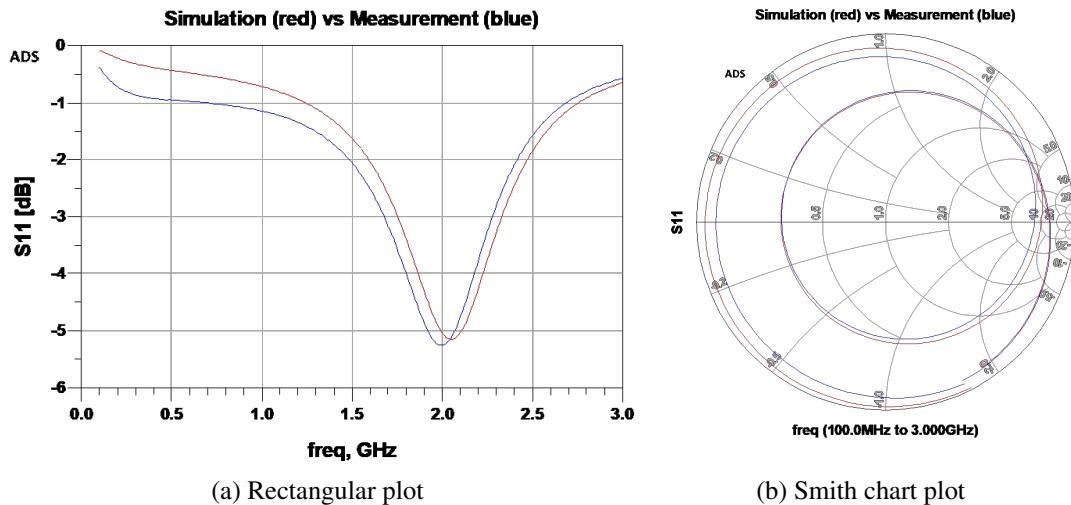

| 4.3  | Prototype 1 Small signal measurement: measurement vs simulation             | 41 |

| 4.4  | Large signal measurement laboratory test bench                              | 42 |

| 4.5  | Large signal measurements Bloch diagram test bench                          | 42 |

| 4.6  | Line-up using a -10 dBm maximum power RF generator                          | 44 |

---

|      |                                                                               |    |

|------|-------------------------------------------------------------------------------|----|

| 4.7  | Line-up using a +15 dBm maximum power RF generator . . . . .                  | 44 |

| 4.8  | Drivers characterization test bench block diagram . . . . .                   | 44 |

| 4.9  | Single Driver Input Power Sweep . . . . .                                     | 45 |

| 4.10 | Carrier configuration . . . . .                                               | 49 |

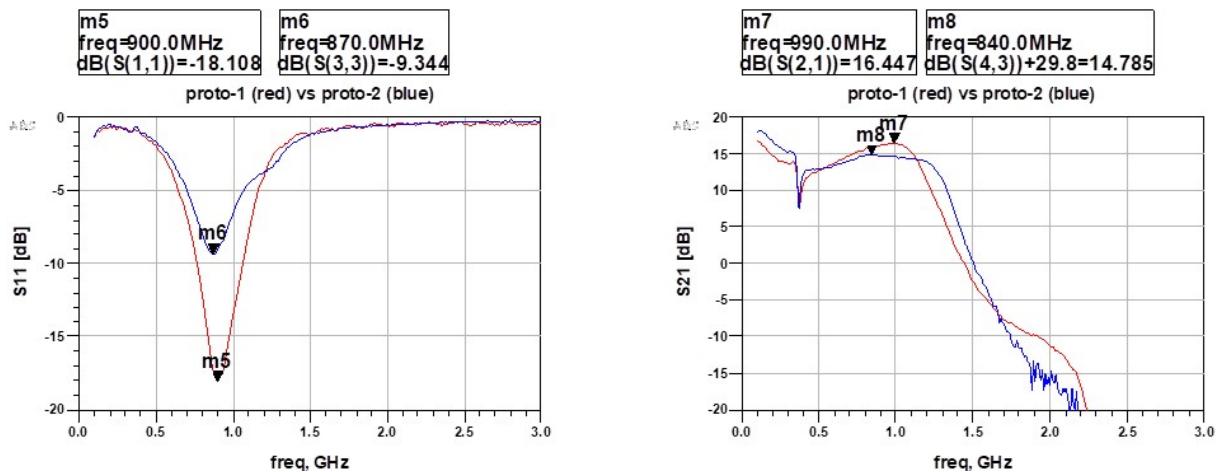

| 4.11 | Small signal measurement: Prototype 1 vs Prototype 2 . . . . .                | 50 |

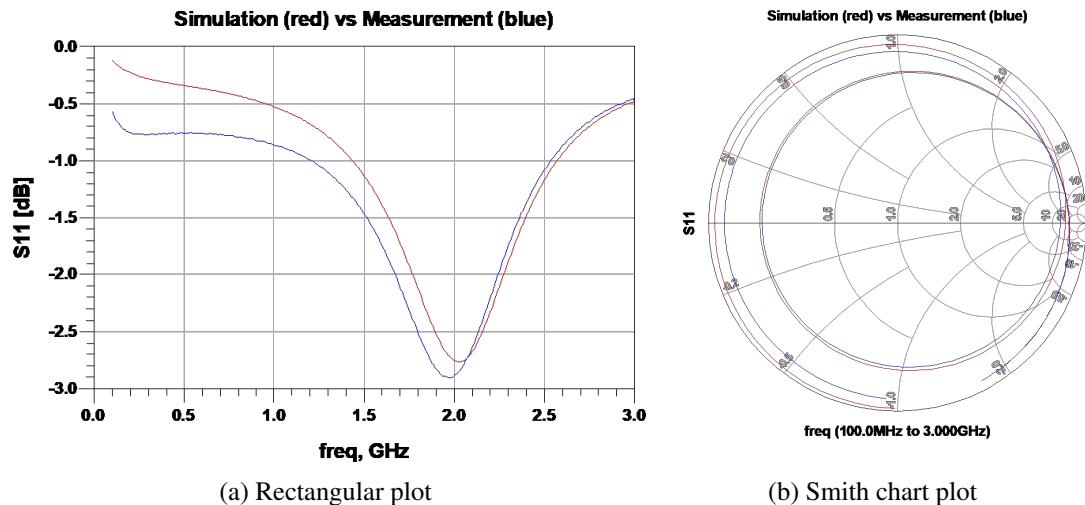

| 4.12 | Input passive network S-parameters measurement (no-MMIC) . . . . .            | 51 |

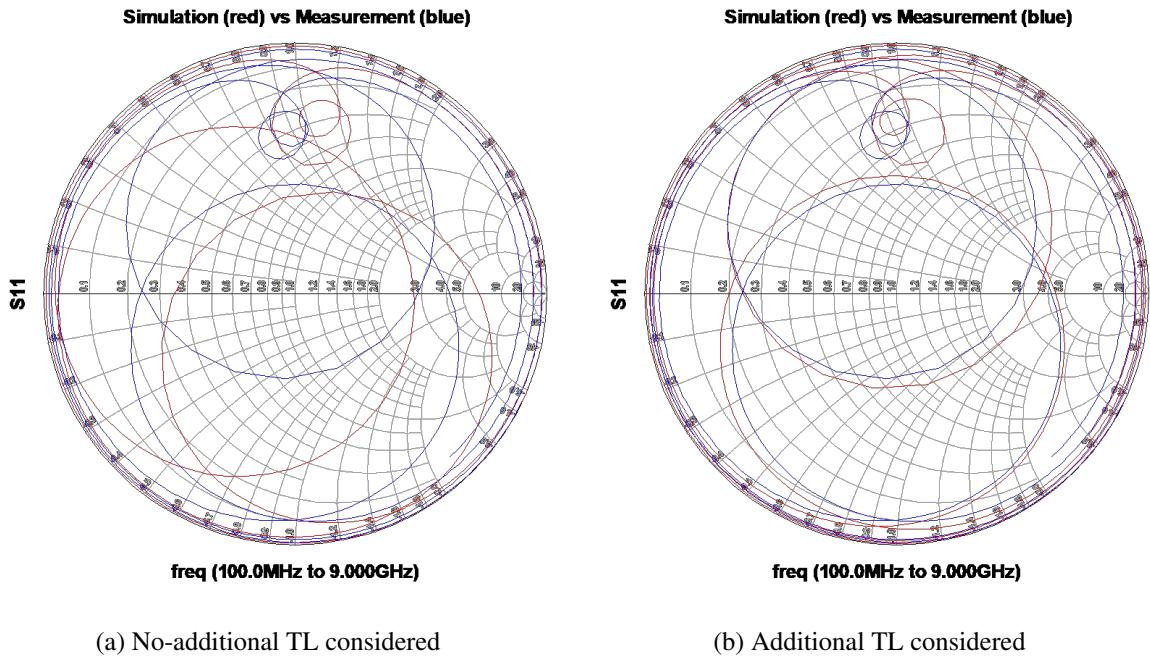

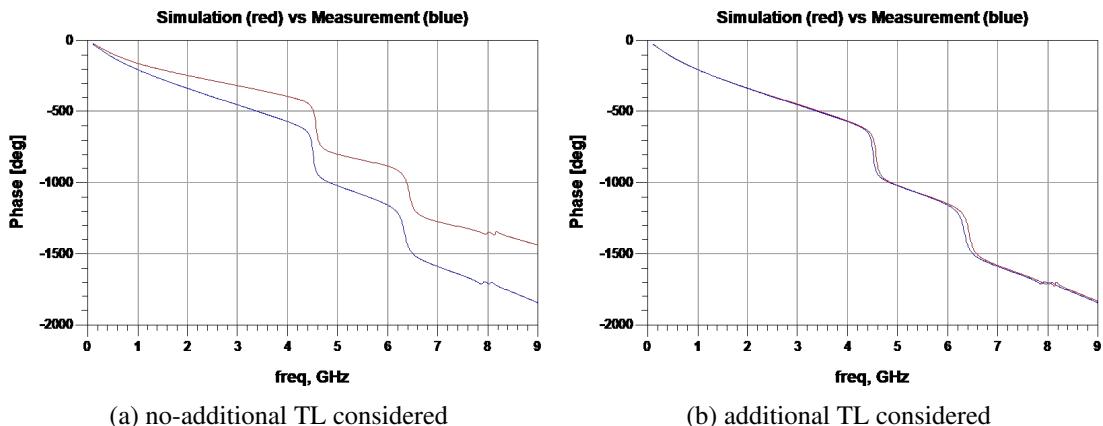

| 5.1  | Input passive network: taper open circuit (no-components) . . . . .           | 54 |

| 5.2  | Input passive network $S_{11}$ rectangular plot: taper open circuit . . . . . | 54 |

| 5.3  | Input passive network $S_{11}$ smith chart: taper open circuit . . . . .      | 55 |

| 5.4  | Input passive network phase rectangular plot: taper open circuit . . . . .    | 55 |

| 5.5  | Input passive network: bonding wires and border capacitors . . . . .          | 56 |

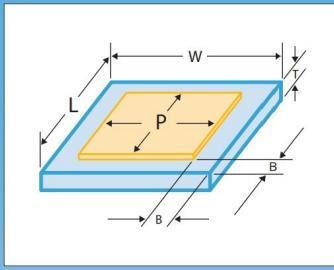

| 5.6  | Border capacitors Part Number Identification . . . . .                        | 56 |

| 5.7  | Border capacitors dimensions . . . . .                                        | 57 |

| 5.8  | Border capacitor simulation techniques . . . . .                              | 58 |

| 5.9  | 3 pF Border capacitor: HFSS model versus Real model . . . . .                 | 59 |

| 5.10 | Piecewise Approximation of Bonding wires . . . . .                            | 60 |

| 5.11 | Bonding wires modeling: option A . . . . .                                    | 60 |

| 5.12 | Bonding wires modeling: option B . . . . .                                    | 61 |

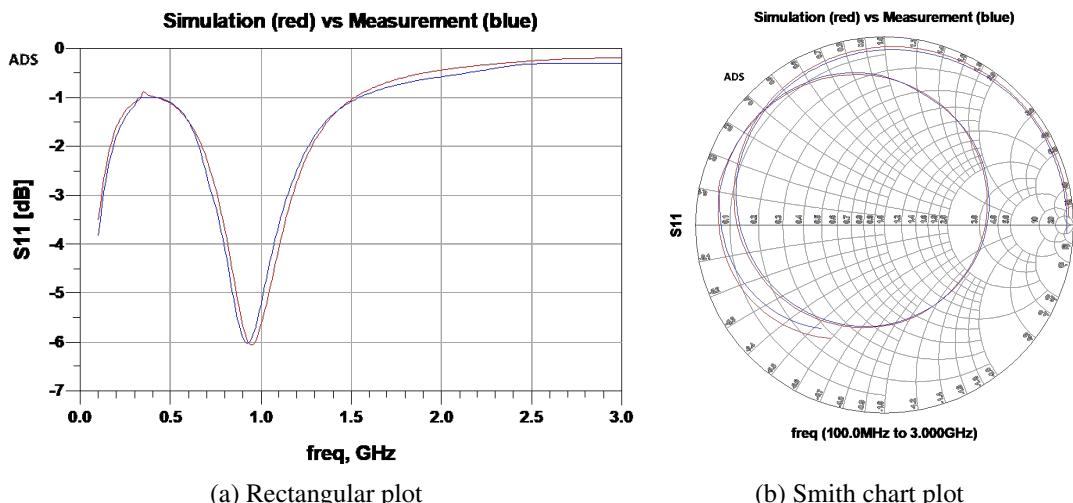

| 5.13 | Bonding wires and border capacitors (figure 5.5) S-parameters . . . . .       | 62 |

| 5.14 | Bonding wires and border capacitors (figure 5.5) S-parameters . . . . .       | 63 |

| 5.15 | Bonding wires and border capacitors . . . . .                                 | 63 |

| 5.16 | Bonding wires and border capacitors: Two connections S-parameters . . . . .   | 64 |

|      |                                                                              |    |

|------|------------------------------------------------------------------------------|----|

| 5.17 | Bonding wires and border capacitors: Four connections S-parameters . . . . . | 64 |

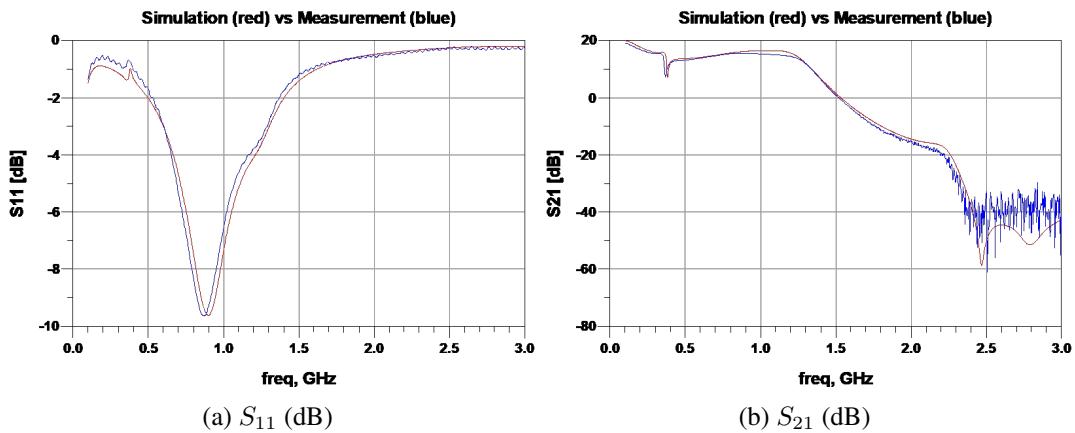

| 5.18 | Input passive network correlation (figure 4.12) S-parameters . . . . .       | 65 |

| 5.19 | SSPA small signal measurement correlation . . . . .                          | 66 |

| 5.20 | SSPA small signal measurement correlation: input matching network tuning . . | 67 |

# List of Tables

|     |                                                          |    |

|-----|----------------------------------------------------------|----|

| 3.1 | Harmonic Balance simulated performance . . . . .         | 31 |

| 3.2 | Harmonic Balance simulated performance summary . . . . . | 38 |

| 4.1 | Single Driver Input Power Sweep . . . . .                | 46 |

| 4.2 | Two Drivers Input Power Sweep . . . . .                  | 47 |

| 4.3 | SSPA Input Power Sweep . . . . .                         | 48 |

# Acronyms

- **ACPR** - Adjacent Channel Power Ratio

- **ADS** - Advanced Design System

- **ATC** - American Technical Ceramics

- **DC** - Direct Current

- **DPD** - Digital Predistortion

- **DUT** - Device Under Test

- **ESR** - Effective Serial Resistance

- **EVM** - Error Vector Magnitude

- **FET** - Field Effect Transistor

- **GaAs** - Gallium Arsenide

- **GaN** - Gallium Nitrite

- **GSM** - Global Systems for Mobile Communications

- **HD** - Harmonic Distortion

- **HEMT** - High Electron Mobility Transistor

- **IMD** - Intermodulation Distortion

- **IMN** - Input Matching Network

- **LNA** - Low Noise Amplifier

- **MMIC** - Microwave Monolithic Integrated Circuit

- **OMN** - Output Matching Network

- **PA** - Power Amplifier

- **PAE** - Power Added Efficiency

- **PCB** - Printed Circuit Board

- **RF** - Radio Frequency

- **RFFE** - Radio Frequency Front-End

- **SRF** - Self-Resonance Frequency

- **THD** - Total Harmonic Distortion

- **TL** - Transmission line

- **WLAN** - Wireless Local Area Network

- **GMSK** - Gaussian Minimum Shift Keying

# Chapter 1

## Introduction

This Master Thesis has been carried out at the Communications Division of the company SENER Aeroespacial as a result of a collaboration project with the Autonomous University of Barcelona (UAB), Engineering School.

### 1.1 Context

A satellite is a complex system with a huge number of electronic components working in harsh environmental conditions. Thus, robustness and reliability are key characteristics that have to be guaranteed to assure the overall success of the mission. Moreover, due to the high cost per kilogram of the payload, space and weight of every subsystems have to be reduced as much as possible to maximize the cost-benefits tradeoff of the mission. Therefore, the design of space borne microwave components is usually the result of a compromise among several aspects. In this context, the power amplifier represents the most critical block since it heavily affects mass,dc power consumption, thermal and mechanical management [6] [7].

#### 1.1.1 Satellite Amplifier Technology

As with nearly all communications systems, satellite transponders include transmit and receive modules. In the traditional architecture, the uplink signal is passed through a low noise amplifier

to a frequency converter, then to the transmit module. Amplifying the signal to the required output level is typically the role of a Travelling Wave Tube (TWT) high-precision amplifiers. This complexity drives the high price of TWTs and increases the risk of failure. TWT amplifiers also require very high bias voltage, usually thousands of volts, generated by a high voltage supply, which is expensive realization processes to avoid multipaction and corona effects. Moreover, they need large volume and heaviness especially in the lower frequency bands such as L and S [6] [8].

A solid-state solution offers a more robust, compact option. A GaN power amplifier uses standard IC manufacturing processes, producing small devices only a few millimeters on each side. Instead of using artisan-style manufacturing, GaN devices are produced using automated semiconductor processes at low-cost. While a single GaN device is unable to deliver the same output power as a TWT amplifier, multiple GaN devices can be combined in a small package. As an added benefit, GaN amplifiers only require bias voltages of 28 to 50 V. Given the differences between GaN and TWT amplifiers, GaN is particularly attractive for applications sensitive to size, weight and cost, as well as those that require less transmit power[8].

### 1.1.2 Challanges of GaN technology in space

While GaN amplifiers offer compelling benefits for satellite applications, specific challenges must be overcome to successfully use GaN in space-qualified hardware. The first and most obvious challenge arises from the high power density of the device. While TWT amplifiers also require a complex cooling system, a GaN IC generates significant heat in a very small space. For example, a 30 W solid-state GaN amplifier can easily draw 2.5 A biased at 28 V, resulting in 40 W power dissipation in an area not much larger than 10 mm<sup>2</sup>. If the thermal transfer is inadequate to cool the device, the elevated junction temperature will lower output power and possibly even causing catastrophic failure [8].

This raises the second challenge: reliability. The hig power dissipation common with GaN devices results in a significant temperature rise in the active region; as the temperature in the device increases, the reliability of the amplifier degrades. The temperature rise depends on the

power dissipation in the GaN and the thermal resistance between the device and the case, both difficult to model and control. Power dissipation depends on multiple factors such as RF drive and load impedance, and the thermal resistance is highly dependent on minor variations in the assembly process [7] [8].

Even under ideal circumstances, where the temperature is carefully controlled, high RF drive levels can cause permanent damage to the GaN lattice, resulting in degraded output power. Compared to GaAs, GaN is a much newer technology, and the lack of heritage raises reliability concerns. While this applies to all applications using GaN, operating in a space environment requires an extra focus to assure reliability. Since repair is generally not an option, a single device failure can be extremely expensive [7] [8].

This discussion highlights several key challenges to implement GaN technology in space-qualified power amplifiers. Addressing these requires multi-disciplinary expertise including, RF design, mechanical design, manufacturing and quality. Chapter 3 discuss possible approaches to managing these challenges when the Solid State Power Amplifier (SSPA) design is considered.

## 1.2 Motivations

SENER Aeroespacial promotes internal research and development tasks to increase its technologic knowledge (heritage) according to the demands of the space satellite systems. Hence, an R+D internal project has been promoted to address the increasing new demands for GaN SSPAs, especially, based on the Galileo Second Generation navigational satellite system needs.

Galileo navigational satellite system determine location on or near the Earth using radio signals broadcast by a constellation of satellites in different orbits around the planet. These satellites operate primarily at L-Band (1-2GHz) and on power generated by solar panels. Thus, every watt of electrical power is truly valuable, bringing a great need for Power amplifiers to be highly efficient. High efficiency is achieved at the expense of linearity and finding a trade-off between the two is one of the most challenging aspects of the power amplifiers design since it depends on the application of the whole system. In this case, the development of new modulation techniques is increasing the linearity required by PAs used for navigation systems

[1].

From a PA-designer's point of view, it is challenging to achieve high efficiency and high linearity simultaneously. However, on one hand , it is well known that a PA, in general, can operate efficiently only at a high level of device saturation, which is also the extremely non-linear region. On the other hand, for linear amplification, the transistor needs to be unsaturated and most of the dc input power is sacrificed in generating head room for a good linearity. Such scarified dc power transforms to heat, which can bring reliability issues and degrade the performance of the power amplifier itself as highlighted in previous section.

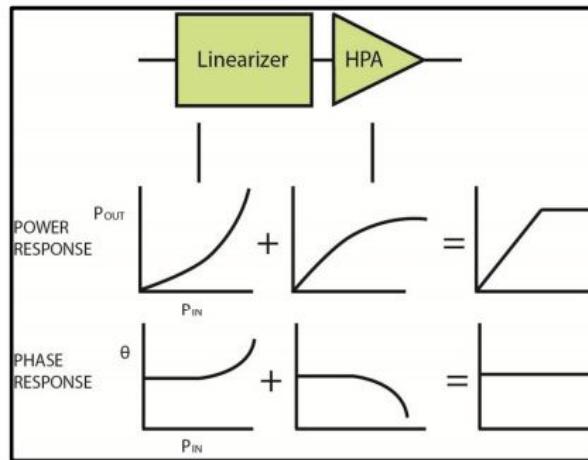

Therefore, an excellent approach for the space navigational application considered would be designing a high efficiency power amplifier at the expense of linearity, then, resolve the conflict of linearity-efficiency by means of using a linearizer to operate linearly as shown in figure 1.1. Note that linearization techniques are out of scope of this project.

Figure 1.1: Linearizer [1]

### 1.3 Scope and objectives

Due to the increasing demand for high efficiency power amplifiers for space applications as highlighted in the previous section, the scope of this thesis is to explore with the nature of SSPAs at L-bands matched in terms of high efficiency, output power and high harmonic rejection while matched to  $50 \Omega$  input and output impedance. Such SSPA is intended for satellite navigation

systems and Mobile Satellite Services (MSS) covered by Galileo Second Generation program.

Taking into account the project scope defined, the following objectives are set and must be satisfied during the development of the project:

1. Research and study of the state of the art of the power amplifier design, where the efficiency enhancement techniques and PA operation classes must be investigated.

2. Learning about the layout design rules and the manufacturing processes as well as the understanding of the electrical models provided by the foundry of each element of the circuit.

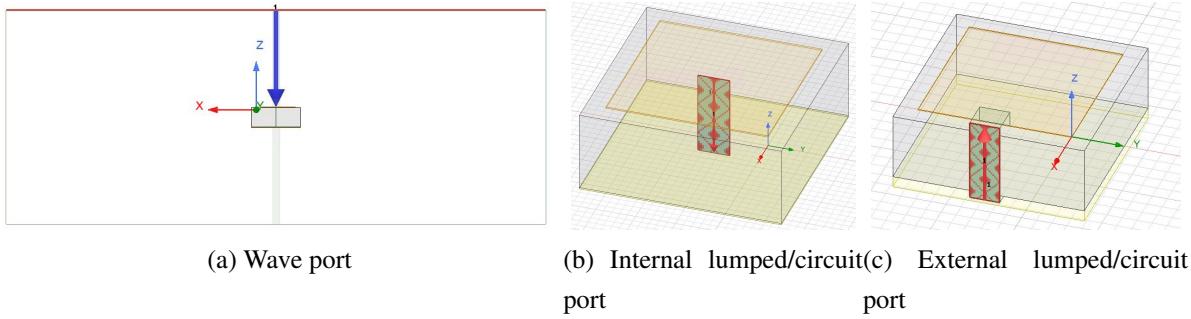

3. 3D and lumped modeling of the parts of the circuit whose electrical models is unavailable using RF/microwave techniques and CAD tools.

4. Reliability Analysis according to ESA and NASA standards.

5. Preparation of manufacturing data (layouts, list of material, etc)

6. Test validation of first prototype in Clean Room using RF instruments.

7. Correlation of measurements and simulation.

8. Preparation of documentation, including design and validation.

In order to achieve these objectives, the Master Thesis here developed describes the procedure from the applied theory to the final SSPA design, prototyping and testing according to an internal specifications defined base on the Galileo Satellite Navigation System requirements and the state of the art of the possible competitors (very important for R+D projects).

## 1.4 Thesis Outline

This thesis is organized in six chapters. The first chapter introduces the project context, motivation, scope/objectives and outline of this thesis. Chapter 2 to 5 contain the main contributions of this research as following:

- **Chapter 2** provides state of the art of power amplifiers. Several aspects such as PAs figures of merit, efficiency enhancements mechanism and PA classes are detailed. Given a general overview of PA fundamentals, definitions and different operation classes.

- **Chapter 3** Describes and presents an SSPA topology design using microstrip technology. General aspects related to the simulations models, microstrip technology and schematic/momentum simulation are detailed in this chapter. Furthermore, given that the thermal management is a critical issue in GaN technology, an general overview about mechanical and thermal management is presented in this chapter.

- **Chapter 4** provides a functional test of the designed SSPA. Small and large signal measurement test bench and results are detailed in this chapter.

- **Chapter 6** provides simulation and measurement results correlation where 3D models of the different parts of the circuit are created to be able to extract the electrical models.

And finally, the document is concluded in chapter 6, summarizing the main results and contributions presented.

# Chapter 2

## State-of-the art

This chapter aims to provide the state of the art of power amplifiers. Several aspects such as PAs figure of merit, efficiency enhancement techniques and PA classes are detailed.

### 2.1 PA figures of merit

Important considerations for RF and microwave power amplifiers are efficiency, power, gain, stability, harmonic distortion, intermodulation distortion, Adjacent Channel Power Ratio (ACPR), Error Vector Magnitude (EVM) and thermal effects.

#### 2.1.1 Power

##### Output/Delivered Power

One of the most important characteristics of PA is the ability to deliver a certain amount of power into the load. The 50 ohms load represents the  $Z_{in}$  of the next stage of the RF system. There are two ways to measure the power, instantaneous power and average power, which are defined as follows:

$$P_{ins} = p(t) = v(t) \cdot i(t) \quad (2.1)$$

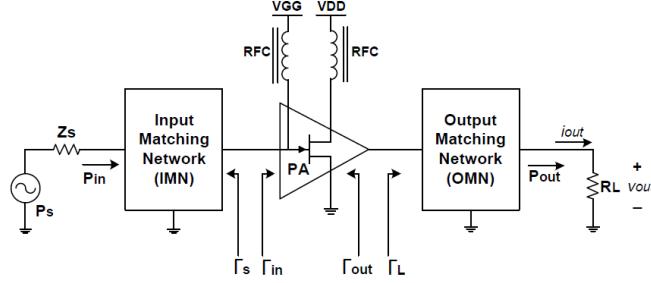

(a) Basic power amplifier diagram [2]

(b) Power flow depiction in a power amplifier [3]

Figure 2.1: PA diagrams

$$P_{avg} = \frac{1}{T} \int_0^T p(t) dt \quad (2.2)$$

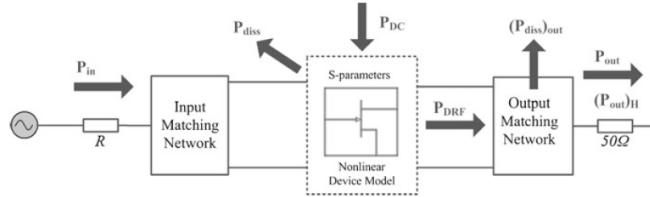

Amplifier's output power is considered to have a linear to its input power until  $P_{1dB}$  (1dB-compression point), which is the power at which output power drops 1dB below its linear expected value (figure 2.2). In addition to  $P_{1dB}$ ,  $P_{3dB}$  is defined as the power where the output power drops 3dB below its linear expected value.  $P_{1dB}$  is used in literature as the point where amplifier starts to be nonlinear, while  $P_{3dB}$  is commonly used in practice to define final stage power in high power amplifiers[2].

## DC Power ( $P_{DC}$ )

It refers to the power used from the power supply in all DC terminals (drain and gate). DC power is calculated as follows:

$$P_{DC}(W) = V_{drain} \cdot I_{drain} + V_{gate} \cdot I_{gate} \quad (2.3)$$

Figure 2.2:  $P_{1dB}$  and  $P_{3dB}$  definition [2]

For the PA in this thesis, Gate DC power can be neglected, since Gate current is intended to be too small ( $I_{gate} \approx 0$ ).

## Input Power

Is the RF power RF power available at the source (or the power delivered by the Previous stage of the RF system), it's used to drive the amplifier.

### 2.1.2 Gain

In lineal scale, Gain is the ratio between output and input power, whereas is their difference in dB scale:

$$G(dB) = 10 \log_{10} \left( \frac{P_{out}(W)}{P_{in}(W)} \right) = P_{out}(dBW) - P_{in}(dBW) \quad (2.4)$$

Gain is constant at low input power and as the input power is increased, the amplifier starts compressing and gain starts decreasing. Hence two gain calculations can be made, and they are used differently.

## Small signal gain

It corresponds to  $|S21|^2$  parameter, and it is often used in signal amplifiers such as Low Noise Amplifiers (LNA) and receiving sections. As it is measured under very low input power (deep back-off) the behavior is linear, and hence cannot be extrapolated for high power amplifiers where compression effects and non-linear parasitics play a key role in amplifier's behavior [2].

## Large signal gain

is obtained with the PA working at higher power, where nonlinear effects such as non-linear capacitances and amplifier saturation take place. At low power levels, the gain is linear, but as power increases the gain decreases. Due to the non-linear behavior, simulation of  $G_p$  should be done by Harmonic Balance [2].

### 2.1.3 Efficiency

The power amplifier is usually the primary consumer of DC power in most hand-held wireless devices, so amplifier efficiency is an important consideration. One measure of amplifier efficiency is the ratio of RF output power to DC input power:

$$\eta = \frac{P_{out}}{P_{dc}} \quad (2.5)$$

This quantity is sometimes referred to as drain efficiency (or collector efficiency). One drawback of this definition is that it does not account for the RF power delivered at the input to the amplifier. Since most power amplifiers have relatively low gains, the efficiency of (2.5) tends to overrate the actual efficiency. A better measure that includes the effect of input power is the power added efficiency, defined as:

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}} = \left(1 - \frac{1}{G}\right) \frac{P_{out}}{P_{dc}} = \left(1 - \frac{1}{G}\right) \eta \quad (2.6)$$

Where  $G$  is the power gain of the amplifier. Power amplifiers are often designed to provide the best efficiency, even if this means that the resulting gain is less than the maximum possible.

### 2.1.4 Stability

Stability is one of the most important factors in the PA that should be considered from the early stage of the design in order to avoid undesired oscillations that would result in signal distortion among others. Oscillations can happen at low frequency or at RF frequency. Low frequency stability is controlled by the bias network (gate and drain) design. However, RF stability depends on the circuit design, for example, in the circuit of figure 2.1a, oscillation is possible if either the input or output port impedance has a negative real part; this would then imply that  $|\Gamma_{in}| > 1$  or  $|\Gamma_{out}| > 1$ . Because  $\gamma_{in}$  and  $\Gamma_{out}$  depend on the source and load matching networks, the stability of the amplifier depends on  $\Gamma_S$  and  $\Gamma_L$  as presented by the matching networks. Thus, we define two types of stability:

- Unconditional stability: The network is unconditionally stable if  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  for all passive source and load impedances (i.e.,  $|\Gamma_S| < 1$  and  $|\Gamma_L| < 1$ ).

- Conditional stability: The network is conditionally stable if  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  only for a certain range of passive source and load impedances. This case is also referred to as potentially unstable.

Note that the stability condition of an amplifier circuit is usually frequency dependent since the input and output matching networks generally depend on frequency. It is therefore possible for an amplifier to be stable at its design frequency but unstable at other frequencies.

### Test for Unconditional Stability

The stability circles discussed in [9] can be used to determine regions for  $\Gamma_S$  and  $\Gamma_L$  where the amplifier circuit will be conditionally stable, but simpler tests can be used to determine unconditional stability. One of these is the **Rollet's condition**, defined as:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} > 1 \quad (2.7)$$

The device will be unconditionally stable if the 2.7 condition is satisfied in conjunction to the auxiliary condition defined as:

$$\Delta = |S_{11}S_{22}| - |S_{12}S_{21}| < 1 \quad (2.8)$$

These two conditions are necessary and sufficient for unconditional stability, and are easily evaluated. If the device scattering parameters do not satisfy the  $K - \Delta$  test, the device is not unconditionally stable, and stability circles must be used to determine if there are values of  $\Gamma_S$  and  $\Gamma_L$  for which the device will be conditionally stable. Also recall that we must have  $|S_{11}| < 1$  and  $|S_{22}| < 1$  if the device is to be unconditionally stable, whereas in unilateral amplifiers ( $S_{12} = 0$ ) fulfilling only  $|S_{11}| < 1$  and  $|S_{22}| < 1$  signify unconditional stability.

Note that K-factor can not be used directly to compare the relative stability of two or more devices, however, a new criterion has been proposed that combines the scattering parameters in a test involving only a single parameter,  $\mu$ , defined as:

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - \Delta S_{11}| + |S_{12}S_{21}|} > 1 \quad (2.9)$$

Thus, if  $\mu > 1$ , the device is unconditionally stable. In addition, it can be said that larger values of  $\mu$  imply greater stability. More details about  $\mu$  factor can be found in [9].

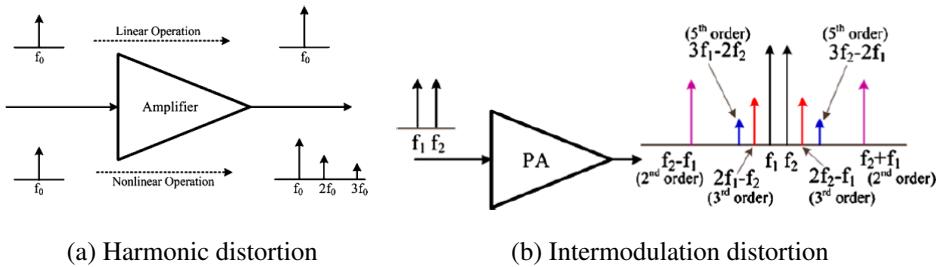

### 2.1.5 Intermodulation and Harmonic Distortion

A power amplifier is a nonlinear system that generates harmonic components in addition to the frequency corresponding to the excitation signal. Intermodulation and harmonic distortions quantify the impact of distortion associated with the harmonic components and provide a measure of linearity performance of a power amplifier.

Harmonic distortion is measured when the amplifier is excited with a single-tone test signal

and harmonic distortion components are generated at the output, as depicted in figure 2.3a. Usually the second and third harmonics carry most of the energy; therefore, the harmonic distortions are defined for these harmonic components.

$$HD_{2,dBc} = 10\log_{10}\left(\frac{P_{out}(2f_0)}{P_{out}(f_0)}\right) \quad (2.10)$$

$$HD_{3,dBc} = 10\log_{10}\left(\frac{P_{out}(3f_0)}{P_{out}(f_0)}\right) \quad (2.11)$$

The harmonic distortions are expressed in dBc relative to the fundamental frequency power. The power level of the harmonics changes with the input power; therefore, the corresponding harmonic distortion figures in dBc change as well.

Figure 2.3: Intermodulation and harmonic distortion [3]

Another harmonic distortion term that is very commonly used is called total harmonic distortion (THD), It includes all the harmonics distortion components in one figure of merit:

$$THD_{dBc} = 10\log_{10}\left(\frac{\sum_{n=2}^{\infty} P_{out}(nf_0)}{P_{out}(f_0)}\right) \quad (2.12)$$

Intermodulation distortion (IMD) is more realistic for the actual wireless communication system. It is the result of two or more signals interacting in a power amplifier to produce additional unwanted signals. For example, the additional unwanted signals (intermodulation products) for two input signals occur at the sum and difference of integer multiples of the original frequencies given by Eq. (2.13) and as depicted in figure 2.3b.

$$IMD_{products} = mf_1 \pm nf_2 \quad (2.13)$$

where m and n are integers and define the order of intermodulation products as a sum of m+n.

As shown in figure 2.3b, 3rd components ( $2f_1 - f_2$  and  $2f_2 - f_1$ ) are the most relevant, as they are very close to the fundamental components, therefore, cannot be easily filtered. Higher order intermodulation products generally do not affect the performance of PAs significantly, as these components either possess very low amplitudes or are far from the fundamental components [3].

Eq. (2.14) corresponds to third-order intermodulation product (IMD3) when the fundamental components  $f_1$  and  $f_2$  are very close.

$$IMD_{3,dBc} = 10\log_{10}\left(\frac{P_{out}(2f_2 - f_1)}{P_{out}(f_2)}\right) \approx 10\log_{10}\left(\frac{P_{out}(2f_1 - f_2)}{P_{out}(f_1)}\right) \quad (2.14)$$

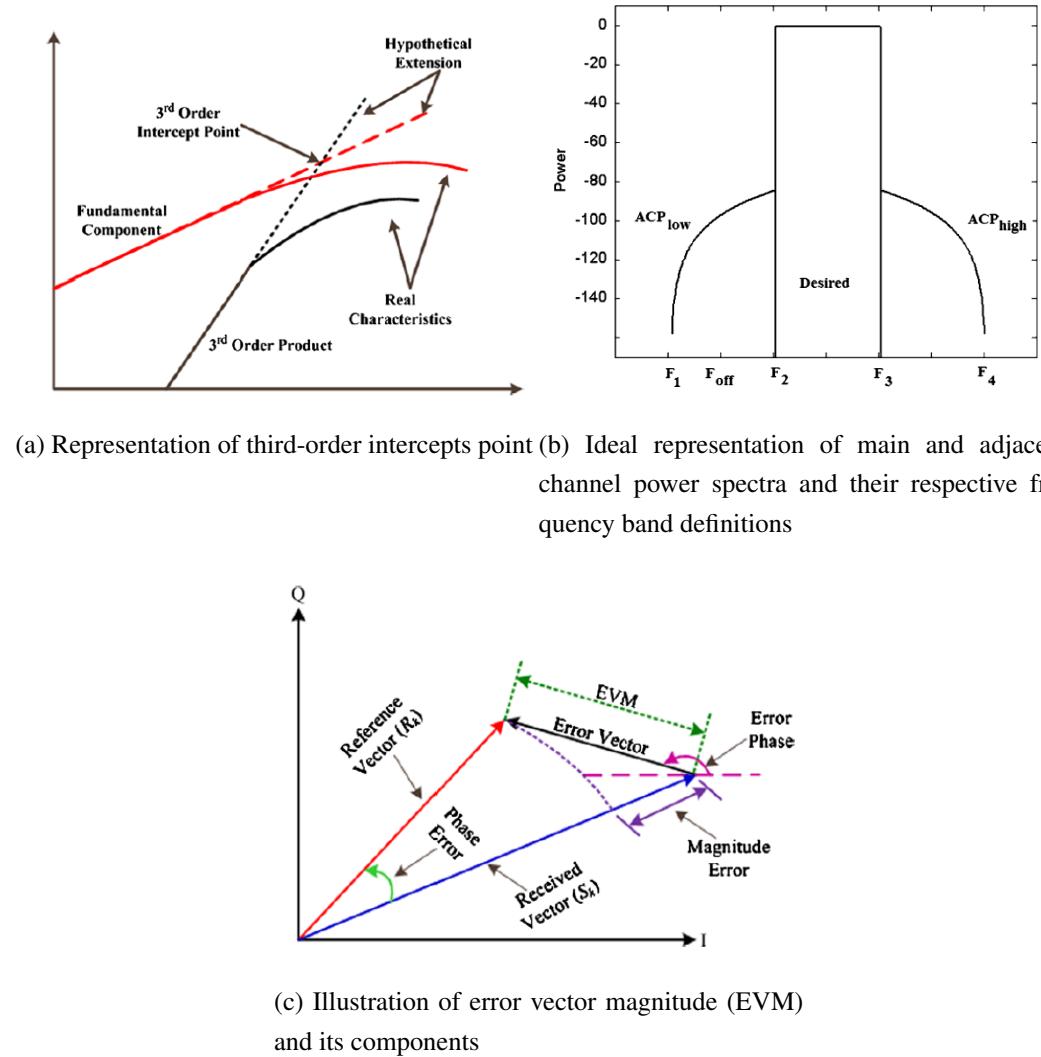

Another metric to describe the linearity performance of a power amplifier is known as the intercept point. For third-order products, it is known as the third-order intercept point (IP3), as shown in figure 2.4a.

It is important to understand that THD, IMD3, and IP3 are good metrics for describing the performance of PAs exhibiting weak memory effects [3]. However, these are insufficient for the situations when the PAs exhibit strong nonlinearity.

## 2.1.6 Adjacent Channel Power Ratio

For amplifiers exhibiting strong nonlinearity or for digitally modulated excitations, adjacent channel power ratio (ACPR) is more relevant considering that harmonic distortion is applicable for single tone excitation and the usefulness of intermodulation distortion is limited to excitations with specified number of tones (usually 2).

ACPR describes the level of spectral regrowth and is often expressed in dB below the main

Figure 2.4: Representation of the figures of merit when a the PA exhibits strong nonlinearity [3]

carrier power (dBc) as depicted in Fig. 1.8 and is expressed as the ratio of the power leaking into the adjacent channel to the power in the main channel given by[3]:

$$ACPR_{dBc} = 10\log_{10}\left(\frac{\int_{F_2}^{F_3} P(F)dF}{\int_{F_1}^{F_2} P(F)dF}\right) \quad (2.15)$$

Figure 2.4b The plot shows a representative power spectrum showing the driving signal (between frequencies  $F_2$  and  $F_3$ ) and the adjacent channel power (ACP) resulting from third order interactions only. In an ideal system, ACPR should be as high as possible as it conveys that the leakage from the main channel to the side channel is low.

### 2.1.7 Error Vector Magnitude

According to 3GPP standards, EVM is a measure of the difference between the reference waveform and the measured waveform [3]. The difference is called error vector, illustrated in figure 2.4c, and the EVM, usually mentioned in percentage, is defined as the square root of the ratio of the mean error vector power to the mean reference power expressed as:

$$EVM_{RMS} = \sqrt{\frac{\sum_{k \in K} |S_k - R_k|^2}{\sum_{k \in K} |R_k|^2}} \quad (2.16)$$

where  $S_k$  is the received (measured) vector,  $R_k$  is the reference symbol vector, and  $K$  is the total number of symbols.

The ACPR provides information about the out-of-band distortion, the error vector magnitude (EVM) estimates the in-band distortion caused by the amplifier nonlinearities. EVM possesses a direct relation with the signal to noise ratio and can be used to determine the physical error introduced at different stages of communication system and thus serves as an easily tool for designers in troubleshooting specific problems.

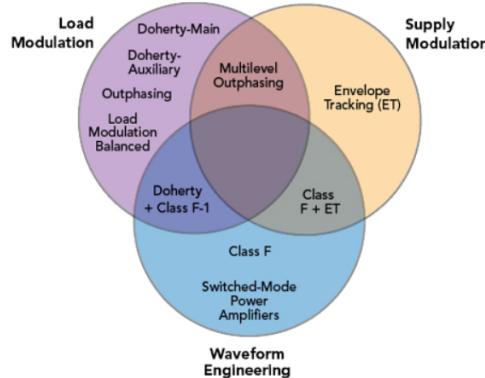

## 2.2 PA classes

Before introducing the different power amplifier classes, as this this thesis is focused in the energy efficiency, let's take a look on some efficiency enhancement mechanisms. The point is, how will efficiency enhancement mechanisms improve the energy efficiency? The following classifications is done in [4] in order to reduce the wasted power in power amplifiers:

**Waveform Engineering** - The shape of the voltage and/or current waveform is modified, which is what happens when passing through the class A to C continuum. Harmonic content is introduced into the current, modifying its waveform, in a predictable but restricted way. Alternatively, the ratio of the current's harmonic content may be modified by injecting harmonics from either the input side or output side. For the current's harmonic content to affect the voltage waveform, a non-zero impedance must be present at that harmonic frequency. In the limiting

case, both current and voltage waveforms are square waves and antiphase. As one of them is zero at any instant in time, the power dissipation is zero. This zero dissipation applies at least to the device, but it could just be shifted elsewhere in the system.

**Supply Modulation** - The average or envelope supply voltage across the device,  $V_{supply}$ , is modified. With a perfect device,  $V_{supply}$  is the root-mean-square value of the voltage waveform, set so the minimum value of  $v_d$  reaches zero

**Load Modulation** - The  $Z_{load}$  presented to the device at the fundamental frequency is modified, ideally so the voltage ( $v_d$ ) swings from 0 to 2 times the supply.

Popular enhancement methods according to the mechanisms they use, are depicted in figure 2.5, using a Venn diagram for classification helps identify where additional schemes are complementary and may further improve efficiency. Once the different mechanisms are presented, different classes based on waveform engineering will be discussed, since the PA design of this thesis is based on the waveform engineering efficiency enhancement.

Figure 2.5: Efficiency enhancement mechanisms their hybrids and possible areas for further improvement [4]

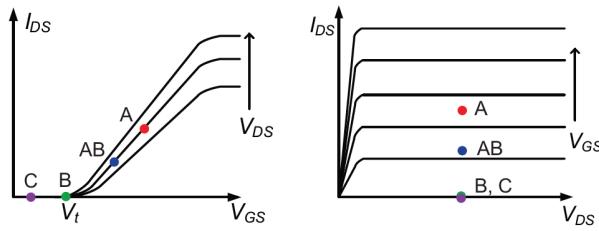

The PAs are classified into several operation classes depending on different voltage and current waveforms. These classes can be categorized into two major groups [5]. The first group is known as transconductance PAs, in which case the transistor, i.e., field effect transistor (FET), is considered as a current source controlled by the gate voltage. The second group is called high-efficiency PAs, including switch-mode, such as the class-E and D, and harmonically tuned ones such as class-F.

### 2.2.1 Transconductance Power amplifiers

For transconductance PAs, the most critical parameter is the transistor gate bias that sets the operating point for the device, which typically determines the class or conduction angle of the operation, i.e., Class A, AB, B, and C (the conduction angle,  $\theta$ , is defined as the number of degrees in a full RF duty-cycle that current flows). Figure 2.6 illustrates various bias condition of these PA's, and figure 2.7 illustrates they drain voltage waveform [5].

Figure 2.6: Various DC bias points of Class-A,AB,B and C [5]

Figure 2.7: Voltage and current waveform [5]

Class A operates in full input and output ranges ( $\theta=360^\circ$ ) where the current waveform has no clipping or distortion, which makes it perfect operation for an amplitude-modulated signals. However, it requires a high quiescent current ( $= \frac{I_{max}}{2}$ ) and delivers a maximum efficiency of 50%. The quiescent current of the transistor can be reduced to below  $I_{max}/\pi$  by decreasing the gate bias voltage to the threshold point, resulting in a Class-B operation. Thus, the conduction angle is reduced to  $180^\circ$ , which means for a certain fraction of the signal period, the transistor is in complete cut off. Therefore, compared to Class-A, Class-B operation is more efficient, but it is less linear due to its half-sinusoidal current-waveform that contains high-order harmonics

and generates inherent non-linearity. If both linearity and efficiency are both concerned, a better option is to operate the amplifier between the class-A and class-B region to alleviate linearity issues while still having better efficiency than Class-A. Such an operation is called Class-AB, which is often used in the applications that require a good trade-off between linearity and efficiency. If the transistor operates for less than half of the cycle or with the conduction angle smaller than  $180^\circ$ , it results in the Class-C operation. This mode is highly efficient and non-linear, and thus it is mostly used for amplifying constant-envelope signals that only use phase and frequency to convey data. To sum up, the bias point determines the amplifier performance in terms of gain, power, and efficiency.

## 2.2.2 High Efficiency Power amplifiers

High-efficiency PAs, such as Class-E, Class-F, their duals, in theory can deliver a 100% efficiency since they are not dissipating any power internally. However, the linearity of these PAs is very poor due to the switching operation of the transistor. This group of amplifiers can be further divided into two subgroups: a) harmonic-tuned PAs, e.g., Class-F, class  $F^{-1}$  and saturated PA, and b) switching-mode PAs, e.g., E and D. Unlike the transconductance PAs, the design of high-efficiency PAs usually require harmonic impedance matching as well as the fundamental one. Hence designing this kind of amplifiers has been a challenge for designers, in part due to poor control of harmonic load impedances.

### 2.2.2.1 Switch-mode PAs

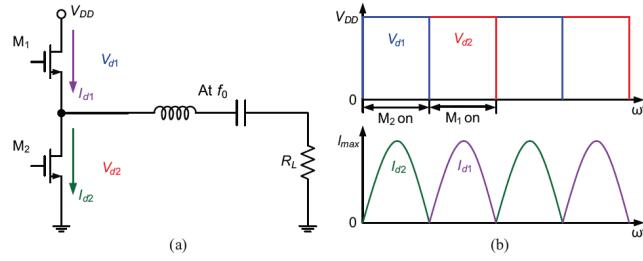

The **Class-D** PA shown in figure 2.8 involves two transistors to switch between, resulting in a square waveform across the switch without the coexistence of current. Each switch conducts a half sinusoidal wave that is combined to form a full sinusoidal wave via the series LC resonator. Class-D is normally used in the low-frequency range ( $< 100$  MHz) where the parasitic effect is nearly negligible.

Another switch-mode PA, **Class-E**, uses a single transistor to switch the current flows through itself and the output capacitor ( $C_p$ ), as shown in Fig. 2.9 [5]. It can be seen that

Figure 2.8: Voltage-mode Class-D PA: (a) simplified circuit schematic, (b) voltage and current waveforms [5]

the current and voltage waveforms are slightly out-of-phase, requiring a inductive load. The Class-E PA can operate at a higher frequency (giga-hertz level), as it is insensitive to parasitics since the parasitic capacitance of the transistor ( $C_{DS}$ ) can be completely absorbed into  $C_p$ . More details about switch-mode PAs can be found in [5, 10].

Figure 2.9: Class-E PA: (a) simplified circuit schematic, (b) voltage and current waveforms [5]

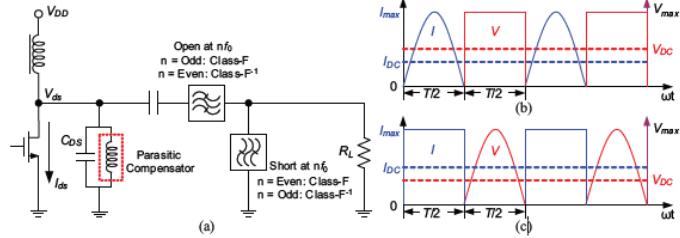

### 2.2.2.2 Harmonic-tuned PAs

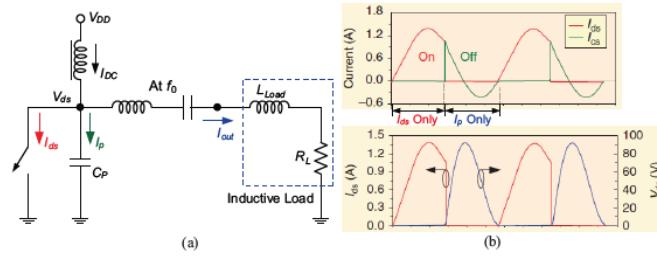

#### Class F and $F^{-1}$ PA

Figure 2.10 [5] shows the circuit schematics of Class-F and inverse Class-F PAs. By providing open-circuit and short-circuit at odd and even harmonic frequencies, the ideal Class-F PA exhibits a half-rectified sinusoidal current and rectangular voltage at the drain node, as shown in Fig. 2.10(b). There is no power dissipation in the device due to non-overlapping between voltage and current, yielding 100% efficiency. The Class- $F^{-1}$  is the dual of Class-F, where the current and voltage waveforms are exchanged as are the harmonic loads, as shown in Fig.

2.10(c).

Figure 2.10: Frequency-domain high-efficiency PAs (Class-F and Class-F<sup>-1</sup>): (a) simplified circuit schematic, and voltage and current waveforms of (b) Class-F and (c) Class-F<sup>-1</sup> PAs.

### Class F and F<sup>-1</sup> PA Theory

The standard Class-F PA is developed from the Class-B PA mode by loading the active device output with proper terminations at its fundamental and harmonic frequencies [5, 10]. The half-sinusoidal current waveform, formed by the Class-B bias condition, has the following expression:

$$i_F(\theta) = I_{peak} \cos(\theta) \quad \frac{-\pi}{2} < \theta < \frac{\pi}{2} \\ = 0 \quad -\pi < \theta \leq \frac{-\pi}{2}, \frac{\pi}{2} \leq \theta \leq \pi \quad (2.17)$$

The above equation can be expressed using Fourier series (normalized to  $I_{peak}$ ), given by [5]:

$$i_F(\theta) = \frac{1}{\pi} + \frac{1}{2} \cos(\theta) + \frac{2}{3\pi} \cos(2\theta) - \frac{2}{15\pi} \cos(4\pi) + \dots \quad (2.18)$$

The output matching network (filter) is required to provide open-circuit terminations at odd harmonics and short-circuit terminations at even harmonics, as shown in figure 2.10. Thus, a square voltage waveform is shaped which has no overlap with the half-sinusoidal current, leading to a theoretical 100% efficiency. In practice, harmonic control is usually conducted up to the third order, as further harmonic control yields limited efficiency improvement but

significantly increased implementation difficulty. Thus, the normalized voltage waveform of a Class-F PA with a finite number of harmonic terminations can be expressed as [5]:

$$v_F(\theta) = 1 - \frac{2}{\sqrt{3}}\cos(\theta) + \frac{1}{3\sqrt{3}}\cos(3\theta). \quad (2.19)$$

The above equation is able to deliver a 90.7% efficiency at the maximum power level.

Inverse Class-F PA mode is the dual of Class-F mode. It exploits dual harmonic loading conditions with open-circuit even-harmonic loads and short-circuit odd-harmonic loads, as shown in figure 2.10. This forms a square-wave current and half-sinusoidal-wave voltage, which can also lead to a theoretical 100% efficiency. In the practical case of controlling three harmonics, the voltage waveform is shaped by second-harmonic peaking [5]:

$$v_{F^{-1}} = 1 + \frac{2}{\sqrt{2}}\cos(\theta) + \frac{1}{2}\cos(2\theta) \quad (2.20)$$

while the current waveform takes the form of:

$$i_{F^{-1}} = i_{DC} - i_1\cos(\theta) + i_3\cos(3\theta) \quad (2.21)$$

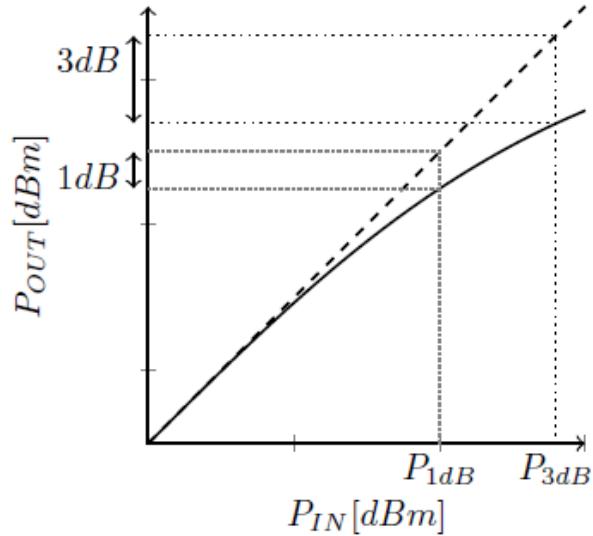

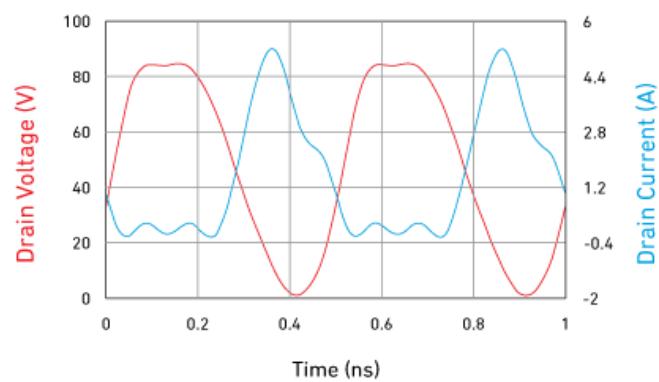

where  $i_{DC} = 0.37$ ,  $i_1 = 0.43$ , and  $i_3 = 0.06$  [5]. Note that the voltage and current waveforms of the standard class F and F-1 where finite harmonic are considered (up to third harmonic) aren't the perfect half sinusoidal and the rectangular waveforms as shown in figure 2.10, but they are quasi-rectangular and quasi-half-sinusoidal waveforms. Figure 2.11 shows an example for a class F.

Figure 2.11: Class F waveforms considering finite harmonics (up to third harmonic)

# Chapter 3

## SSPA design using Power Bar

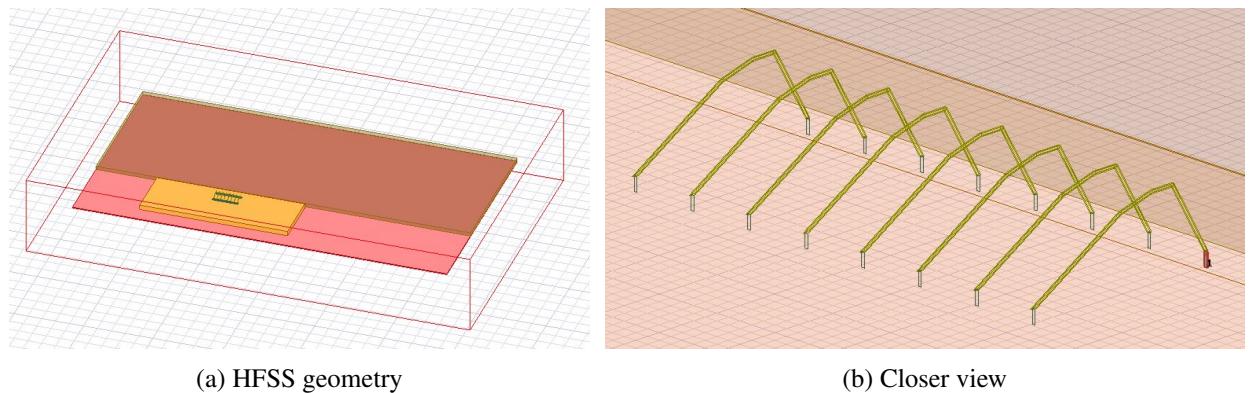

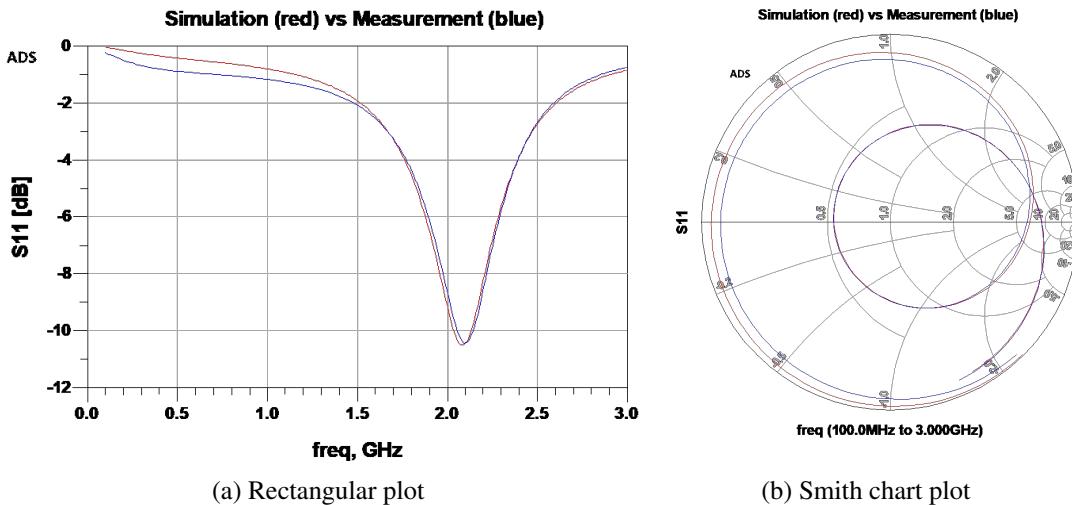

The aim of this chapter is to introduce the design flow of SSPAs that minimizes uncertainties using a bare die model. The bare die model is 85W Gallium Nitride High Electron Mobility Transistor which offers a general purpose and broadband solution for variety of RF applications such as radar and telecommunications. The circuit is manufactured on a  $0.25\mu\text{m}$  gate length GaN HEMT technology on SiC substrate. It is proposed in a bare die form and requires an external matching circuitry.

### 3.1 Mechanical and Thermal Design

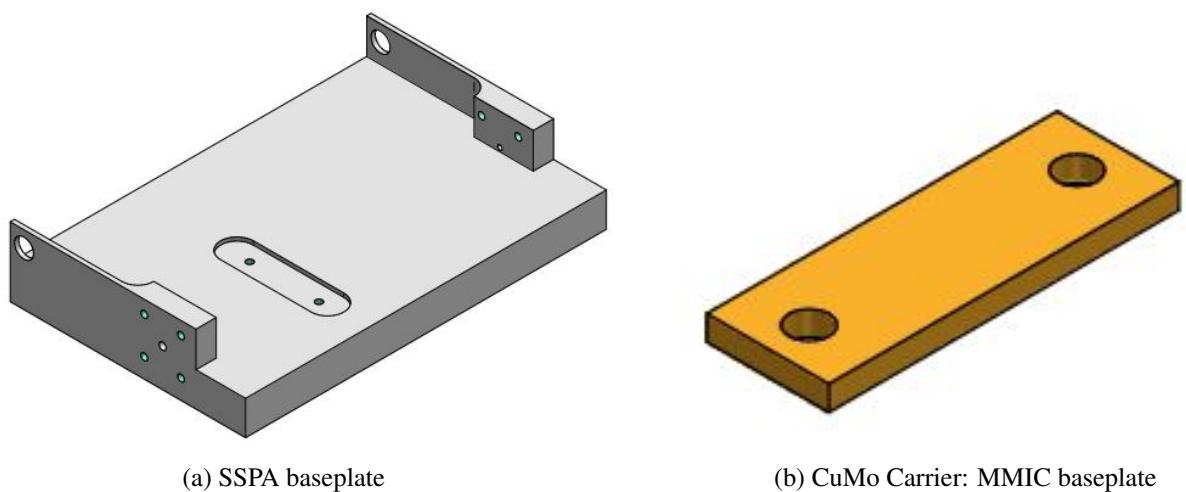

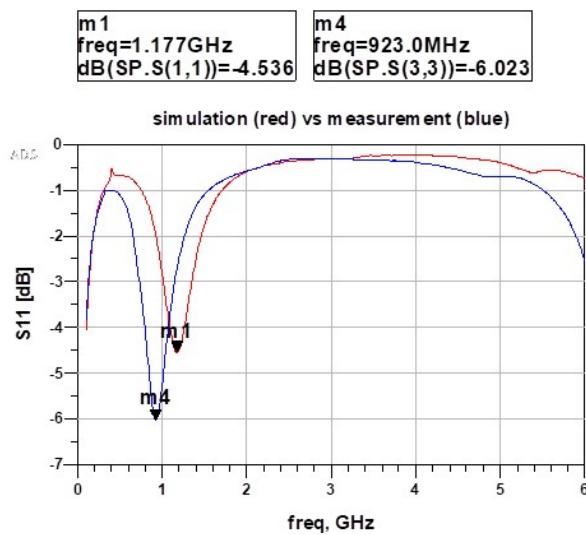

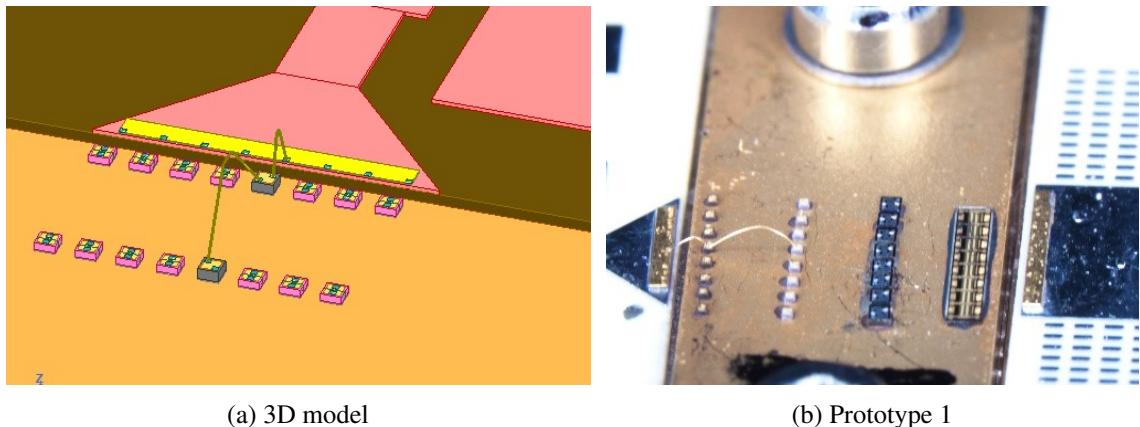

Even though the mechanical and thermal design is out of scope of this thesis, it has been considered by mechanical engineers in parallel with electrical design considered in scope of this thesis in order to overcome successfully the challenges cited in chapter 1. Figure 3.1b shows the 3D view of the SSPA prototype baseplate where the input and output network substrates will be mounted together with MMIC baseplate (Carrier) shown in figure 3.1a which will carry the MMIC power transistor together with its pre-matching network. The mentioned input, output and pre-matching network will be explained in the electrical design section.

As explained in chapter 1, the high power density in GaN semiconductors presents a major thermal management challenge. Pulling the heat away from the active region of the device is critical to maximizing the output power and reliability. Starting with the bare die, proper

thermal management requires an optimal die attach process. Since even a small increase in thermal resistance results in a significant temperature rise, use of a high thermal conductivity material for die attach is critical [1].

For example, using a gold-tin eutectic or Namics die attach process provides much better thermal conductivity than silver epoxy. However, achieving good die attach with high thermal conductivity requires more than simply choosing the correct material. The process must be carefully controlled. Since even small air voids under the die can greatly increase thermal resistance (creating hot spots), they must be minimized, which requires experience, careful process control and techniques such as performing die attach in a vacuum [1].

The thermal conductivity of the baseplate material holding the die (figure 3.1a) must also be maximized. For lower power applications, die is often installed on a Kovar baseplate, chosen because of its matched coefficient of thermal expansion (CTE). However, when thermal conduction is critical like in this case, a material such as copper molybdenum (CuMo) is a better choice.

The process of choosing materials to optimize the thermal conductivity of each interface continues through the entire design, i.e, from the MMIC to MMIC baseplate (figure 3.1a), then, from MMIC baseplate to SSPA baseplate (figure 3.1b) and so on. While this thermal design approach is used for GaN amplifier designs regardless of application, it is particularly important for space-qualified hardware. The size and weight constraints common to space programs increase power density by limiting the volume, while the reliability requirements for space operation require maximum cooling of the active devices [1].

## 3.2 Electrical design

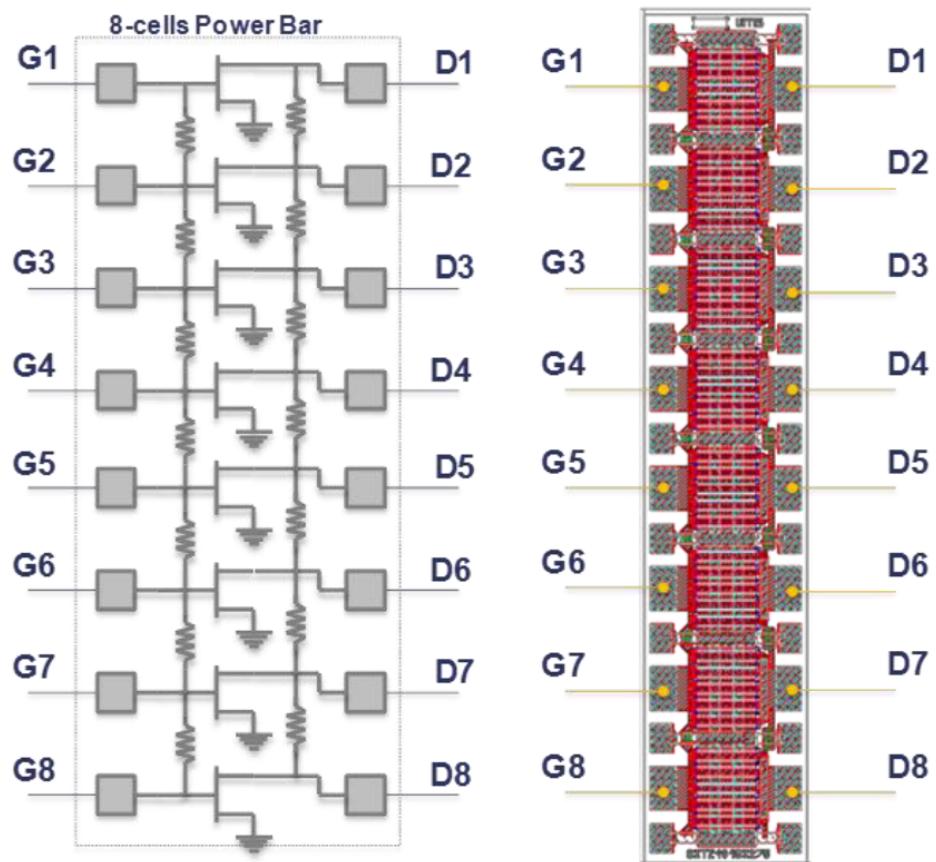

### 3.2.1 8-cells Power Bar Description

The device is composed of 8x11W elementary cells. These cells are connected together with a specific network providing a good trad-off between performance and stability (resistance between gates and drains as described on figure 3.2). The reference planes are on the center of the

Figure 3.1: Baseplate 3D view

bonding pads.

Figure 3.2: Power Bar configuration

### Elementary Cell Maximum Gain and stability characteristics

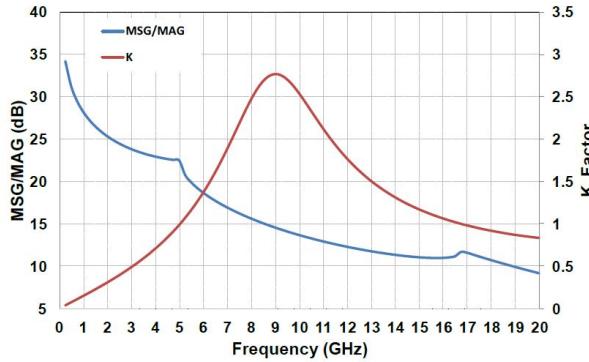

Figure 3.3 shows Maximum Gain and stability simulated performance available on datasheet considering  $T_{ref}=+25^{\circ}\text{C}$ ,  $V_{DS} = +30\text{V}$ ,  $I_{DQ} = 140\text{mA}$ .

Figure 3.3: Maximum Gain and stability simulated performance

### Elementary Cell Load Pull Performance

Table depicted in figure 3.4 shows the load pull simulated performance available on datasheet considering  $T_{ref}=+25^{\circ}\text{C}$ ,  $V_{DS} = +30\text{V}$ ,  $I_{DQ} = 140\text{mA}$ . The impedances are chosen as a trade-off between Output Power, PAE and Stability of the device.

| Frequency (GHz) | $Z_s$       | $Z_l$       | Gain (dB) @PAE <sub>max</sub> | Pout (W) @PAE <sub>max</sub> | PAE <sub>max</sub> (%) | Pout <sub>max</sub> (W) |

|-----------------|-------------|-------------|-------------------------------|------------------------------|------------------------|-------------------------|

| 1               | 11.6+ j28.4 | 51+ j20.3   | 16                            | 12.5                         | 75                     | 13.2                    |

| 3               | 2.2+ j11    | 23.8+ j27.1 | 16                            | 11.4                         | 72                     | 12.4                    |

| 5               | 1.3+ j5.5   | 11.4+ j20.7 | 15                            | 11.3                         | 69                     | 12.3                    |

| 7               | 1.5+ j2.9   | 8.7+ j15.4  | 11.5                          | 11.2                         | 63                     | 12                      |

| 8               | 1.3+ j1.6   | 5.4+ j13.4  | 10                            | 10.5                         | 62                     | 11                      |

Figure 3.4: Elementary Cell Load Pull Performance

### 3.2.2 Biasing procedure

As explained in the previous chapter, bias point sets the class mode operation. In this case, bias point provided by the datasheet is selected ( $V_{DS} = 30\text{V}$  and  $I_{DQ} = 140\text{mA}$  for a single unit

cell) which corresponds to class-AB operation. In order to set the biasing point, the following procedure is recommended:

1. Bias power bar gate voltage at  $V_g$  close to  $V_{pinch-off}$  (typically:  $V_{GS} = -5V$ )

2. Apply  $V_{DS}$  bias voltage.

3. Increase  $V_{GS}$  up to quiescent bias drain current  $I_{D_Q}$ .

### 3.2.3 Optimal load and source impedance extraction

Given that the biasing point provided by the datasheet is selected, optimal source and load impedance of the fundamental tone provided by the datasheet are used since they are extracted under same biasing condition. Therefore, the initial step would be running an Harmonic balance simulation using the simplest schematic as shown in figure 3.5 to be able to compare the obtained and datasheet performance.

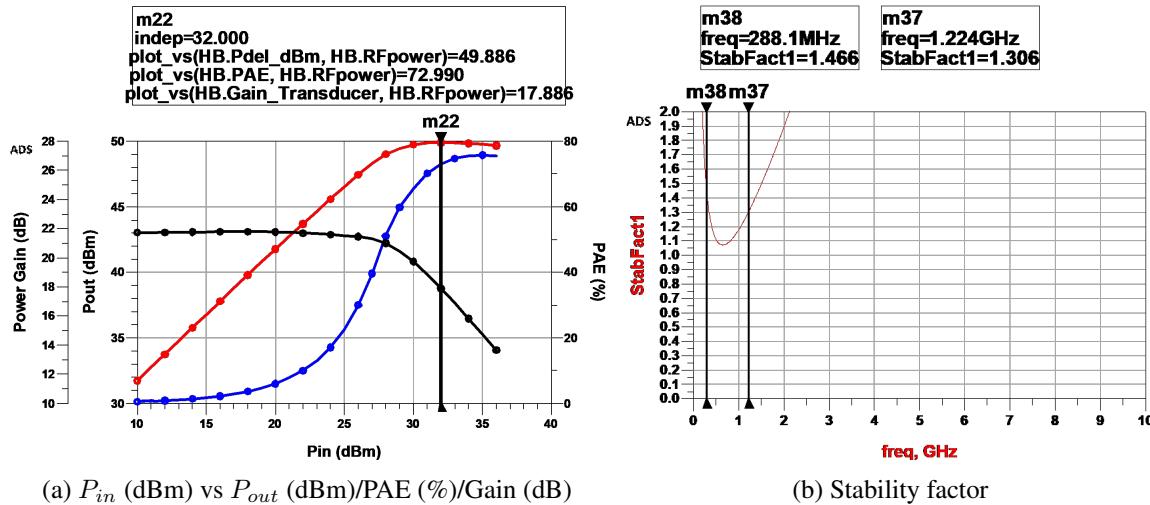

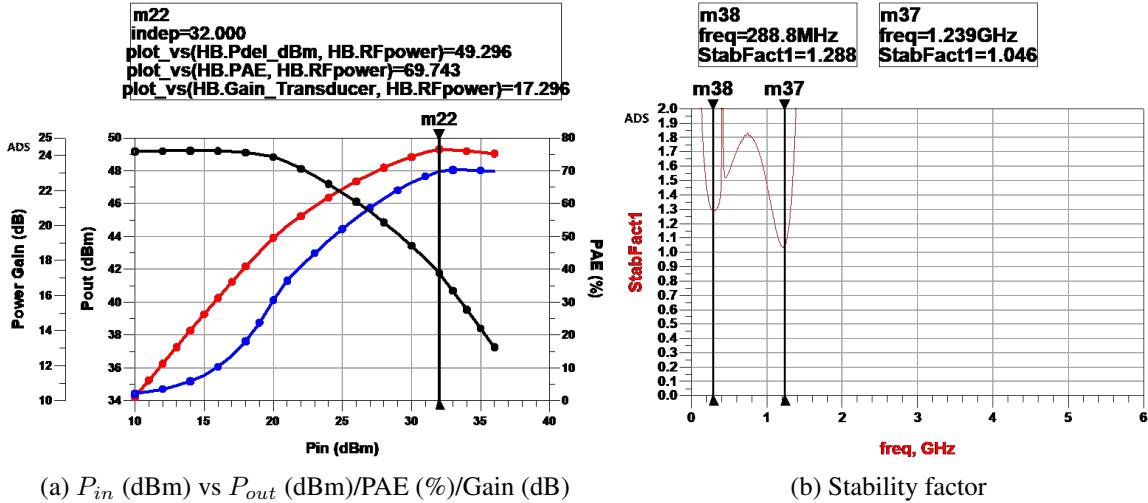

Harmonic balance simulation results are depicted in figure 3.6, achieving 49.9 dBm output power, 17.9 dB gain and 69.12% Power Added Efficiency (PAE). To achieve higher PAE levels, harmonic loading should be considered in order to mitigate the power carried by second and third harmonics. To do so, Load Pull simulation should be performed in order to find the optimum harmonic loads.

Harmonic Load pull has been performed using the template provided by Advanced Design System (ADS). Once the optimum harmonic loads have been obtained, Harmonic Balance simulation is carried out again using the simplest schematic presented previously in figure 3.5. The obtained results are shown in figure 3.7, observe that when harmonics power is absorbed properly, such power is added to the fundamental tone which leads to an improvement in  $P_{out}$ , Gain and PAE as depicted in table 3.1.

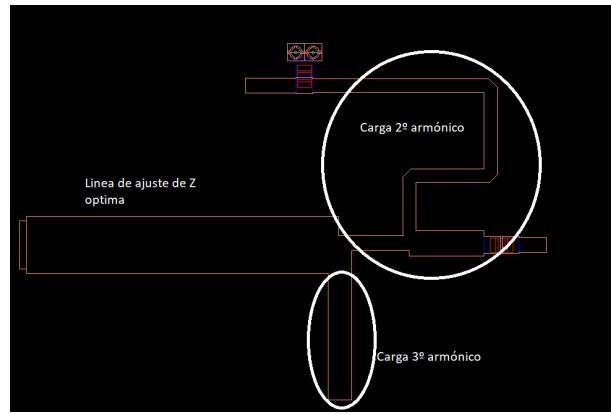

Figure 3.5: Harmonic Balance Simulation schematic

Figure 3.6: Harmonic Balance Simulation performance

Figure 3.7: Harmonic Balance Simulation performance using Harmonic Loads

|                                          | PAE (%) | $P_{out}$ (dBm) | Gain (dB) |

|------------------------------------------|---------|-----------------|-----------|

| Ideal Schematic:<br>Non-Harmonic Loading | 69      | 49.9            | 17.9      |

| Ideal Schematic:<br>Harmonic Loading     | 74      | 50.4            | 18.3      |

Table 3.1: Harmonic Balance simulated performance

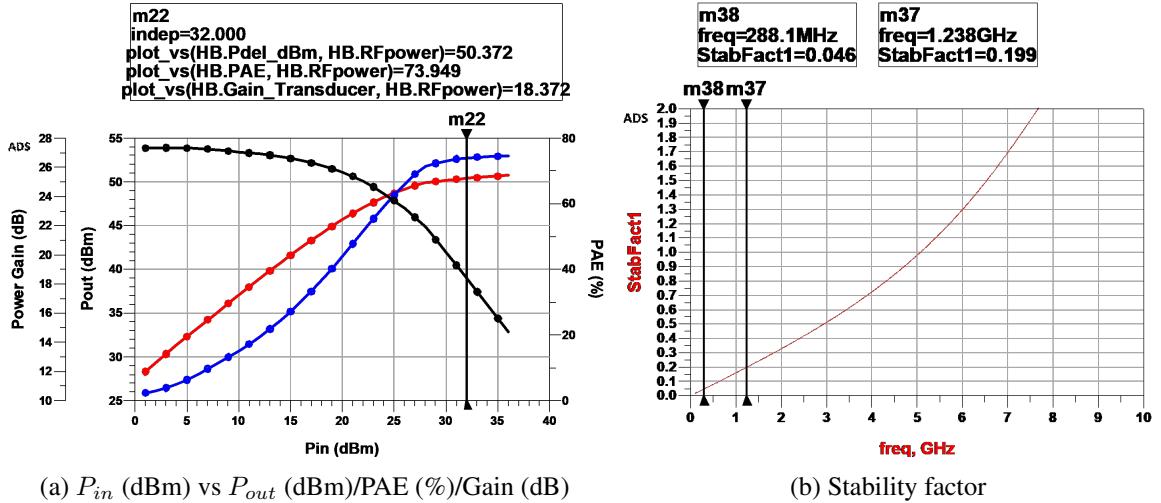

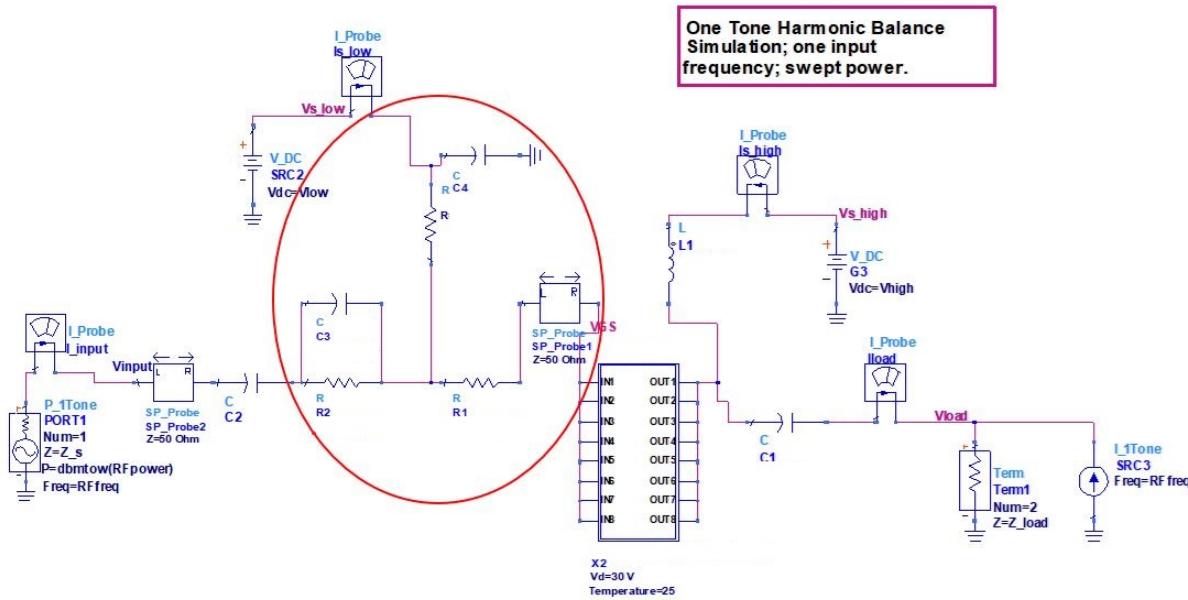

### 3.2.4 Stability Network Design

At this point, having obtained the optimal impedances, it is time design the stability network in order to achieve Stability factor higher than unity at lower and design frequencies. Depending on the working frequency and transistor mode, different stability network typologies could be considered. In this case, the designed topology is shown in figure 3.8. The parallel RC (Resistor, Capacitor) plus the series Resistor placed on the RF path control the stability at higher frequencies while the elements placed on the bias network control the stability at lower frequencies.

Having included the stability network, Harmonic Balance simulation is carried out and results shown in figure 3.9 are obtained. Observe that stability factor higher than unity is achieved

Figure 3.8: Harmonic Balance Simulation schematic including stability network

in broadband frequency range.

Figure 3.9: Harmonic Balance Simulation performance including stability network

### 3.2.5 Pre-matching network design

Now, the next step is to design the pre-matching network and add it to previous simulation, then, re-adjust it to maintain the previous obtained performance. Pre-matching network is usually

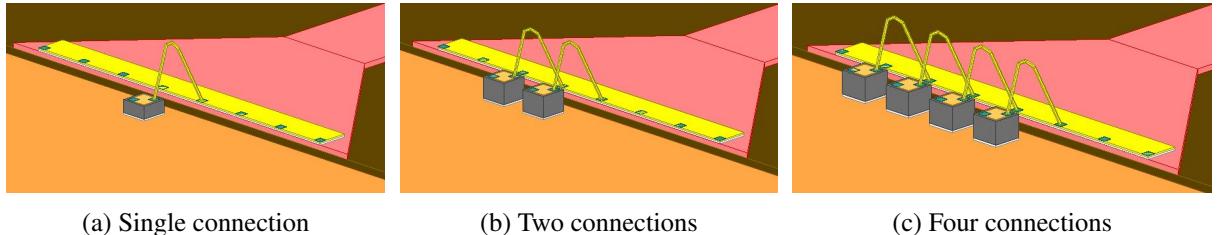

used in power transistors package (in this case, in the carrier) to convert the MMIC gate low impedance to a higher impedance which can be matched to the source impedance by means of an external input matching network. Pre-matching network is the combination of bonding wires (inductors) + capacitors.

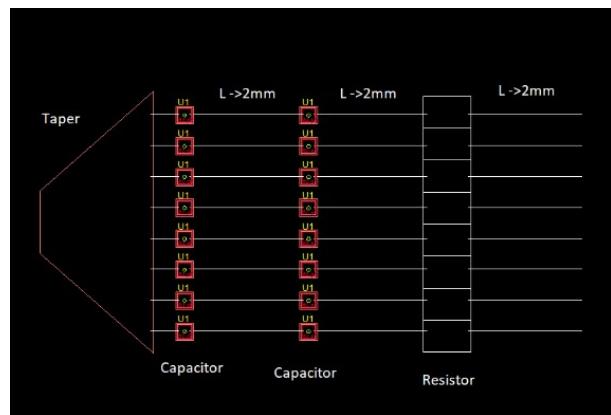

It must be taken into account that in the the taper + pre-matching network ( $R + L + C$ ), is the set of elements that must be adjusted to obtain the optimal impedance to the input of the transistor, since the stability network will have a fixed impedance marked by the elements that compose it which can not be modified since they are necessary to stabilize the SSPA. Figure 3.10 shows the designed Taper and Carrier pre-matching Network, it is composed by Resistors (used to stabilize) + Inductors + Capacitors where Inductors are modeling bonding wires to be used in practice.

Figure 3.10: Pre-matching Network

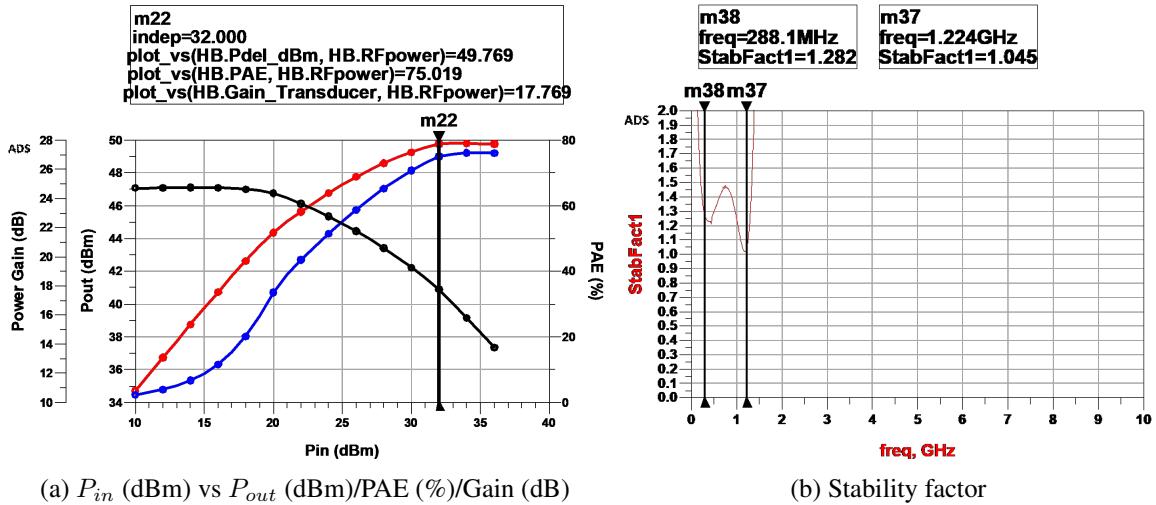

Once the pre-matching is designed and taper is modeled in momentum together with stability network, Harmonic Balance simulation is carried out and results shown in figure 3.11 are obtained where it can be seen that the previous performance is maintained as required.

### 3.2.6 Input Matching Network Design

Once the Taper and stability network are designed, the next step is to measure the input impedance at beginning of the stability network as the reference point. In this case,  $Z_{in} = 15.5 + j16$  is measured at established reference point, therefore, a matching network should

Figure 3.11: Harmonic Balance Simulation performance including stability network + Taper

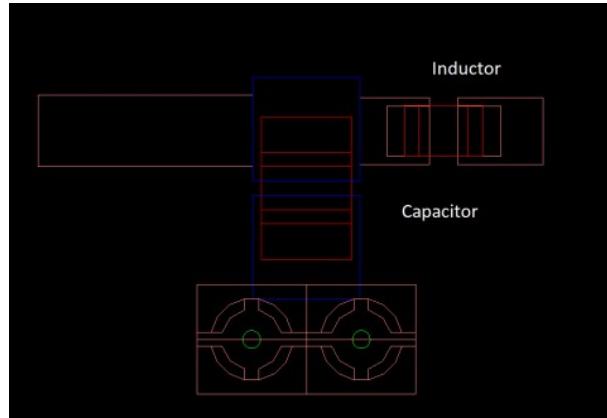

be designed in order to convert such impedance into  $Z_{in} = Z_0 = 50\Omega$ . Figure 3.12 shows the proposed matching network, a series Inductor + shunt Capacitor.

Figure 3.12: Input Matching Network

At this point, the designed input matching network must be incorporated to the entire input network of the SSPA and simulate it in momentum. Then, perform Harmonic Balance simulation to verify whether the designed input matching network is working properly or not. In this case, similar results to the ones shown previously in figure 3.11 are obtained.

### 3.2.7 Output Matching Network

In this subsection, a matching network able to match fundamental, second and third harmonic frequencies will be presented based on [11]. Initially, second and third harmonic loads extracted in load pull simulation will be synthesized by means of shunt stubs as shown in figure 3.13. Then, fundamental frequency matching must be considered by means of adjusting the entire topology.

Figure 3.13: Output Matching Network

The presented topology have been designed using passive S-parameters simulation to assure that the input impedance seen from the transistor side corresponds to the impedance given by the datasheet at fundamental frequency and to the loadpull extracted impedances at harmonic frequencies. In order to verify its functionality, it is incorporated to the Harmonic Balance simulation setup and the results obtained are shown in figure 3.14.

At this point, the SSPA design could be closed, however, before doing so, part stress and derating analysis should be performed in order to verify if the different components (mainly at the input network) withstand the power or current flowing through them. Such analysis will be detailed in the following subsection.

### 3.2.8 Part Stress and Derating Analysis

Part stress analysis is based on placing two probes at the border of the component to be analyzed to be able calculate the power and current at the simulation level. Once these values

Figure 3.14: Harmonic Balance Simulation performance including input and output networks

are determined, component power and current handling must be checked on datasheet to verify how much power/current is able to withstand. Apart of complying with the analyzed value, it is necessary to leave a margin (derating) stipulated by the ECCS standard, i.e, if a 0.1 A RF and 90mA DC current are measured on a  $50\Omega$ , that is 0.9W, a minimum margin of 1.8W must be kept.

Having said that, part stress analysis of the input network components has been performed, mainly the stability network resistors presented previously in figure 3.8, and the corresponding layout is presented in figure 3.15. Observe that instead of using a single Resistors value in the stability network as in figure 3.8, several Resistors have been arranged in parallel to achieve the desired value, this is done to withstand the power/current and to comply with ECCS standard derating values. Performing such modifications in the input network layout may produce some changes on the performance, therefore, possible adjustments of the input network may be required.

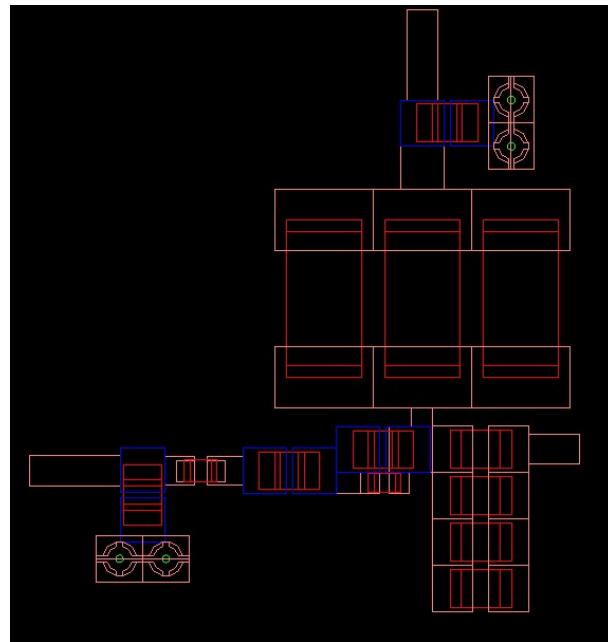

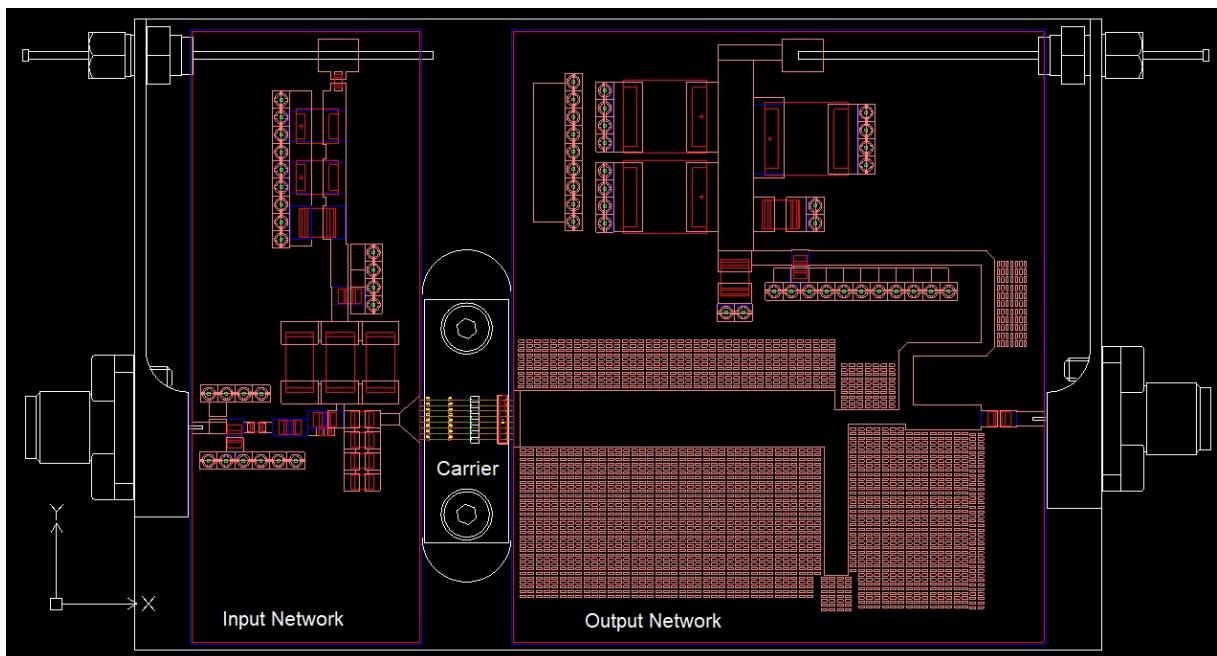

### 3.2.9 SSPA full layout

Figure 3.16 shows the SSPA full layout as the result of joining all the parts described in the previous subsections: input network, carrier (pre-matching network + MMIC) and output network.

Figure 3.15: Input network considering Resistors deratings

Figure 3.16: SSPA full layout

Such layout have been simulated and optimized to achieve a quite similar performance to the one obtained previously in figure 3.14 where the full design was simulated without taking into account the part stress and derating analysis. Table 3.2 illustrates a summary of the full layout and initial obtained performance, observe that the full layout design achieves 49.2 dBm output

power, 17.3 dB gain and 69.12 % Power Added Efficiency.

|                                          | PAE (%) | $P_{out}$ (dBm) | Gain(dB) |

|------------------------------------------|---------|-----------------|----------|

| Ideal Schematic:<br>Non-Harmonic Loading | 69      | 49.9            | 17.9     |

| Ideal Schematic:<br>Harmonic Loading     | 74      | 50.4            | 18.3     |

| Full Layout                              | 69,7    | 49,2            | 17,3     |

Table 3.2: Harmonic Balance simulated performance summary

# Chapter 4

## SSPA Functional Test

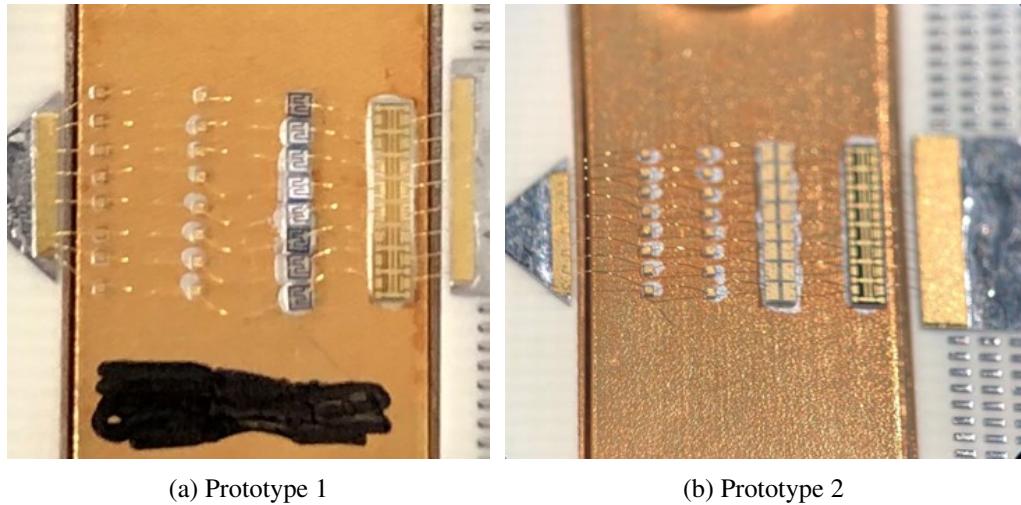

This chapter aims to present the functional test of two prototypes. Such prototypes are mounted and tested at ambient temperature under small and large signal conditions.

### 4.1 Prototype 1

The mounted prototype 1 is shown in figure 4.1, observe that it is composed by an input network (left), output network (right) and the carrier where the MMIC power transistor is mounted together with its internal matching network. Components mounted on the carrier are interconnected using wire bonding technology.

#### 4.1.1 Small signal measurement

To be able to perform small signal measurement, it is necessary to bias the transistor previously. To do so, the following biasing procedure is proposed:

1. Bias power gate voltage at  $V_g$  close to  $V_{pinch-off}$ : typically:  $V_{GS} = -5V$

2. Apply  $V_{DS}$  bias voltage (Typically:  $V_{DS} = 30V$ )

3. Increase  $V_{GS}$  up to quiescent bias drain current  $I_{DQ}$

Figure 4.1: Fabricated SSPA prototype 1

The quiescent current steady state must be carefully controlled as it is influenced by the operating mode, the temperature and the overall thermal resistance. A drain current control is recommended on the biasing network.

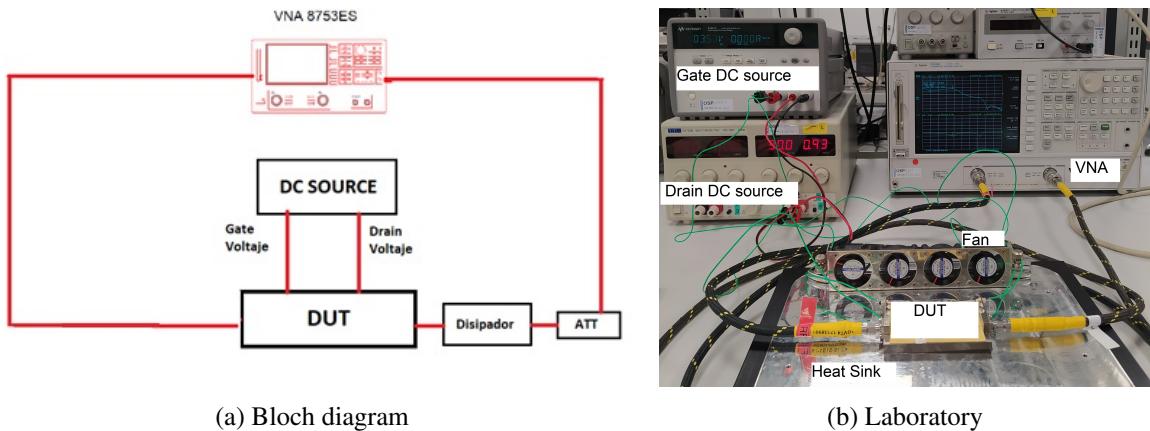

Figure 4.2: Small signal measurement test bench

Once the biasing procedure is completed, the next step is perform the small signal measurement, to do so, the test bench shown in figure 4.2 will be used where the following instruments are required:

1. **Vector Network Analyzer (VNA)** to perform S-parameters measurement.

2. **DC source** to bias the transistor.

3. **Attenuators** to protect the VNA (in this case, it is optional if the test is at very small signal levels).

4. **Dissipator** to achieve good heat dissipation.

5. **Calibration** kit for de-embedding additional elements placed in the RF path (harness, transitions, attenuators, etc...).

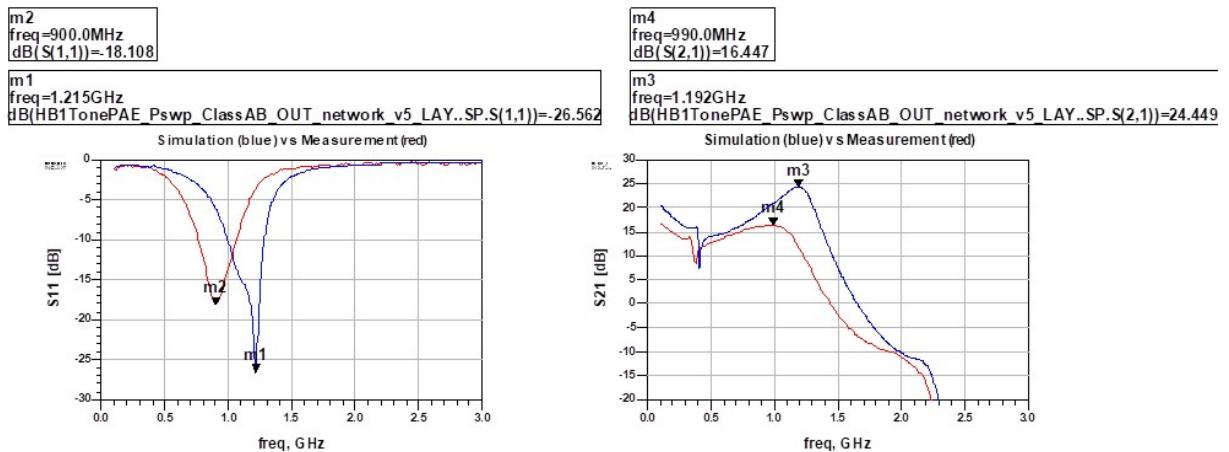

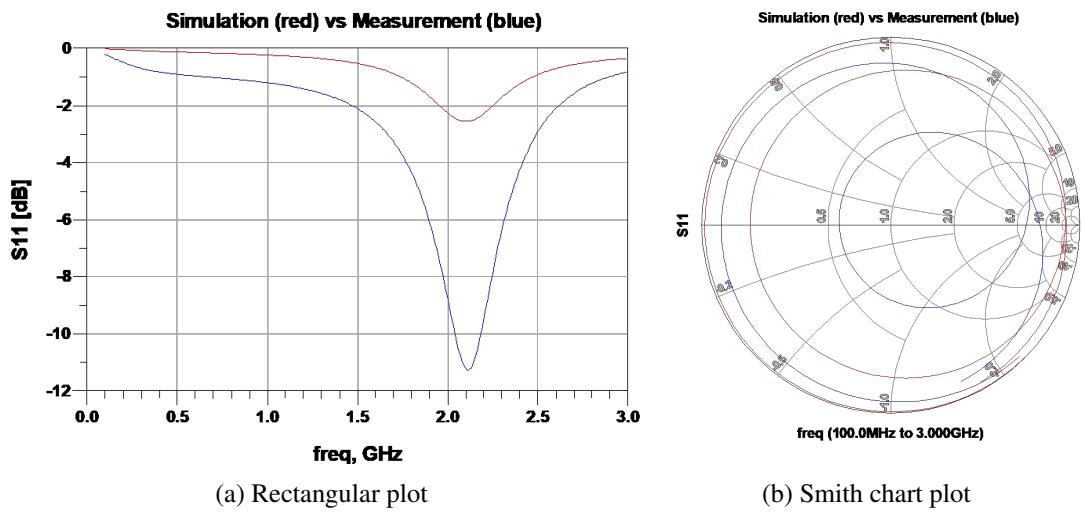

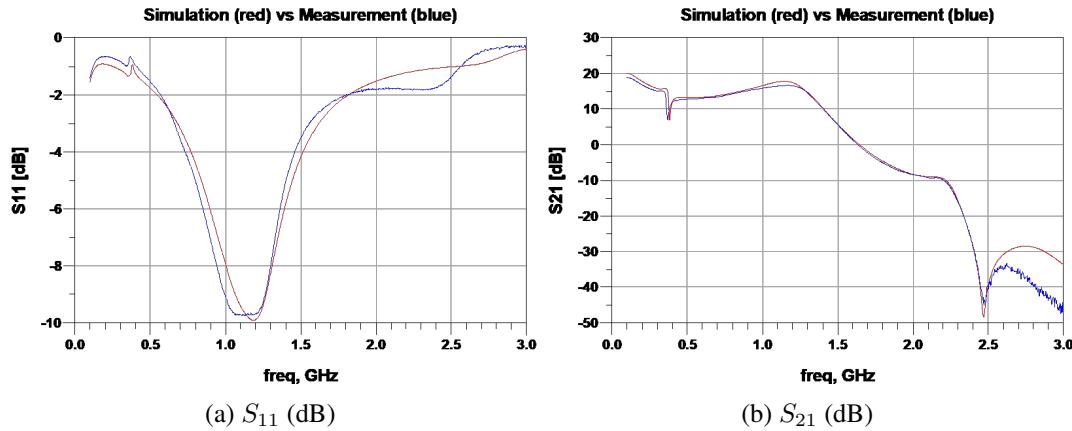

Measurement results are shown in figure 4.3, it can be observed that measurement traces present a frequency shift compared to simulation. Given this situation, two options could be considered. On one side, carry out power measurement at the frequency where the prototype 1 is centered (990 MHz), this will give us an idea about how the SSPA behaves when RF power is injected, however, efficiency and Power Added Efficiency cannot be calculated efficiently given that the output matching network was designed at 1.225GHz as the central frequency. On the other hand, shift back the prototype response to the design frequency in order to carry out power measurement efficiently.

Figure 4.3: Prototype 1 Small signal measurement: measurement vs simulation

### 4.1.2 Large signal Measurements

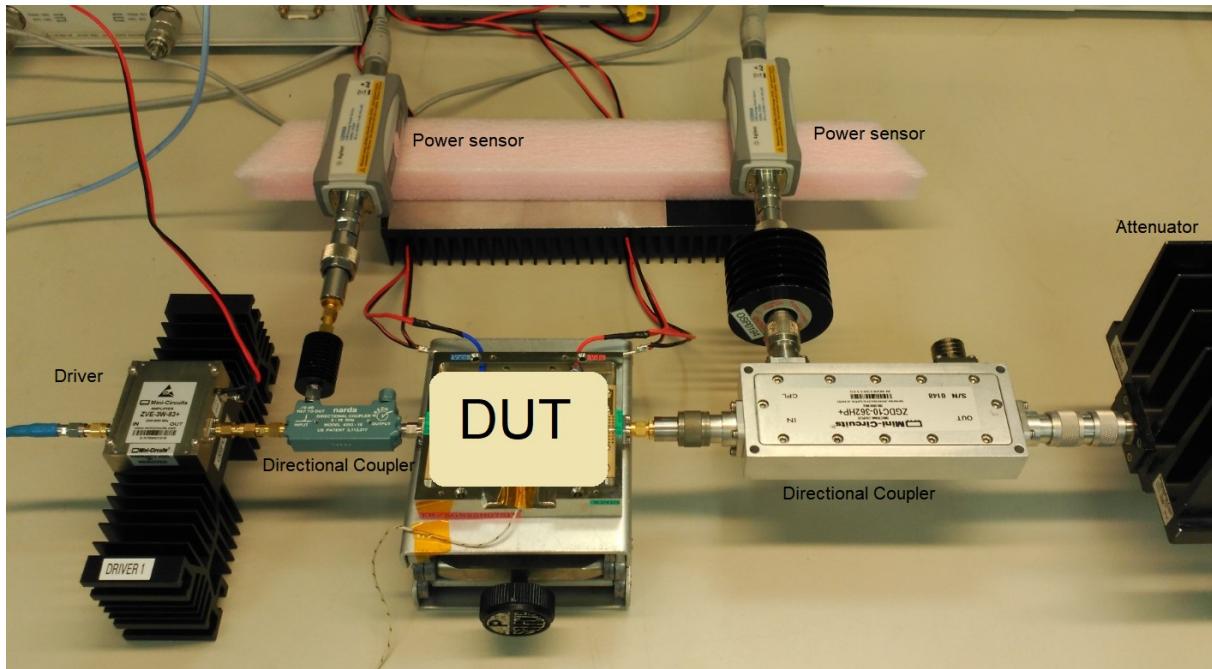

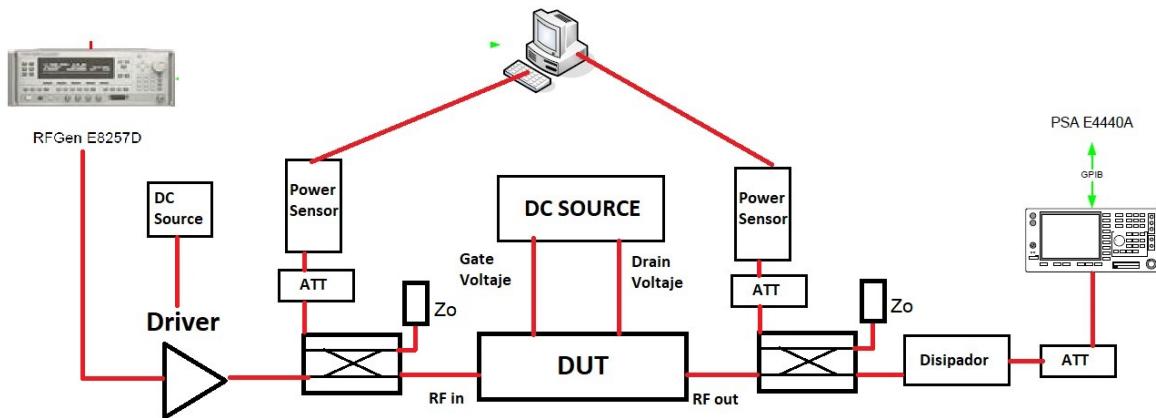

To be able to carry out power measurements, a more sophisticated test bench is required. Figure 4.4 shows the mounted test bench at the laboratory, it is equivalent to the block diagram shown in figure 4.5.

Figure 4.4: Large signal measurement laboratory test bench

Figure 4.5: Large signal measurements Bloch diagram test bench

In order to be able to mount the previously mentioned test bench, the following instruments are required:

1. **RF generator** to generate the RF signal.

2. **Directional couplers** to take samples of the signal at input and output of the DUT.

3. **Power sensors** to measure the signal power received at the coupled ports (input and

output power of the DUT).

4. **Attenuators** to protect power sensors and Power Signal Analyzer.

5. **Driver** to achieve the input power required by the DUT.

6. **Heatsink** to achieve good heat dissipation.

7. **DC source** for Driver and DUT biasing.

8. **Power Signal Analyzer (PSA)** to analyze the power signal at output of the DUT.

9. **Calibration Kit** for de-embedding additional elements placed at the RF path (harness, transitions, attenuators, couplers, etc)

#### 4.1.2.1 Line-up

To be able to test the DUT at large signal levels, a line-up must be defined in order to identify the necessary power amplification sections at the input of the DUT to achieve the required input power and the necessary attenuation at output to protect the instruments at the output of the DUT. Besides, line-up provides information about the input power of each stage of the RF path, this helps to select the model of each instrument in terms of power handling.

Having said that, let us introduce the two possible scenarios to be considered. The first one is one shown in figure 4.6 where the RF generator is able to handle up to -10 dBm RF power, this leads us to use a 48 dB pre-amplification stage. The second one is shown in figure 4.7 where the RF generator is able to handle up to +15 dBm RF power, this leads us to use a 24 dB pre-amplification stage. Both scenarios may be considered at the testing phase depending on the RF generator availability in the laboratory.

#### 4.1.2.2 Pre-amplification stage characterization

As stated previously, pre-amplification stage depends mainly on the RF generator maximum available power. Thus, considering the first case where the RF generator is able to handle up to +15dBm, a pre-amplification stage of 24 dB is required to achieve the input power required by

| Inputs |       | DUT   |        |         |        |       |         |       |       |       |

|--------|-------|-------|--------|---------|--------|-------|---------|-------|-------|-------|

| RF     | 25 °C | Units | Cable  | Coupler | Driver | DUT   | Coupler | ATT   | ATT   | Cable |

|        | G     | dB    | -1,0   | -0,1    | 48,0   | 17,2  | -0,1    | -30,0 | -20,0 | -1,0  |

|        | Pin   | dBm   | -14,9  | -15,9   | -16,0  | 32,0  | 49,2    | 49,1  | 29,1  | 28,1  |

|        | Pout  | dBm   | -15,90 | -16,00  | 32,00  | 49,24 | 49,14   | 19,14 | -0,86 | -1,86 |

Figure 4.6: Line-up using a -10 dBm maximum power RF generator

| Inputs |       | DUT   |       |         |        |       |         |       |       |       |

|--------|-------|-------|-------|---------|--------|-------|---------|-------|-------|-------|

| RF     | 25 °C | Units | Cable | Coupler | Driver | DUT   | Coupler | ATT   | ATT   | Cable |

|        | G     | dB    | -1,0  | -0,1    | 24,0   | 17,2  | -0,1    | -30,0 | -20,0 | -1,0  |

|        | Pin   | dBm   | 9,1   | 8,1     | 8,0    | 32,0  | 49,2    | 49,1  | 29,1  | 28,1  |

|        | Pout  | dBm   | 8,10  | 8,00    | 32,00  | 49,24 | 49,14   | 19,14 | -0,86 | -1,86 |

Figure 4.7: Line-up using a +15 dBm maximum power RF generator

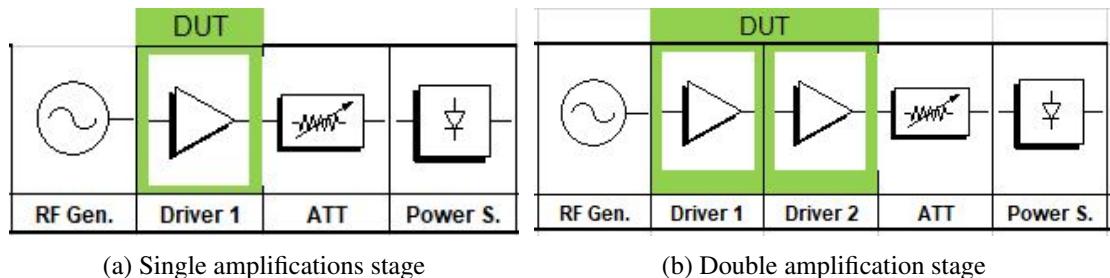

the DUT ( $P_{in} = 32 \text{ dBm}$ ). SPA029 SARAS Technology is the selected driver to be used in the pre-amplification stage, such power amplifier has been characterized in the laboratory using the test bench block diagram depicted in figure 4.8a.

Figure 4.8: Drivers characterization test bench block diagram

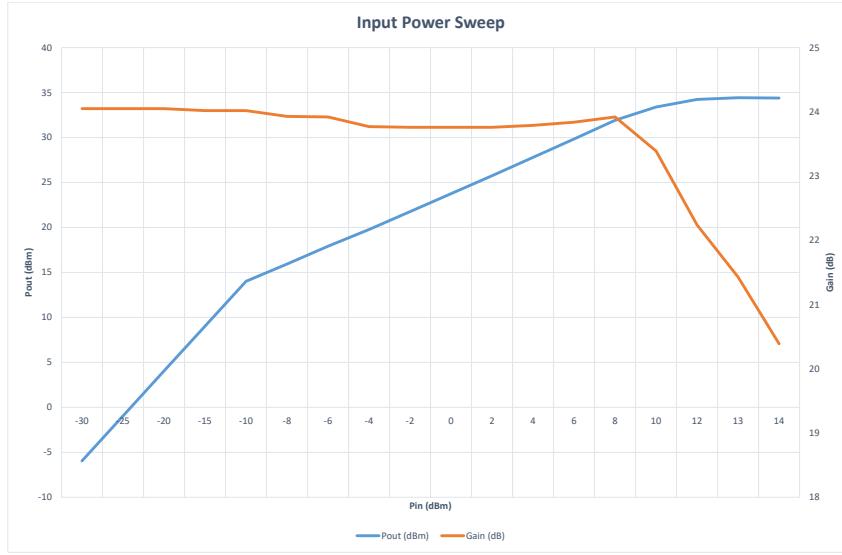

The obtained results are depicted in figure 4.9 and table 4.1, observe that the analyzed driver is able to handle up to  $P_{1dB} \geq 33 \text{ dBm}$  providing 23 dB power gain as stated by the manufacturer in the datasheet. Therefore, it will work perfectly for the SSPA power measurement given that it is able to handle 32 dBm at input of the SSPA below 1dB compression point.

Figure 4.9: Single Driver Input Power Sweep

Even though the analyzed driver works properly for the intended SSPA power measurement, the problem may come from the availability of the 15 dBm RF generator as mentioned previously. Hence, other solutions must be considered for the case where the RF generator is able to handle up to -10 dBm RF power. Such scenario requires higher gain in the pre-amplification stage, therefore, two options may be considered:

1. Single pre-amplification section using a single driver able to provide 48 dB power gain as stated in the line-up section.

2. Two pre-amplification sections concatenating two drivers as the one analyzed previously (SPA029 SARAS Technology) to provide 48 dB total power gain as stated in the line-up section.

In this case, option 2 will be considered due to the availability of the instruments. Such scenario where two drivers are concatenated has been characterized in the laboratory using the test bench shown in figure 4.8b and the results obtained are depicted in table 4.2. In the same way as in case of a single driver, the proposed pre-amplification stage is able to handle

| RF Gen.        |           | Driver    |                 |               |

|----------------|-----------|-----------|-----------------|---------------|

| $P_{av}$ (dBm) | Gain (dB) | Comp (dB) | $P_{out}$ (dBm) | $P_{out}$ (W) |

| -30            | 24,05     | 0         | -5,95           | 0,0003        |

| -25            | 24,05     | 0         | -0,95           | 0,0008        |

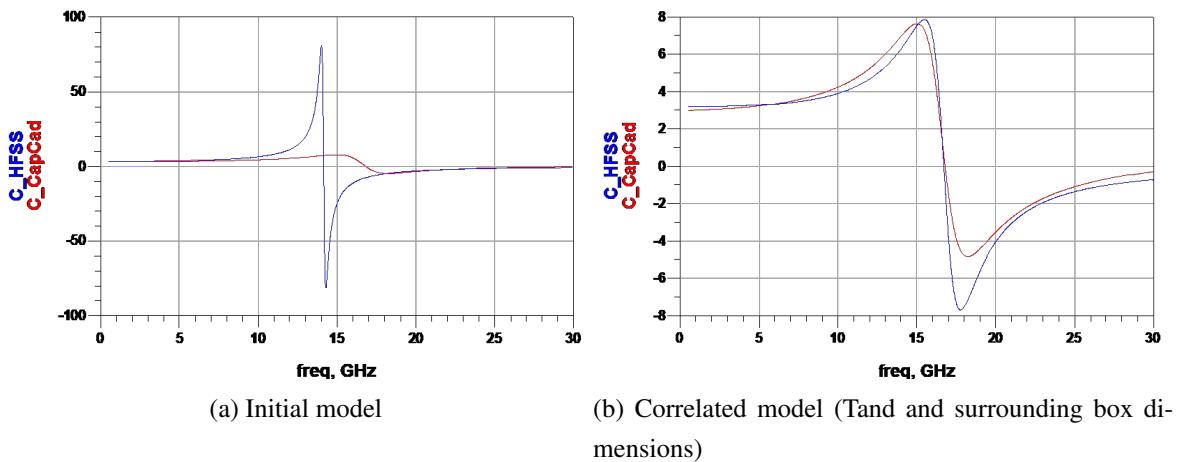

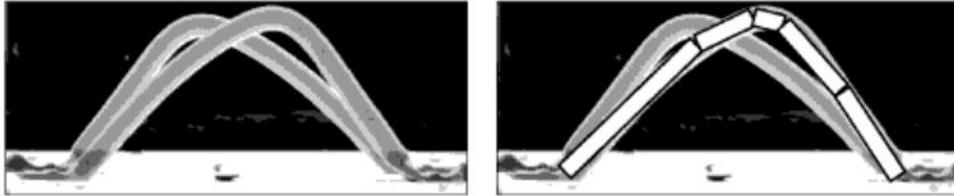

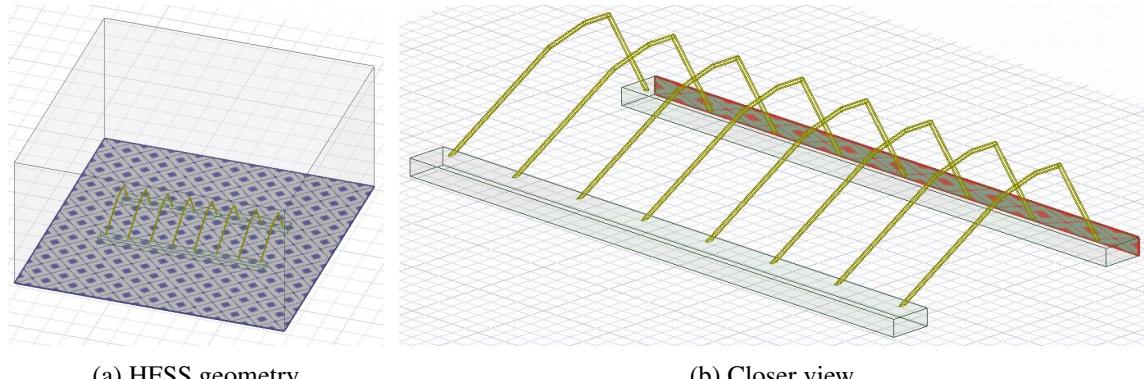

| -20            | 24,05     | 0         | 4,05            | 0,0025        |